### Features

- Low-voltage and Standard-voltage Operation

- $-2.7 (V_{CC} = 2.7V \text{ to } 5.5V)$

- 1.8 (V<sub>CC</sub> = 1.8V to 5.5V)

- User-selectable Internal Organization

- 2K: 256 x 8 or 128 x 16

- 4K: 512 x 8 or 256 x 16

- 3-wire Serial Interface

- Sequential Read Operation

Sequential Read Operation

- 2 MHz Clock Rate (5V)

- Self-timed Write Cycle (10 ms Max)

- High Reliability

- Endurance: 1 Million Write Cycles

- Data Retention: 100 Years

- Automotive Grade, Extended Temperature, and Lead-free/Halogen-free

Devices Available

- 8-lead PDIP, 8-lead JEDEC SOIC, 8-lead EIAJ SOIC, 8-lead MAP, 8-lead TSSOP, and 8-ball dBGA2<sup>™</sup> Packages

## Description

The AT93C56A/66A provides 2048/4096 bits of serial electrically erasable programmable read-only memory (EEPROM) organized as 128/256 words of 16 bits each when the ORG pin is connected to VCC and 256/512 words of 8 bits each when it is tied to ground. The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operations are essential. The AT93C56A/66A is available in space-saving 8-lead PDIP, 8-lead JEDEC SOIC, 8-lead EIAJ SOIC, 8-lead MAP, 8-lead TSSOP, and 8-ball dBGA2<sup>™</sup> packages.

# 3-wire Serial EEPROMs

2K (256 x 8 or 128 x 16)

4K (512 x 8 or 256 x 16)

## AT93C56A AT93C66A

# Advance Information

### **Pin Configurations**

| Pin Name | Function              |

|----------|-----------------------|

| CS       | Chip Select           |

| SK       | Serial Data Clock     |

| DI       | Serial Data Input     |

| DO       | Serial Data Output    |

| GND      | Ground                |

| VCC      | Power Supply          |

| ORG      | Internal Organization |

| DC       | Don't Connect         |

8-lead TSSOP

7

6

5

🗆 ORG

GND

CS

SK 🖂 2

DO

4

#### 8-ball dBGA2 8-lead SOIC VCC 8 ᠿ CS CS 🗆 1 8 DC (7) 2 SK SK 🗆 2 7 ORG 6 3 DI 🗆 ORG DI 🗆 3 6 4 GND (5) DO DO 🗆 GND 4 5 Bottom View 8-lead MAP 8-lead PDIP VCC 8 $\Box$ cs 8 vcc CS 🗌 1 2 SK SK 🗆 2 ORG 6 3 DI 6 ORG GND 5 5 GND Bottom View

The AT93C56A/66A is enabled through the Chip Select pin (CS) and accessed via a 3-wire serial interface consisting of Data Input (DI), Data Output (DO), and Shift Clock (SK). Upon receiving a READ instruction at DI, the address is decoded and the data is

clocked out serially on the data output pin DO. The WRITE cycle is completely selftimed and no separate ERASE cycle is required before WRITE. The WRITE cycle is only enabled when the part is in the ERASE/WRITE ENABLE state. When CS is brought "high" following the initiation of a WRITE cycle, the DO pin outputs the READY/BUSY status of the part.

The AT93C56A/66A is available in 2.7V to 5.5V and 1.8V to 5.5V versions.

#### Absolute Maximum Ratings\*

| Operating Temperature55°C to +125°C                       |

|-----------------------------------------------------------|

| Storage Temperature65°C to +150°C                         |

| Voltage on Any Pin<br>with Respect to Ground1.0V to +7.0V |

| Maximum Operating Voltage 6.25V                           |

| DC Output Current 5.0 mA                                  |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability

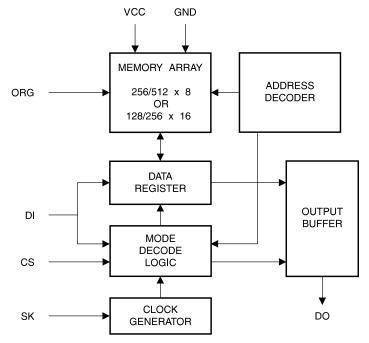

### **Block Diagram**

Note: When the ORG pin is connected to VCC, the x 16 organization is selected. When it is connected to ground, the x 8 organization is selected. If the ORG pin is left unconnected and the application does not load the input beyond the capability of the internal 1 Meg ohm pullup, then the x 16 organization is selected. The feature is not available on the 1.8V devices.

## Pin Capacitance<sup>(1)</sup>

Applicable over recommended operating range from T<sub>A</sub> =  $25^{\circ}$ C, f = 1.0 MHz, V<sub>CC</sub> = +5.0V (unless otherwise noted).

| Symbol           | Test Conditions                | Мах | Units | Conditions     |

|------------------|--------------------------------|-----|-------|----------------|

| C <sub>OUT</sub> | Output Capacitance (DO)        | 5   | pF    | $V_{OUT} = 0V$ |

| C <sub>IN</sub>  | Input Capacitance (CS, SK, DI) | 5   | pF    | $V_{IN} = 0V$  |

Note: 1. This parameter is characterized and is not 100% tested.

### **DC** Characteristics

Applicable over recommended operating range from:  $T_{AI} = -40^{\circ}C$  to +85°C,  $V_{CC} = +1.8V$  to +5.5V,  $T_{AE} = -40^{\circ}C$  to +125°C,  $V_{CC} = +1.8V$  to +5.5V (unless otherwise noted).

| Symbol                                                             | Parameter                               | Test Condition                                           |                           | Min                           | Тур | Max                                          | Unit |

|--------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------|---------------------------|-------------------------------|-----|----------------------------------------------|------|

| V <sub>CC1</sub>                                                   | Supply Voltage                          |                                                          |                           | 1.8                           |     | 5.5                                          | V    |

| V <sub>CC2</sub>                                                   | Supply Voltage                          |                                                          |                           | 2.7                           |     | 5.5                                          | V    |

| V <sub>CC3</sub>                                                   | Supply Voltage                          |                                                          |                           | 4.5                           |     | 5.5                                          | V    |

|                                                                    |                                         |                                                          | READ at 1.0 MHz           |                               | 0.5 | 2.0                                          | mA   |

| I <sub>CC</sub>                                                    | Supply Current                          | $V_{CC} = 5.0V$                                          | WRITE at 1.0 MHz          |                               | 0.5 | 2.0                                          | mA   |

| SB1                                                                | Standby Current                         | V <sub>CC</sub> = 1.8V                                   | CS = 0V                   |                               | 0   | 0.1                                          | μA   |

| I <sub>SB2</sub>                                                   | Standby Current                         | V <sub>CC</sub> = 2.7V                                   | CS = 0V                   |                               | 6.0 | 10.0                                         | μA   |

| I <sub>SB3</sub>                                                   | Standby Current                         | V <sub>CC</sub> = 5.0V                                   | CS = 0V                   |                               | 17  | 30                                           | μA   |

| IIL                                                                | Input Leakage                           | $V_{IN} = 0V$ to $V_{CC}$                                |                           |                               | 0.1 | 3.0                                          | μA   |

| I <sub>OL</sub>                                                    | Output Leakage                          | $V_{IN} = 0V$ to $V_{CC}$                                |                           |                               | 0.1 | 3.0                                          | μA   |

| V <sub>IL1</sub> <sup>(1)</sup><br>V <sub>IH1</sub> <sup>(1)</sup> | Input Low Voltage<br>Input High Voltage | $2.7 \text{V} \le \text{V}_{\text{CC}} \le 5.5 \text{V}$ |                           | -0.6<br>2.0                   |     | 0.8<br>V <sub>CC</sub> + 1                   | V    |

| V <sub>IL2</sub> <sup>(1)</sup><br>V <sub>IH2</sub> <sup>(1)</sup> | Input Low Voltage<br>Input High Voltage | $1.8V \le V_{CC} \le 2.7V$                               |                           | -0.6<br>V <sub>CC</sub> x 0.7 |     | V <sub>CC</sub> x 0.3<br>V <sub>CC</sub> + 1 | V    |

| V <sub>OL1</sub>                                                   | Output Low Voltage                      |                                                          | I <sub>OL</sub> = 2.1 mA  |                               |     | 0.4                                          | V    |

| V <sub>OH1</sub>                                                   | Output High Voltage                     | $2.7V \le V_{CC} \le 5.5V$                               | I <sub>OH</sub> = -0.4 mA | 2.4                           |     |                                              | V    |

| V <sub>OL2</sub>                                                   | Output Low Voltage                      |                                                          | I <sub>OL</sub> = 0.15 mA |                               |     | 0.2                                          | V    |

| V <sub>OH2</sub>                                                   | Output High Voltage                     | $1.8V \le V_{CC} \le 2.7V$                               | I <sub>OH</sub> = -100 μA | V <sub>CC</sub> – 0.2         |     |                                              | V    |

Note: 1.  $V_{IL}$  min and  $V_{IH}$  max are reference only and are not tested.

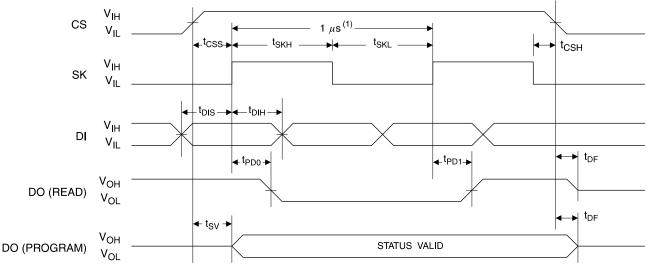

### **AC Characteristics**

Applicable over recommended operating range from T<sub>AI</sub> =  $-40^{\circ}$ C to + 85°C, T<sub>AE</sub> =  $-40^{\circ}$ C to +125°C, V<sub>CC</sub> = As Specified, CL = 1 TTL Gate and 100 pF (unless otherwise noted).

| Symbol                   | Parameter                     | Test Condition                                                                                                              |                                                                                                                                                     | Min         | Тур | Max            | Units       |

|--------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|----------------|-------------|

| f <sub>SK</sub>          | SK Clock<br>Frequency         | $\begin{array}{l} 4.5 V \leq V_{CC} \leq 5.5 V \\ 2.7 V \leq V_{CC} \leq 5.5 V \\ 1.8 V \leq V_{CC} \leq 5.5 V \end{array}$ | 1                                                                                                                                                   | 0<br>0<br>0 |     | 2<br>1<br>0.25 | MHz         |

| t <sub>sкн</sub>         | SK High Time                  | $\begin{array}{ c c c c } 2.7V \leq V_{CC} \leq 5.5V \\ 1.8V \leq V_{CC} \leq 5.5V \end{array}$                             |                                                                                                                                                     | 250<br>1000 |     |                | ns          |

| t <sub>SKL</sub>         | SK Low Time                   | $\begin{array}{ c c c c c } 2.7V \leq V_{CC} \leq 5.5V \\ 1.8V \leq V_{CC} \leq 5.5V \end{array}$                           |                                                                                                                                                     | 250<br>1000 |     |                | ns          |

| t <sub>CS</sub>          | Minimum CS<br>Low Time        | $\begin{array}{c} 2.7 V \leq V_{CC} \leq 5.5 V \\ 1.8 V \leq V_{CC} \leq 5.5 V \end{array}$                                 |                                                                                                                                                     | 250<br>1000 |     |                | ns          |

| t <sub>CSS</sub>         | CS Setup Time                 | Relative to SK                                                                                                              | $\begin{array}{c} 2.7 \text{V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{V} \\ 1.8 \text{V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{V} \end{array}$ | 50<br>200   |     |                | ns          |

| t <sub>DIS</sub>         | DI Setup Time                 | Relative to SK                                                                                                              | $\begin{array}{l} 2.7 \text{V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{V} \\ 1.8 \text{V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{V} \end{array}$ | 100<br>400  |     |                | ns          |

| t <sub>CSH</sub>         | CS Hold Time                  | Relative to SK                                                                                                              |                                                                                                                                                     | 0           |     |                | ns          |

| t <sub>DIH</sub>         | DI Hold Time                  | Relative to SK                                                                                                              | $\begin{array}{l} 2.7 \text{V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{V} \\ 1.8 \text{V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{V} \end{array}$ | 100<br>400  |     |                | ns          |

| t <sub>PD1</sub>         | Output Delay to "1"           | AC Test                                                                                                                     | $\begin{array}{c} 2.7 \text{V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{V} \\ 1.8 \text{V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{V} \end{array}$ |             |     | 250<br>1000    | ns          |

| t <sub>PD0</sub>         | Output Delay to "0"           | AC Test                                                                                                                     | $\begin{array}{c} 2.7 V \leq V_{CC} \leq 5.5 V \\ 1.8 V \leq V_{CC} \leq 5.5 V \end{array}$                                                         |             |     | 250<br>1000    | ns          |

| t <sub>SV</sub>          | CS to Status Valid            | AC Test                                                                                                                     | $\begin{array}{c} 2.7 \text{V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{V} \\ 1.8 \text{V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{V} \end{array}$ |             |     | 250<br>1000    | ns          |

| t <sub>DF</sub>          | CS to DO in High<br>Impedance | AC Test<br>CS = V <sub>IL</sub>                                                                                             | $\begin{array}{c} 2.7 \text{V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{V} \\ 1.8 \text{V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{V} \end{array}$ |             |     | 150<br>400     | ns          |

|                          |                               | 1                                                                                                                           |                                                                                                                                                     |             |     | 10             | ms          |

| t <sub>WP</sub>          | Write Cycle Time              |                                                                                                                             | $4.5V \le V_{CC} \le 5.5V$                                                                                                                          | 0.1         | 3   |                | ms          |

| Endurance <sup>(1)</sup> | 5.0V, 25°C, Page Mode         |                                                                                                                             | ,                                                                                                                                                   | 1M          |     |                | Write Cycle |

Note: 1. This parameter is characterized and is not 100% tested.

|             |    | Ор   | Addr                           | Address                         |                                 | ata                              |                                                                                                   |

|-------------|----|------|--------------------------------|---------------------------------|---------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------|

| Instruction | SB | Code | x 8                            | x 16                            | x 8                             | x 16                             | Comments                                                                                          |

| READ        | 1  | 10   | $A_8 - A_0$                    | A <sub>7</sub> – A <sub>0</sub> |                                 |                                  | Reads data stored in memory, at specified address.                                                |

| EWEN        | 1  | 00   | 11XXXXXXX                      | 11XXXXXX                        |                                 |                                  | Write enable must precede all programming modes.                                                  |

| ERASE       | 1  | 11   | A <sub>8</sub> -A <sub>0</sub> | $A_7 - A_0$                     |                                 |                                  | Erases memory location $A_n - A_0$ .                                                              |

| WRITE       | 1  | 01   | A <sub>8</sub> -A <sub>0</sub> | $A_7 - A_0$                     | $D_{7} - D_{0}$                 | D <sub>15</sub> – D <sub>0</sub> | Writes memory location $A_n - A_0$ .                                                              |

| ERAL        | 1  | 00   | 10XXXXXXX                      | 10XXXXXX                        |                                 |                                  | Erases all memory locations. Valid only at $V_{CC}$ = 4.5V to 5.5V.                               |

| WRAL        | 1  | 00   | 01XXXXXXX                      | 01XXXXXX                        | D <sub>7</sub> – D <sub>0</sub> | D <sub>15</sub> – D <sub>0</sub> | Writes all memory locations. Valid only at $V_{CC} = 5.0V \pm 10\%$ and Disable Register cleared. |

| EWDS        | 1  | 00   | 00XXXXXXX                      | 00XXXXXX                        |                                 |                                  | Disables all programming instructions.                                                            |

### Instruction Set for the AT93C56A and AT93C66A

Note: The X's in the address field represent don't care values and must be clocked.

#### **Functional Description**

The AT93C56A/66A is accessed via a simple and versatile 3-wire serial communication interface. Device operation is controlled by seven instructions issued by the host processor. **A valid instruction starts with a rising edge of CS** and consists of a Start Bit (logic "1") followed by the appropriate Op Code and the desired memory address location.

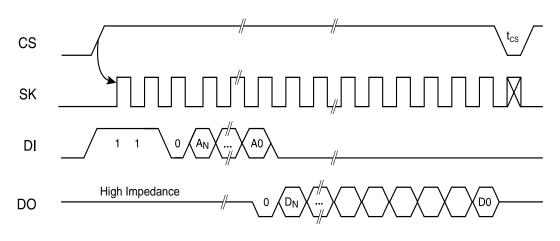

**READ (READ):** The Read (READ) instruction contains the address code for the memory location to be read. After the instruction and address are decoded, data from the selected memory location is available at the serial output pin DO. Output data changes are synchronized with the rising edges of serial clock SK. It should be noted that a dummy bit (logic "0") precedes the 8- or 16-bit data output string. The AT93C56A/66A supports sequential read operations. The device will automatically increment the internal address pointer and clock out the next memory location as long as Chip Select (CS) is held high. In this case, the dummy bit (logic "0") will not be clocked out between memory locations, thus allowing for a continuous stream of data to be read.

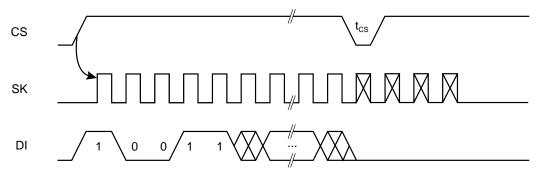

**ERASE/WRITE (EWEN):** To assure data integrity, the part automatically goes into the Erase/Write Disable (EWDS) state when power is first applied. An Erase/Write Enable (EWEN) instruction must be executed first before any programming instructions can be carried out. Please note that once in the EWEN state, programming remains enabled until an EWDS instruction is executed or  $V_{CC}$  power is removed from the part.

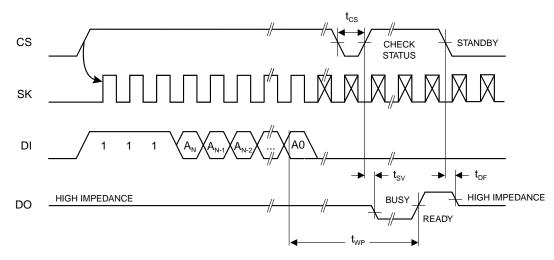

**ERASE (ERASE):** The Erase (ERASE) instruction programs all bits in the specified memory location to the logical "1" state. The self-timed erase cycle starts once the ERASE instruction and address are decoded. The DO pin outputs the READY/BUSY status of the part if CS is brought high after being kept low for a minimum of 250 ns ( $t_{CS}$ ). A logic "1" at pin DO indicates that the selected memory location has been erased, and the part is ready for another instruction.

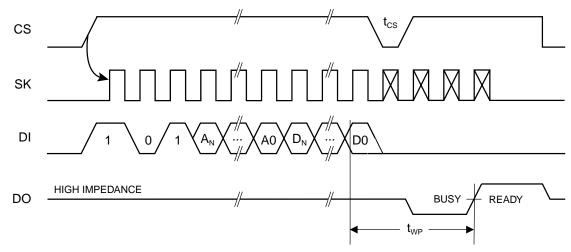

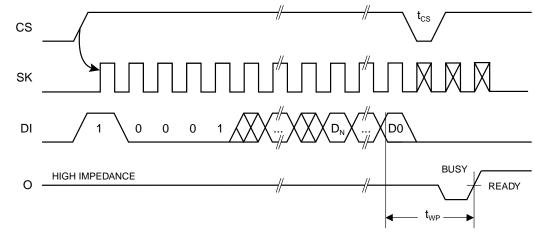

**WRITE (WRITE):** The Write (WRITE) instruction contains the 8 or 16 bits of data to be written into the specified memory location. The self-timed programming cycle  $t_{WP}$  starts after the last bit of data is received at serial data input pin DI. The DO pin outputs the READY/BUSY status of the part if CS is brought high after being kept low for a minimum of 250 ns ( $t_{CS}$ ). A logic "0" at DO indicates that programming is still in progress. A logic "1" indicates that the memory location at the specified address has been written with the data pattern contained in the instruction and the part is ready for further instructions. A **READY/BUSY status cannot be obtained if the CS is brought high after the end of the self-timed programming cycle t<sub>WP</sub>**.

**ERASE ALL (ERAL):** The Erase All (ERAL) instruction programs every bit in the memory array to the logic "1" state and is primarily used for testing purposes. The DO pin outputs the READY/BUSY status of the part if CS is brought high after being kept low for a minimum of 250 ns ( $t_{CS}$ ). The ERAL instruction is valid only at  $V_{CC} = 5.0V \pm 10\%$ .

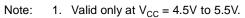

**WRITE ALL (WRAL)**: The Write All (WRAL) instruction programs all memory locations with the data patterns specified in the instruction. The DO pin outputs the READY/BUSY status of the part if CS is brought high after being kept low for a minimum of 250 ns ( $t_{CS}$ ). The WRAL instruction is valid only at  $V_{CC} = 5.0V \pm 10\%$ .

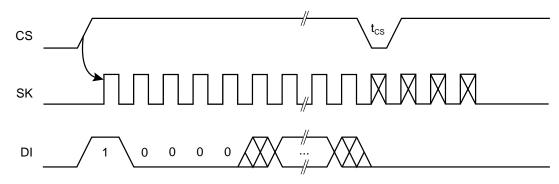

**ERASE/WRITE DISABLE (EWDS):** To protect against accidental data disturb, the Erase/Write Disable (EWDS) instruction disables all programming modes and should be executed after all programming operations. The operation of the READ instruction is independent of both the EWEN and EWDS instructions and can be executed at any time.

### **Timing Diagrams**

Note: 1. This is the minimum SK period.

|                | AT93C56A (2K)                 |                               | AT93C6         | 6A (4K)         |

|----------------|-------------------------------|-------------------------------|----------------|-----------------|

| I/O            | x 8                           | x 16                          | x 8            | x 16            |

| A <sub>N</sub> | A <sub>8</sub> <sup>(1)</sup> | A <sub>7</sub> <sup>(2)</sup> | A <sub>8</sub> | A <sub>7</sub>  |

| D <sub>N</sub> | D <sub>7</sub>                | D <sub>15</sub>               | D <sub>7</sub> | D <sub>15</sub> |

### **Organization Key for Timing Diagrams**

A<sub>8</sub> is a DON'T CARE value, but the extra clock is required.

A<sub>7</sub> is a DON'T CARE value, but the extra clock is required. Notes:

#### **READ Timing**

#### **EWEN** Timing

### **EWDS** Timing

### WRITE Timing

WRAL Timing<sup>(1)</sup>

### **ERASE** Timing

ERAL Timing<sup>(1)</sup>

### AT93C56A Ordering Information

| Ordering Code       | Package | Operation Range                                   |

|---------------------|---------|---------------------------------------------------|

| AT93C56A-10PI-2.7   | 8P3     |                                                   |

| AT93C56A-10SI-2.7   | 8S1     |                                                   |

| AT93C56AW-10SI-2.7  | 8S2     | Industrial Temperature                            |

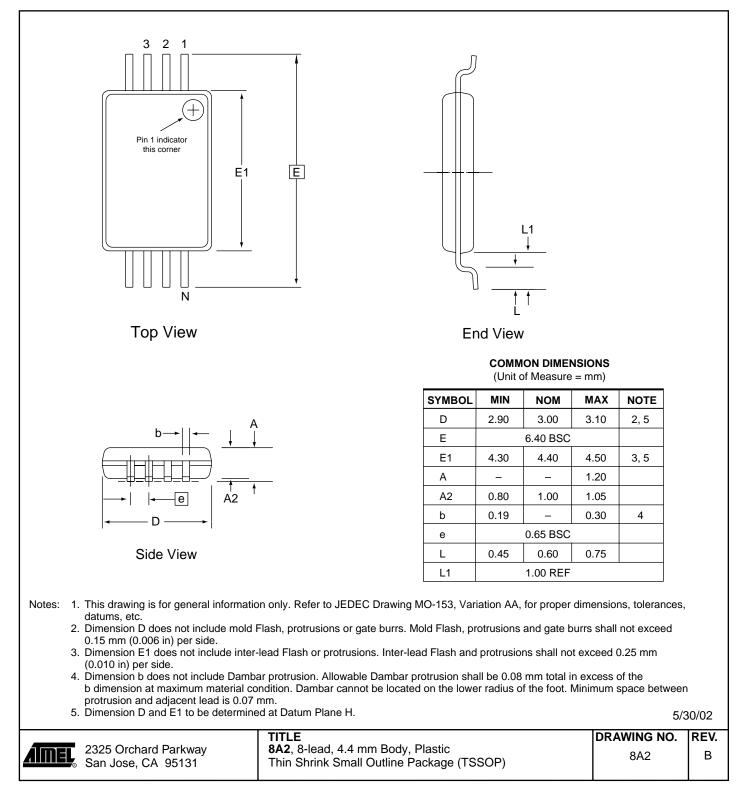

| AT93C56A-10TI-2.7   | 8A2     | (-40°C to 85°C)                                   |

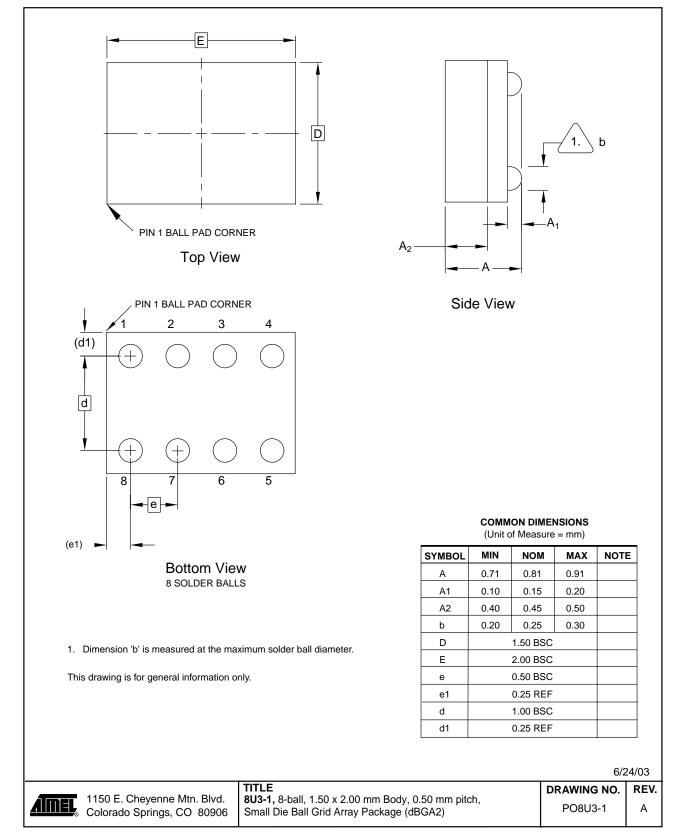

| AT93C56AU3-10UI-2.7 | 8U3-1   |                                                   |

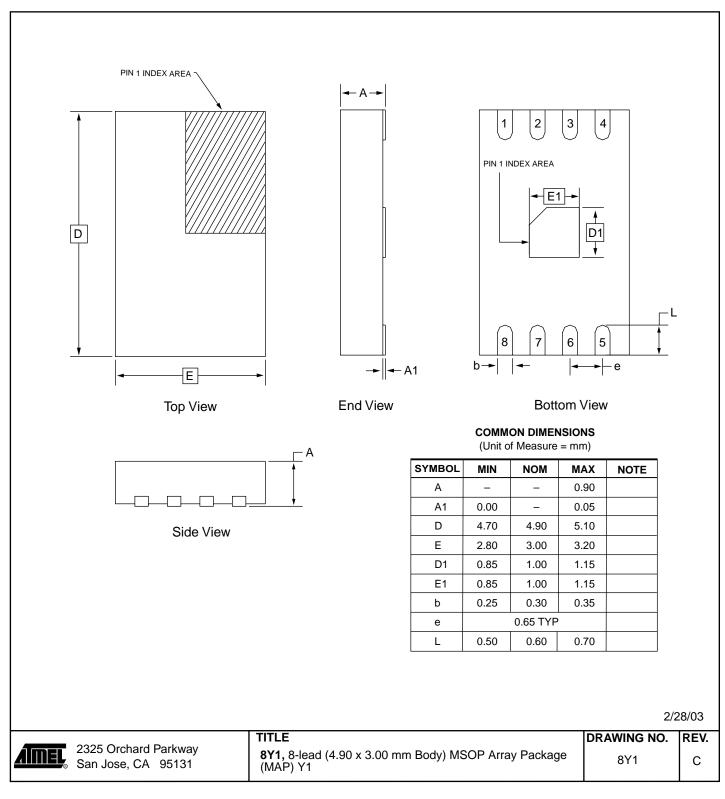

| AT93C56AY1-10YI-2.7 | 8Y1     |                                                   |

| AT93C56A-10PI-1.8   | 8P3     |                                                   |

| AT93C56A-10SI-1.8   | 8S1     |                                                   |

| AT93C56AW-10SI-1.8  | 8S2     | Industrial Temperature                            |

| AT93C56A-10TI-1.8   | 8A2     | (–40°C to 85°C)                                   |

| AT93C56AU3-10UI-1.8 | 8U3-1   |                                                   |

| AT93C56AY1-10YI-1.8 | 8Y1     |                                                   |

| AT93C56A-10SU-2.7   | 8S1     |                                                   |

| AT93C56A-10SU-1.8   | 8S1     | Lead-free/Halogen-free/<br>Industrial Temperature |

| AT93C56A-10TU-2.7   | 8A2     | (-40°C to 85°C)                                   |

| AT93C56A-10TU-1.8   | 8A2     |                                                   |

|                     |         | Lead-free/Halogen-free/                           |

| AT93C56A-10SQ-2.7   | 8S1     | High Grade/Extended Temperature                   |

|                     |         | (–40°C to 125°C)                                  |

| AT02056A 1005 2.7   | 964     | High Grade/Extended Temperature                   |

| AT93C56A-10SE-2.7   | 8S1     | (-40°C to 125°C)                                  |

Note: For 2.7V devices used in the 4.5V to 5.5V range, please refer to performance values in the AC and DC characteristics table.

|       | Package Type                                                                              |  |  |  |

|-------|-------------------------------------------------------------------------------------------|--|--|--|

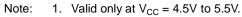

| 8P3   | 8-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)                                   |  |  |  |

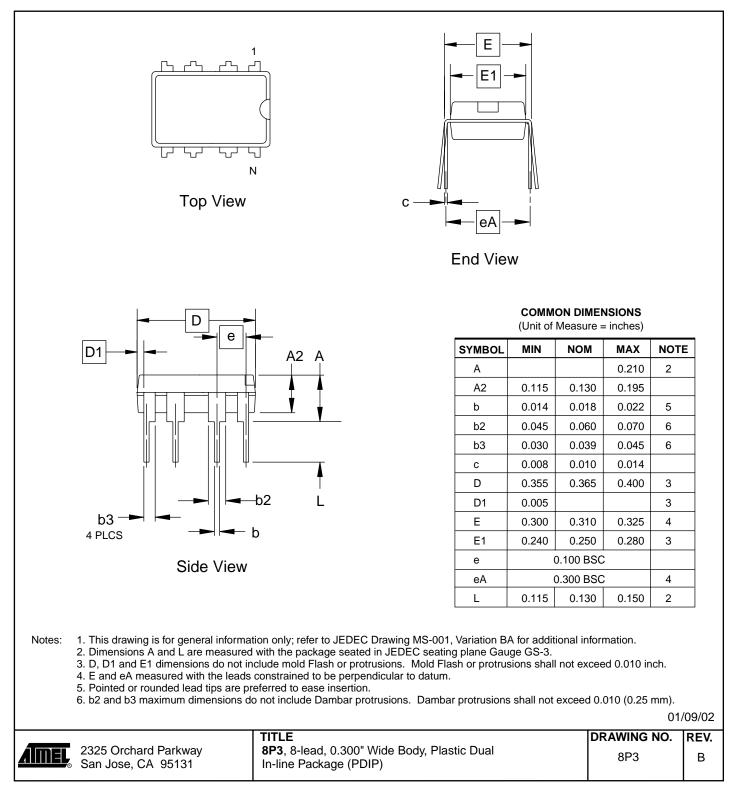

| 8S1   | 8-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)                         |  |  |  |

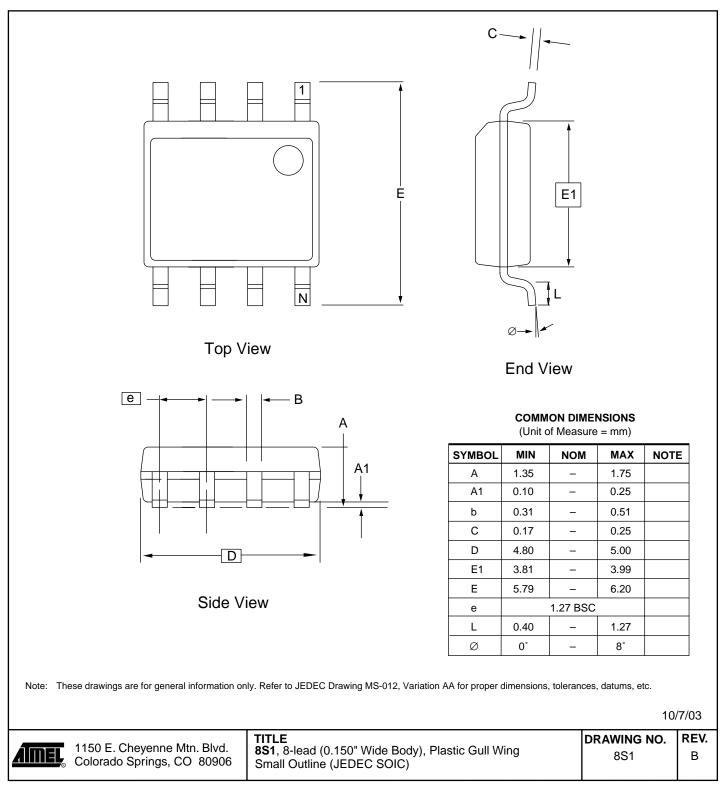

| 8S2   | 8-lead, 0.200" Wide, Plastic Gull Wing Small Outline (EIAJ SOIC)                          |  |  |  |

| 8A2   | 8-lead, 0.170" Wide, Thin Shrink Small Outline Package (TSSOP)                            |  |  |  |

| 8U3-1 | 8-ball, die Ball Grid Array Package (dBGA2)                                               |  |  |  |

| 8Y1   | 8-lead, 4.90 mm x 3.00 mm Body, Dual Footprint, Non-leaded, Miniature Array Package (MAP) |  |  |  |

|       | Options                                                                                   |  |  |  |

| -2.7  | Low-voltage (2.7V to 5.5V)                                                                |  |  |  |

| 1.8   | Low-voltage (1.8V to 5.5V)                                                                |  |  |  |

### AT93C66A Ordering Information

| Ordering Code       | Package | Operation Range                                   |

|---------------------|---------|---------------------------------------------------|

| AT93C66A-10PI-2.7   | 8P3     |                                                   |

| AT93C66A-10SI-2.7   | 8S1     |                                                   |

| AT93C66AW-10SI-2.7  | 8S2     | Industrial                                        |

| AT93C66A-10TI-2.7   | 8A2     | (−40°C to 85°C)                                   |

| AT93C66AU3-10UI-2.7 | 8U3-1   |                                                   |

| AT93C66AY1-10YI-2.7 | 8Y1     |                                                   |

| AT93C66A-10PI-1.8   | 8P3     |                                                   |

| AT93C66A-10SI-1.8   | 8S1     |                                                   |

| AT93C66AW-10SI-1.8  | 8S2     | Industrial                                        |

| AT93C66A-10TI-1.8   | 8A2     | (−40°C to 85°C)                                   |

| AT93C66AU3-10UI-1.8 | 8U3-1   |                                                   |

| AT93C66AY1-10YI-1.8 | 8Y1     |                                                   |

| AT93C66A-10SU-2.7   | 8S1     |                                                   |

| AT93C66A-10SU-1.8   | 8S1     | Lead-free/Halogen-free/<br>Industrial Temperature |

| AT93C66A-10TU-2.7   | 8A2     | (–40°C to 85°C)                                   |

| AT93C66A-10TU-1.8   | 8A2     | (=40 C 10 03 C)                                   |

|                     |         | Lead-free/Halogen-free/                           |

|                     | 8S1     | High Grade/Extended Temperature                   |

| AT93C66A-10SQ-2.7   |         | (–40°C to 125°C)                                  |

|                     | 851     | High Grade/Extended Temperature                   |

| AT93C66A-10SE-2.7   |         | (–40°C to 125°C)                                  |

Note: For 2.7V devices used in the 4.5V to 5.5V range, please refer to performance values in the AC and DC characteristics table.

|       | Package Type                                                                              |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------|--|--|--|--|

| 8P3   | 8-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)                                   |  |  |  |  |

| 8S1   | 8-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)                         |  |  |  |  |

| 8S2   | 8-lead, 0.200" Wide, Plastic Gull Wing Small Outline (EIAJ SOIC)                          |  |  |  |  |

| 8A2   | 8-lead, 0.170" Wide, Thin Shrink Small Outline Package (TSSOP)                            |  |  |  |  |

| 8U3-1 | 8-ball, die Ball Grid Array Package (dBGA2)                                               |  |  |  |  |

| 8Y1   | 8-lead, 4.90 mm x 3.00 mm Body, Dual Footprint, Non-leaded, Miniature Array Package (MAP) |  |  |  |  |

|       | Options                                                                                   |  |  |  |  |

| -2.7  | Low-voltage (2.7V to 5.5V)                                                                |  |  |  |  |

| -1.8  | Low-voltage (1.8V to 5.5V)                                                                |  |  |  |  |

### **Packaging Information**

#### 8P3 – PDIP

#### 8S2 – EIAJ SOIC

#### 8U3-1 - dBGA2

#### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Atmel Operations**

#### Memory

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

#### Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

Literature Requests www.atmel.com/literature

**Disclaimer:** Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time wihout notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

© Atmel Corporation 2004. All rights reserved. Atmel<sup>®</sup> and combinations thereof, are the registered trademarks, and dBGA<sup>™</sup> is the trademark of Atmel Corporation or its subsidiaries. Other terms and product names may be the trademarks of others.