# HD6305V0, HD63A05V0, HD63B05V0 CMOS MCU (Microcomputer Unit)

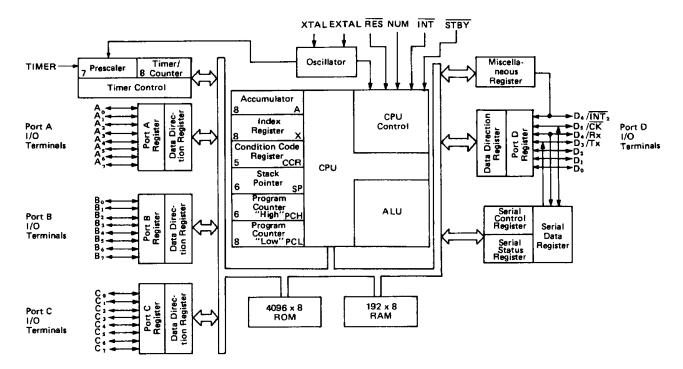

The HD6305V0 is a CMOS 8-bit single-chip MCU which is similar to the HD6305X MCU family. This version is upward compatible with the HD6805 family in respect to instructions. A CPU, a clock generator, a 4k-byte ROM, a 192-byte RAM, 31 I/O terminals, two timers, and a serial communication interface (SCI) are incorporated in the HD6305V0. As a result of CMOS technology, the HD6305V0 consumes much less power than NMOS counterparts. In addition, three low power dissipation modes (stop, wait and standby) which further decreases power consumption, are included in the HD6305V0.

Other notable features include enhanced instruction cycle of the main instructions and the use of three additional instructions to improve system throughput.

#### **■ HARDWARE FEATURES**

- CMOS 8-bit single-chip MCU

- 4096 bytes of ROM

- 192 bytes of RAM

- 31 bidirectional I/O terminals

- Two timers

- 8-bit timer with a 7-bit prescaler (programmable prescaler; event counter)

- 15-bit timer (commonly used with the SCI clock divider)

- On-chip serial interface circuit (synchronized with clock)

- Six interrupts (two external, two timer, one serial and one software)

- Low power dissipation modes

- Wait...... In this mode, the clock oscillator is on and the CPU halts but the timer/serial/interrupt function is operatable. Also, all registers are held, except the I bit in the condition code register is cleared.

- Stop...... In this mode, the clock stops but the RAM data, I/O status and registers are held Except the timer control register (bits 6 and 7) and the I bit of the condition code register.

- Standby.... In this mode, the clock stops, the RAM data is held, and the other internal condition is reset.

- Minimum instruction cycle time

- HD6305V0......1  $\mu$ s (f = 1 MHz)

- HD63A05V0 . . . . 0.67  $\mu$ s (f = 1.5 MHz)

- HD63B05V0.....0.5  $\mu$ s (f = 2 MHz)

- Wide operating range

- $V_{CC} = 3 \text{ to 6V (f} = 0.1 \text{ to 0.5 MHz)}$

- HD6305V0..... f = 0.1 to 1 MHz

- $(V_{CC} = 5V \pm 10\%)$  HD63A05V0 . . . . f = 0.1 to 1.5 MHz

- $(V_{CC} = 5V \pm 10\%)$

- HD63B05V0.....f = 0.1 to 2 MHz

- $(V_{CC} = 5V \pm 10\%)$

- System development fully supported by an emulator

#### **■ SOFTWARE FEATURES**

- Similar to HD6800

- Byte efficient instruction set

- Powerful bit manipulation instructions (Bit Set, Bit Clear, and Bit Test and Branch usable for all RAM bits and all I/O terminals)

- A variety of interrupt operations

- Index addressing mode useful for table processing

- A variety of conditional branch instructions

- Ten powerful addressing modes

- All addressing modes adaptable to RAM, and I/O instructions

- Three new instructions, Stop, Wait and DAA, added to the HD6805 family instruction set

- Compatible instruction set with HD6305X

# **■ PROGRAM DEVELOPMENT SUPPORT TOOLS**

- Cross assembler software for use with IBM PCs and compatibles

- In circuit emulator for use with IBM PCs and compatibles

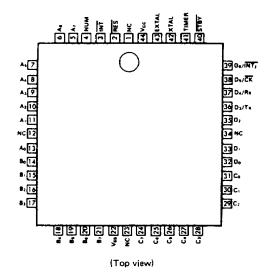

#### ■ PIN ARRANGEMENT

HD6305VOP, HD63A05VOP, HD6305V0F, HD63A05V0F, HD63B05V0P HD63B05V0F 40 Vcc RES 1 0 INT 2 NUM 3 39 EXTAL 38 XTAL 37 TIMER 48 NC 47 B<sub>2</sub> 46 B<sub>2</sub> A7 4 C3 7 36 STBY C2 8 De/INT2 C1 9 34 Ds/CK €₀ [10 45 B1 33 D₄/Rx D<sub>3</sub>/T<sub>x</sub> NC 12 D<sub>2</sub> Dı Do [13 Bo 12 29 0₀ 28 C<sub>0</sub> 27 C<sub>1</sub> 81 B<sub>2</sub> 14 Da: Tx 16 26 B<sub>3</sub> 15 C2 B<sub>4</sub> 16 B<sub>5</sub> 17 B<sub>6</sub> 18 B<sub>7</sub> 19 Vss 20 C3 C4 38 A4 C5 Ds CR 19 Ds./INT2 20 3**5** As 34 NC NC 21 STBY 22 33 🛰 (Top view) INT 29 NUM 30 Š SUB

HD6305V0CP, HD63A05V0CP, HD63B05V0CP

(Top view)

NC pins are not for user application.

Do not connect to any line.

# ■ BLOCK DIAGRAM

# ■ ABSOLUTE MAXIMUM RATINGS

| Item                  | Symbol           | Value                        | Unit     |

|-----------------------|------------------|------------------------------|----------|

| Supply voltage        | Vcc              | -0.3 ~ +7.0                  | V        |

| Input voltage         | Vin              | -0.3 ~ V <sub>CC</sub> + 0.3 | <b>v</b> |

| Operating temperature | Topr             | 0~+70                        | °C       |

| Storage temperature   | T <sub>stg</sub> | <b>−55 ~ +150</b>            | °C       |

[NOTE] These products have a protection circuit in their input terminals against high electrostatic voltage or high electric fields. Notwithstanding, be careful not to apply any voltage higher than the absolute maximum rating to these high input impedance circuits. To assure normal operation, we recommended  $V_{in}$ ,  $V_{out}$ ;  $V_{SS} \leq (V_{in} \text{ or } V_{out}) \leq V_{CC}$ .

# ■ ELECTRICAL CHARACTERISTICS

• DC Characteristics ( $V_{CC}$  = 5.0V  $\pm$  10%,  $V_{SS}$  = GND and  $T_a$  = 0  $\sim$  +70 $^{\circ}$ C unless otherwise specified)

| 1                           | tem                                                                        | Symbol            | Test condition                                    | min                   | typ | max                   | Unit |

|-----------------------------|----------------------------------------------------------------------------|-------------------|---------------------------------------------------|-----------------------|-----|-----------------------|------|

| Input                       | RES, STBY                                                                  |                   |                                                   | V <sub>CC</sub> - 0.5 |     | V <sub>CC</sub> + 0.3 |      |

| voltage                     | EXTAL                                                                      | V <sub>IH</sub>   |                                                   | V <sub>CC</sub> x 0.7 | -   | V <sub>CC</sub> + 0.3 | ٧    |

| "High"                      | Others                                                                     |                   |                                                   | 2.0                   | -   | V <sub>CC</sub> + 0.3 | V    |

| Input volt-<br>age "Low"    | All inputs                                                                 | V <sub>1L</sub>   |                                                   | -0.3                  |     | 0.8                   | V    |

|                             | Operating                                                                  |                   |                                                   | _                     | 5   | 10                    | mA   |

| Current *                   | Wait                                                                       | lcc               | f = 1MHz**                                        | _                     | 2   | 5                     | mA   |

| dissipation                 | Stop                                                                       |                   | 7 - 1141112                                       | _                     | 2   | 10                    | μΑ   |

|                             | Standby                                                                    | 1                 |                                                   | _                     | 2   | 10                    | μΑ   |

| Input<br>leakage<br>current | TIMER,<br>INT,<br>STBY                                                     | H <sub>IL</sub> ! |                                                   |                       | _   | 1                     | μΑ   |

| Three-<br>state<br>current  | $A_0 \sim A_7$ ,<br>$B_0 \sim B_7$ ,<br>$C_0 \sim C_7$ ,<br>$D_0 \sim D_6$ | <sup> </sup>  TSi | V <sub>in</sub> = 0.5 ~<br>V <sub>CC</sub> - 0.5V | _                     | _   | 1                     | μΑ   |

| Input capacity              | All<br>terminals                                                           | C <sub>in</sub>   | f = 1MHz,<br>V <sub>in</sub> = 0V                 | -                     | -   | 12                    | pF   |

<sup>\*</sup> All output and RES terminal are open. (V<sub>IH</sub> min = V<sub>CC</sub> - 1.0V, V<sub>IL</sub> max = 0.8V), are penetrate current of input are not included.

\*\*The value at f = xMHz can be calculated by the following equation: I<sub>CC</sub> (f = xMHz) = I<sub>CC</sub> (f = 1MHz) multiplied by x x

# $\bullet$ AC Characteristics (V<sub>CC</sub> = 5.0V $\pm$ 10%, V<sub>SS</sub> = GND and T<sub>a</sub> = 0 $\sim$ +70°C unless otherwise specified)

| _                                |                   | Test                                       | н                        | D6305V | 0   | HD                         | 63A05V | 0   | HD                       | 63B05\ | 0   | Unit             |

|----------------------------------|-------------------|--------------------------------------------|--------------------------|--------|-----|----------------------------|--------|-----|--------------------------|--------|-----|------------------|

| ltem                             | Symbol            | condition                                  | min                      | typ    | max | min                        | typ    | max | min                      | typ    | max | Oiiit            |

| Clock<br>frequency               | f <sub>cl</sub>   |                                            | 0.4                      | -      | 4   | 0.4                        | _      | 6   | 0.4                      | _      | 8   | MHz              |

| Cycle time                       | t <sub>cyc</sub>  |                                            | 1.0                      | _      | 10  | 0.666                      | _      | 10  | 0.5                      | _      | 10  | μs               |

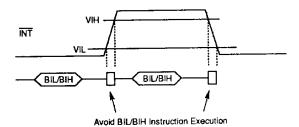

| INT pulse<br>width               | tiwL              |                                            | t <sub>cyc</sub><br>+250 | -      | -   | t <sub>cyc</sub><br>+200   | -      | _   | t <sub>cyc</sub><br>+200 | -      | _   | ns               |

| INT2 pulse<br>width              | t <sub>IWL2</sub> |                                            | t <sub>cyc</sub><br>+250 | _      | -   | t <sub>cyc</sub><br>+200   | -      | _   | t <sub>cyc</sub><br>+200 | 1      | _   | ns               |

| RES pulse<br>width               | tRWL              |                                            | 5                        |        | -   | 5                          | -      | -   | 5                        | +      | _   | t <sub>cyc</sub> |

| TIMER pulse width                | <sup>t</sup> TWL  |                                            | t <sub>cyc</sub><br>+250 | _      | _   | t <sub>cyc</sub> .<br>+200 | _      | _   | t <sub>cyc</sub><br>+200 | +      | _   | ns               |

| Oscillation start time (crystal) | tosc              | $C_L = 22pF \pm 20\%$ $R_s = 60\Omega$ max | _                        | -      | 20  | _                          | _      | 20  | _                        | _      | 20  | ms               |

| Reset delay time                 | t <sub>RHL</sub>  | External cap.<br>2.2µF                     | 80                       | -      | -   | 80                         | _      | -   | 80                       | -      | -   | ms               |

# ullet Port Electrical Characteristics (V<sub>CC</sub> = 5.0V $\pm$ 10%, V<sub>SS</sub> = GND and T<sub>a</sub> = 0 $\sim$ +70°C unless otherwise specified)

| Ite                        | m                   | Symbol          | Test<br>condition                                 | min                   | typ | max                   | Unit |

|----------------------------|---------------------|-----------------|---------------------------------------------------|-----------------------|-----|-----------------------|------|

| Output volt-               |                     |                 | I <sub>OH</sub> = -200μA                          | 2,4                   | _   | -                     | ٧    |

| age "High"                 | Ports A,            | Voн             | I <sub>OH</sub> = -10μA                           | V <sub>CC</sub> - 0.7 | _   | -                     | V    |

| Output volt-<br>age "Low"  | В, С, D             | VoL             | I <sub>OL</sub> = 1.6mA                           | -                     | _   | 0.55                  | V    |

| Input volt-<br>age "High"  |                     | V <sub>1H</sub> |                                                   | 2.0                   | _   | V <sub>CC</sub> + 0.3 | ٧    |

| Input volt-<br>age "Low"   | Ports A,<br>B, C, D | V <sub>1L</sub> |                                                   | - 0.3                 | _   | 0.8                   | V    |

| Input leak-<br>age current |                     | البدا           | V <sub>in</sub> = 0.5 ~<br>V <sub>CC</sub> - 0.5V |                       | _   | 1                     | μΑ   |

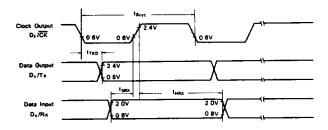

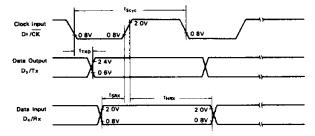

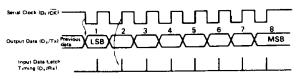

# • SCI Timing ( $V_{CC}$ = 5.0V±10%, $V_{SS}$ = GND and Ta = 0 $\sim$ +70°C unless otherwise specified)

|                        | Sumb al          | Test        | Н   | D6305 | V0    | HD   | 63A05 | vo    | НΩ  | 63B05 | V0       | Unit |

|------------------------|------------------|-------------|-----|-------|-------|------|-------|-------|-----|-------|----------|------|

| item                   | Symbol           | Condition   | min | typ   | max   | min  | typ   | max   | min | typ   | max      | •    |

| Clock Cycle            | tScyc            |             | 1   |       | 32768 | 0.67 | -     | 21845 | 0.5 |       | 16384    | μs   |

| Data Output Delay Time | t <sub>TXD</sub> | 1<br>Fig. 1 | _   | +     | 250   | -    | _     | 250   |     | -     | 250      | ns   |

| Data Set-up Time       | tsrx             | Fig. 2      | 200 | -     | -     | 200  | _     |       | 200 | _     | <u> </u> | ns   |

| Data Hold Time         | tHRX             | 1           | 100 | _     |       | 100  |       |       | 100 |       | -        | ns   |

Figure 1 SCI Timing (Internal Clock)

Figure 2 SCI Timing (External Clock)

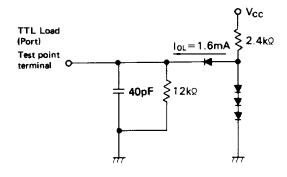

[NOTES] 1. The load capacitance includes stray capacitance caused by the probe, etc.

2. All diodes are 1S2074 (H)

Figure 3 Test Load

#### **■ DESCRIPTION OF TERMINAL FUNCTIONS**

The input and output signals of the HD6305V0 are described here.

#### V<sub>CC</sub>, V<sub>SS</sub>

Voltage is applied to the HD6305V0 through these two terminals.  $V_{CC}$  is 5.0V  $\pm$  10%, while  $V_{SS}$  is grounded.

#### INT, INT<sub>2</sub>

External interrupt request inputs to the HD6305V0. For details, refer to "INTERRUPTS". The  $\overline{INT_2}$  terminal is also used as the port  $D_6$  terminal.

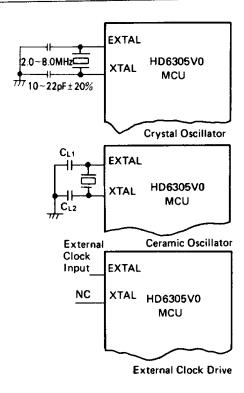

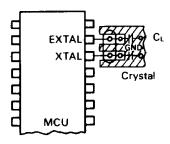

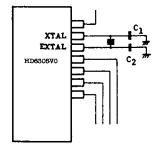

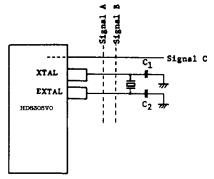

#### XTAL, EXTAL

These terminals provide input to the on-chip clock circuit. A crystal oscillator (AT cut, 2.0 to 8.0 MHz) or ceramic filter is connected to the terminal. Refer to "INTERNAL OSCILLATOR" for using these input terminals.

#### • TIMER

This is an input terminal for event counter. Refer to "TIMER" for details.

#### • RES

Used to reset the MCU. Refer to "RESET" for details.

#### NUM

This terminal is not intended for user applications. It must be grounded to  $V_{\rm SS}$ .

# Input/Output Terminals (A<sub>0</sub> ~ A<sub>7</sub>, B<sub>0</sub> ~ B<sub>7</sub>, C<sub>0</sub> ~ C<sub>7</sub>, D<sub>0</sub> ~ D<sub>.1</sub>

These 31 terminals consist of three 8-bit I/O ports (A, B and C) and a 7-bit I/O port D. Each of these can be used as an input or output terminal on a bit basis through program control of the data direction register (DDR). For details, refer to "I/O PORTS."

Since port  $D_6$  is also used for the  $\overline{INT_2}$  input, in order to use port  $D_6$  as an I/O port, the  $\overline{INT_2}$  interrupt mask bit in the miscellaneous register should be set to "1" to disable the  $\overline{INT_2}$  input.

#### • STBY

This terminal is used to place the MCU into the standby mode. With STBY at "Low" level, the oscillation stops and the internal condition is reset. For details, refer to "STANDBY MODE."

The terminals described in the following are I/O pins for serial communication interface (SCI). They are also used as ports  $D_3$ ,  $D_4$  and  $D_5$ . For details, refer to "SERIAL COMMUNICATION INTERFACE."

# • CK (D,)

Used to input or output clocks for serial operation.

#### Rx (D<sub>4</sub>)

Used to receive serial data.

#### • Tx (D<sub>2</sub>)

Used to transmit serial data.

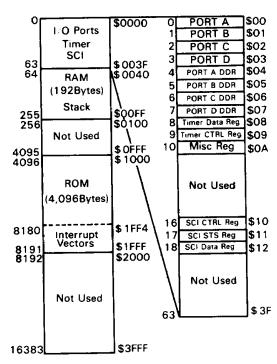

#### **MEMORY MAP**

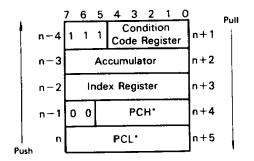

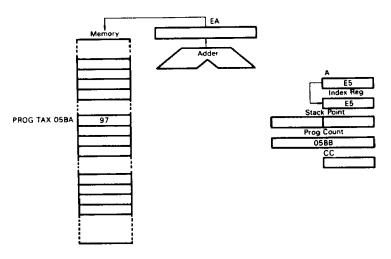

The memory map of the HD6305V0 MCU is shown in Fig. 4. During interrupt processing, the contents of the MCU registers are saved into the stack in the sequence shown in Fig. 5. This saving begins with the lower byte (PCL) of the program counter. Then the value of the stack pointer is decremented and the higher byte (PCH) of the program counter, index register (X), accumulator (A) and condition code register (CCR) are stacked in that order. In a subroutine call, only the contents of the program counter (PCH and PCL) are stacked.

Figure 4 Memory Map of HD6305V0 MCU

In a subroutine call, only PCL and PCH are stacked.

Figure 5 Sequence of Interrupt Stacking

#### ■ REGISTERS

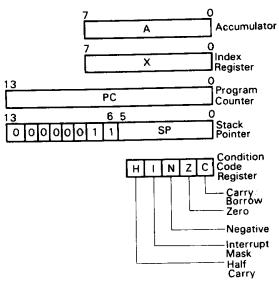

There are five registers which the programmer can operate.

#### Accumulator (A)

This accumulator is a general purpose 8-bit register which holds operands or the result of arithmetic operation or data processing.

# Index Register (X)

The index register is an 8-bit register, and is used for index addressing mode. Each of the addresses contained in the register consists of 8 bits which, combined with an offset value, provides an effective address.

In the case of a read/modify/write instruction, the index register can be used like an accumulator to hold operation data or the result of operation.

If not used in the index addressing mode, the register can be used to store data temporarily.

Figure 6 Programming Model

# Program Counter (PC)

The program counter is a 14-bit register that contains the address of the next instruction to be executed.

#### Stack Pointer (SP)

The stack pointer is a 14-bit register that indicates the address of the next stacking space. Just after reset, the stack pointer is set at address \$00FF. It is decremented when data is pushed, and incremented when pulled. The upper 8 bits of the stack pointer are fixed to 00000011. During the MCU being reset or during a reset stack pointer (RSP) instruction, the pointer is set to address \$00FF. Since a subroutine or interrupt can use space up to address \$00C1 for stacking, the subroutine can be used up to 31 levels and the interrupt up to 12 levels.

#### • Condition Code Register (CCR)

The condition code register is a 5-bit register, each bit indicating the result of the instruction just executed. The bits can be individually tested by conditional branch instructions. The CCR bits are as follows:

Half Carry (H): Used to indicate that a carry occurred between bits 3 and 4 during an arithmetic operation

(ADD, ADC).

Interrupt (I): Setting this bit causes all interrupts, except a software interrupt, to be masked. If an interrupt occurs with the bit I set, it is latched. It will be processed the instant the interrupt mask bit is reset. (More specifically, it will enter the interrupt processing routine after the instruction following the CLI has been executed.)

Negative (N): Used to indicate that the result of the most recent arithmetic operation, logical operation or data processing is negative (bit 7 is logic "1").

Zero (Z): Used to indicate that the result of the most recent arithmetic operation, logical operation or data processing is zero.

Carry/ Represents a carry or borrow that occurred in Borrow (C): the most recent arithmetic operation. This bit is

also affected by the Bit Test and Branch instruction, a shift instruction and a Rotate instruction.

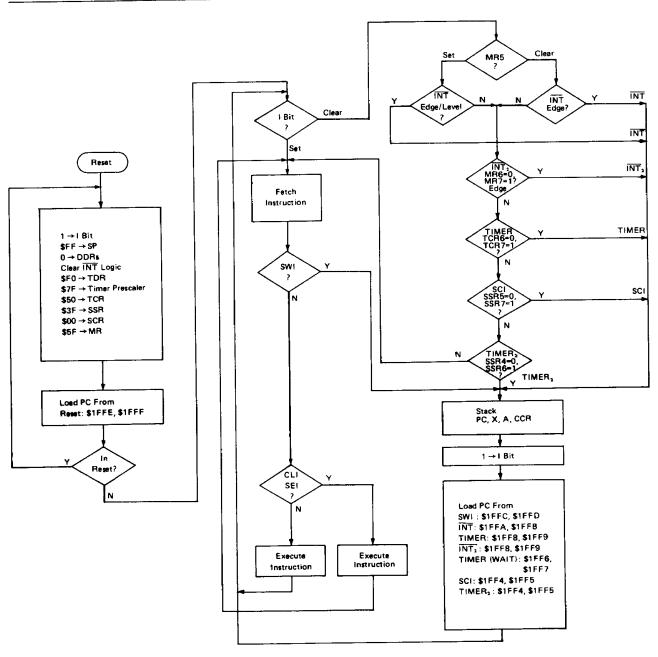

#### **■ INTERRUPT**

There are six different types of interrupt: external interrupts  $(\overline{INT}, \overline{INT_2})$ , internal timer interrupts  $(TIMER, TIMER_2)$ , serial

interrupt (SCI) and interrupt by an instruction (SWI).

Of these six interrupts, the  $\overline{INT_2}$  and TIMER or the SCI and TIMER<sub>2</sub> generate the same vector address, respectively. Although, a different vector address is generated for a timer interrupt during the wait mode, as shown in Table 1.

When an interrupt occurs, the program in progress stops and then the CPU status is saved onto the stack. And then, the interrupt mask bit (I) of the condition code register is set and the start address of the interrupt processing routine is obtained from a particular interrupt vector address. Then the interrupt routine starts from the start address. System can exit from the interrupt routine by a RTI instruction. When this instruction is executed, the CPU status before the interrupt (saved onto the stack) is pulled and the CPU restarts the sequence with the instruction next to the one at which the interrupt occurred. Table 1 lists the priority of interrupts and their vector addresses.

Table 1 Priority of Interrupts

| Priority | Interrupt    | Vector  | Address |

|----------|--------------|---------|---------|

| 1        | ŘES          | \$1FFE, | \$1FFF  |

| 2        | SWI          | \$1FFC, | \$1FFD  |

| 3        | ĪNT          | \$1FFA, | \$1FFB  |

| 4        | TIMER/INT2   | \$1FF8, | \$1FF9  |

| 5        | TIMER (WAIT) | \$1FF6, | \$1FF7  |

| 6        | SCI/TIMER2   | \$1FF4, | \$1FF5  |

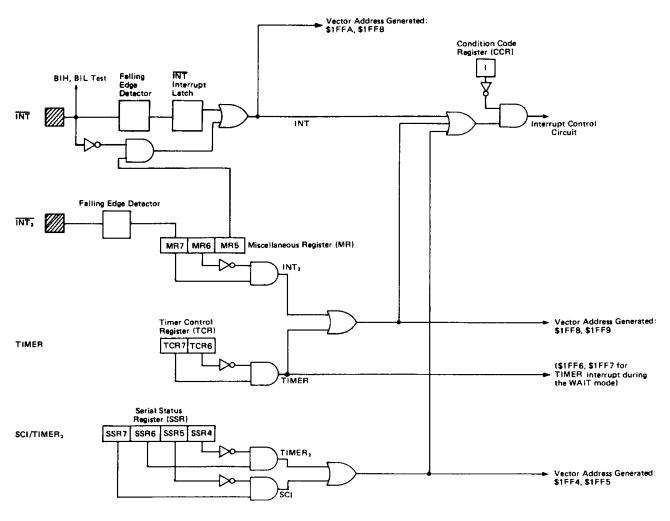

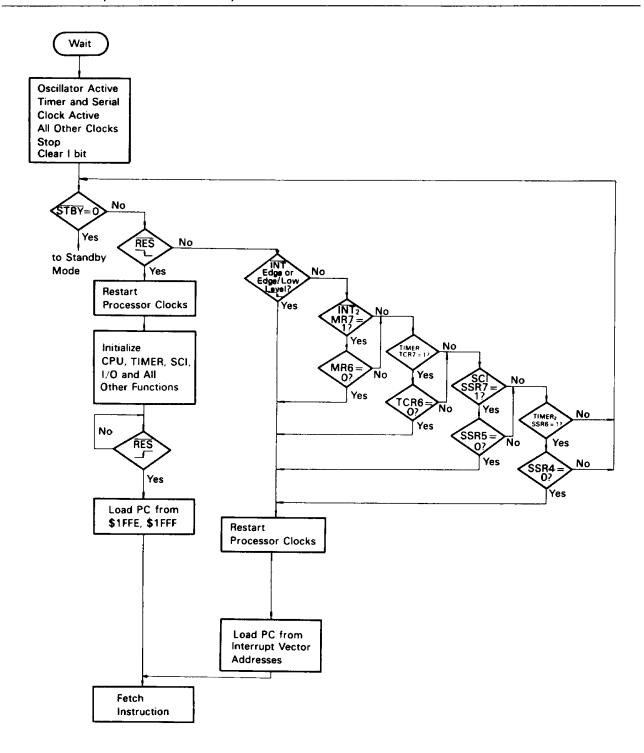

A flowchart of the interrupt sequence is shown in Fig. 7. A block diagram of the interrupt request source is shown in Fig. 8.

In the block diagram of Fig. 8, the external interrupt  $\overline{INT_2}$  is a falling edge trigger input, whereas, the external interrupt  $\overline{INT}$  can be configured as a falling edge trigger input or a combination of falling edge and low level trigger input, depending on the status of bit 5 in the miscellaneous register (MR). When an interrupt request is detected at the  $\overline{INT_2}$  or  $\overline{INT}$  inputs, an interrupt request is generated and latched. The  $\overline{INT}$  interrupt request is automatically cleared if jumping is made to the  $\overline{INT}$  processing routine. Meanwhile, the  $\overline{INT_2}$  request is cleared if "0" is written in bit 7 of the miscellaneous register.

For the external interrupts (INT, INT<sub>2</sub>), internal timer interrupts (TIMER, TIMER<sub>2</sub>) and serial interrupt (SCI), each interrupt request is held, but not processed, if the I bit of the condition code register is set. Immediately after the I bit is cleared, the

corresponding interrupt processing starts according to the priority.

The  $\overline{INT_2}$  interrupt can be masked by setting bit 6 of the miscellaneous register; the TIMER interrupt by setting bit 6 of the timer control register; the SCI interrupt by setting bit 5 of the serial status register; and the TIMER<sub>2</sub> interrupt by setting bit 4 of the serial status register.

The status of the  $\overline{\text{INT}}$  terminal can be tested by a BIL or BIH instruction. The  $\overline{\text{INT}}$  falling edge and falling edge/low level detector circuit and its latching circuit are independent of testing by these instructions. This is also true with the status of the  $\overline{\text{INT}}_2$  terminal.

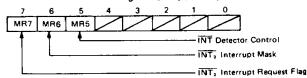

#### Miscellaneous Register (MR; \$000A)

The external interrupt  $\overline{INT_2}$  and the TIMER interrupt have identical interrupt vector addresses, as shown in Table 1. For this reason, bits 6 and 7 of a special register called the miscellaneous register (MR: \$000A) are available to control the  $\overline{INT_2}$  interrupt. Moreover, bit 5 of the MR controls the sensing mode for the  $\overline{INT}$  interrupt detector (falling edge detector or falling edge/low level detector).

Bit 7 of the MR is the  $\overline{INT_2}$  interrupt request flag. When a falling edge is detected at the  $\overline{INT_2}$  terminal, bit 7 is set to "1" Then the interrupt routine software (vector addresses: \$1FF8, \$1FF9) checks bit 7 to see if an  $\overline{INT_2}$  interrupt occurred. Bit 7 can be reset by software.

Miscellaneous Register (MR; \$000A)

Bit 6 is the  $\overline{INT_2}$  interrupt mask bit. If this bit is set to "1", then the  $\overline{INT_2}$  interrupt is disabled. Both read and write are possible with bit 7, but "1" cannot be written in this bit by software. In other words, an  $\overline{INT_2}$  interrupt request by software is not possible

Bit 5 is the control bit for  $\overline{\text{INT}}$  interrupt detection. If this bit is reset to "0", the detection logic will detect a falling edge. When this bit is set to "1", the detection logic will detect a falling edge or a low level

When reset, bit 7 is cleared to "0", bit 6 is set to "1" and bit 5 is cleared to "0".

Figure 7 Interrupt Flowchart

Figure 8 Interrupt Request Generation Circuitry

# **TIMER**

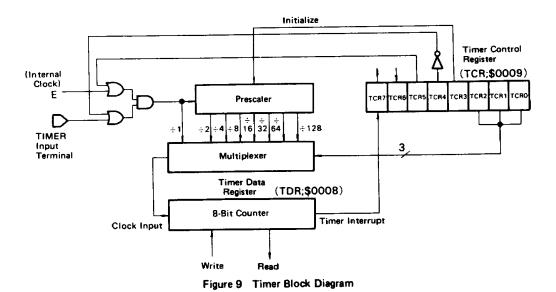

Figure 9 shows an MCU timer block diagram. The timer data register is loaded by software and, upon receipt of a clock input, begins to count down. When the timer data register (TDR) becomes "0", the timer interrupt request bit (bit 7) in the timer control register is set. In response to the interrupt request, the MCU saves its status into the stack and fetches the timer interrupt routine addresses \$1FF8 and \$1FF9 (or \$1FF6 and \$1FF7 when the timer interrupt occures during the wait mode) and executes the interrupt routine. The timer interrupt can be masked by setting the timer interrupt mask bit (bit 6) in the timer control register. The mask bit (1) in the condition code register can also mask the timer interrupt.

The source clock to the timer can be either an external signal from the timer input terminal or the internal E signal (the oscillator clock divided by 4). If the E signal is used as the source, the clock input can be gated by the input to the timer input terminal.

Once the timer count has reached 0, it starts counting down with "FF". The count can be monitored whenever desired by reading the timer data register. This permits the program to know the length of time having passed after the occurrence of a timer interrupt, without disturbing the contents of the counter.

When the MCU is reset or placed in the stop mode, the timer data register (TDR) is initialized to \$F0. The timer interrupt re-

quest bit (bit 7) then is cleared and the timer interrupt mask bit (bit 6) is set.

To clear the timer interrupt request bit (bit 7), it is necessary to write "0" in that bit.

| TCR7 | Timer interrupt reques |

|------|------------------------|

| 0    | Absent                 |

| 1    | Present                |

| TCR6 | Timer interrupt mask   |

| _    | Enabled                |

| v    | 2.140.04               |

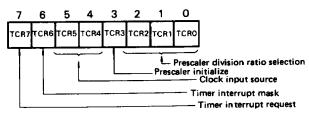

# • Timer Control Register (TCR; \$0009)

Selection of a clock source, selection of a prescaler frequency division ratio, and a timer interrupt can be controlled by the timer control register (TCR; \$0009).

For the selection of a clock source, any one of the four modes (see Table 2) can be selected by bits 5 and 4 of the timer control register (TCR).

## Timer Control Register (TCR; \$0009)

After reset, the TCR is initialized to "E under timer terminal control" (bit 5=0, bit 4=1). If the timer terminal is "1", the counter starts counting down with "\$F0" immediately after reset.

When "1" is written in bit 3, the prescaler is initialized to "\$7F". This bit always shows "0" when read.

Table 2 Clock Source Selection

| TC    | R     | Clock input source                |

|-------|-------|-----------------------------------|

| Bit 5 | Bit 4 | Clock input source                |

| 0     | 0     | Internal clock E                  |

| 0     | 1     | E under TIMER terminal control    |

| 1     | 0     | No clock input (counting stopped) |

| 1     | 1     | Event input from TIMER terminal   |

A prescaler division ratio is selected by the combination of three bits (bits 0, 1 and 2) of the timer control register (see Table 3). There are eight different division ratios: +1, +2, +4, +8, +16, +32, +64 and +128. After reset, the TCR is set to the +1 mode.

Table 3 Prescaler Division Ratio Selection

|       | TCR   |       |                          |

|-------|-------|-------|--------------------------|

| Bit 2 | Bit 1 | Bit 0 | Prescaler division ratio |

| 0     | 0     | 0     | ÷1                       |

| 0     | 0     | 1     | ÷2                       |

| 0     | 1     | 0     | ÷4                       |

| 0     | 1     | 1     | ÷8                       |

| 1     | 0     | 0     | ÷16                      |

| 1     | 0     | 1     | ÷32                      |

| 1     | 1     | 0     | ÷64                      |

| 1     | 1     | 1     | ÷128                     |

A timer interrupt is enabled when the timer interrupt mask

bit is "0", and disabled when the bit is "1". When a timer inter-

rupt occurs, "1" is set in the timer interrupt request bit. This bit can be cleared by writing "0" in that bit.

#### ■ SERIAL COMMUNICATION INTERFACE (SCI)

This interface is used for serial transmission or reception of 8-bit data. Sixteen transfer rates are available in the range from 1  $\mu$ s to approx. 32 ms (for oscillation at 4 MHz).

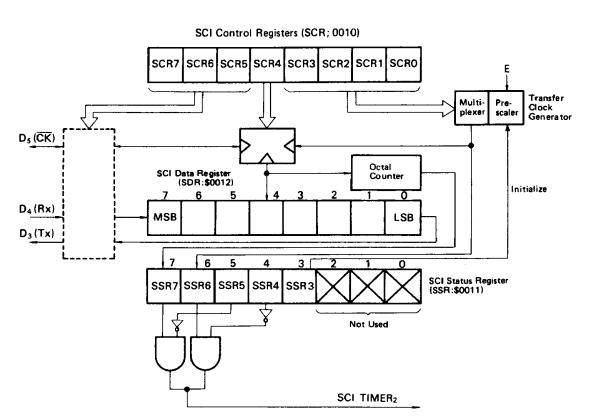

The SCI consists of three registers, one octal counter and one prescaler. (See Fig. 10.) SCI communicates with the CPU via the data bus, and with the outside world through bits 3, 4 and 5 of port D. Described below are the operations of each reg-

ister and data transfer.

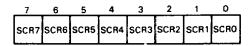

#### • SCI Control Register (SCR; \$0010)

Figure 10 SCI Block Diagram

| sc   | :R7  | D <sub>3</sub> terminal       |                           |  |  |  |

|------|------|-------------------------------|---------------------------|--|--|--|

|      | 0    | Used as I/O terminal (by DDR) |                           |  |  |  |

|      | 1    | Serial data out               | put (DDR output)          |  |  |  |

| SC   | R6   |                               | D <sub>4</sub> terminal   |  |  |  |

| (    | ,    | Used as I/O terminal (by DDR) |                           |  |  |  |

| -    | 1    | Serial data inp               | ut (DDR input)            |  |  |  |

| SCR5 | SCR4 | Clock source                  | D <sub>5</sub> terminal   |  |  |  |

| 0    | 0    | _                             | Used as I/O terminal (by  |  |  |  |

| 0    | 1    | _                             | DDR)                      |  |  |  |

| 1    | 0    | Internal                      | Clock output (DDR output) |  |  |  |

| 1    | 1    | External                      | Clock input (DDR input)   |  |  |  |

#### Bit 7 (SCR7)

When this bit is set, the DDR corresponding to the  $D_3$  becomes "1" and this terminal serves for output of SCI data. After reset, the bit is cleared to "0".

#### Bit 6 (SCR6)

When this bit is set, the DDR corresponding to the  $D_4$  becomes "0" and this terminal serves for input of SCI data. After reset, the bit is cleared to "0".

# Bits 5 and 4 (SCR5, SCR4)

These bits are used to select a clock source. After reset, the bits are cleared to "0".

#### Bits $3 \sim 0$ (SCR3 $\sim$ SCR0)

These bits are used to select a transfer clock rate. After reset, the bits are cleared to "0".

|      |      | 2004 | cono | Transfer | clock rate |

|------|------|------|------|----------|------------|

| SCR3 | SCR2 | SCR1 | SCR0 | 4.00 MHz | 4.194 MHz  |

| 0    | 0    | 0    | 0    | 1 μs     | 0.95 μs    |

| 0    | 0    | 0    | 1    | 2 μs     | 1.91 µs    |

| 0    | 0    | 1    | О    | 4 μs     | 3.82 µs    |

| 0    | 0    | 1    | 1    | 8 μs     | 7.64 µs    |

| ₹    |      | . ≀  | ₹    | ₹ .      | . ₹        |

| 1    | 1    | 1    | 1    | 32768 µs | 1/32 s     |

# SCI Data Register (SDR; \$0012)

A serial-parallel conversion register that is used for transfer of data.

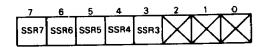

# • SCI Status Register (SSR; \$0011)

#### Bit 7 (SSR7)

Bit 7 is the SCI interrupt request bit which is set upon completion of transmitting or receiving 8-bit data. It is cleared when reset or data is written to or read from the SCI data register with the SCR5 = "1". The bit can also be cleared by writing "0" in it

#### Bit 6 (SSR6)

Bit 6 is the TIMER<sub>2</sub> interrupt request bit. TIMER<sub>2</sub> is used commonly with the serial clock generator, and SSR6 is set each time the internal transfer clock falls. When reset, the bit is cleared. It also be cleared by writing "0" in it. (For details, see TIMER<sub>2</sub>.)

## Bit 5 (SSR5)

Bit 5 is the SCI interrupt mask bit which can be set or cleared by software. When it is "1", the SCI interrupt (SSR7) is masked. When reset, it is set to "1".

| SSR7 | SCI interrupt request                |  |  |  |

|------|--------------------------------------|--|--|--|

| 0    | Absent                               |  |  |  |

| 1    | Present                              |  |  |  |

| SSR6 | TIMER <sub>2</sub> interrupt request |  |  |  |

| 0    | Absent                               |  |  |  |

| 1    | Present                              |  |  |  |

| SSR5 | SCI interrupt mask                   |  |  |  |

| 0    | Enabled                              |  |  |  |

| 1    | Disabled                             |  |  |  |

| SSR4 | TIMER <sub>2</sub> interrupt mask    |  |  |  |

|      |                                      |  |  |  |

| 0    | Enabled                              |  |  |  |

#### Bit 4 (SSR4)

Bit 4 is the TIMER<sub>2</sub> interrupt mask bit which can be set or cleared by software. When the bit is "1", the TIMER<sub>2</sub> interrupt (SSR6) is masked. When reset, it is set to "1".

# Bit 3 (SSR3)

When "1" is written in this bit, the prescaler of the transfer clock generator is initialized. When read, the bit always is "0".

Bits  $2 \sim 0$ Not used.

#### Data Transmission

By writing the desired control bits into the SCI control registers, a transfer rate and a source of transfer clock are determined and bits 3 and 5 of port D are set at the serial data output terminal and the serial clock terminal, respectively. The transmit data should be stored from the accumulator or index register into the SCI data register. The data written in the SCI data register is output from the D<sub>3</sub>/Tx terminal, starting with the LSB, synchronously with the falling edge of the serial clock. (See Fig. 11.) When 8 bits of data have been transmitted, the interrupt request bit is set in bit 7 of the SCI status register. This request can be masked by setting bit 5 of the SCI status register. Once the data has been sent, the 8th bit data (MSB) stays at the D<sub>3</sub>/Tx terminal. If an external clock source has been selected, the transfer rate determined by bits  $0 \sim 3$  of the SCI control register is ignored, and the D<sub>s</sub>/CK terminal is set as input. If the internal clock has been selected, the D<sub>5</sub>/CK terminal is set as output and clocks are output at the transfer rate selected by bits  $0 \sim 3$  of the SCI control register.

Figure 11 SCI Timing Chart

## Data Reception

By writing the desired control bits into the SCI control register, a transfer rate and a source of transfer clock are determined and bits 4 and 5 of Port D are set at the serial data input terminal and the serial clock terminal, respectively. Then dummy-writing or -reading the SCI data register, the system is ready for receiving data. (This procedure is not needed for the second and subsequent data receptions. It must be taken only after resetting.)

The data from the  $D_4/Rx$  terminal is input to the SCI data register synchronously with the leading edge of the serial clock (see Fig. 11). When 8 bits of data have been received, the interrupt request bit is set in bit 7 of the SCI status register. This request can be masked by setting bit 5 of the SCI status register. If an external clock source have been selected, the transfer rate determined by bits  $0 \sim 3$  of the SCI control register is ignored and the data is received synchronously with the clock from the  $D_4/\overline{CK}$  terminal. If the internal clock has been selected, the  $D_4/\overline{CK}$  terminal is set as output and clocks are output at the transfer rate selected by bits  $0 \sim 3$  of the SCI control register.

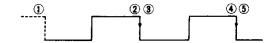

#### • TIMER

The SCI transfer clock generator can be used as a timer. The clock selected by bits  $3 \sim 0$  of the SCI control register (4  $\mu$ s  $\sim$  approx. 32 ms (for oscillation at 4 MHz)) is input to bit 6 of the SCI status register and the TIMER<sub>2</sub> interrupt request bit is set at each falling edge of the clock. Since interrupt requests occur periodically, TIMER<sub>2</sub> can be used as a reload counter or clock.

- :Transfer clock generator is reset and mask bit (bit 4 of SCI status register) is cleared.

- 2, 4 : TIMER2 interrupt request

- (3), (5) : TIMER2 interrupt request bit cleared

TIMER<sub>2</sub> is commonly used with the SCI transfer clock generator. If wanting to use  $TIMER_2$  independently of the SCI, specify "External" (SCR5 = 1, SCR4 = 1) as the SCI clock source.

If "Internal" is selected as the clock source, reading or writing the SDR causes the prescaler of the transfer clock generator to be initialized.

#### ■ I/O PORTS

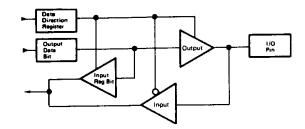

There are 31 input/output terminals (ports A, B, C, D). Each I/O terminal can be selected for either input or output by the data direction register. More specifically, an I/O port will be input if "0" is written in the data direction register, and output if "1" is written in the data direction register. Port A, B, C or D reads latched data if it has been programmed as output, even with the output level being fluctuated by the output load. (See Fig. 12.)

When reset, the data direction register goes "0" and all the input/output terminals are used as input.

| Bit of data<br>direction<br>register | Bit of output data | Status of output | Input to<br>CPU |

|--------------------------------------|--------------------|------------------|-----------------|

| 1                                    | 0                  | 0                | 0               |

| 1                                    | 1                  | 1                | 1               |

| 0                                    | Х                  | 3-state          | Pin             |

Figure 12 Input/Output Port (Ports A, B, C and D) Diagram

All input/output terminals are TTL compatible and CMOS compatible in respect of both input and output.

If I/O ports are not used, they should be connected to V<sub>SS</sub> via resistors. With none connected to these terminals, there is the possibility of power being consumed despite that they are not used.

#### ■ RESET

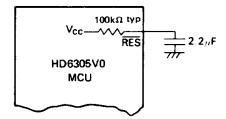

The MCU can be reset either by external reset input ( $\overline{RES}$ ) or power-on reset. (See Fig. 13.) On power up, the reset input must be held "Low" for at least  $t_{OSC}$  to assure that the internal oscillator is stabilized. A sufficient time of delay can be obtained by connecting a capacitance to the  $\overline{RES}$  input as shown in Fig. 14.

Figure 13 Power On and Reset Timing

Figure 14 Input Reset Delay Circuit

#### ■ INTERNAL OSCILLATOR

The internal oscillator circuit is designed to meet the requirement for minimum external configurations. It can be driven by connecting a crystal (AT cut  $2.0 \sim 8.0$  MHz) or ceramic oscillator between EXTAL and XTAL pins depending on the required oscillation frequency stability.

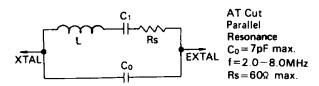

Three different terminal connections are shown in Fig. 15. Figs. 16 and 17 illustrate the specifications and typical arrangement of the crystal, respectively.

Figure 15 Internal Oscillator Circuit

Figure 16 Parameters of Crystal

[NOTE] Use as short wirings as possible for connection of the crystal with the EXTAL and XTAL terminals. Do not allow these wirings to cross others.

Figure 17 Typical Crystal Arrangement

# ■ LOW POWER DISSIPATION MODE

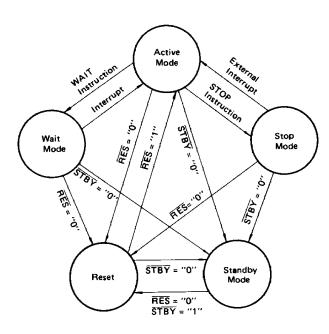

The HD6305V0 has three low power dissipation modes: wait, stop and standby.

#### Wait Mode

When WAIT instruction being executed, the MCU enters into the wait mode. In this mode, the oscillator stays active but the internal clock stops. The CPU stops but the peripheral functions— the timer and the serial communication interface—stay active. (NOTE: Once the system has entered the wait mode, the serial communication interface can no longer be retriggered.) In the wait mode, the registers (except the 1 bit of the condition code register which is cleared), RAM and I/O terminals hold their condition just before entering into the wait mode.

The escape from this mode can be done by interrupt (INT, TIMER/INT<sub>2</sub> or SCI/TIMER<sub>2</sub>), RES or STBY. The RES resets the MCU and the STBY brings it into the standby mode. (This will be mentioned later.)

When interrupt is requested to the CPU and accepted, the wait mode escapes, then the CPU is brought to the operation mode and vectors to the interrupt routine. If an interrupt other than the INT (i.e., TIMER/INT<sub>2</sub> or SCI/TIMER<sub>2</sub>) is masked by the timer control register, miscellaneous register or serial status register, there is no interrupt request to the CPU, so the wait mode cannot be released.

Fig. 18 shows a flowchart for the wait function.

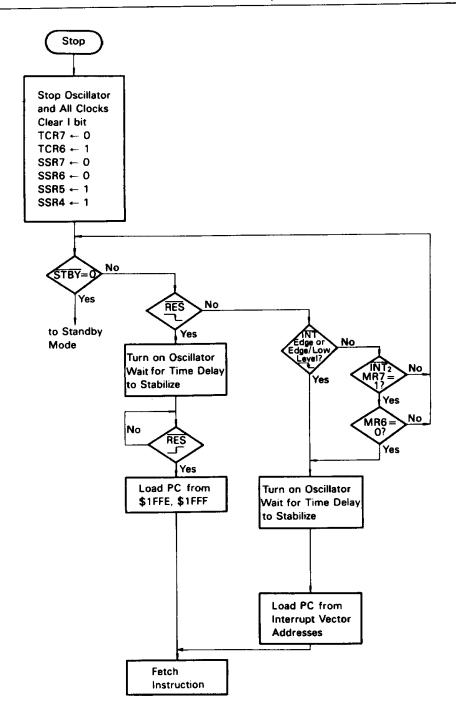

#### Stop Mode

When STOP instruction being executed, MCU enters into the stop mode. In this mode, the oscillator stops and the CPU and peripheral functions become inactive, but the RAM, registers (except bits 6 and 7 of the timer control register and the 1 bit of the condition code register) and I/O terminals hold their condition just before entering the stop mode. Bits 6 and 7 of the timer control register are initialized to "1" and "0", bits 7, 6, 5 and 4 of SCI status register are initialized "0", "0", "1", "1", respectively, and the 1 bit of the condition code register is cleared.

The escape from this mode can be done by an external interrupt ( $\overline{INT}$  or  $\overline{INT}_2$ ),  $\overline{RES}$  or  $\overline{STBY}$ . The  $\overline{RES}$  resets the MCU and the  $\overline{STBY}$  brings into the standby mode.

When interrupt is requested to the CPU and accepted, the stop mode escapes, then the CPU is brought to the operation mode and vectors to the interrupt routine. If the  $\overline{INT_2}$  interrupt is masked by the miscellaneous register, there is no interrupt request to the MCU, so the stop mode cannot be released.

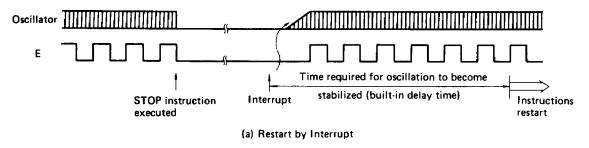

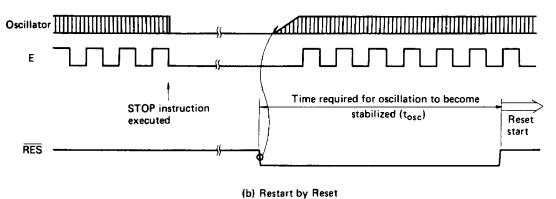

Fig. 19 shows a flowchart for the stop function. Fig. 20 shows a timing chart of return to the operation mode from the stop mode.

For releasing from the stop mode by an interrupt, oscillation starts upon input of the interrupt and, after the internal delay time for stabilized oscillation, the CPU becomes active. For restarting by  $\overline{RES}$ , oscillation starts when the  $\overline{RES}$  goes "0" and the CPU restarts when the  $\overline{RES}$  goes "1". The duration of  $\overline{RES}$  = "0" must exceed  $t_{osc}$  to assure stabilized oscillation.

# Standby Mode

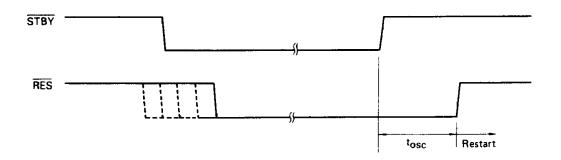

The MCU enters into the standby mode when the STBY terminal goes "Low". In this mode, all operations stop and the internal condition is reset but the contents of the RAM are hold. The I/O terminals turn to high-impedance state. The standby mode should escape by bringing STBY "High". The CPU must be restarted by reset. The timing of input signals at the RES and STBY terminals is shown in Fig. 21.

Table 4 lists the status of each parts of the MCU in each low power dissipation modes. Transitions between each mode are shown in Fig. 22.

Figure 18 Wait Mode Flowchart

Figure 19 Stop Mode Flowchart

Figure 20 Timing Chart of Releasing from Stop Mode

Figure 21 Timing Chart of Releasing from Standby Mode

Table 4 Status of Each Part of MCU in Low Power Dissipation Modes

|              |                                                        |            |                 |      | Co               | ndition   |      |                     |                                                                                                    |

|--------------|--------------------------------------------------------|------------|-----------------|------|------------------|-----------|------|---------------------|----------------------------------------------------------------------------------------------------|

| Mode         |                                                        | Start      | Oscil-<br>lator | CPU  | Timer,<br>Serial | Register* | RAM  | I/O<br>terminal     | Escape                                                                                             |

| WAIT         | T Soft- WAIT in-<br>struction  P STOP in-<br>struction |            | Active          | Stop | Active           | Keep      | Keep | Кеер                | STBY, RES, INT, INT <sub>2</sub> ,<br>each interrupt request of<br>TIMER, TIMER <sub>2</sub> , SCI |

| STOP         |                                                        |            | Stop            | Stop | Stop             | Keep      | Keep | Keep                | STBY, RES, INT, INT2                                                                               |

| Stand-<br>by |                                                        | STBY="Low" | Stop            | Stop | Stop             | Reset     | Keep | High im-<br>pedance | STBY="High"                                                                                        |

<sup>\*</sup> Register in the CPU (except I bit in the CCR)

Figure 22 Transitions among Active Mode, Wait Mode, Stop Mode, Standby Mode and Reset

# BIT MANIPULATION

The HD6305V0 MCU can use a single instruction (BSET or BCLR) to set or clear one bit of the RAM or an I/O port. Every bit of memory or I/O within page 0 (\$00 ~ \$FF) can be tested by the BRSET or BRCLR instruction; depending on the result of the test, the program can branch to required destinations. Since bits in the RAM, or I/O can be manipulated, the user may use a bit within the RAM as a flag or handle a single I/O bit as an independent I/O terminal. Fig. 23 shows an example of bit manipulation and the validity of test instructions. In the example, the program is configured assuming that bit 0 of port A is connected to a zero cross detector circuit and bit 1 of the same port to the trigger of a triac.

The program shown can activate the triac within a time of  $10\mu s$  from zero-crossing through the use of only 7 bytes on the ROM. The on-chip timer provides a required time of delay and pulse width modulation of power is also possible.

SELF 1. BRCLR 0, PORT A, SELF 1

BSET 1, PORT A

BCLR 1, PORT A

Figure 23 Example of Bit Manipulation

# ■ ADDRESSING MODES

Ten different addressing modes are available to the HD6305V0 MCU.

#### Immediate

See Fig. 24. The immediate addressing mode provides access to a constant which does not vary during execution of the program.

This access requires an instruction length of 2 bytes. The effective address (EA) is PC and the operand is fetched from the byte that follows the operation code.

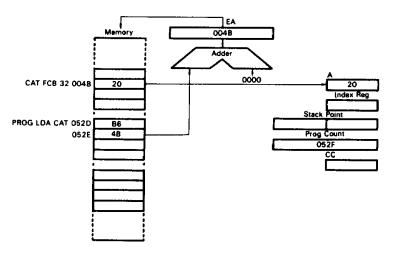

#### Direct

See Fig. 25. In the direct addressing mode, the address of the operand is contained in the 2nd byte of the instruction. The user can gain direct access to memory up to the lower 255th address. All RAM and I/O registers are on page 0 of address space so that the direct addressing mode may be utilized.

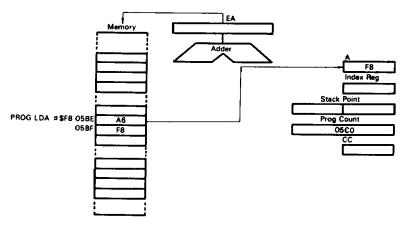

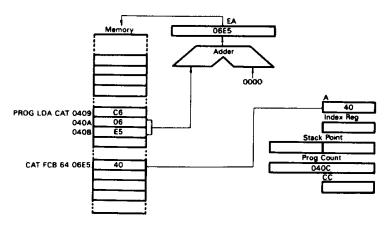

#### Extended

See Fig. 26, the extended addressing is used for referencing to all addresses of memory. The EA is the contents of the 2 bytes that follow the operation code. An extended addressing instruction requires a length of 3 bytes.

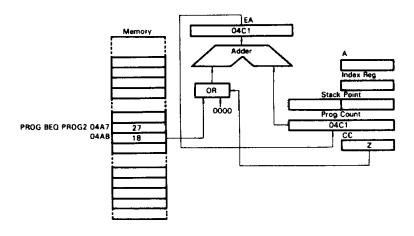

## Relative

See Fig. 27. The relative addressing mode is used with branch instructions only. When a branch occurs, the program counter is loaded with the contents of the byte following the operation code. EA = (PC) + 2 + Rel., where Rel. indicates a signed 8-bit data following the operation code. If no branch occurs, Rel. = 0. When a branch occurs, the program jumps to any byte in the range +129 to -127. A branch instruction requires a length of 2 bytes.

# Indexed (No Offset)

See Fig. 28. The indexed addressing mode allows access up to the lower 255th address of memory. In this mode, an instruction requires a length of one byte. The EA is the contents of the index register.

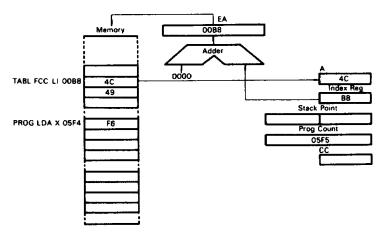

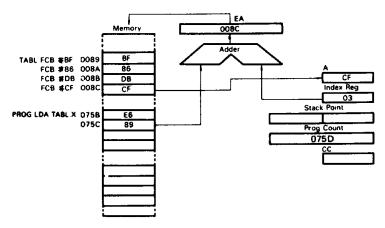

#### Indexed (8-bit Offset)

See Fig. 29. The EA is the contents of the byte following the operation code, plus the contents of the index register. This mode allows access up to the lower 511th address of memory. Each instruction when used in the index addressing mode (8-bit offset) requires a length of 2 bytes.

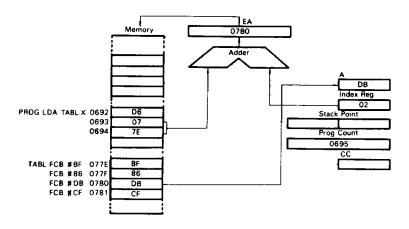

# Indexed (16-bit Offset)

See Fig. 30. The contents of the 2 bytes following the operation code are added to content of the index register to compute the value of EA. In this mode, the complete memory can be accessed. When used in the indexed addressing mode (16-bit offset), an instruction must be 3 bytes long.

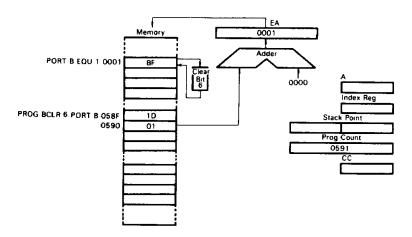

#### Bit Set/Clear

See Fig. 31. This addressing mode is applied to the BSET and BCLR instructions that can set or clear any bit on page 0. The lower 3 bits of the operation code specify the bit to be set or cleared. The byte that follows the operation code indicates an address within page 0.

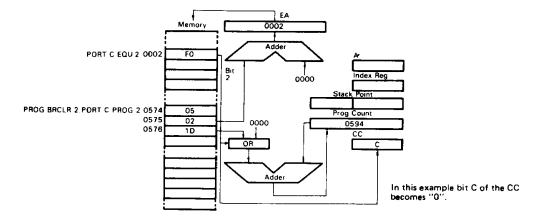

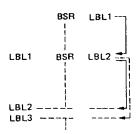

# Bit Test and Branch

See Fig. 32. This addressing mode is applied to the BRSET and BRCLR instructions that can test any bit within page 0 and can be branched in the relative addressing mode. The byte to be tested is addressed depending on the contents of the byte following the operation code. Individual bits within the byte to be tested are specified by the lower 3 bits of the operation code. The 3rd byte represents a relative value which will be added to the program counter when a branch condition is established. Each of these instructions should be 3 bytes long. The result of the test is written in the carry bit of the condition code register. (Set if true, cleared otherwise.)

## Implied

See Fig. 33. This mode involves no EA. All information needed for execution of an instruction is contained in the operation code. Direct manipulation on the accumulator and index register is included in the implied addressing mode. Other instructions such as SWI and RTI are also used in this mode. All instructions used in the implied addressing mode should have a length of one byte.

Figure 24 Example of Immediate Addressing

Figure 25 Example of Direct Addressing

Figure 26 Example of Extended Addressing

Figure 27 Example of Relative Addressing

Figure 28 Example of Indexed (No Offset) Addressing

Figure 29 Example of Indexed (8-bit Offset) Addressing

Figure 30 Example of Indexed (16-bit Offset) Addressing

Figure 31 Example of Bit Set/Clear Addressing

Figure 32 Example of Bit Test and Branch Addressing

Figure 33 Example of Implied Addressing

# ■ INSTRUCTION SET

There are 62 basic instructions available to the HD6305V0 MCU. They can be classified into five categories: register/memory, read/modify/write, branch, bit manipulation, and control. The details of each instruction are described in Tables 5 through 11.

#### Register/Memory Instructions

Most of these instructions use two operands. One operand is either an accumulator or index register. The other is derived from memory using one of the addressing modes used on the HD6305V0 MCU. There is no register operand in the unconditional jump instruction (JMP) and the subroutine jump instruction (JSR). See Table 5.

# Read/Modify/Write Instructions

These instructions read a memory or register, then modify or test its contents, and write the modified value into the memory or register. Zero test instruction (TST) does not write data, and is handled as an exception in the read/modify/write group. See Table 6.

#### • Branch Instructions

A branch instruction branches from the program sequence in progress if a particular condition is established. See Table 7.

#### Bit Manipulation Instructions

These instructions can be used with any bit located up to the lower 255th address of memory. Two groups are available, one for setting or clearing and the other for bit testing and branching. See Table 8.

#### Control Instructions

The control instructions control the operation of the MCU which is executing a program. See Table 9.

# List of Instructions in Alphabetical Order

Table 10 lists all the instructions used on the HD6305V0 MCU in the alphabetical order.

#### Operation Code Map

Table 11 shows the operation code map for the instructions used on the MCU.

Table 5 Register/Memory Instructions

|                      |          |            |     |            |    |      |    | Α        | ddr      | <b>: 35</b> i | ng M | ode        | \$ |    |               |    |            |              |                                                  |                                       |      |            |             |            |          |

|----------------------|----------|------------|-----|------------|----|------|----|----------|----------|---------------|------|------------|----|----|---------------|----|------------|--------------|--------------------------------------------------|---------------------------------------|------|------------|-------------|------------|----------|

| Operations           | Mnemonic | lm         | med | iate       |    | Dire | ct | E×       | tend     | led           |      | dex<br>Off |    |    | ndex<br>Bit O |    | Ir<br>(16- | dex<br>Bit C |                                                  | Boolean/<br>Arithmetic<br>Operation   |      |            | ondi<br>Cod |            |          |

|                      |          | OP         | #   | T          | OP | #    | -  | ОP       | #        | -             | OP   | #          |    | OP | #             | T- | OP         | Ħ            | -                                                | operation.                            | н    | 1          | N           | Z          | С        |

| Load A from Memory   | LDA      | A6         | 2   | 2          | В6 | 2    | 3  | C6       | 3        | 4             | F6   | 1          | 3  | E6 | 2             | 4  | D6         | 3            | 5                                                | M→A                                   | •    | •          | ^           | ^          | •        |

| Load X from Memory   | LDX      | ΑE         | 2   | 2          | BE | 2    | 3  | CE       | 3        | 4             | FE   | 1          | 3  | EΕ | 2             | 4  | DE         | 3            | 5                                                | M→X                                   | •    | •          | ٨           | ^          | •        |

| Store A in Memory    | STA      | <b> </b> - | -   | -          | В7 | 2    | 3  | C7       | 3        | 4             | F7   | 1          | 4  | E7 | 2             | 4  | 07         | 3            | 5                                                | A→M                                   | •    | •          | ٨           | ٨          | •        |

| Store X in Memory    | STX      | Ī-         | _   | <b>1</b> – | BF | 2    | 3  | CF       | 3        | 4             | FF   | 1          | 4  | EF | 2             | 4  | DF         | 3            | 5                                                | X-→M                                  | •    | •          | ۸           | ^          | •        |

| Add Memory to A      | ADD      | AB         | 2   | 2          | 88 | 2    | 3  | СВ       | 3        | 4             | FB   | 1          | 3  | EB | 2             | 4  | DB         | 3            | 5                                                | A+M-·A                                | ^    | •          | ۸           | ٨          | ۸        |

| Add Memory and Carry |          | T          |     | Τ          |    |      |    |          | 1        |               |      |            |    |    | Ī             |    |            |              | İ                                                |                                       | 1    | T-         | -           | <u>†</u> — | Г        |

| to A                 | ADC      | A9         | 2   | 2          | В9 | 2    | 3  | C9       | 3        | 4             | F9   | 1          | 3  | E9 | 2             | 4  | D9         | 3            | 5                                                | A+M+C-A                               | Ϊ, Α | •          | Λ           | ^          |          |

| Subtract Memory      | SUB      | AO         | 2   | 2          | во | 2    | 3  | CO       | 3        | 4             | FO   | 1          | 3  | EO | 2             | 4  | DO         | 3            | 5                                                | A-M-A                                 | •    | •          | ۸           | ۸          | ۸        |

| Subtract Memory from | 1        |            | Ī   |            | ļ  |      |    | <b>†</b> | <u> </u> | +             | _    | İ          |    |    | Ī             | Ī  | T          | T            | 1                                                |                                       | 1    |            |             |            |          |

| A with Borrow        | SBC      | A2         | 2   | 2          | B2 | 2    | 3  | C2       | 3        | 4             | F2   | 1          | 3  | E2 | 2             | 4  | D2         | 3            | 5                                                | A-M-C→A                               | •    | •          | ٨           | ^          | 1        |

| AND Memory to A      | AND      | A4         | 2   | 2          | B4 | 2    | 3  | C4       | 3        | 4             | F4   | 1          | 3  | E4 | 2             | 4  | D4         | 3            | 5                                                | A · M →A                              | . •  | •          | Λ           | 4          | •        |

| OR Memory with A     | ORA      | AA         | 2   | 2          | ВА | 2    | 3  | CA       | 3        | 4             | FA   | 1          | 3  | EA | 2             | 4  | DA         | 3            | 5                                                | A+M→A                                 | •    | •          | ۸           | ^          | •        |

| Exclusive OR Memory  | T        | 1          |     | 1          | †  |      |    | 1        | 1        | †-            |      | ļ          |    | T  | Ī             | 1  |            | T            |                                                  |                                       |      | <b>†</b> – | !           |            | -        |

| with A               | EOR      | A8         | 2   | 2          | B8 | 2    | 3  | C8       | 3        | 4             | F8   | 1          | 3  | 83 | 2             | 4  | DB         | 3            | 5                                                | A+M →A                                | •    | •          | ٨           | ۸          | •        |

| Arithmetic Compare A |          |            |     |            |    | -    |    | !        |          | -             |      |            | T  | 1  | 1             |    | Ī          |              |                                                  |                                       | †    | !          |             |            |          |

| with Memory          | СМР      | A1         | 2   | 2          | В1 | 2    | 3  | C1       | 3        | 4             | F1   | 1          | 3  | E1 | 2             | 4  | D1         | 3            | 5                                                | AM                                    |      | •          | ٨           | ^          | 1        |

| Arithmetic Compare X |          |            | i   |            |    |      |    | 1        |          | 1             | 1    | <u> </u>   |    |    |               | 1  | T          | †<br>!       | <del>                                     </del> |                                       |      |            |             | _          | _        |

| with Memory          | CPX      | А3         | 2   | 2          | В3 | 2    | 3  | СЗ       | 3        | 4             | F3   | 1          | 3  | €3 | 2             | 4  | D3         | 3            | 5                                                | X~M                                   |      | •          | Λ           | ٨          | ^        |

| Bit Test Memory with |          |            | T   | 1          |    |      |    | ļ        |          |               |      |            |    | 1  |               |    | † ·        |              |                                                  |                                       | :    | !          |             | 1          | $\vdash$ |

| A (Logical Compare)  | BIT      | A5         | 2   | 2          | 85 | 2    | 3  | C5       | 3        | 4             | F5   | 1          | 3  | E5 | 2             | 4  | D5         | 3            | 5                                                | A · M                                 | •    | •          |             | ١,٨        |          |

| Jump Unconditional   | JMP      | 1-         | -   | <b>†</b> - | ВС | 2    | 2  | СС       | 3        | 3             | FC   | 1          | 2  | EC | 2             | 3  | DC         | 3            | 4                                                |                                       | . •  | •          | •           | •          | •        |

| Jump to Subroutine   | JSR      | <b> </b> _ | 1=  | 1=         | BD | 2    | 5  | CD       | 3        | 6             | FD   | 1          | 5  | ED | 2             | 5  | DD         | 3            | 6                                                | • • • • • • • • • • • • • • • • • • • |      | •          |             | •          |          |

Symbols: Op = Operation

# = Number of bytes

~ = Number of cycles

Table 6 Read/Modify/Write Instructions

|                         |          | ĺ  |      |      |    |       | Add  | ires | ing   | Mod | des |     |   |    |               |              |                               |   |   |              |   |   |

|-------------------------|----------|----|------|------|----|-------|------|------|-------|-----|-----|-----|---|----|---------------|--------------|-------------------------------|---|---|--------------|---|---|

| Operations              | Mnemonic | lm | plie | d(A) | Im | plied | 1(X) | ,    | Direc | et  | "   | dex |   |    | idex<br>Bit O | ed<br>ffset) | Boolean/Arithmetic Operation  |   |   | ndit<br>Code |   |   |

|                         |          | ОР | Ħ    | -    | OP | n     | -    | OP   | #     | -   | OP  | Ħ   | - | OP | ı             | -            | 1                             | н | ı | N            | Z | С |

| Increment               | INC      | 4C | 1    | 2    | 5C | 1     | 2    | 3С   | 2     | 5   | 7C  | 1   | 5 | 6C | 2             | 6            | A+1 → A or X+1 → X or M+1 → M | • | • | ^            | ^ | • |

| Decrement               | DEC      | 44 | 1    | 2    | 5A | 1     | 2    | 3A   | 2     | 5   | 7A  | 1   | 5 | 6A | 2             | 6            | A-1 →A or X-1 →X or M-1 →M    | • | • | ۸            | ٨ | • |

| Clear                   | CLR      | 4F | 1    | 2    | 5F | 1     | 2    | 3F   | 2     | 5   | 7F  | 1   | 5 | 6F | 2             | 6            | 00 → A or 00 → X or 00 → M    | • | • | 0            | 1 | • |

| Complement              | COM      | 43 | 1    | 2    | 53 | 1     | 2    | 33   | 2     | 5   | 73  | 1   | 5 | 63 | 2             | 6            | Ā⊸A or X→X or Mi⊸M            | • | • | ^            | ۸ | 1 |

| Negate                  |          |    | 1    | Ī    |    |       |      |      |       |     |     |     |   |    |               |              | 00 - A → A or 00 - X → X      | Ī |   |              |   | Г |

| (2's Complement)        | NEG      | 40 | 1    | 2    | 50 | 1     | 2    | 30   | 2     | 5   | 70  | 1   | 5 | 60 | 2             | 6            | or 00 MM                      | • | • | ٨            | ٨ | ٨ |

| Rotate Left Thru Carry  | ROL      | 49 | 1    | 2    | 59 | 1     | 2    | 39   | 2     | 5   | 79  | 1   | 5 | 69 | 2             | 6            | C b; A or X or M bo           | • | • | ۸            | ^ | ٨ |

| Rotate Right Thru Carry | ROR      | 46 | ,    | 2    | 56 | ,     | 2    | 36   | 2     | 5   | 76  | 1   | 5 | 66 | 2             | 6            | -C-                           | • | • | ^            | ^ | ^ |

| Logical Shift Left      | LSL      | 48 | 1    | 2    | 58 | 1     | 2    | 38   | 2     | 5   | 78  | ,   | 5 | 68 | 2             | 6            |                               | • | • | ^            | ^ | ۸ |

| Logical Shift Right     | LSR      | 44 | 1    | 2    | 54 | ,     | 2    | 34   | 2     | 5   | 74  | 1   | 5 | 64 | 2             | 6            | 0 Log X or M C                | • | • | 0            | ^ | 4 |

| Arithmetic Shift Right  | ASR      | 47 | 1    | 2    | 57 | 1     | 2    | 37   | 2     | 5   | 77  | ,   | 5 | 67 | 2             | 6            | b, — bo c                     | • | • | ^            | ٨ | ٨ |

| Arithmetic Shift Left   | ASL      | 48 | 1    | 2    | 58 | 1     | 2    | 38   | 2     | 5   | 78  | 1   | 5 | 68 | 2             | 6            | Equal to LSL                  | • | • | ^            | ۸ | Λ |

| Test for Negative       |          |    |      |      |    |       | 1    |      | _     |     |     |     |   |    |               |              |                               |   |   |              |   |   |

| or Zero                 | TST      | 4D | 1    | 2    | 5D | 1     | 2    | 30   | 2     | 4   | 70  | 1   | 4 | 6D | 2             | 5            | A-00 or X-00 or M-00          | • | • | ٨            | 1 | • |

Symbols: Op = Operation

# = Number of bytes

~ = Number of cycles

Table 7 Branch Instructions

|                            |          | Addr | essing N | /lodes       |             |   | Cond | lition | Cod | le |

|----------------------------|----------|------|----------|--------------|-------------|---|------|--------|-----|----|

| Operations                 | Mnemonic | F    | Relative | <del>)</del> | Branch Test |   |      |        |     |    |

|                            |          | OP   | #        | ~            |             | Н | ١    | N      | Z   | С  |

| Branch Always              | BRA      | 20   | 2        | 3            | None        | • | •    | •      | •   | •  |

| Branch Never               | BRN      | 21   | 2        | 3            | None        | • | •    | •      | •   | •  |

| Branch IF Higher           | ВНІ      | 22   | 2        | 3            | C+Z=0       | • | •    | •      | •   | •  |

| Branch IF Lower or Same    | BLS      | 23   | 2        | 3            | C+Z=1       | • | •    | •      | •   | •  |

| Branch IF Carry Clear      | всс      | 24   | 2        | 3            | C=0         | • | •    | •      | •   | •  |

| (Branch IF Higher or Same) | (BHS)    | 24   | 2        | 3            | C=0         | • | •    | •      | •   | •  |

| Branch IF Carry Set        | BCS      | 25   | 2        | 3            | C = 1       | • | •    | •      | •   | •  |

| (Branch IF Lower)          | (BLO)    | 25   | 2        | 3            | C=1         | • | •    | •      | •   | •  |

| Branch IF Not Equal        | BNE      | 26   | 2        | 3            | Z=0         | • | •    | •      | •   | •  |

| Branch IF Equal            | BEQ      | 27   | 2        | 3            | Z=1         | • | •    | •      | •   | •  |

| Branch IF Half Carry Clear | внсс     | 28   | 2        | 3            | H=0         | • | •    | •      | •   | •  |

| Branch IF Half Carry Set   | BHCS     | 29   | 2        | 3            | H=1         | • | •    | •      | •   | •  |

| Branch IF Plus             | BPL      | 2A   | 2        | 3            | N=0         | • | •    | •      | •   | •  |

| Branch IF Minus            | ВМІ      | 2B   | 2        | 3            | N=1         | • | •    | •      | •   | •  |

| Branch IF Interrupt Mask   |          |      |          |              |             |   |      |        |     |    |

| Bit is Clear               | BMC      | 2C   | 2        | 3            | I=0         | • | •    | •      | •   | •  |

| Branch IF Interrupt Mask   |          |      |          |              |             |   | 1    |        |     |    |

| Bit is Set                 | BMS      | 2D   | 2        | 3            | l=1         | • | •    | •      | •   | •  |

| Branch IF Interrupt Line   |          |      |          |              |             |   |      |        | 1   |    |

| is Low                     | BIL      | 2E   | 2        | 3            | INT=0       | • | •    | •      | •   | •  |

| Branch IF Interrupt Line   |          |      |          |              |             |   |      |        |     |    |

| is High                    | він      | 2F   | 2        | 3            | 1NT = 1     | • | •    | •      | •   | •  |

| Branch to Subroutine       | BSR      | AD   | 2        | 5            |             | • | •    | •      | •   |    |

Symbols: Op = Operation # = Number of bytes ~ = Number of cycles

Table 8 Bit Manipulation Instructions

|                          |                  | ,       | Add  | ressi | ng Modes     |       |     | Boolean/   | D              |   | andi  | ition | Cod | -la |

|--------------------------|------------------|---------|------|-------|--------------|-------|-----|------------|----------------|---|-------|-------|-----|-----|

| Operations               | Mnemonic         | Bit Set | Clea | ar .  | Bit Test and | d Bra | nch | Arithmetic | Branch<br>Test |   | or id | LIOI  | COL | 16  |

| <b>Operation</b>         |                  | OP      | #    | ~     | OP           | #     | ~   | Operation  | 1031           | Н | 1     | N     | Z   | С   |

| Branch IF Bit n is set   | BRSET n(n=0···7) | _       | _    | -     | 2·n          | 3     | 5   |            | Mn = 1         | • | •     | •     | •   |     |

| Branch IF Bit n is clear | BRCLR n(n=0···7) | _       | _    |       | 01+2·n       | 3     | 5   |            | Mn=0           | • | •     | •     | •   | L   |

| Set Bit n                | BSET n(n=07)     | 10+2·n  | 2    | 5     |              | -     |     | 1→Mn       |                | • | •     | •     | •   | •   |

| Clear Bit n              | BCLR n(n=07)     | 11+2·n  | 2    | 5     |              | -     | _   | 0→Mn       |                | • | •     | •     | •   | •   |

Symbols: Op = Operation # = Number of bytes ~ = Number of cycles

Table 9 Control Instructions

|                          |          | Addre | essing | Modes |                                                      |              |          |       |     |                |

|--------------------------|----------|-------|--------|-------|------------------------------------------------------|--------------|----------|-------|-----|----------------|

| Operations               | Mnemonic |       | Implie | d     | Boolean Operation                                    | C            | ond      | ition | Coc | de             |

|                          |          | OP    | #      | ~     |                                                      | Н            | T        | N     | Z   | C              |

| Transfer A to X          | TAX      | 97    | 1      | 2     | A→X                                                  | -            |          |       | -   | ÷              |

| Transfer X to A          | TXA      | 9F    | 1      | 2     | X→A                                                  |              |          | -     | -   | +              |

| Set Carry Bit            | SEC      | 99    | 1      | 1     | 1-+C                                                 | - i          |          |       | -   | +-             |

| Clear Carry Bit          | CLC      | 98    | 1      | 1     | 0→C                                                  | -            | -        | -     |     | 0              |

| Set Interrupt Mask Bit   | SEI      | 98    | 1      | 2     | 1→                                                   | -            | 1        | -     | -   | -              |

| Clear Interrupt Mask Bit | CLI      | 9A    | 1      | 2     | 0-+1                                                 |              | 0        | H     |     | +              |

| Software Interrupt       | SWI      | 83    | 1      | 10    |                                                      | +            | 1        |       | -   | -              |

| Return from Subroutine   | RTS      | 81    | 1      | 5     |                                                      |              | <u> </u> | -     | -   | -              |

| Return from Interrupt    | RTI      | 80    | 1      | 8     |                                                      | 7            | 2        | 7     | 2   | -,             |

| Reset Stack Pointer      | RSP      | 9C    | 1      | 2     | \$FF→SP                                              |              | <u> </u> | -     | !   | -              |

| No-Operation             | NOP      | 9D    | 1      | 1     | Advance Prog. Cntr. Only                             | <del>-</del> |          | -     |     | <u> </u>       |

| Decimal Adjust A         | DAA      | 8D    | 1      | 2     | Converts binary add of BCD charcters into BCD format | +            | -        |       |     | <del>  •</del> |

| Stop                     | STOP     | 8E    | 1      | 4     | BCD format                                           | •            | 0        |       |     |                |

| Wait                     | WAIT     | 8F    | 1      | 4     |                                                      | -            | 0        |       | _   | •              |

Symbols: Op = Operation

# = Number of bytes

~ = Number of cycles

\* Are BCD characters of upper byte 10 or more? (They are not cleared if set in advance.)

Table 10 Instruction Set (in Alphabetical Order)

| _        |          |                                                  |        |          | Addressin                             | ng Modes               |                    |                     |                      |                                                  | . ( | ond | ition | Coc          | de |

|----------|----------|--------------------------------------------------|--------|----------|---------------------------------------|------------------------|--------------------|---------------------|----------------------|--------------------------------------------------|-----|-----|-------|--------------|----|

| Mnemonic | Implied  | Immediate                                        | Direct | Extended | Relative                              | Indexed<br>(No Offset) | Indexed<br>(8-Bit) | Indexed<br>(16-Bit) | Bit<br>Set/<br>Clear | Bit<br>Test &<br>Branch                          | Н   | ı   | N     | z            | С  |

| ADC      |          | ×                                                | ×      | ×        |                                       | ×                      | ×                  | ×                   |                      | 1                                                | 7.  | •   | ,     | Α            | ۸. |

| ADD      |          | ×                                                | ×      | ×        |                                       | ×                      | ×                  | ×                   |                      | <del> </del>                                     | 7   | •   | ٠.    | _            | 17 |

| AND      |          | ×                                                | ×      | ×        | · · · · · · · · · · · · · · · · · · · | ×                      | ×                  | ×                   |                      | <del> </del>                                     | •   | •   | Λ.    | Α            | •  |

| ASL      | ×        |                                                  | ×      |          |                                       | ×                      | ×                  |                     |                      | <u> </u>                                         | •   | •   |       | <del>!</del> | +- |

| ASR      | ×        |                                                  | ×      | 1        |                                       | ×                      | ×                  |                     |                      | ļ                                                | •   | •   |       |              | 1. |

| BCC      |          |                                                  |        |          | ×                                     |                        |                    |                     |                      | 1                                                | •   | •   | •     | •            | •  |

| BCLR     |          |                                                  |        | 1        |                                       |                        |                    |                     | ×                    | <del> </del>                                     | •   | •   | •     | •            | •  |

| BCS      |          | † <u> </u>                                       |        |          | ×                                     | !                      |                    |                     |                      | † · · · · -                                      | •   | •   | •     | •            | •  |