# SmartHSF™ Mobile Modem

Host-Processed, V.90/K56flex™ Modem Device Set with CX11250 Host Side Device, CX20463 SmartDAA™, and Optional CX20437 Voice Codec for PCI Bus/Mini PCI-Based Mobile Applications

**Data Sheet**

**Conexant Proprietary Information**

## **Revision History**

| Revision | Date      | Comments            |

|----------|-----------|---------------------|

| В        | 7/28/2000 | Revision B release. |

| Α        | 4/19/2000 | Initial release.    |

© 2000, Conexant Systems, Inc. All Rights Reserved.

Information in this document is provided in connection with Conexant Systems, Inc. ("Conexant") products. These materials are provided by Conexant as a service to its customers and may be used for informational purposes only. Conexant assumes no responsibility for errors or omissions in these materials. Conexant may make changes to specifications and product descriptions at any time, without notice. Conexant makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Conexant's Terms and Conditions of Sale for such products, Conexant assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF CONEXANT PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. CONEXANT FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. CONEXANT SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

Conexant products are not intended for use in medical, lifesaving or life sustaining applications. Conexant customers using or selling Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: Conexant™, the Conexant C symbol, "What's Next in Communications Technologies"™, K56flex™, SmartDAA™, and SmartHSF™. Product names or services listed in this publication are for identification purposes only, and may be trademarks of third parties. Third-party brands and names are the property of their respective owners.

For additional disclaimer information, please consult Conexant's Legal Information posted at www.conexant.com, which is incorporated by reference.

Reader Response: Conexant strives to produce quality documentation and welcomes your feedback. Please send comments and suggestions to tech.pubs@conexant.com. For technical questions, contact your local Conexant sales office or field applications engineer.

# **Contents**

| RE |     |                                         |                                                          |     |  |  |

|----|-----|-----------------------------------------|----------------------------------------------------------|-----|--|--|

| 1. |     |                                         |                                                          |     |  |  |

|    | 1.1 |                                         |                                                          |     |  |  |

|    | 1.2 |                                         |                                                          |     |  |  |

|    |     |                                         | neral Modem Features                                     |     |  |  |

|    |     |                                         | Bus Host Interface Features                              |     |  |  |

|    |     |                                         | artDAA Features                                          |     |  |  |

|    |     |                                         | plications                                               |     |  |  |

|    | 1.3 |                                         | OVERVIEW                                                 |     |  |  |

|    |     |                                         | neral Description                                        |     |  |  |

|    |     |                                         | st Modem Software                                        |     |  |  |

|    |     | 1.3.3 Ope                               | erating Modes                                            |     |  |  |

|    |     |                                         | Data/Fax Modes                                           |     |  |  |

|    |     |                                         | Synchronous Access Mode - Video Conferencing             |     |  |  |

|    |     |                                         | TAM Mode                                                 |     |  |  |

|    |     |                                         | Voice/Speakerphone Mode (S Models)                       |     |  |  |

|    |     |                                         | Personal Digital Cellular High Speed Mode (C Models)     |     |  |  |

|    |     |                                         | PDC Packet Mode (C Models)                               |     |  |  |

|    |     |                                         | PHS Mode (C Models)                                      |     |  |  |

|    |     |                                         | cdmaOne Data Mode IS95A (C Models)                       |     |  |  |

|    |     |                                         | cdmaOne Data Packet Mode IS95B (C Models)                |     |  |  |

|    |     |                                         | GSM Mode (C Models)                                      |     |  |  |

|    |     |                                         | erence Design                                            |     |  |  |

|    | 1.4 |                                         | E DESCRIPTION                                            |     |  |  |

|    |     |                                         | 1-7                                                      |     |  |  |

|    |     |                                         | 1-8                                                      |     |  |  |

|    |     | 1.4.3 CX20463 SmartDAA Line Side Device |                                                          |     |  |  |

|    |     | 1.4.4 CX2                               | 20437 Voice Codec (S Models)                             | 1-8 |  |  |

| 2. | TEC | HNICAL SPEC                             | CIFICATIONS                                              | 2-1 |  |  |

|    | 2.1 | <b>ESTABLISH</b>                        | ING DATA MODEM CONNECTIONS                               | 2-1 |  |  |

|    |     |                                         | Dialing                                                  | 2-1 |  |  |

|    |     |                                         | Modem Handshaking Protocol                               |     |  |  |

|    |     |                                         | Call Progress Tone Detection                             |     |  |  |

|    |     |                                         | Answer Tone Detection                                    |     |  |  |

|    |     |                                         | Ring Detection                                           |     |  |  |

|    |     |                                         | Billing Protection                                       |     |  |  |

|    |     |                                         | Connection Speeds                                        |     |  |  |

|    |     |                                         | Automode                                                 |     |  |  |

|    | 2.2 | DATA MODE                               | <u> </u>                                                 |     |  |  |

|    |     |                                         | Speed Buffering (Normal Mode)                            |     |  |  |

|    |     |                                         | DTE-to-Modem Flow Control                                |     |  |  |

|    |     |                                         | Escape Sequence Detection                                |     |  |  |

|    |     |                                         | GSTN Cleardown (V.90/K56flex, V.34, V.32 bis, V.32)      |     |  |  |

|    |     |                                         | Fall Forward/Fallback (V.90/K56flex, V.34/V.32 bis/V.32) |     |  |  |

|    |     |                                         | Retrain                                                  |     |  |  |

|    | 2.3 | FRROR COL                               | RRECTION AND DATA COMPRESSION                            |     |  |  |

|    | 0   |                                         | V.42 Error Correction                                    |     |  |  |

|    |     |                                         | MNP 2-4 Error Correction.                                |     |  |  |

|    |     |                                         | V.42 bis Data Compression                                |     |  |  |

|    |     |                                         | MNP 5 Data Compression                                   |     |  |  |

|    | 2.4 | FAX CLASS                               | 1 OPERATION                                              |     |  |  |

|    | 2.5  | VOICE/1 | TAM MODE                                                               | 2-2  |

|----|------|---------|------------------------------------------------------------------------|------|

|    |      | 2.5.1   | Online Voice Command Mode                                              |      |

|    |      | 2.5.2   | Voice Receive Mode                                                     | 2-3  |

|    |      | 2.5.3   | Voice Transmit Mode                                                    | 2-3  |

|    |      | 2.5.4   | Speakerphone Modes                                                     | 2-3  |

|    | 2.6  |         | JPLEX SPEAKERPHONE (FDSP) MODE                                         |      |

|    | 2.7  |         | R ID                                                                   |      |

|    | 2.8  | MULTIP  | LE COUNTRY SUPPORT (W MODELS)                                          |      |

|    |      | 2.8.1   | OEM Programmable Parameters                                            |      |

|    |      | 2.8.2   | Blacklist Parameters                                                   |      |

|    | 2.9  |         | OSTICS                                                                 |      |

|    |      | 2.9.1   | Commanded Tests                                                        |      |

|    | 2.10 | LOW PC  | OWER SLEEP MODE                                                        | 2-4  |

| 3. | HARD | WARE II | NTERFACE                                                               | 3-1  |

|    | 3.1  | CX1125  | 0 HSD HARDWARE PINS AND SIGNALS                                        | 3-1  |

|    |      | 3.1.1   | HSD Signal Interfaces                                                  | 3-1  |

|    |      |         | PCI Bus/Mini PCI Host Interface                                        |      |

|    |      |         | Power Detection and Switching                                          |      |

|    |      |         | Serial EEPROM Interface                                                |      |

|    |      |         | LSD Interface (Through DIB)                                            |      |

|    |      |         | VC Interface (S Models)                                                |      |

|    |      |         | Telephone Handset Interface (S Models)                                 |      |

|    |      |         | Call Progress Speaker Interface                                        |      |

|    |      |         | PDC/PDC packet Interface                                               |      |

|    |      |         | PHS Interface                                                          |      |

|    |      |         | CDMA Interface                                                         |      |

|    |      |         | GSM Interface                                                          |      |

|    |      | 3.1.2   | HSD Interface Signals, Pin Assignments, and Signal Definitions         | 3-3  |

|    | 3.2  |         | 3 SMARTDAA LSD HARDWARE PINS AND SIGNALS                               |      |

|    |      | 3.2.1   | LSD Signal Interfaces                                                  |      |

|    |      |         | HSD Interface (Through DIB)                                            |      |

|    |      | 2 2 2   | Telephone Line Interface                                               |      |

|    | 2.2  |         | LSD Interface Signals, Pin Assignments, and Signal Definitions         |      |

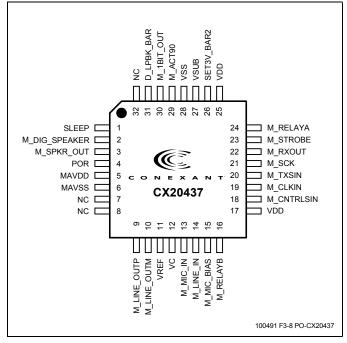

|    | 3.3  | 3.3.1   | 7 VC HARDWARE PINS AND SIGNALS (S MODELS)                              |      |

|    |      | 3.3.1   |                                                                        |      |

|    |      |         | Speakerphone Interface Telephone Handset/Headset Interface             |      |

|    |      |         | HSD Interface                                                          |      |

|    |      | 3.3.2   | VC Interface Signals, Pin Assignments, and Signal Definitions          |      |

|    | 3.4  |         | RICAL ENVIRONMENTAL, AND TIMING SPECIFICATIONS                         |      |

|    | 0.4  | 3.4.1   | Operating Conditions, Absolute Maximum Ratings, and Power Requirements |      |

|    |      |         | Caution: Handling CMOS Devices                                         |      |

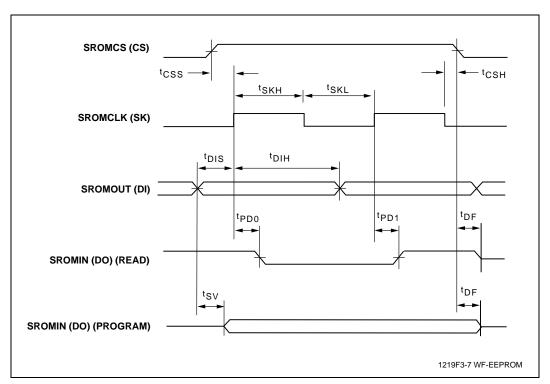

|    |      | 3.4.2   | SERIAL EEPROM INTERFACE TIMING                                         | 3-29 |

| 4. | HOST | SOFTW   | ARE INTERFACE                                                          | 4-1  |

|    | 4.1  | PCI CON | NFIGURATION REGISTERS                                                  | 4-1  |

|    |      | 4.1.1   | 0x00 - Vendor ID Field                                                 |      |

|    |      | 4.1.2   | 0x02 - Device ID Field                                                 | 4-2  |

|    |      | 4.1.3   | 0x04 - Command Register                                                | 4-2  |

|    |      | 4.1.4   | 0x06 - Status Register                                                 | 4-3  |

|    |      | 4.1.5   | 0x08 - Revision ID Field                                               | 4-3  |

|    |      | 4.1.6   | 0x09 - Class Code Field                                                | 4-3  |

|    |      | 4.1.7   | 0x0D - Latency Timer Register                                          |      |

|    |      | 4.1.8   | 0x0E - Header Type Field                                               |      |

|    |      | 4.1.9   | 0x28 - CIS Pointer Register                                            |      |

|    |      | 4.1.10  | 0x2C - Subsystem Vendor ID Register                                    |      |

|    |      | 4.1.11  | 0x2E- Subsystem ID Register                                            |      |

|    |      | 4.1.12  | 0x34 - Cap Ptr                                                         |      |

|    |      | 4.1.13  | 0x3C - Interrupt Line Register                                         | 4-4  |

## SmartHSF Mobile Modem Data Sheet

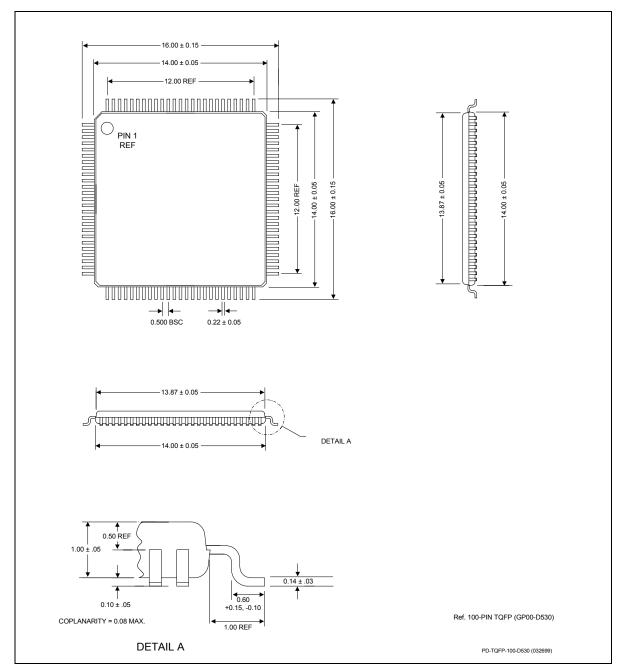

| 5. | PAC | KAGE DI | MENSIONS                                                                     | 5-1             |

|----|-----|---------|------------------------------------------------------------------------------|-----------------|

|    |     |         |                                                                              |                 |

|    |     |         | Load CISRAM Count (CIS _SIZE) (Not Used)                                     | 4-9<br>4-9      |

|    |     |         | dissipated)dissipated                                                        | <i>1</i> _0     |

|    |     |         | Data Scale PMCSR[14.13] (D0C, D1C, D2C, D3C, D0D, D1D, D2D, D3D)             | <del>4</del> -9 |

|    |     |         | Data Scale PMCSR[14:13] (D0C, D1C, D2C, D3C, D0D, D1D, D2D, D3D)             |                 |

|    |     |         | Used)                                                                        | <i>1</i> _0     |

|    |     |         | CardBus CIS Pointer (CardBus CIS pointer High, CardBus CIS pointer Low) (Not | 4-9             |

|    |     |         | Class Code Register (Class Code, Sub-class Code, Prog. I/F)                  |                 |

|    |     |         | Max_Lat Register PMC [8:6] and PME DRV Type                                  |                 |

|    |     |         | Min_Gnt Register                                                             |                 |

|    |     |         | Subsystem Vendor ID and Subsystem Device Register                            |                 |

|    |     |         | Vendor ID Register                                                           |                 |

|    |     |         | Device ID Register                                                           |                 |

|    |     | 4.3.2   | Definitions                                                                  |                 |

|    |     | 4.3.1   | Supported EEPROM Sizes                                                       |                 |

|    | 4.3 |         | EEPROM INTERFACE                                                             |                 |

|    | 4.2 |         | ADDRESS REGISTER                                                             |                 |

|    |     | 4.1.22  | 0x47 - Data                                                                  |                 |

|    |     | 4.1.21  | 0x46 - PMCSR_BSE - PMCSR PCI to PCI Bridge Support Extensions                |                 |

|    |     | 4.1.20  | 0x44 - PMCSR - Power Management Control/Status Register (Offset = 4)         |                 |

|    |     | 4.1.19  | 0x42 - PMC - Power Management Capabilities                                   |                 |

|    |     | 4.1.18  | 0x41 - Next Item Pointer                                                     |                 |

|    |     | 4.1.17  | 0x40 - Capability Identifier                                                 |                 |

|    |     | 4.1.16  | 0x3F - Max Latency Register                                                  | 4-4             |

|    |     | 4.1.15  | 0x3E - Min Grant Register                                                    |                 |

|    |     | 4.1.14  | 0x3D - Interrupt Pin Register                                                | 4-4             |

|    |     |         |                                                                              |                 |

٧

# **Figures**

| Figure 1-2. SmartHSF Modem Major Interfaces                 | 1-3  |

|-------------------------------------------------------------|------|

| Figure 3-1. CX11250 HSD Hardware Interface Signals          |      |

| Figure 3-2. CX11250 HSD 100-Pin TQFP Pin Signals            |      |

| Figure 3-3. CX20463 LSD Hardware Interface Signals          | 3-17 |

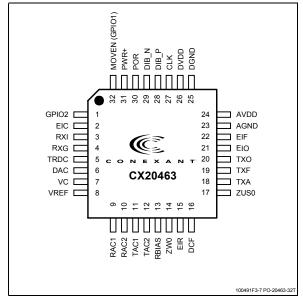

| Figure 3-4. CX20463 LSD 32-Pin TQFP Pin Signals             | 3-17 |

| Figure 3-5. CX20437 VC Hardware Interface Signals           | 3-22 |

| Figure 3-6. CX20437 VC 32-Pin TQFP Pin Signals              | 3-22 |

| Figure 3-7. Waveforms - Serial EEPROM Interface             |      |

| Figure 5-1. Package Dimensions - 100-Pin TQFP               |      |

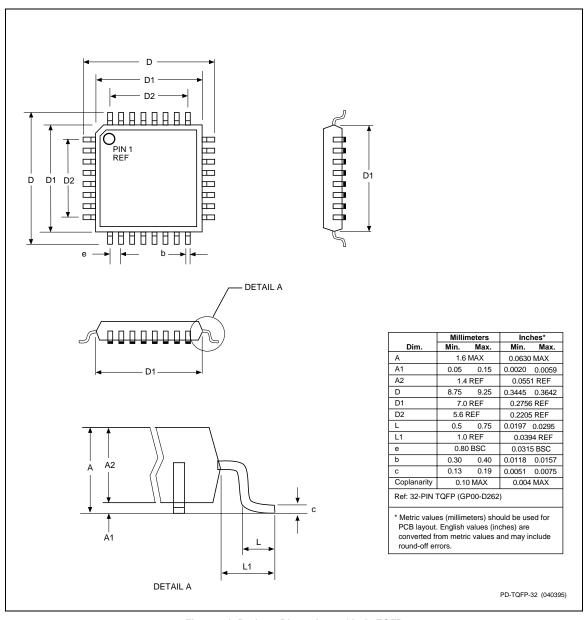

| Figure 5-2. Package Dimensions - 32-pin TQFP                | 5-2  |

| Tables                                                      |      |

| labies                                                      |      |

| Table 1-1. SmartHSF Modem Models and Functions              |      |

| Table 3-1. CX11250 HSD 100-Pin TQFP Pin Signals             |      |

| Table 3-2. CX11250 HSD Pin Signal Definitions               |      |

| Table 3-3. Cell Phone/Telephone Line Interface Signals      |      |

| Table 3-4. CX20463 LSD 32-Pin TQFP Pin Signals              |      |

| Table 3-5. CX20463 LSD Pin Signal Definitions               |      |

| Table 3-6. CX20463 LSD DC Electrical Characteristics        |      |

| Table 3-7. CX20437 VC 32-Pin TQFP Pin Signals               |      |

| Table 3-8. CX20437 VC Pin Signal Definitions                |      |

| Table 3-9. CX20437 VC Digital Electrical Characteristics    |      |

| Table 3-10. CX20437 VC Analog Electrical Characteristics    | 3-26 |

| Table 3-11. Operating Conditions                            |      |

| Table 3-12. Absolute Maximum Ratings                        |      |

| Table 3-13. Current and Power Requirements                  |      |

| Table 3-14. Timing - Serial EEPROM Interface                |      |

| Table 4-1. PCI Configuration Registers                      |      |

| Table 4-2. Command Register                                 |      |

| Table 4-3. Status Register                                  |      |

| Table 4-4. Power Management Capabilities (PMC) Register     |      |

| Table 4-5. Power Management Control/Status Register (PMCSR) |      |

| Table 4-6. HSD Address Map                                  |      |

| Table 4-7. EEPROM Content for 256 Words by 16 Bits per Word |      |

| Table 4-8. EEPROM Content for 128 Words by 16 Bits per Word | 4-7  |

## 1. INTRODUCTION

## 1.1 OVERVIEW

The Conexant™ SmartHSF Host-Processed (SoftK56™) V.90/K56flex™ Modem Device Family with SmartDAA technology supports analog data up to 56 kbps, analog fax to 14.4 kbps, telephone answering machine (TAM), and PCI Bus/Mini PCI host interface operation. In addition, the device set optionally supports cellular phone interface (PDC high speed/PDC packet data, PHS data, CDMA/CDMA Packet data, GSM data) or voice/speakerphone. These modem devices meet the size and power requirements of the mobile environment. Table 1-1 lists the available models.

The modem operates with PSTN telephone lines in the U.S./Japan/Canada and, optionally, worldwide. Optional cellular interface supports Japanese PDC (Personal Digital Cellular) and PHS (Personal Handyphone System) phones, GSM (Global System for Mobile Communications) phones, and cdmaOne (IS-95A/IS-95B) phones. Modem and cellular data protocol software is provided.

Conexant's SmartDAA technology (patent pending) eliminates the need for a costly line transformer, relays, and opto-isolators typically used in discrete DAA (Data Access Arrangement) implementations. The SmartDAA architecture also simplifies product implementation by eliminating the need for country-specific board configurations enabling worldwide homologation of a single modem board design.

The SmartDAA system-powered DAA operates reliably without drawing power from the line, unlike line-powered DAAs which operate poorly when line current is insufficient due to long lines or poor line conditions. Enhanced features, such as monitoring of local extension status without going off-hook, are also supported.

Incorporating Conexant's proprietary Digital Isolation Barrier (DIB) design (patent pending) and other innovative DAA features, such as Digital PBX line protection and reporting, the SmartDAA architecture simplifies application design, minimizes layout area, and reduces component cost.

For over a decade, Conexant has assisted customers with DAA technology and homologation. This expertise and system level approach has been leveraged in this product.

The SmartHSF device set, consisting of a CX11250 Host Side Device (HSD) in a 100-pin TQFP and a CX20463 SmartDAA Line Side Device (LSD) in a 32-pin TQFP, supports data/fax/TAM operation with host software-based digital signal processing and cell phone/DAA/telephone line interface functions.

The optional CX20437 Voice Codec (VC), in a 32-pin TQFP, supports voice/full-duplex speakerphone (FDSP) operation with interfaces to a microphone, speaker, and telephone handset/headset. Because some cellular interface signals and CX20437 VC interface signals share the same CX11250 HSD pins, speakerphone configuration does not support the cellular interface.

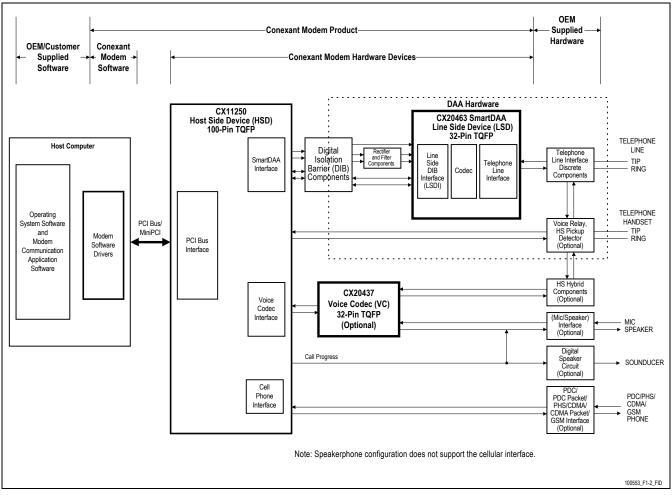

The major hardware signal interfaces are identified in Figure 1-1.

In V.90/K56flex data mode, the modem can receive data at speeds up to 56 kbps from a digitally connected V.90 or K56flex-compatible central site modem. In this mode, the modem can transmit data at speeds up to V.34 rates.

In V.34 data mode, the modem operates at line speeds up to 33.6 kbps. When applicable, error correction (V.42/MNP 2-4) and data compression (V.42 bis/MNP 5) maximize data transfer integrity and boost average data throughput. Non-error-correcting mode is also supported.

Fax Group 3 send and receive rates are supported up to 14.4 kbps with T.30 protocol.

V.80 synchronous access mode supports host-controlled communication protocols, e. g., H.324 video conferencing.

Audio recording and playback over the telephone line interface using A-Law, μ-Law, or linear coding at 8 kHz sample rate supports applications such as remote digital telephone answering machine (TAM).

This designer's guide describes the modem hardware capabilities and identifies the supporting commands. Commands and parameters are defined in the Commands Reference Manual (Doc. No. 100498, formerly identified as Doc. No. 1118).

Table 1-1. SmartHSF Modem Models and Functions

|                  | Model/O                 | rder/Part Numbers                                       | Supported Hardware Functions (See Note 3)              |                                                  |             |             |                                             |           |                |                |

|------------------|-------------------------|---------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------|-------------|-------------|---------------------------------------------|-----------|----------------|----------------|

| Marketing Name   | Device Set<br>Order No. | Host Side<br>Device (HSD)<br>[100-Pin TQFP]<br>Part No. | Line Side<br>Device (LSD)<br>[32-Pin TQFP]<br>Part No. | Voice Codec<br>(VC)<br>[32-Pin TQFP]<br>Part No. | Host<br>Bus | DAA<br>Type | PDC HS/<br>PDC Packet,<br>PHS,<br>CDMA, GSM | V.17 Fax, | World-<br>wide | Voice/<br>FDSP |

| SmartHSF/MC-PCI  | DS56-L155-111           | 11250-11                                                | 20463-12                                               | _                                                | PCI         | US/J/C      | Υ                                           | Υ         | _              | _              |

| SmartHSF/MS-PCI  | DS56-L155-121           | 11250-11                                                | 20463-12                                               | 20437-11                                         | PCI         | US/J/C      | N                                           | Y         | _              | Υ              |

| SmartHSF/MWC-PCI | DS56-L155-131           | 11250-11                                                | 20463-11                                               | _                                                | PCI         | WW          | Υ                                           | Υ         | Υ              | _              |

| SmartHSF/MWS-PCI | DS56-L155-141           | 11250-11                                                | 20463-11                                               | 20437-11                                         | PCI         | WW          | N                                           | Υ         | Υ              | Υ              |

## NOTES:

1. Model options:

C Cellular M Mobile

S Voice/full-duplex speakerphone (FDSP)

W Worldwide support including U.S./Japan/Canada

-PCI PCI Bus/Mini PCI interface

2. Supported functions (Y = Supported; - = Not supported):

TAM Telephone answering machine (Voice playback and record through telephone line)

FDSP Full-duplex speakerphone and voice playback and record through telephone line, handset, and mic/speaker

PDC HS Personal Digital Cellular High Speed data

PDC Packet Personal Digital Cellular Packet data

PHS Personal Handyphone System

CDMA Code Division Multiple Access

GSM Global System for Mobile Communications data

- 3. Software configuration/functions determined by Device ID programmed into EEPROM (see Section 4.3).

- 4. For ordering purposes, the CX prefix may not be included in the part number for some devices. Also, the CX prefix may not appear in the part number as branded on some devices.

Figure 1-1. SmartHSF Modem Major Interfaces

#### 1.2 FEATURES

#### 1.2.1 General Modem Features

- V.90 data modem with receive rates up to 56k bps and send rates up to V.34 rates

- ITU-T V.90, K56flex, V.34 (33.6 kbps), V.32 bis, V.32, V.22 bis, V.22, V.23, and V.21; Bell 212A and 103

- V.42 LAPM and MNP 2-4 error correction

- V.42 bis and MNP 5 data compression

- V.250 and V.251 commands

- V.17 fax modem with send and receive rates up to 14.4 kbps

- V.17, V.29, V.27 ter, and V.21 channel 2

- EIA/TIA 578 Class 1 and T.31 Class 1.0 commands

- Telephony/TAM

- V.253 commands

- 8-bit μ-Law/A-Law coding (G.711)

- 8-bit/16-bit linear coding

- -8 kHz sample rate

- Concurrent DTMF, ring, and Caller ID detection

- V.80 synchronous access mode supports host-controlled communication protocols with H.324 interface support

- V.8/V.8bis and V.251 commands

- Cellular data hardware interface and software support (C models)

- Protocol stacks for PDC high speed data, PDC packet data, PHS data, CDMA IS-95A/IS-95B data, and GSM data

- API for customer-provided cellular data protocol stack

- Full-duplex Speakerphone (FDSP) Mode (S models)

- Microphone and speaker interface

- Telephone handset/headset interface

- Data/Fax/Voice call discrimination

- Host software/MMX-based digital signal processing

- Single configuration profile stored in host

- Operates in U.S./Japan/Canada

- Worldwide operation including U.S./Japan/Canada (W models)

- Complies to TBR21 and other country requirements

- Caller ID detection

- System compatibility

- Windows 95/98, Windows NT 4.0, Windows 2000, and Windows Millennium (Windows Me) operating systems

- Microsoft'/Intel PC 99 Windows Hardware Designer's Guide-compliant

- Advanced Configuration and Power Interface (ACPI)

- Unimodem/V compliant

- Pentium 166 MHz MMX-compatible PC or greater

- 16 Mbyte RAM or more

- Thin packages support low profile designs

- CX11250 HSD: 100-pin TQFP (1.2 mm max. height)

- CX20463 LSD: 32-pin TQFP (1.6 mm max. height)

- CX20437 VC: 32-pin TQFP (1.6 mm max. height)

- +3.3V operation with +5V tolerant digital inputs

#### 1.2.2 PCI Bus Host Interface Features

- 32-bit PCI Bus host interface

- Meets PCI Local Bus Specification Rev. 2.2

- PCI Bus Mastering interface

- -33 MHz PCI clock support

- Supports Power Management

- Meets PCI Bus Power Management Spec. Rev. 1.1

- ACPI Power Management Registers

- APM support

- PME# support

- Vaux/Vpci power switching support (-PCI model option)

- VauxDET support

## 1.2.3 SmartDAA Features

- · Digital PBX line protection

- System side powered DAA operates under poor line current supply conditions

- Wake-on-ring

- Ring detection

- Line polarity reversal detection

- · Line current loss detection

- Caller ID (CID) detect

- Pulse dialing

- Line-in-use detection detects even while on-hook

- Remote hang-up detect for efficient call termination

- Extension pickup detect

- · Call waiting detection

- Meets worldwide DC VI Masks requirements (W models)

## 1.2.4 Applications

- · Laptop, notebook, and handheld computers

- PCI Bus/Mini PCI embedded system boards

- PCI Bus/Mini PCI plug-in cards

## 1.3 TECHNICAL OVERVIEW

## 1.3.1 General Description

Modem operation, including dialing, call progress, telephone line interface, telephone handset interface, PDC High Speed/GSM interface, voice/speakerphone interface, and host interface functions are supported and controlled through the V.250, V.251, and V.253-compatible command set.

The modem hardware connects to the host processor via a PCI/Mini PCI bus interface. The OEM adds a crystal circuit, EEPROM, DIB and LSD power rectifier and filter components, telephone line interface, optional telephone handset interface, optional PDC high speed/GSM interface, optional voice/speakerphone interface, and other supporting discrete components as required by the modem model and the application to complete the system.

## 1.3.2 Host Modem Software

The host modem software performs the following tasks:

- General modem control, which includes command sets, fax Class 1, TAM, voice/speakerphone, error correction, data compression, GSM protocol stacks, PDC high speed data protocol stacks and phone drivers, and operating system interface functions.

- 2. Modem data pump signal processing, which includes data and facsimile modulation and demodulation, as well as voice sample formatting, is performed by the host processor using Conexant SoftK56 technology.

- SmartDAA control, which includes HSD SmartDAA Interface control, LSD configuration and control, telephone line interface parameter control, and telephone line impedance control.

Configurations of the modem software are provided to support modem models listed in Table 1-1.

## 1.3.3 Operating Modes

#### **Data/Fax Modes**

In V.90/K56flex data modem mode, the modem can receive data from a digital source using a V.90- or K56flex-compatible central site modem at line speeds up to 56 kbps. Asymmetrical data transmission supports sending data at line speeds up to V.34 rates. This mode can fallback to full-duplex V.34 mode, and to lower rates, as dictated by line conditions.

In V.34 data modem mode, the modem can operate in 2-wire, full-duplex, asynchronous modes at line rates up to 33.6 kbps. Data modem modes perform complete handshake and data rate negotiations. Using V.34 modulation to optimize modem configuration for line conditions, the modem can connect at the highest data rate that the channel can support from 33600 bps down to 2400 bps with automatic fallback. Automode operation in V.34 is provided in accordance with PN3320 and in V.32 bis in accordance with PN2330. All tone and pattern detection functions required by the applicable ITU or Bell standard are supported.

In V.32 bis data modem mode, the modem can operate at line speeds up to 14.4 kbps.

In fax modem mode, the modem can operate in 2-wire, half-duplex, synchronous modes and can support Group 3 facsimile send and receive speeds of 14400, 12000, 9600, 7200, 4800, and 2400 bps. Fax data transmission and reception performed by the modem are controlled and monitored through the EIA/TIA-578 Class 1 or T.31 Class 1.0 command interface. Full HDLC formatting, zero insertion/deletion, and CRC generation/checking are provided.

## Synchronous Access Mode - Video Conferencing

V.80 Synchronous Access Mode (SAM) between the modem and the host/DTE is provided for host-controlled communication protocols, e.g., H.324 video conferencing applications.

Voice-call-first (VCF) before switching to a videophone call is also supported.

#### **TAM Mode**

TAM Mode features include 8-bit  $\mu$ -Law, A-Law, and linear coding at 8 kHz sample rate. Full-duplex voice supports concurrent voice receive and transmit. Tone detection/generation, call discrimination, and concurrent DTMF detection are also supported. This mode supports applications such as digital TAM, voice annotation, and recording from and playback to the telephone line. ADPCM (4-bit IMA) coding is also supported to meet Microsoft WHQL logo requirements.

TAM Mode is supported by three submodes:

- Online Voice Command Mode supports connection to the telephone line or, for S models, a microphone/speaker/handset/headset.

- Voice Receive Mode supports recording voice or audio data input from the telephone line or, for S models, a microphone/handset/headset.

- Voice Transmit Mode supports playback of voice or audio data to the telephone line or, for S models, a speaker/handset/headset.

## Voice/Speakerphone Mode (S Models)

The S models include additional telephone handset, external microphone, and external speaker interfaces which support voice and full-duplex speakerphone (FDSP) operation.

Hands-free full-duplex telephone operation is supported in Speakerphone Mode under host control. Speakerphone Mode features an advanced proprietary speakerphone algorithm which supports full-duplex voice conversation with acoustic, line, and handset echo cancellation. Parameters are constantly adjusted to maintain stability with automatic fallback from full-duplex to pseudo-duplex operation. The speakerphone algorithm allows position independent placement of microphone and speaker. The host can separately control volume, muting, and AGC in microphone and speaker channels.

NOTE: Because some cellular interface signals and CX20437 VC interface signals share the same CX11250 HSD pins, speakerphone configuration does not support the cellular interface.

## Personal Digital Cellular High Speed Mode (C Models)

Personal Digital Cellular (PDC) High Speed Mode, implemented in host software, includes V.42 bis data compression and ARQ framing. A pass-through mode is also available to allow phone book data to be transferred to and from the PC at speeds up to 9600 bps (e.g., for editing on the PC). PDC High Speed Mode is enabled by the +WS46=20 and +CPDCM=2 AT commands and disabled by the +WS46=1 AT command.

#### **PDC Packet Mode (C Models)**

PDC Packet Mode, implemented in host software as an optional mode of PDC, enables packet-based data communications at 28.8 kbps. PDC Packet Data Mode is enabled by the +WS46=20 and +CPDCM=3 AT commands and disabled by the +WS46=1 AT command.

#### PHS Mode (C Models)

PHS Data Mode is implemented in host software and supports a data rate of 32 kbps. PHS uses the PIAFS protocol stack. PHS Data Mode is enabled by the +WS46=26 AT command and disabled by the +WS46=1 AT command.

## cdmaOne Data Mode IS95A (C Models)

cdmaOne Data Mode is implemented in host software and supports data rates of 9.6 kbps and 14.4 kbps. cdmaOne Data Mode is enabled by the +WS46=13 AT command and disabled by the +WS46=1 AT command.

## cdmaOne Data Packet Mode IS95B (C Models)

cdmaOne Data Packet Mode is implemented in host software and supports a data rate of 64 kbps. cdmaOne Data Packet Mode is enabled by the +WS46=13 AT command and disabled by the +WS46=1 AT command.

#### **GSM Mode (C Models)**

GSM Mode, implemented in host software, supports data and fax transfer. The supported features include:

- Data modem

- -V.21, V.23, V.22, V.22 bis, V.32

- ISDN interoperability: 300 bps to 9600 bps

- Transparent asynchronous mode up to 9600 bps

- Non-transparent mode (RLP) up to 9600 bps

- Fax modem send and receive rate up to 9600 bps

- AT GSM commands (ETSI 07.07)

- · GSM direct connect

- Driver interface for OEM-provided phone driver

- Built-in parallel host (16550A UART) interface

GSM mode is enabled by the +WS46=12 AT command and disabled by the +WS46=1 AT command.

## 1.3.4 Reference Design

A Mini PCI Type IIIB data/fax/TAM reference design board is available to minimize application design time and costs.

The board is pretested to pass FCC Part 15, Part 68, and CTR 21 for immediate manufacturing.

A design package for the board is available in electronic form. The design package includes schematics, bill of materials (BOM), vendor parts list (VPL), board layout files in Gerber format, and complete documentation.

The design can also be used for the basis of a custom design by the OEM to accelerate design completion for rapid market entry.

## 1.4 HARDWARE DESCRIPTION

SmartDAA™ technology (patent pending) eliminates the need for a costly analog transformer, relays, and opto-isolators that are typically used in discrete DAA implementations. The programmable SmartDAA architecture simplifies product implementation in worldwide markets by eliminating the need for country-specific components.

## 1.4.1 CX11250 Host Side Device

The CX11250 Host Side Device (HSD), packaged in a 100-pin TQFP, includes a PCI/Mini PCI Interface and a SmartDAA Interface.

The PCI/Mini PCI interface connects directly to an embedded or external PCI/Mini PCI interface eliminating the need for additional external logic components.

The SmartDAA Interface communicates with, and supplies power and clock to, the LSD through the DIB.

## 1.4.2 Digital Isolation Barrier

The OEM-supplied Digital Isolation Barrier (DIB) electrically DC isolates the HSD from the LSD and telephone line. The HSD is connected to a fixed digital ground and operates with standard CMOS logic levels. The LSD is connected to a floating ground and can tolerate high voltage input (compatible with telephone line and typical surge requirements).

The DIB transformer couples power and clock from the HSD to the LSD. (See Mobile Product Updates for qualified transformers.)

The DIB data channel supports bidirectional half-duplex serial transfer of data, control, and status information between the HSD and the LSD.

## 1.4.3 CX20463 SmartDAA Line Side Device

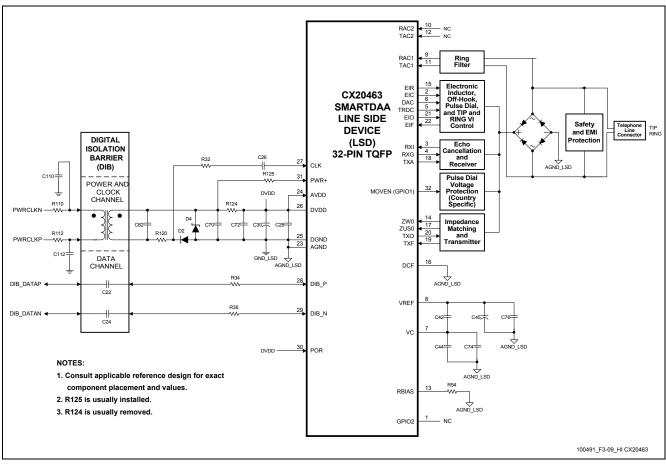

The CX20463 SmartDAA Line Side Device (LSD) includes a Line Side DIB Interface (LSDI), a coder/decoder (codec), and a Telephone Line Interface (TLI).

The LSDI communicates with, and receives power and clock from, the SmartDAA interface in the HSD through the DIB.

LSD power is received from the HSD PWRCLKP and PWRCLKN pins via the DIB through a half-wave rectifying diode and capacitive power filter circuit connected to the DIB transformer secondary winding. The CLK input is also coupled from the transformer secondary winding through a capacitor and a resistor in series.

Information is transferred between the LSD and the HSD through the DIB\_P and DIB\_N pins. These pins connect to the HSD DIB\_DATAP and DIB\_DATAN pins, respectively, through the DIB.

The TLI integrates DAA and direct telephone line interface functions and connects directly to the line TIP and RING pins, as well as to external line protection components.

Direct LSD connection to TIP and RING allows real-time measurement of telephone line parameters, such as the telephone central office (CO) battery voltage, individual telephone line (copper wire) resistance, and allows dynamic regulation of the off-hook TIP and RING voltage and total current drawn from the central office (CO). This allows the modem to maintain compliance with U.S. and worldwide regulations and to actively control the DAA power dissipation.

## 1.4.4 CX20437 Voice Codec (S Models)

The optional CX20437 Voice Codec (VC), packaged in a 32-pin TQFP, supports voice/full-duplex speakerphone (FDSP) operation with interfaces to a microphone and speaker and to a telephone handset/headset.

## 2. TECHNICAL SPECIFICATIONS

## 2.1 ESTABLISHING DATA MODEM CONNECTIONS

### **Dialing**

**DTMF Dialing.** DTMF dialing using DTMF tone pairs is supported in accordance with ITU-T Q.23. The transmit tone level complies with Bell Publication 47001.

Pulse Dialing. Pulse dialing is supported in accordance with EIA/TIA-496-A.

Blind Dialing. The modem can blind dial in the absence of a dial tone if enabled by the X0, X1, or X3 command.

## **Modem Handshaking Protocol**

If a tone is not detected within the time specified in the S7 register after the last digit is dialed, the modem aborts the call attempt.

## **Call Progress Tone Detection**

Ringback, equipment busy, and progress tones can be detected in accordance with the applicable standard represented by the country profile currently in affect.

## **Answer Tone Detection**

Answer tone can be detected over the frequency range of 2100 ± 40 Hz in ITU-T modes and 2225 ± 40 Hz in Bell modes.

#### **Ring Detection**

A ring signal can be detected from a TTL-compatible square wave input (frequency is country-dependent).

#### **Billing Protection**

When the modem goes off-hook to answer an incoming call, both transmission and reception of data are prevented for a period of time determined by country requirement to allow transmission of the billing signal.

## **Connection Speeds**

Data modem line speed can be selected using the +MS command in accordance with V.25 ter. The +MS command selects modulation, enables/disables automode, and selects transmit and receive minimum and maximum line speeds.

#### **Automode**

Automode detection can be enabled by the +MS command to allow the modem to connect to a remote modem in accordance with V.25 ter.

#### 2.2 DATA MODE

Data mode exists when a telephone line connection has been established between modems and all handshaking has been completed.

## **Speed Buffering (Normal Mode)**

Speed buffering allows a DTE to send data to, and receive data from, a modem at a speed different than the line speed. The modem supports speed buffering at all line speeds.

## **DTE-to-Modem Flow Control**

If the modem-to-line speed is less than the DTE-to-modem speed, the modem supports XOFF/XON or RTS/CTS flow control with the DTE to ensure data integrity.

#### **Escape Sequence Detection**

The "+++" escape sequence can be used to return control to the command mode from the data mode. Escape sequence detection is disabled by an S2 Register value greater than 127.

### GSTN Cleardown (V.90/K56flex, V.34, V.32 bis, V.32)

Upon receiving GSTN Cleardown from the remote modem in a non-error correcting mode, the modem cleanly terminates the call.

## Fall Forward/Fallback (V.90/K56flex, V.34/V.32 bis/V.32)

During initial handshake, the modem will fallback to the optimal line connection within K56flex/V.34/V.32 bis/V.32 mode depending upon signal quality if automode is enabled by the +MS command.

When connected in V.90/K56flex/V.34/V.32 bis/V.32 mode, the modem will fall forward or fallback to the optimal line speed within the current modulation depending upon signal quality if fall forward/fallback is enabled by the %E1 command.

#### Retrain

The modem may lose synchronization with the received line signal under poor line conditions. If this occurs, retraining may be initiated to attempt recovery depending on the type of connection.

The modem initiates a retrain if line quality becomes unacceptable if enabled by the %E command. The modem continues to retrain until an acceptable connection is achieved, or until 30 seconds elapse resulting in line disconnect.

## 2.3 ERROR CORRECTION AND DATA COMPRESSION

#### V.42 Error Correction

V.42 supports two methods of error correction: LAPM and, as a fallback, MNP 4. The modem provides a detection and negotiation technique for determining and establishing the best method of error correction between two modems.

#### **MNP 2-4 Error Correction**

MNP 2-4 is a data link protocol that uses error correction algorithms to ensure data integrity. Supporting stream mode, the modem sends data frames in varying lengths depending on the amount of time between characters coming from the DTE.

#### V.42 bis Data Compression

V.42 bis data compression mode operates when a LAPM or MNP connection is established.

The V.42 bis data compression employs a "string learning" algorithm in which a string of characters from the DTE is encoded as a fixed length codeword. Two dictionaries, dynamically updated during normal operation, are used to store the strings.

## **MNP 5 Data Compression**

MNP 5 data compression mode operates during an MNP connection.

In MNP 5, the modem increases its throughput by compressing data into tokens before transmitting it to the remote modem, and by decompressing encoded received data before sending it to the DTE.

#### 2.4 FAX CLASS 1 OPERATION

Facsimile functions operate in response to Fax Class 1 commands when +FCLASS=1 or +FCLASS=1.0.

In the fax mode, the on-line behavior of the modem is different from the data (non-fax) mode. After dialing, modem operation is controlled by fax commands. Some AT commands are still valid but may operate differently than in data modem mode.

Calling tone is generated in accordance with T.30.

## 2.5 VOICE/TAM MODE

Voice and audio functions are supported by the Voice Mode. Voice Mode includes three submodes: Online Voice Command Mode, Voice Receive Mode, and Voice Transmit Mode.

#### 2.5.1 Online Voice Command Mode

This mode results from the connection to the telephone line or a voice/audio I/O device (e.g., microphone or speaker) through the use of the +FCLASS=8 and +VLS commands. After mode entry, AT commands can be entered without aborting the connection.

#### 2.5.2 Voice Receive Mode

This mode is entered when the +VRX command is active in order to record voice or audio data input, typically from a microphone or the telephone line.

Received analog voice samples are converted to digital form and compressed for reading by the host. AT commands control the codec sample rate.

Received analog mono audio samples are converted to digital form and formatted into 8-bit  $\mu$ -Law, A Law, linear, or 4-bit IMA ADPCM format for reading by the host. AT commands control the bit length and sampling rate. Concurrent DTMF/tone detection is available.

#### 2.5.3 Voice Transmit Mode

This mode is entered when the +VTX command is active in order to playback voice or audio data, typically to a speaker or to the telephone line. Concurrent DTMF/tone detection is available. Digitized audio data is converted to analog form.

## 2.5.4 Speakerphone Modes

Speakerphone modes are selected in voice mode with the following commands:

Speakerphone ON/OFF (+VSP). This command turns the Speakerphone function ON (+VSP = 1) or OFF (+VSP = 0).

Microphone Gain (+VGM=<gain>). This command sets the microphone gain of the Speakerphone function.

Speaker Gain (+VGS=<gain>). This command sets the speaker gain of the Speakerphone function.

## 2.6 FULL-DUPLEX SPEAKERPHONE (FDSP) MODE

The modem operates in FDSP mode when +FCLASS=8 and +VSP=1 (see 2.5.4).

In FDSP Mode, speech from a microphone or handset is converted to digital form, shaped, and output to the telephone line through the line interface circuit. Speech received from the telephone line is shaped, converted to analog form, and output to the speaker or handset. Shaping includes both acoustic and line echo cancellation.

### 2.7 CALLER ID

Caller ID can be enabled/disabled using the +VCID command. When enabled, caller ID information (date, time, caller code, and name) can be passed to the DTE in formatted or unformatted form. Inquiry support allows the current caller ID mode and mode capabilities of the modem to be retrieved from the modem. The retrieval of the Caller ID via an explicit AT query at a later time is essential for implementing a compliant "Instantly available PC" concept.

## 2.8 MULTIPLE COUNTRY SUPPORT (W MODELS)

W models support modem operation in various countries. The country choice is made via the AT+GCI command or country select applet from within those installed in Windows registry. The following capabilities are provided in addition to the data modem functions previously described. Country dependent parameters are included in the .INF file for customization by the OEM Programmable Parameters

## 2.8.1 OEM Programmable Parameters

The following parameters are programmable:

- Dial tone detection levels and frequency ranges

- . DTMF dialing transmit output level, DTMF signal duration, and DTMF interdigit interval parameters

- Pulse dialing parameters such as make/break times, set/clear times, and dial codes

- · Ring detection frequency range

- Blind dialing disable/enable

- The maximum, minimum, and default carrier transmit level values

- Calling tone, generated in accordance with V.25, may also be disabled

- Call progress frequency and tone cadence for busy, ringback, congested, dial tone 1, and dial tone 2

- Answer tone detection period

- On-hook/off-hook, make/break, and set/clear relay control parameters

#### 2.8.2 Blacklist Parameters

The modem can operate in accordance with requirements of individual countries to prevent misuse of the network by limiting repeated calls to the same number when previous call attempts have failed. Call failure can be detected for reasons such as no dial tone, number busy, no answer, no ringback detected, voice (rather than modem) detected, and key abort (dial attempt aborted by user). Actions resulting from such failures can include specification of minimum inter-call delay, extended delay between calls, and maximum numbers of retries before the number is permanently forbidden ("blacklisted"). Up to 20 such numbers may be tabulated. The blacklist parameters are programmable. The current blacklisted and delayed numbers can be queried via AT\*B and AT\*D commands, respectively.

#### 2.9 DIAGNOSTICS

#### 2.9.1 Commanded Tests

Diagnostics are performed in response to the &T1 command per V.54.

**Analog Loopback (&T1 Command).** Data from the local DTE is sent to the modem, which loops the data back to the local DTE.

Last Call Status Report (#UD). This command reports the status of the last call.

## 2.10 LOW POWER SLEEP MODE

When not connected in data, fax, or speakerphone mode, the HSD is placed in a low power state, i.e., Idle Mode.

## 3. HARDWARE INTERFACE

## 3.1 CX11250 HSD HARDWARE PINS AND SIGNALS

## 3.1.1 HSD Signal Interfaces

#### PCI Bus/Mini PCI Host Interface

The Host Side Device conforms to the PCI Local Bus Specification Version 2.2 and Mini PCI Specification Draft 1.0. It is a memory slave and a bus master for PC host memory accesses (burst transactions). Configuration is by PCI configuration protocol.

The PCI Bus/Mini PCI interface signals are:

- · Address and data

- 32 bidirectional Address/Data (AD[31-0]); bidirectional

- -4 Bus Command and Byte Enable (CBE [3:0]); bidirectional

- Bidirectional Parity (PAR); bidirectional

- Interface control

- Cycle Frame (FRAME#); bidirectional

- Initiator Ready (IRDY#); bidirectional

- Target Ready (TRDY#); bidirectional

- Stop (STOP#); bidirectional

- Initialization Device Select (IDSEL); input

- Device Select (DEVSEL#); bidirectional

- Arbitration

- Request (REQ#); output

- Grant (GRANT#); input

- Error reporting

- Parity Error (PERR#); bidirectional

- System Error (SERR#); bidirectional

- Interrupt

- Interrupt A (INTA#); output

- System

- Clock (PCICLK); input

- Reset (PCIRST#): input

- Clock Running (CLKRUN#); input

- Power Management Event (PME#), output

## **Power Detection and Switching**

- Vaux Enable (VauxEN#); output

- Vpci Enable (VpciEN#); output

- Vpci Detect (VpciDET); input

- Vaux Detect (VauxDET); input

## **Serial EEPROM Interface**

A serial EEPROM is required to store the Device ID, Vendor ID, Subsystem ID, Subsystem Vendor ID, and Power Management parameters for the PCI Configuration Space Header.

The EEPROM must be 2048 (128 x 16) bits or larger and be rated at 1MHz (SROMCLK is 537.6 kHz). For example, the following EEPROMs or equivalent may be used: Microchip 93LC66B (256 x 16), 93LC56B (128 x 16), Atmel AT93C66 (256 x 16), AT93C56 (128 x 16). The EEPROM is programmable by the PC via the modem.

The EEPROM interface signals are:

- Serial Data Input (SROMIN): input

- Serial Data Output (SROMOUT); output

- Clock (SROMCLK); output

- Chip Select (SROMCS); output

### LSD Interface (Through DIB)

The DIB interface signals are:

- Clock and Power Positive (PWRCLKP); output

- Clock and Power Negative (PWRCLKN); output

- Data Positive (DIB\_DATAP); input/output

- Data Negative (DIB\_DATAN); input/output

## **VC Interface (S Models)**

The VC interface signals are:

- Modem Sleep (IASLEEP); output

- Master Clock (M CLK); output

- Voice Serial Clock (V\_SCLK); input

- Voice Serial Control (V\_CTRL); output

- Voice Serial Frame Sync (V\_STROBE); input

- Voice Serial Transmit Data (V\_TXSIN); output

- Voice Serial Receive Data (V RXOUT); input

## **Telephone Handset Interface (S Models)**

The telephone handset interface signals are:

- Voice Relay Control (VOICE#); output

- Handset Pickup Detect (H\_PICKUP); input

## **Call Progress Speaker Interface**

The call progress speaker interface signal is:

• Digital speaker output (DSPKOUT); output

DSPKOUT is a square wave output in Data/Fax mode used for call progress or carrier monitoring. This output can be optionally connected to a low-cost on-board speaker, e.g., a sounducer, or to an analog speaker circuit.

## PDC/PDC packet Interface

Nine lines, defined by the installed cell phone driver software, are available to support the PDC/PDC packet cellular phone interface:

- Panel 1

- Panel 2

- ADP

- CELL\_RXD

- CELL\_TXD

- TCH CLK

- TCH\_TX

- TCH\_RX

- TCH\_FRAME

## **PHS Interface**

Eleven lines, defined by the installed cell phone driver software, are available to support the PHS cellular phone interface.

- ASLP

- PSLP

- DFCK

- ReadyDSDT

- USDT

- BITC

- UDT

- DDT

- UFCK

#### **CDMA Interface**

Twelve lines, defined by the installed cell phone driver software, are available to support the CDMA cellular phone interface:

- Panel 1

- Panel 2

- CB

- CF

- CJ

- CC

- CE

- CD

- Control RXD

- Control TXD

- BB (USART IN)

- BA (USART OUT)

## **GSM Interface**

Five lines, defined by the installed cell phone driver software, are available to support the GSM phone interface:

- DA(IN)

- RX-A

- TX-A

- TX-A

- RX2-B USART

- TX2-B USART

## 3.1.2 HSD Interface Signals, Pin Assignments, and Signal Definitions

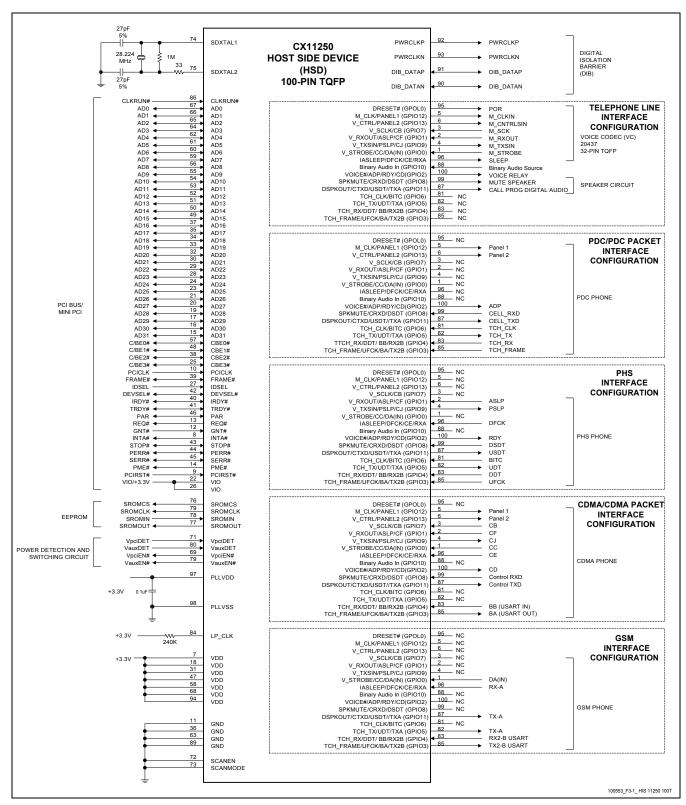

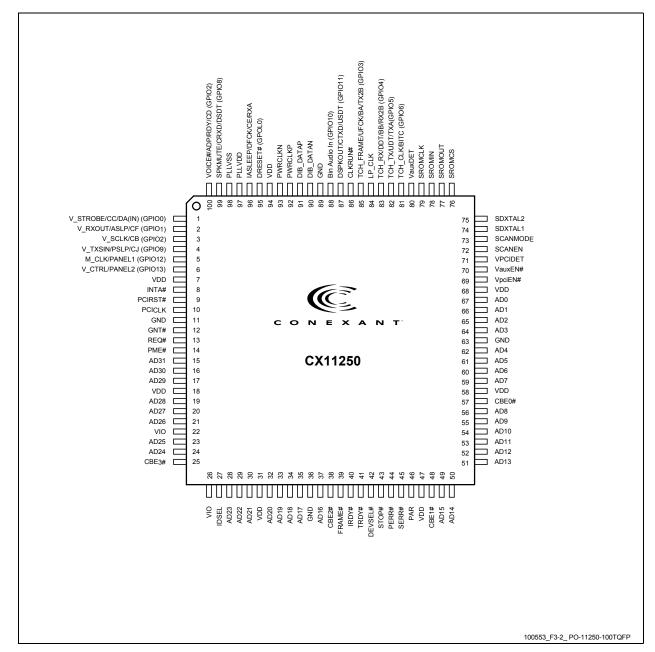

The CX11250 HSD 100-pin TQFP hardware interface signals are shown by major interface in Figure 3-1, are shown by pin number in Figure 3-2, and are listed by pin number in Table 3-1.

The CX11250 HSD hardware interface signals are defined in Table 3-2.

Cell phone/telephone line interface signal assignments are listed in Table 3-3.

Figure 3-1. CX11250 HSD Hardware Interface Signals

Figure 3-2. CX11250 HSD 100-Pin TQFP Pin Signals

Table 3-1. CX11250 HSD 100-Pin TQFP Pin Signals

| Pin | Signal Label        | I/O Type | Interface                                        | Pin | Signal Label             | I/O Type  | Interface                             |

|-----|---------------------|----------|--------------------------------------------------|-----|--------------------------|-----------|---------------------------------------|

| 1   | V_STROBE/           | Itpd     | Telephone Line: VC M_STROBE                      | 51  | AD13                     | I/Opts    | PCI Bus: AD13                         |

|     | CC/                 | '        | CDMA Phone: CC                                   |     |                          |           |                                       |

|     | DA(IN) (GPIO0)      |          | GSM Phone: DA(IN)                                |     |                          |           |                                       |

| 2   | V_RXOUT/            | Itk      | Telephone Line: VC M_RXOUT                       | 52  | AD12                     | I/Opts    | PCI Bus: AD12                         |

|     | ASLP/               |          | PHS Phone: ASLP                                  |     |                          |           |                                       |

|     | CF (GPIO1)          |          | CDMA Phone: CF                                   |     |                          |           |                                       |

| 3   | V_SCLK/             | Itpd     | Telephone Line: VC M_SCK                         | 53  | AD11                     | I/Opts    | PCI Bus: AD11                         |

|     | CB (GPIO2)          |          | CDMA Phone: CB                                   |     |                          |           |                                       |

| 4   | V_TXSIN/            | Ot2      | Telephone Line: VC M_TXSIN                       | 54  | AD10                     | I/Opts    | PCI Bus: AD10                         |

|     | PSLP/<br>CJ (GPIO9) |          | PHS Phone: PSLP                                  |     |                          |           |                                       |

| 5   | M CLK/              | Ot2      | CDMA Phone: CJ                                   | 55  | AD9                      | 1/0-4-    | PCI Bus: AD9                          |

| 5   | PANEL1              | Otz      | VC Telephone Line: VC M_CLKIN PDC Phone: Panel 1 | 55  | AD9                      | I/Opts    | PCI Bus: AD9                          |

|     | (GPIO12)            |          | CDMA Phone: Panel 1                              |     |                          |           |                                       |

| 6   | V CTRL/             | Ot2      | Telephone Line: VC M CNTRLSIN                    | 56  | AD8                      | I/Opts    | PCI Bus: AD8                          |

| Ü   | PANEL2              | Otz      | PDC Phone: Panel 2                               | 00  | /\D0                     | "Opto     | 1 01 043. 700                         |

|     | (GPIO13)            |          | CDMA Phone: Panel 2                              |     |                          |           |                                       |

| 7   | VDD                 | PWR      | +3.3V                                            | 57  | CBE0#                    | I/Opts    | PCI Bus: CBE0#                        |

| 8   | INTA#               | Opod     | PCI Bus: INTA#                                   | 58  | VDD                      | PWR       | +3.3V                                 |

| 9   | PCIRST#             | lp       | PCI Bus: PCIRST#                                 | 59  | AD7                      | I/Opts    | PCI Bus: AD7                          |

| 10  | PCICLK              | lp       | PCI Bus: PCICLK                                  | 60  | AD6                      | I/Opts    | PCI Bus: AD6                          |

| 11  | GND                 | GND      | GND                                              | 61  | AD5                      | I/Opts    | PCI Bus: AD5                          |

| 12  | GNT#                | lpts     | PCI Bus: GNT#                                    | 62  | AD4                      | I/Opts    | PCI Bus: AD4                          |

| 13  | REQ#                | Opts     | PCI Bus: REQ#                                    | 63  | GND                      | GND       | GND                                   |

| 14  | PME#                | Opod     | PCI Bus: PME#                                    | 64  | AD3                      | I/Opts    | PCI Bus: AD3                          |

| 15  | AD31                | I/Opts   | PCI Bus: AD31                                    | 65  | AD2                      | I/Opts    | PCI Bus: AD2                          |

| 16  | AD30                | I/Opts   | PCI Bus: AD30                                    | 66  | AD1                      | I/Opts    | PCI Bus: AD1                          |

| 17  | AD29                | I/Opts   | PCI Bus: AD29                                    | 67  | AD0                      | I/Opts    | PCI Bus: AD0                          |

| 18  | VDD                 | PWR      | +3.3V                                            | 68  | VDD                      | PWR       | +3.3V                                 |

| 19  | AD28                | I/Opts   | PCI Bus: AD28                                    | 69  | VpciEN#                  | Ot2       | Pwr Detection/Switching Ckt           |

| 20  | AD27                | I/Opts   | PCI Bus: AD27                                    | 70  | VauxEN#                  | Ot2       | Pwr Detection/Switching Ckt           |

| 21  | AD26                | I/Opts   | PCI Bus: AD26                                    | 71  | VpciDET                  | Itpd      | Pwr Detection/Switching Ckt           |

| 22  | VIO                 | PWR      | PCI Bus: VI/O or +3.3V                           | 72  | SCANEN                   | Itpd      | GND                                   |

| 23  | AD25                | I/Opts   | PCI Bus: AD25                                    | 73  | SCANMODE                 | Itpd      | GND                                   |

| 24  | AD24                | I/Opts   | PCI Bus: AD24                                    | 74  | SDXTAL1                  | lx        | Crystal or Clock Circuit              |

| 25  | CBE3#               | I/Opts   | PCI Bus: CBE3#                                   | 75  | SDXTAL2                  | Ox        | Crystal or NC (if SDXTAL1 connected   |

|     |                     | - 10     |                                                  |     |                          |           | to Clock Circuit)                     |

| 26  | VIO                 | PWR      | PCI Bus: VI/O or +3.3V                           | 76  | SROMCS                   | Ot2       | SROM: Chip Select (CS)                |

| 27  | IDSEL               | lp       | PCI Bus: IDSEL                                   | 77  | SROMOUT                  | Ot2       | SROM: Data In (DI)                    |

| 28  | AD23                | I/Opts   | PCI Bus: AD23                                    | 78  | SROMIN                   | Itpu      | SROM: Data Out (DO)                   |

| 29  | AD22                | I/Opts   | PCI Bus: AD22                                    | 79  | SROMCLK                  | Ot2       | SROM: Clock (SK)                      |

| 30  | AD21                | I/Opts   | PCI Bus: AD21                                    | 80  | VauxDET                  | Itpd      | Pwr Detection/Switching Ckt           |

| 31  | VDD                 | PWR      | +3.3V                                            | 81  | TCH_CLK/<br>BITC (GPIO6) | Itpu/Ot12 | PDC Phone: TCH_CLK<br>PHS Phone: BITC |

| 32  | AD20                | I/Opts   | PCI Bus: AD20                                    | 82  | TCH_TX/<br>UDT/          | Itpu/Ot12 | PDC Phone: TCH_TX K PHS Phone: UDT    |

|     |                     |          |                                                  |     | TXA<br>(GPIO5)           |           | GSM Phone: TXA                        |

| 33  | AD19                | I/Opts   | PCI Bus: AD19                                    | 83  | TCH_RX/                  | Itpu/Ot12 | PDC Phone: TCH_RX                     |

|     |                     | 1        |                                                  |     | DDT/                     | · ·       | PHS Phone: DDT                        |

|     |                     |          |                                                  | 1   | BB/                      |           | CDMA Phone: BB_RXD                    |

|     |                     |          |                                                  | I   | RX2B                     |           | GSM Phone: RX2-B                      |

|     |                     |          |                                                  | 1   | (GPIO4)                  |           |                                       |

| 34  | AD18                | I/Opts   | PCI Bus: AD18                                    | 84  | LP_CLK                   | RC        | +3.3V through 240 KΩ                  |

Table 3-1. CX11250 HSD 100-Pin TQFP Pin Signals (Continued)

|     | 0:           | W0.T     | 1.4.5            |     |                                               | ,<br>,    | Literature                                                                                                                              |

|-----|--------------|----------|------------------|-----|-----------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Pin | Signal Label | I/O Type | Interface        | Pin | Signal Label                                  | I/O Type  | Interface                                                                                                                               |

| 35  | AD17         | I/Opts   | PCI Bus: AD17    | 85  | TCH_FRAME/<br>UFCK/<br>BA/<br>TX2B            | Itpu/Ot12 | PDC Phone: TCH_FRAME PHS Phone: UFCK CDMA Phone: BA_TXD GSM Phone: TX2-B                                                                |

|     |              |          |                  |     | (GPIO3)                                       |           |                                                                                                                                         |

| 36  | GND          | GND      | GND              | 86  | CLKRUN#                                       | I/Opod    | PCI Bus: CLKRUN#                                                                                                                        |

| 37  | AD16         | I/Opts   | PCI Bus: AD16    | 87  | DSPKOUT/<br>CTXD/<br>USDT/<br>TXA<br>(GPIO11) | Ot12      | Telephone Line: Spkr circuit PDC Phone: CELL_TXD PHS Phone: USDT CDMA Phone: Control TXD GSM: TX-A                                      |

| 38  | CBE2#        | I/Opts   | PCI Bus: CBE2#   | 88  | Bin Audio In<br>(GPIO10)                      | Itpu      | Line Interface: Binary Audio Source                                                                                                     |

| 39  | FRAME#       | I/Opsts  | PCI Bus: FRAME#  | 89  | GND                                           | GND       | GND                                                                                                                                     |

| 40  | IRDY#        | I/Opsts  | PCI Bus: IRDY#   | 90  | DIB_DATAN                                     | ldd/Odd   | DIB: Data Negative Channel                                                                                                              |

| 41  | TRDY#        | I/Opsts  | PCI Bus: TRDY#   | 91  | DIB_DATAP                                     | ldd/Odd   | DIB: Data Positive Channel                                                                                                              |

| 42  | DEVSEL#      | I/Opsts  | PCI Bus: DEVSEL# | 92  | PWRCLKP                                       | Odpc      | DIB: Transformer primary winding non-dotted terminal                                                                                    |

| 43  | STOP#        | I/Opsts  | PCI Bus: STOP#   | 93  | PWRCLKN                                       | Odpc      | DIB: Transformer primary winding dotted terminal                                                                                        |

| 44  | PERR#        | I/Opsts  | PCI Bus: PERR#   | 94  | VDD                                           | PWR       | +3.3V                                                                                                                                   |

| 45  | SERR#        | I/Opod   | PCI Bus: SERR#   | 95  | DRESET#<br>(GPOL0)                            | Ot2       | VC: POR                                                                                                                                 |

| 46  | PAR          | I/Opts   | PCI Bus: PAR     | 96  | IASLEEP/<br>DFCK/<br>CE/<br>RXA               | Ot2       | Telephone Line: VC SLEEP<br>PHS Phone: DFCK<br>CDMA Phone: CE<br>GSM Phone: RX-A                                                        |

| 47  | VDD          | PWR      | +3.3V            | 97  | PLLVDD                                        | PWR       | +3.3V and to GND through 0.1 μF                                                                                                         |

| 48  | CBE1#        | I/Opts   | PCI Bus: CBE1#   | 98  | PLLVSS                                        | GND       | GND                                                                                                                                     |

| 49  | AD15         | I/Opts   | PCI Bus: AD15    | 99  | SPKMUTE/<br>CRXD/<br>DSDT (GPIO8)             | lt/Ot12   | Telephone Line: Spkr Circuit (Out);<br>Vaux Mode Power Select (In)<br>PDC Phone: CELL_RXD<br>PHS Phone: DSDT<br>CDMA Phone: Control RXD |

| 50  | AD14         | I/Opts   | PCI Bus: AD14    | 100 | VOICE#/ADP/<br>RDY/CD (GPIO2)                 | Ot12      | Telephone Line: Voice Relay Control<br>PDC Phone: ADP<br>PHS Phone: RDY<br>CDMA Phone: CD                                               |

| NOTES:           |                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------|

| 1. I/O Types     |                                                                                                          |

| I/Opod           | Digital input/output, PCI, open drain (PCI type = o/d)                                                   |

| I/Opsts          | Digital input/output, PCI, sustained three-state (PCI type = s/t/s)                                      |

| I/Opts           | Digital input/output, PCI, three-state (PCI type = t/s)                                                  |

| ldd              | input, DIB, data channel                                                                                 |

| lp               | Digital input, PCI, totem pole (PCI type = in)                                                           |

| Ipts             | Digital input, PCI, (PCI type = t/s)                                                                     |

| It               | Digital input, TTL-compatible                                                                            |

| ltk              | Digital input, TTL-compatible, internal keeper                                                           |

| Itpd             | Digital input, TTL-compatible, internal 75k $\pm$ 25k $\Omega$ pull-down                                 |

| Itpu             | Digital input, TTL-compatible, internal 75k $\pm$ 25k $\Omega$ pull-up                                   |

| It/Ot2           | Digital input, TTL-compatible/digital output, TTL-compatible, 2 mA, $Z_{INTERNAL}$ = 120 $\Omega$        |

| It/Ot12          | Digital input, TTL-compatible/digital output, TTL-compatible, 12 mA, $Z_{\mbox{INTERNAL}}$ = 32 $\Omega$ |

| lx               | Crystal/clock input                                                                                      |

| Odpc             | Output, DIB power and clock channel                                                                      |

| Odd              | Output, DIB data channel                                                                                 |

| Ood              | Digital output, open drain                                                                               |

| Opod             | Digital output, PCI, open drain (PCI type =o/d)                                                          |

| Opts             | Digital output, PCI, three-state (PCI type = t/s)                                                        |

| Ot2              | Digital output, TTL-compatible, 2 mA, $Z_{\text{INTERNAL}}$ = 120 $\Omega$                               |

| Ot12             | Digital output, TTL-compatible, 12 mA, $Z_{INTERNAL}$ = 32 $\Omega$                                      |

| Ox               | Crystal output                                                                                           |

| 2. Interface L   |                                                                                                          |

| NC               | No internal pin connection                                                                               |