# CXD1804AR

### **CD-ROM Decoder**

#### Description

The CXD1804AR is a CD-ROM decoder LSI with a built-in Fast SCSI controller.

#### **Features**

- Fast SCSI controller (Target mode)

- Maximum transfer speed of 10MB/s (when using Fast SCSI synchronous transfer)

- SCSI overhead reduced by executing multiple SCSI sequences

- Supports SCAM Level 2

- Compatible with CD-ROM, CD-I and CD-ROM XA formats

- Real-time error correction

- Capable of handling up to twelvefold-speed playback

- Multiblock auto-transfer function

- Can read subcode-Q data for each byte from the sub CPU

- Real-time subcode (R to W) error correction

- Serial transfer of commands to CD DSP

- Connectable with standard DRAM of up to 8M bits (1024K bytes)

- DRAM bit width selectable for 8 bits or 16 bits

#### **Absolute Maximum Ratings** (Ta = 25°C)

| <ul> <li>Supply voltage</li> </ul>      | $V_{DD}$ | -0.5 to $+7.0$                | V  |

|-----------------------------------------|----------|-------------------------------|----|

| <ul> <li>Input voltage</li> </ul>       | Vı       | -0.5 to V <sub>DD</sub> + 0.5 | V  |

| <ul> <li>Output voltage</li> </ul>      | Vo       | -0.5 to V <sub>DD</sub> + 0.5 | V  |

| • Operating temperature                 | Topr     | -20 to +75                    | °C |

| <ul> <li>Storage temperature</li> </ul> | Tstg     | -55 to +150                   | °C |

#### **Recommended Operating Conditions**

#### **Applications**

**CD-ROM drives**

#### **Structure**

Silicon gate CMOS IC

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

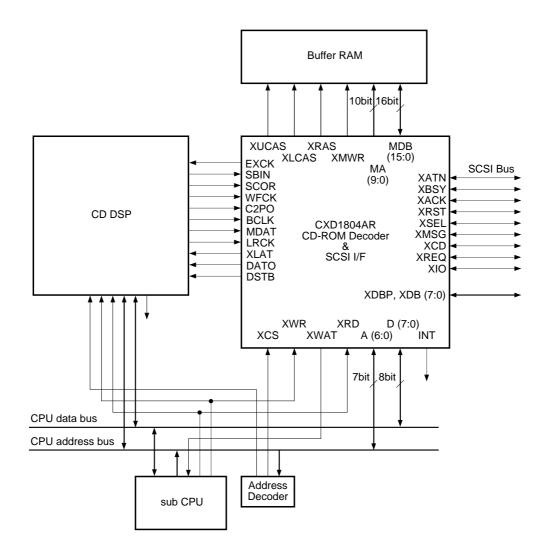

### **Connection Example**

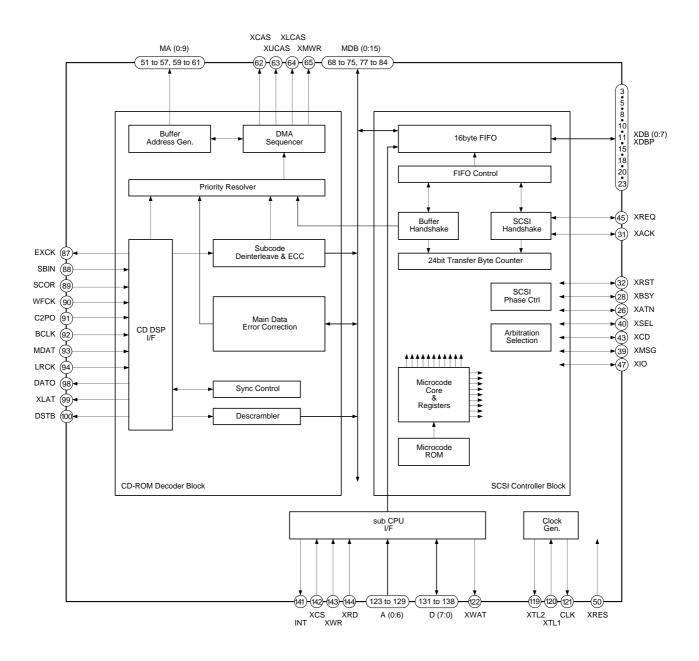

#### **Block Diagram**

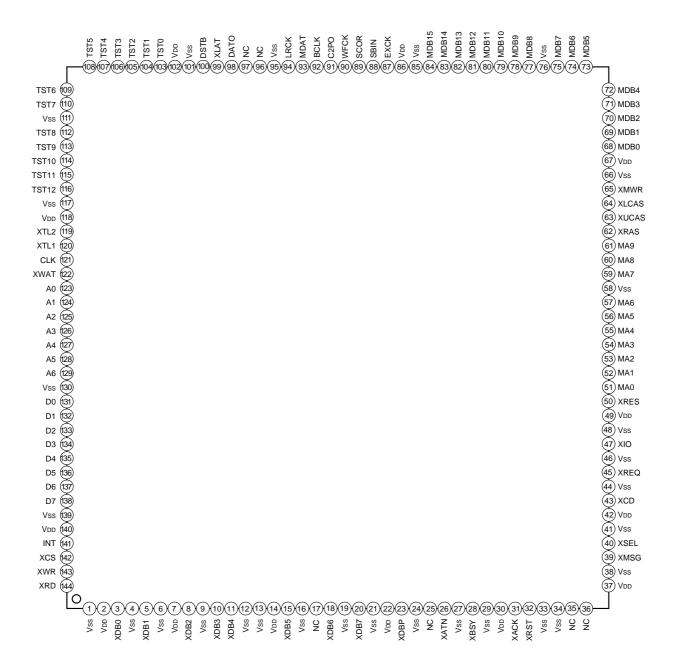

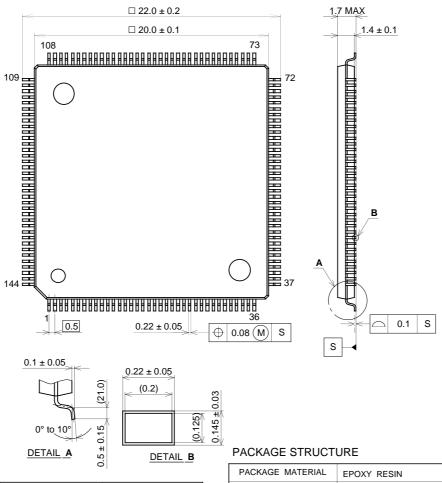

### **Pin Configuration**

### **Pin Description**

| Pin<br>No. | Symbol | I/O | Logic    | Classification | Description                  |

|------------|--------|-----|----------|----------------|------------------------------|

| 1          | Vss    |     | _        | Power          | Vss                          |

| 2          | VDD    | _   | _        | Power          | VDD                          |

| 3          | XDB0   | I/O | Negative | SCSI I/F       | SCSI data bus bit 0          |

| 4          | Vss    | _   | _        | Power          | Vss                          |

| 5          | XDB1   | I/O | Negative | SCSI I/F       | SCSI data bus bit 1          |

| 6          | Vss    | _   | _        | Power          | Vss                          |

| 7          | VDD    | _   | _        | Power          | VDD                          |

| 8          | XDB2   | I/O | Negative | SCSI I/F       | SCSI data bus bit 2          |

| 9          | Vss    |     | _        | Power          | Vss                          |

| 10         | XDB3   | I/O | Negative | SCSI I/F       | SCSI data bus bit 3          |

| 11         | XDB4   | I/O | Negative | SCSI I/F       | SCSI data bus bit 4          |

| 12         | Vss    | _   | _        | Power          | Vss                          |

| 13         | Vss    | _   | _        | Power          | Vss                          |

| 14         | VDD    | _   | _        | Power          | VDD                          |

| 15         | XDB5   | I/O | Negative | SCSI I/F       | SCSI data bus bit 5          |

| 16         | Vss    | _   | _        | Power          | Vss                          |

| 17         | NC     | _   | _        | NC             | NC                           |

| 18         | XDB6   | I/O | Negative | SCSI I/F       | SCSI data bus bit 6          |

| 19         | Vss    | _   | _        | Power          | Vss                          |

| 20         | XDB7   | I/O | Negative | SCSI I/F       | SCSI data bus bit 7          |

| 21         | Vss    | _   | _        | Power          | Vss                          |

| 22         | VDD    | _   | _        | Power          | VDD                          |

| 23         | XDBP   | I/O | Negative | SCSI I/F       | SCSI data bus parity         |

| 24         | Vss    | _   | _        | Power          | Vss                          |

| 25         | NC     | _   | _        | NC             | NC                           |

| 26         | XATN   | I/O | Negative | SCSI I/F       | SCSI control bus XATN signal |

| 27         | Vss    | _   | _        | Power          | Vss                          |

| 28         | XBSY   | I/O | Negative | SCSI I/F       | SCSI control bus XBSY signal |

| 29         | Vss    | _   | _        | Power          | Vss                          |

| 30         | Vdd    | _   | _        | Power          | VDD                          |

| 31         | XACK   | I/O | Negative | SCSI I/F       | SCSI control bus XACK signal |

| 32         | XRST   | I/O | Negative | SCSI I/F       | SCSI control bus XRST signal |

| 33         | Vss    | _   | _        | Power          | Vss                          |

| 34         | Vss    | _   | _        | Power          | Vss                          |

| 35         | NC     | _   | _        | NC             | NC                           |

| 36         | NC     | _   | _        | NC             | NC                           |

| Pin<br>No. | Symbol | I/O | Logic    | Classification | Description                                      |

|------------|--------|-----|----------|----------------|--------------------------------------------------|

| 37         | VDD    | _   | _        | Power          | VDD                                              |

| 38         | Vss    | _   | _        | Power          | Vss                                              |

| 39         | XMSG   | I/O | Negative | SCSI I/F       | SCSI control bus XMSG signal                     |

| 40         | XSEL   | I/O | Negative | SCSI I/F       | SCSI data bus XSEL signal                        |

| 41         | Vss    | _   | _        | Power          | Vss                                              |

| 42         | VDD    | _   | _        | Power          | VDD                                              |

| 43         | XCD    | I/O | Negative | SCSI I/F       | SCSI control bus XCD signal                      |

| 44         | Vss    | _   | _        | Power          | Vss                                              |

| 45         | XREQ   | I/O | Negative | SCSI I/F       | SCSI control bus XREQ signal                     |

| 46         | Vss    | _   | _        | Power          | Vss                                              |

| 47         | XIO    | I/O | Negative | SCSI I/F       | SCSI control bus XIO signal                      |

| 48         | Vss    | _   | _        | Power          | Vss                                              |

| 49         | VDD    | _   | _        | Power          | VDD                                              |

| 50         | XRES   | I   | Negative | System I/F     | CXD1804AR reset signal                           |

| 51         | MA0    | 0   |          | BufMem I/F     | Address bus output bit 0 to buffer memory        |

| 52         | MA1    | 0   |          | BufMem I/F     | Address bus output bit 1 to buffer memory        |

| 53         | MA2    | 0   |          | BufMem I/F     | Address bus output bit 2 to buffer memory        |

| 54         | MA3    | 0   |          | BufMem I/F     | Address bus output bit 3 to buffer memory        |

| 55         | MA4    | 0   |          | BufMem I/F     | Address bus output bit 4 to buffer memory        |

| 56         | MA5    | 0   |          | BufMem I/F     | Address bus output bit 5 to buffer memory        |

| 57         | MA6    | 0   |          | BufMem I/F     | Address bus output bit 6 to buffer memory        |

| 58         | Vss    |     | _        | Power          | Vss                                              |

| 59         | MA7    | 0   |          | BufMem I/F     | Address bus output bit 7 to buffer memory        |

| 60         | MA8    | 0   |          | BufMem I/F     | Address bus output bit 8 to buffer memory        |

| 61         | MA9    | 0   |          | BufMem I/F     | Address bus output bit 9 to buffer memory        |

| 62         | XRAS   | 0   | Negative | BufMem I/F     | Buffer memory RAS (Row Address Strobe) signal    |

| 63         | XUCAS  | 0   | Negative | BufMem I/F     | Buffer memory CAS (Column Address Strobe) signal |

| 64         | XLCAS  | 0   | Negative | BufMem I/F     | Buffer memory CAS (Column Address Strobe) signal |

| 65         | XMWR   | 0   | Negative | BufMem I/F     | Data write strobe signal to buffer memory        |

| 66         | Vss    |     | _        | Power          | Vss                                              |

| 67         | VDD    | _   | _        | BufMem I/F     | VDD                                              |

| 68         | MDB0   | I/O |          | BufMem I/F     | Buffer memory data bus bit 0                     |

| 69         | MDB1   | I/O |          | BufMem I/F     | Buffer memory data bus bit 1                     |

| 70         | MDB2   | I/O |          | BufMem I/F     | Buffer memory data bus bit 2                     |

| 71         | MDB3   | I/O |          | BufMem I/F     | Buffer memory data bus bit 3                     |

| 72         | MDB4   | I/O |          | BufMem I/F     | Buffer memory data bus bit 4                     |

| 73         | MDB5   | I/O |          | BufMem I/F     | Buffer memory data bus bit 5                     |

| Pin<br>No. | Symbol | I/O | Logic | Classification | Description                                                               |

|------------|--------|-----|-------|----------------|---------------------------------------------------------------------------|

| 74         | MDB6   | I/O |       | BufMem I/F     | Buffer memory data bus bit 6                                              |

| 75         | MDB7   | 1/0 | _     | BufMem I/F     | Buffer memory data bus bit 7                                              |

| 76         | Vss    |     |       | Power          | Vss                                                                       |

| 77         | MDB8   | 1/0 |       | BufMem I/F     | Buffer memory data bus bit 8                                              |

| 78         | MDB9   | I/O |       | BufMem I/F     | Buffer memory data bus bit 9                                              |

| 79         | MDB10  | 1/0 |       | BufMem I/F     | Buffer memory data bus bit 10                                             |

| 80         | MDB11  | 1/0 |       | BufMem I/F     | Buffer memory data bus bit 11                                             |

| 81         | MDB12  | I/O |       | BufMem I/F     | Buffer memory data bus bit 12                                             |

| 82         | MDB13  | I/O |       | BufMem I/F     | Buffer memory data bus bit 13                                             |

| 83         | MDB14  | I/O |       | BufMem I/F     | Buffer memory data bus bit 14                                             |

| 84         | MDB15  | I/O |       | BufMem I/F     | Buffer memory data bus bit 15                                             |

| 85         | Vss    | _   | _     | Power          | Vss                                                                       |

| 86         | VDD    | _   | _     | Power          | VDD                                                                       |

| 87         | EXCK   | 0   |       | CD DSP I/F     | SBIN read clock (connected to the EXCK pin (Pin 65) of the CXD2500)       |

| 88         | SBIN   | I   |       | CD DSP I/F     | Subcode serial signal (connected to the SBSO pin (Pin 64) of the CXD2500) |

| 89         | SCOR   | I   |       | CD DSP I/F     | Subcode sync signal (connected to the SCOR pin (Pin 63) of the CXD2500)   |

| 90         | WFCK   | I   |       | CD DSP I/F     | Write frame clock (connected to the WFCK pin (Pin 62) of the CXD2500)     |

| 91         | C2PO   | I   |       | CD DSP I/F     | Indicates that an error exists in C2 pointer signal MDAT.                 |

| 92         | BCLK   | I   |       | CD DSP I/F     | Bit clock. MDAT strobe signal.                                            |

| 93         | MDAT   | I   |       | CD DSP I/F     | Serial data stream from CD DSP                                            |

| 94         | LRCK   | I   |       | CD DSP I/F     | LR signal. Indicates MDAT L or R channel.                                 |

| 95         | Vss    | _   | _     | Power          | Vss                                                                       |

| 96         | NC     | _   | _     | NC             | NC                                                                        |

| 97         | NC     | _   | _     | NC             | NC                                                                        |

| 98         | DATO   | 0   |       | CD DSP I/F     | Serial data output from sub CPU to CD DSP                                 |

| 99         | XLAT   | 0   |       | CD DSP I/F     | DATO latch signal. Latches at the rising edge.                            |

| 100        | DSTB   | 0   |       | CD DSP I/F     | DATO transfer clock                                                       |

| 101        | Vss    | _   | _     | Power          | Vss                                                                       |

| 102        | Vdd    | _   | _     | Power          | VDD                                                                       |

| 103        | TST0   | I   |       | Test I/F       | Test pin 0                                                                |

| 104        | TST1   | I   |       | Test I/F       | Test pin 1                                                                |

| 105        | TST2   | I   |       | Test I/F       | Test pin 2                                                                |

| 106        | TST3   | I   |       | Test I/F       | Test pin 3                                                                |

| 107        | TST4   | I   |       | Test I/F       | Test pin 4                                                                |

| Pin<br>No. | Symbol | I/O | Logic      | Classification | Description                                   |

|------------|--------|-----|------------|----------------|-----------------------------------------------|

| 108        | TST5   | I   |            | Test I/F       | Test pin 5                                    |

| 109        | TST6   | ı   |            | Test I/F       | Test pin 6                                    |

| 110        | TST7   | I   |            | Test I/F       | Test pin 7                                    |

| 111        | Vss    | _   | _          | Power          | Vss                                           |

| 112        | TST8   | ı   |            | Test I/F       | Test pin 8                                    |

| 113        | TST9   | ı   |            | Test I/F       | Test pin 9                                    |

| 114        | TST10  | ı   |            | Test I/F       | Test pin 10                                   |

| 115        | TST11  | ı   |            | Test I/F       | Test pin 11                                   |

| 116        | TST12  | ı   |            | Test I/F       | Test pin 12                                   |

| 117        | Vss    | _   | _          | Power          | Vss                                           |

| 118        | VDD    | _   | _          | Power          | VDD                                           |

| 119        | XTL2   | 0   |            | System I/F     | Crystal oscillation circuit output            |

| 120        | XTL1   | I   |            | System I/F     | Crystal oscillation circuit input             |

| 121        | CLK    | 0   |            | System I/F     | Clock output                                  |

| 122        | XWAT   | 0   | Negative   | sub CPU I/F    | Wait signal for sub CPU buffer memory access  |

| 123        | A0     | I   |            | sub CPU I/F    | CXD1804AR built-in register address bus bit 0 |

| 124        | A1     | I   |            | sub CPU I/F    | CXD1804AR built-in register address bus bit 1 |

| 125        | A2     | I   |            | sub CPU I/F    | CXD1804AR built-in register address bus bit 2 |

| 126        | A3     | I   |            | sub CPU I/F    | CXD1804AR built-in register address bus bit 3 |

| 127        | A4     | I   |            | sub CPU I/F    | CXD1804AR built-in register address bus bit 4 |

| 128        | A5     | I   |            | sub CPU I/F    | CXD1804AR built-in register address bus bit 5 |

| 129        | A6     | I   |            | sub CPU I/F    | CXD1804AR built-in register address bus bit 6 |

| 130        | Vss    | _   | _          | Power          | Vss                                           |

| 131        | D0     | I/O |            | sub CPU I/F    | Sub CPU data bus bit 0                        |

| 132        | D1     | I/O |            | sub CPU I/F    | Sub CPU data bus bit 1                        |

| 133        | D2     | I/O |            | sub CPU I/F    | Sub CPU data bus bit 2                        |

| 134        | D3     | I/O |            | sub CPU I/F    | Sub CPU data bus bit 3                        |

| 135        | D4     | I/O |            | sub CPU I/F    | Sub CPU data bus bit 4                        |

| 136        | D5     | I/O |            | sub CPU I/F    | Sub CPU data bus bit 5                        |

| 137        | D6     | I/O |            | sub CPU I/F    | Sub CPU data bus bit 6                        |

| 138        | D7     | I/O |            | sub CPU I/F    | Sub CPU data bus bit 7                        |

| 139        | Vss    | _   | _          | Power          | Vss                                           |

| 140        | Vdd    | _   | _          | Power          | VDD                                           |

| 141        | INT    | 0   | Selectable | sub CPU I/F    | Interrupt to sub CPU                          |

| 142        | XCS    | I   | Negative   | sub CPU I/F    | CXD1804AR chip select signal                  |

| 143        | XWR    | I   | Negative   | sub CPU I/F    | CXD1804AR built-in register write signal      |

| 144        | XRD    | ļ   | Negative   | sub CPU I/F    | CXD1804AR built-in register read signal       |

### **Electrical Characteristics**

$(VDD = 5V \pm 10\%, Vss = 0V, Topr = -20 \text{ to } +75^{\circ}C)$

| Item                                                     | Symbol           | Conditions       | Min.               | Тур.   | Max.               | Unit     | Applicable pins |

|----------------------------------------------------------|------------------|------------------|--------------------|--------|--------------------|----------|-----------------|

| TTL input level pin<br>High level input voltage          | VIH1             |                  | 2.2                |        |                    | ٧        | *1              |

| TTL input level pin<br>Low level input voltage           | VIL1             |                  |                    |        | 0.8                | ٧        | *1              |

| CMOS input level pin<br>High level input voltage         | V <sub>IH2</sub> |                  | 0.7VDD             |        |                    | ٧        | *2              |

| CMOS input level pin<br>Low level input voltage          | VIL2             |                  |                    |        | 0.3Vpd             | V        | *2              |

| CMOS Schmitt input level pin<br>High level input voltage | VIH4             |                  | 0.8VDD             |        |                    | V        | *3              |

| CMOS Schmitt input level pin Low level input voltage     | VIL4             |                  |                    |        | 0.2VDD             | V        | *3              |

| CMOS Schmitt input level pin Input voltage hysteresis    | VIH4 — VIL4      |                  |                    | 0.6    |                    | V        | *3              |

| TTL Schmitt input level pin<br>High level input voltage  | VIH5             |                  | 2.2V               |        |                    | V        | *4              |

| TTL Schmitt input level pin Low level input voltage      | VIL5             |                  |                    |        | 0.8V               | V        | *4              |

| TTL Schmitt input level pin Input voltage hysteresis     | VIH5 — VIL4      |                  |                    | 0.4    |                    | <b>V</b> | *4              |

| SCSI Schmitt input level pin<br>High level input voltage | Vihs             |                  | 2.2V               |        |                    | <b>V</b> | *11             |

| SCSI Schmitt input level pin<br>Low level input voltage  | VILS             |                  |                    |        | 0.8V               | <b>V</b> | *11             |

| SCSI Schmitt input level pin Input voltage hysteresis    | VIHTS – VILTS    |                  |                    | 0.4    |                    | V        | *11             |

| Bidirectional pin with pull-up resistor Input current    | Іігз             | VIN = 0V         | -90                | -200   | -440               | μΑ       | *5              |

| High level output voltage                                | Vон1             | Iон = −2mA       | VDD - 0.8          |        |                    | V        | *6              |

| High level output voltage                                | Voн2             | Iон = −6mA       | VDD - 0.8          |        |                    | V        | *7              |

| SCSI high level output voltage                           | Vons             |                  | 2.5                |        | 3.7                | V        | *12             |

| Low level output voltage                                 | Vol1             | IoL = 4mA        |                    |        | 0.4                | V        | *8              |

| SCSI low level output voltage                            | Vols             | IoL = 48mA       |                    |        | 0.5                | ٧        | *11             |

| Input leakage current                                    | l <sub>11</sub>  | VIN = Vss or VDD | -10                |        | 10                 | μΑ       | *9              |

| Oscillation cell high level input voltage                | VIH4             |                  | 0.7V <sub>DD</sub> |        |                    | V        | *10             |

| Oscillation cell low level input voltage                 | VIL4             |                  |                    |        | 0.3VDD             | V        |                 |

| Oscillation cell logic threshold value                   | LVтн             |                  |                    | 0.5Vdd |                    | V        |                 |

| Oscillation cell feedback resistance value               | RfB              | VIN = Vss or VDD | 250k               | 1M     | 2.5M               | Ω        |                 |

| Oscillation cell high level output voltage               | Vонз             | Iон = −12mA      | 0.5V <sub>DD</sub> |        |                    | V        |                 |

| Oscillation cell low level output voltage                | Vol3             | IoL = 12mA       |                    |        | 0.5V <sub>DD</sub> | V        |                 |

- \*1 D7 to 0, MDBF to 0

- \*2 MDAT, LRCK, C2PO, SBIN, SCOR, TD12 to 0

- \*3 BLCK, WFCK, XRES

- \*4 A6 to 0, XWR, XRD, XCS

- \*5 D7 to 0, MDBF to 0

- \*6 All output pins except XTL2, XRAS, XUCAS, XLCAS, XMWR and CLK

- \*7 XRAS, XUCAS, XLCAS, XMWR, CLK

- \*8 All output pins except XTL2

- \*9 All input pins except \*5 and XTL1

- \*10 Input: XTL1, Output: XTL2

- \*11 XRST, XBSY, XSEL, XATN, XMSG, XCD, XIO, XREQ, XACK, XDBP, XDB7 to 0

- \*12 XREQ, XACK, XDBP and XDB7 to 0 when active negation is ON

### I/O Capacitance

$$(VDD = VI = 0V, f = 1MHz)$$

| Item               | Symbol | Min. | Тур. | Max. | Unit |

|--------------------|--------|------|------|------|------|

| Input capacitance  | CIN    |      |      | 9    | pF   |

| Output capacitance | Соит   |      |      | 11   | pF   |

| I/O capacitance    | Cı/o   |      |      | 11   | pF   |

### **AC Characteristics**

### 1. Sub CPU Interface (Output Load = 50pF)

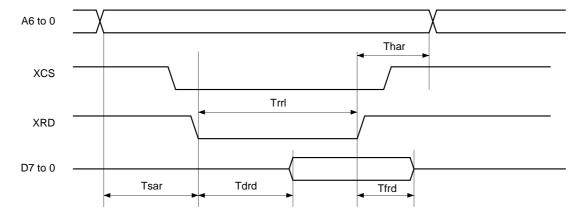

## (1) Read

| Item                                 | Symbol | Min. | Тур. | Max. | Unit |

|--------------------------------------|--------|------|------|------|------|

| Address setup time (for XCS & XRD ↓) | Tsar   | 10   |      |      | ns   |

| Address hold time (for XCS & XRD ↑)  | Thar   | 10   |      |      | ns   |

| Data delay time (for XCS & XRD ↓)    | Tdrd   |      |      | 35   | ns   |

| Data float time (for XCS & XRD ↑)    | Tfrd   | 0    |      | 15   | ns   |

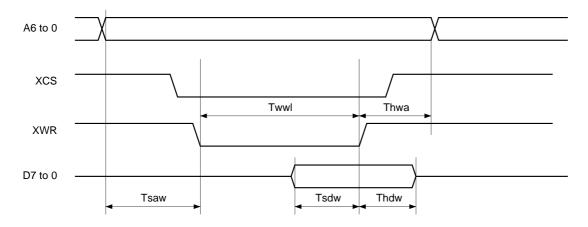

# (2) Write

| Item                                             | Symbol | Min. | Тур. | Max. | Unit |

|--------------------------------------------------|--------|------|------|------|------|

| Address setup time (for XCS & XWR $\downarrow$ ) | Tsaw   | 20   |      |      | ns   |

| Address hold time (for XCS & XWR ↑)              | Thaw   | 10   |      |      | ns   |

| Data setup time (for XCS & XWR ↓)                | Tsdw   | 20   |      |      | ns   |

| Data hold time (for XCS & XWR ↑)                 | Thdw   | 10   |      |      | ns   |

| Low level XWR pulse width                        | Twwl   | 30   |      |      | ns   |

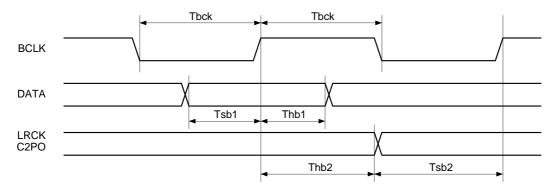

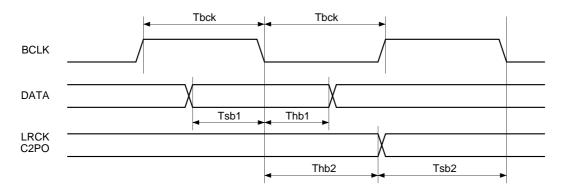

### 2. CD DSP Interface

### BCKRED = "H"

### BCKRED = "L"

| Item                             | Symbol | Min. | Тур. | Max. | Unit |

|----------------------------------|--------|------|------|------|------|

| BCLK frequency                   | Fbck   |      |      | 26   | ns   |

| BCLK pulse width                 | Tbck   | 19   |      |      | ns   |

| DATA setup time (for BCLK)       | Tsb1   | 10   |      |      | ns   |

| DATA hold time (for BCLK)        | Thb1   | 10   |      |      | ns   |

| LRCK, C2PO setup time (for BCLK) | Tsb2   | 10   |      |      | ns   |

| LRCK, C2PO hold time (for BCLK)  | Thb2   | 10   |      |      | ns   |

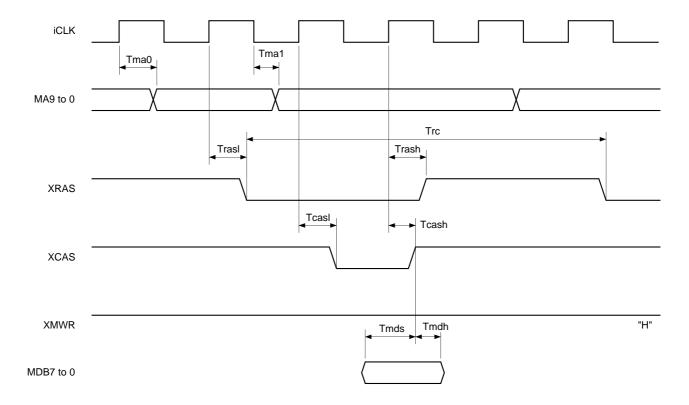

### 3. DRAM Interface

## (1) Read

| Item                                        | Symbol | Min. | Тур. | Max. | Unit |

|---------------------------------------------|--------|------|------|------|------|

| Random read/write cycle time                | Trc    | 5Tw  |      |      | ns   |

| Address delay time (for XTL2 ↑)             | Tma0   | 13   | 24   | 45   | ns   |

| Address delay time (for XTL2 $\downarrow$ ) | Tma1   | 11   | 22   | 41   | ns   |

| XRAS ↓ delay time (for XTL2 ↑)              | Trasl  | 6    | 12   | 23   | ns   |

| XRAS ↑ delay time (for XTL2 ↑)              | Trash  | 6    | 11   | 20   | ns   |

| XCAS ↓ delay time (for XTL2 ↑)              | Tcasl  | 7    | 14   | 25   | ns   |

| XCAS ↑ delay time (for XTL2 ↑)              | Tcash  | 6    | 12   | 22   | ns   |

| Data setup time (for XCAS ↑)                | Tmds   | 2    | 4    | 6    | ns   |

| Data hold time (for XCAS $\downarrow$ )     | Tmdh   | 0    |      |      | ns   |

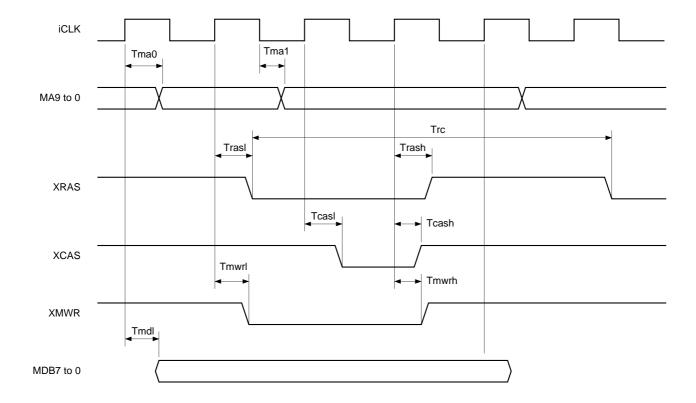

### (2) Write

| Item                                        | Symbol | Min. | Тур. | Max. | Unit |

|---------------------------------------------|--------|------|------|------|------|

| Random read/write cycle time                | Trc    | 5Tw  |      |      | ns   |

| Address delay time (for XTL2 ↑)             | Tma0   | 13   | 24   | 45   | ns   |

| Address delay time (for XTL2 $\downarrow$ ) | Tma1   | 11   | 22   | 41   | ns   |

| XRAS ↓ delay time (for XTL2 ↑)              | Trasl  | 6    | 12   | 23   | ns   |

| XRAS ↑ delay time (for XTL2 ↑)              | Trash  | 6    | 11   | 20   | ns   |

| XCAS ↓ delay time (for XTL2 ↑)              | Tcasl  | 7    | 14   | 25   | ns   |

| XCAS ↑ delay time (for XTL2 ↑)              | Tcash  | 6    | 12   | 22   | ns   |

| XMWR ↓ delay time (for XTL2 ↑)              | Tmwrl  | 7    | 14   | 25   | ns   |

| XMWR ↑ delay time (for XTL2 ↑)              | Tmwrh  | 6    | 11   | 21   | ns   |

| Data setup time (for XTL2 ↑)                | Tmdws  | 14   | 28   | 51   | ns   |

| Data hold time (for XTL2 ↑)                 | Tmdwh  | 7    | 14   | 26   | ns   |

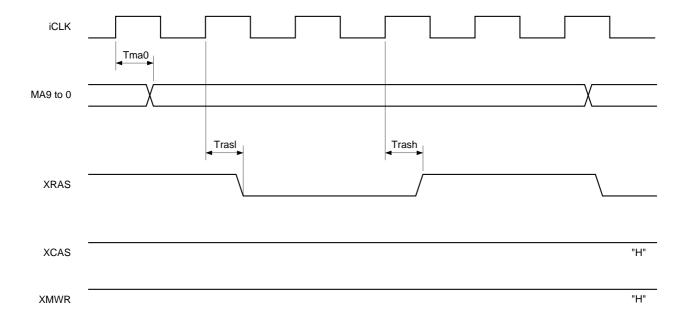

## (3) Refresh (RAS only refresh)

| Item                            | Symbol | Min. | Тур. | Max. | Unit |

|---------------------------------|--------|------|------|------|------|

| Random read/write cycle time    | Trc    | 5Tw  |      |      | ns   |

| Address delay time (for XTL2 ↑) | Tma0   | 12   | 24   | 43   | ns   |

| XRAS ↓ delay time (for XTL2 ↑)  | Tras1  | 6    | 12   | 23   | ns   |

| XRAS ↑ delay time (for XTL2 ↑)  | Trash  | 6    | 11   | 20   | ns   |

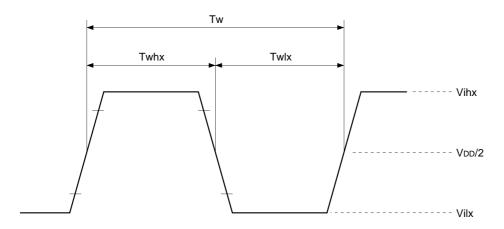

### 4. SCSI Interface

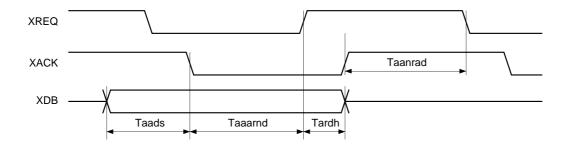

### (1) SCSI asynchronous transfer timing

When receiving: Initiator  $\rightarrow$  Target

When transmitting: Target  $\rightarrow$  Initiator

| Item                                          | Symbol  | Min. | Тур. | Max. | Unit |

|-----------------------------------------------|---------|------|------|------|------|

| XDB setup time (for XACK $\downarrow$ )       | Taads   | 15   |      |      | ns   |

| XDB hold time (for XREQ ↑)                    | Tardh   | 0    |      |      | ns   |

| XDB setup time (for XREQ $\downarrow$ )       | Tards   | 30   |      |      | ns   |

| XDB hold time (for XREQ $\downarrow$ )        | Taadh   | 60   |      |      | ns   |

| XREQ rise delay time (for XACK $\downarrow$ ) | Taaarnd | 30   |      | 70   | ns   |

| XREQ fall time (for XACK ↑)                   | Taanrad | 30   |      | 85   | ns   |

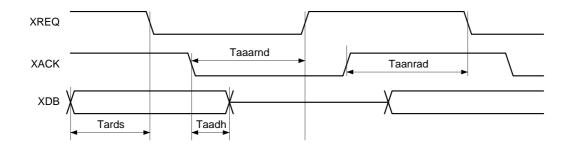

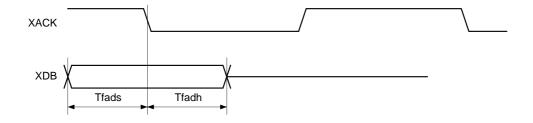

### (2) SCSI synchronous transfer timing

When receiving: Initiator  $\rightarrow$  Target

When transmitting: Target  $\rightarrow$  Initiator

| Item                                    | Symbol | Min. | Тур. | Max. | Unit |

|-----------------------------------------|--------|------|------|------|------|

| XDB setup time (for XACK ↓)             | Tnads  | 15   |      |      | ns   |

| XDB hold time (for XACK $\downarrow$ )  | Tnadh  | 10   |      |      | ns   |

| XDB setup time (for XREQ $\downarrow$ ) | Tnrds  | 80   |      |      | ns   |

| XDB hold time (for XREQ $\downarrow$ )  | Tnrdh  | 105  |      |      | ns   |

| XREQ assert time                        | Tnrap  |      |      | 110  | ns   |

| XREQ negate time                        | Tnrnp  | 90   |      |      | ns   |

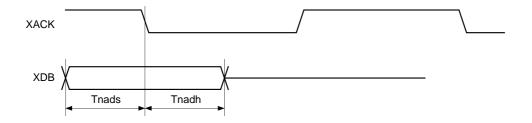

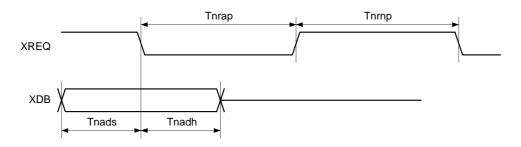

### (3) Fast SCSI synchronous transfer timing

When receiving: Initiator  $\rightarrow$  Target

When transmitting: Target  $\rightarrow$  Initiator

| Item                                    | Symbol | Min. | Тур. | Max. | Unit |

|-----------------------------------------|--------|------|------|------|------|

| XDB setup time (for XACK ↓)             | Tfads  | 15   |      |      | ns   |

| XDB hold time (for XACK $\downarrow$ )  | Tfadh  | 10   |      |      | ns   |

| XDB setup time (for XREQ $\downarrow$ ) | Tfrds  | 55   |      |      | ns   |

| XDB hold time (for XREQ $\downarrow$ )  | Tfrdh  | 55   |      |      | ns   |

| XREQ assert time                        | Tfrap  |      |      | 60   | ns   |

| XREQ negate time                        | Tfrnp  | 40   |      |      | ns   |

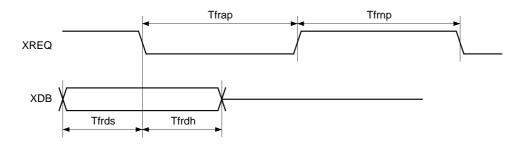

### 5. XTL1 and XTL2 Pins

### (1) When using self-excited oscillation

| Item                  | Symbol | Min. | Тур. | Max. | Unit |

|-----------------------|--------|------|------|------|------|

| Oscillation frequency | Fmax   |      |      | 40.0 | MHz  |

# (2) When inputting a pulse to the XTL1 pin

| Item                   | Symbol | Min. | Тур. | Max. | Unit |

|------------------------|--------|------|------|------|------|

| High level pulse width | Twhx   | 10   |      |      | ns   |

| Low level pulse width  | Twhx   | 10   |      |      | ns   |

| Pulse cycle            | Tw     | 25   |      |      | ns   |

### Contents

| [1] De: | scription of Registers                          | 21   |

|---------|-------------------------------------------------|------|

| 1-1.    | Description of Decoder Block Registers          | 21   |

| 1-2.    | Description of SCSI2 Controller Block Registers | 46   |

| 1-3.    | Common Registers                                | 60   |

| [2] De: | scription of SCSI Controller Block Commands     | 68   |

| 2-1.    | Precautions when Executing Commands             | . 69 |

|         | Category 00 Commands                            |      |

| 2-3.    | Category 01 Commands                            | 74   |

| 2-4.    | Category 10 Commands                            | 76   |

| 2-5.    | Category 11 Commands                            | 79   |

|         | pendix A                                        |      |

| 3-1.    | List of CD-ROM Decoder Block Registers          | 84   |

|         | List of SCSI Controller Block Registers         |      |

|         | List of Common Registers                        |      |

| 3-4.    | Register Reset Conditions                       | 96   |

| [4] Ap  | pendix B                                        | 102  |

| 4-1.    | Summary of SCSI Controller Block Commands       | 102  |

### [1] Description of Registers

The CXD1804AR's register address area is allotted as shown in the table below.

| Address    |                      | Description                                 |

|------------|----------------------|---------------------------------------------|

| 00h to 4Fh | 0xx xxxx<br>100 xxxx | CD-ROM decoder block                        |

| 50h to 6Fh | 101 xxxx<br>110 xxxx | SCSI2 interface block                       |

| 70h to 7Fh | 111 xxxx             | CD-ROM decoder/SCSI2 interface common block |

#### 1-1. Description of Decoder Block Registers

### 1-1-1. 00h

### (1) RAWMIN (raw minute) register (read)

RAWMIN (raw minute) register

| Adr.    | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Reg.   |

|---------|------|------|------|------|------|------|------|------|--------|

| 00h (R) |      |      |      |      |      |      |      |      | REWMIN |

The Header Minute byte for the sector being sent from the CD DSP while DECINT is active can be read from this register. A difference of two sectors exists between the RAWxxx and BFxxx registers during the write-only and real-time correction modes.

### (2) CONFIG0 (configuration 0) register (write)

CONFIG0 (configuration 0) register

| Adr.    | bit7        | bit6         | bit5         | bit4         | bit3        | bit2        | bit1        | bit0        | Reg.    |

|---------|-------------|--------------|--------------|--------------|-------------|-------------|-------------|-------------|---------|

| 00h (W) | CINT<br>POL | RAM<br>SIZE1 | RAM<br>SIZE0 | RAM8<br>BITW | RAM2<br>CAS | EXCK<br>SEL | CLK<br>SEL1 | CLK<br>SEL0 | CONFIG0 |

#### bit 7: CINTPOL (sub CPU interrupt polarity)

High: The INT pin becomes active high. When the register is inactive, it goes low.

Low: The INT pin becomes active low. When the register is inactive, it goes to high impedance.

#### bits 6, 5: RAMSIZE1, 0 (DRAM size 1, 0)

Set these bits according to the total size of the DRAM connected to this IC.

| RAMSIZE1 | RAMSIZE0 | DRAM total size |

|----------|----------|-----------------|

| "L"      | "L"      | 1M bits         |

| "L"      | "H"      | 2M bits         |

| "H"      | "L"      | 4M bits         |

| "H"      | "H"      | 8M bits         |

### bit 4: RAM8BITW (DRAM 8-bit wide)

This bit is set according to the bit width of the DRAM data bus to be connected.

High: Set this bit high when the DRAM to be connected has the 8-bit width.

Low: Set this bit low when the DRAM to be connected has the 16-bit width.

(Set low when two 8-bit width DRAMs are connected in parallel.)

#### bit 3: RAM2CAS (DRAM 2 CAS)

When the DRAM bus width is 16 bits, set this bit according to the number of CAS and WE signals. When the DRAM bus width is 8 bits, this bit has no meaning.

High: Set this bit high when the IC is connected to a DRAM with 2 CAS signals and 1 WE signal.

Low: Set this bit low when the IC is connected to a DRAM with 1 CAS signal and 2 WE signals.

### bit 2: EXCKSEL (EXCK select)

This bit determines the frequency of the EXCK clock that is used to get the subcode from the CD DSP. This bit is set by the sub CPU on the basis of the playback speed and the clock frequency on the XTL1 pin. (The maximum frequency for EXCK is 1MHz.)

High: The EXCK frequency is 1/48 the frequency of the XTL1 pin. Set this bit high when the XTL1 frequency is greater than 32MHz.

Low: The EXCK frequency is 1/32 the frequency of the XTL1 pin. Set this bit low when the XTL1 frequency is less than 32MHz.

### bits 1, 0: CLKSEL1, 0 (CLK select 1, 0)

These bits determine the clock frequency output from the CLK pin.

| CLKSEL1 | CLKSEL0 | Clock frequency        |

|---------|---------|------------------------|

| "L"     | "L"     | Fixed to high          |

| "L"     | "H"     | 1/2 of XTL1            |

| "H"     | "L"     | Same frequency as XTL1 |

| "H"     | "H"     | RESERVED               |

#### 1-1-2. 01h

### (1) RAWSEC (raw second) register (read)

RAWSEC (raw second) register

| Adr.    | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Reg.   |

|---------|------|------|------|------|------|------|------|------|--------|

| 00h (R) |      |      |      |      |      |      |      |      | RAWSEC |

The Header Second byte for the sector being sent from the CD DSP while DECINT is active can be read from this register.

#### (2) CONFIG1 (configuration 1) register (write)

CONFIG1 (configuration 1) register

| Adr.    | bit7       | bit6        | bit5        | bit4        | bit3         | bit2 | bit1        | bit0        | Reg.    |

|---------|------------|-------------|-------------|-------------|--------------|------|-------------|-------------|---------|

| 00h (W) | SW<br>OPEN | SYC<br>NGC2 | SYC<br>NGC1 | SYC<br>NGC0 | HWKR<br>QDIS | "L"  | SBC<br>ECC1 | SBC<br>ECC0 | CONFIG1 |

#### bit 7: SWOPEN (sync window open)

High: The Sync mark detection window opens. In this case, the IC's internal Sync protection circuit is disabled.

Low: The Sync mark detection window is controlled by the IC's internal Sync protection circuit.

#### bits 6 to 4: SYCNGC2 to 0 (sync NG count 2 to 0)

The Sync mark detection window opens once the number of Sync marks specified by these bits is inserted. Setting a value of 1h or less for these bits is prohibited. (After a reset, these bits are set to 2h.)

CXD1804AR

#### bit 3 HWKRQDIS (host DMA weak request disable)

High: (For the send system command passed through a buffer)

When the FIFO does not have eight empty bytes or more, the DMA does not start to the FIFO from the buffer.

(For the receive system command passed through a buffer)

When the data of eight bytes or more are written (or the last data is written) in the FIFO, the DMA starts to the buffer from the FIFO.

Low: (For the send system command passed through a buffer)

When the FIFO is not filled with data, the DMA starts to the FIFO from the buffer.

(For the receive system command passed through a buffer)

The DMA starts to the buffer from the FIFO immediately after the data are written in the FIFO.

The number of times of the DMA execution for the host is reduced by setting this bit high.

(Because the page mode is always used.)

#### bit 2: RESERVED

Normally set low.

#### bits 1, 0: SBCECC1, 0 (subcode ECC 1, 0)

These two bits specify the error correction method when decoding the subcode.

| SBECC1 | SBECC0 | Subcode error correction           |

|--------|--------|------------------------------------|

| "X"    | "L"    | Error correction not performed.    |

| "L"    | "H"    | Single error correction performed. |

| "H"    | "H"    | Double error correction performed. |

#### 1-1-3, 02h

#### (1) RAWBLK (raw block) register (read)

RAWBLK (raw block) register

| Adr.    | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Reg.   |

|---------|------|------|------|------|------|------|------|------|--------|

| 02h (R) |      |      |      |      |      |      |      |      | RAWBLK |

The Header Block byte for the sector being sent from the CD DSP while DECINT is active can be read from this register.

#### (2) DSPIF (DSP interface) register (write)

DSPIF (DSP interface) register

| Adr.    | bit7         | bit6       | bit5       | bit4        | bit3        | bit2       | bit1 | bit0         | Reg.  |

|---------|--------------|------------|------------|-------------|-------------|------------|------|--------------|-------|

| 02h (W) | C2PO<br>L1st | LCH<br>LOW | BCK<br>RED | BCKL<br>MD1 | BCKL<br>MD0 | LSB<br>1st | "L"  | BFSH<br>DFSL | DSPIF |

This register controls the connection mode with the CD DSP. After the IC is reset, the sub CPU sets this register according to the CD DSP to be connected.

#### bit 7: C2PL1ST (C2PO lower byte first)

High: When two bytes of data are input, C2PO inputs the lower byte first followed by the upper byte.

Low: When two bytes of data are input, C2PO inputs the upper byte first followed by the lower byte. Here, "upper byte" means the upper 8 bits including MSB from the CD DSP and "lower byte" means the lower 8 bits including LSB from the CD DSP. For example, the Header minute byte is the lower byte and the second byte, the upper byte.

CXD1804AR

bit 6: LCHLOW (Lch low)

High: When LRCK is low, determined to be the left channel data.

Low: When LRCK is high, determined to be the right channel data.

bit 5: BCKRED (BLCK rising edge)

High: Data is strobed at the rising edge of BCLK.

Low: Data is strobed at the falling edge of BCLK.

bits 4, 3: BCKMD1, 0 (BCLK mode 1, 0)

These bits are set according to the number of clocks output for BCLK during 1/2 LCLK cycle by the CD digital signal processing LSI (CD DSP).

| BCKMD1 | BCKMD0 |              |

|--------|--------|--------------|

| "L"    | "L"    | 16BCLKs/WCLK |

| "L"    | "H"    | 24BCLKs/WCLK |

| "H"    | "X"    | 32BCLKs/WCLK |

bit 2: LSB1ST (LSB first)

High: Connected with the CD DSP which outputs data with LSB first.

Low: Connected with the CD DSP which outputs data with MSB first.

bit 1: RESERVED

Normally set low.

Any change to the bits in this register must be made in the decoder disable status. (After the IC is reset, the address is 28h.)

bit 0 BFSHDFSL (buffering subheader flag select)

High: The Sub Headers written two times are compared and, if they do not match, the result reports an error to bits 3 to 0 of BFHDRFLG.

Low: When the C2PO of the Sub Headers written two times are both high, that reports an error to the bits 3 to 0 of BFHDRFLG.

### 1-1-4. 03h

#### (1) RAWMD (raw mode) register (read)

RAWMD (raw mode) register

| Adr.    | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Reg.  |

|---------|------|------|------|------|------|------|------|------|-------|

| 03h (R) |      |      |      |      |      |      |      |      | RAWMD |

The Header Mode byte for the sector being sent from the CD DSP while DECINT is active can be read from this register.

#### (2) RFINTVL (refresh interval) register (write)

RFINTVL (refresh interval) register

| Adr.    | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Reg.    |

|---------|------|------|------|------|------|------|------|------|---------|

| 03h (W) | b7   | b6   | b5   | b4   | b3   | b2   | b1   | b0   | RFINTVL |

This register determines the refresh interval. The refresh interval is RFINTVL  $\times$  4  $\times$  TW. Here, TW represents the XTL1 clock frequency. Note that this IC performs RAS only refresh.

#### 1-1-5. 04h

### (1) BFMIN (buffer minute) register (read)

BFMIN (buffer minute) register

| Adr.    | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Reg.  |

|---------|------|------|------|------|------|------|------|------|-------|

| 04h (R) |      |      |      |      |      |      |      |      | BFMIN |

During the execution of a write-only or real-time error correction command and after execution of a repeat correction command, the Header Minute byte of the current sector can be read from this register. This register is invalid when the decoder is disabled or a monitor-only command is being executed.

### (2) DSPCTL (DSP control) register (write)

DSPCTL (DSP control) register

| Adr.    | bit7        | bit6        | bit5        | bit4        | bit3        | bit2 | bit1         | bit0         | Reg.   |

|---------|-------------|-------------|-------------|-------------|-------------|------|--------------|--------------|--------|

| 04h (W) | DSTB<br>SL1 | DSTB<br>SL0 | DIS<br>XLAT | XFR<br>BYT1 | XFR<br>BYT0 | "L"  | SBAI<br>TMSL | FAST<br>EXCK | DSPCTL |

#### bits 7, 6: DSTBSL1, 0

These bits determine the frequency of the DSTB and XLAT clocks used for passing data (DATO) to the CD DSP. The sub CPU sets these bits according to the frequency of the clock on the XTL1 pin. (The maximum frequency for DSTB is 1MHz.)

| DSTBDL1 | DSTBDL0 | Frequency    |

|---------|---------|--------------|

| 0       | 0       | 1/24 of XTL1 |

| 0       | 1       | 1/32 of XTL1 |

| 1       | 0       | 1/48 of XTL1 |

| 1       | 1       | 1/64 of XTL1 |

#### bit 5: DISXLAT (disable XLAT output)

High: After the contents of the DSPCMD register are transferred to the DSP, a latch pulse is not output from the XLAT pin. In this case, the sub CPU uses DSPCMDLT (bit 0 of the CHPCTL0 register) to output a latch pulse from the XLAT pin at the appropriate time.

Low: After the contents of the DSPCMD register are transferred to the DSP, a latch pulse is output from the XLAT pin.

#### bits 4, 3: XFRBYT1, 0 (transfer command byte length 1,0)

These bits determine the number of bytes in the command data (DSPCMD register) to be transferred to the CD DSP. The relationship between the settings and the number of transferred bytes is shown in the following table.

| XFRBYT1 | XFRBYT0 | Number of transferred bytes |

|---------|---------|-----------------------------|

| "L"     | "L"     | Prohibited                  |

| "L"     | "H"     | 1                           |

| "H"     | "L"     | 2                           |

| "H"     | "H"     | 3                           |

#### bits 2: RESERVED

Normally set low.

CXD1804AR

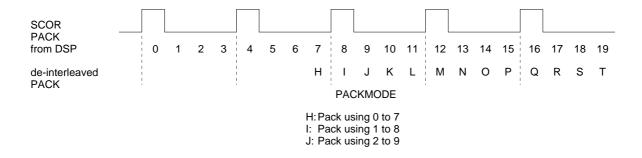

bit 1 SBAITMSL (subcode buffering area increment timing select)

High: The internal subcode buffering area is incremented when the first pack of data is retrieved and de-interleaving is performed.

Low: The internal subcode buffering are is incremented when the subcode Sync mark is detected and inserted.

bit 0 FASTEXCK (fast EXCK)

High: The EXCK frequency is 1/8 the frequency of the XTL1 pin.

Low: The EXCK frequency depends on the settings of EXCKSEL (CONFIG0 bit 2)

#### 1-1-6. 05h

#### (1) BFSEC (buffer second) register (read)

BFSEC (buffer second) register

| Adr.    | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Reg.  |

|---------|------|------|------|------|------|------|------|------|-------|

| 05h (R) |      |      |      |      |      |      |      |      | BFSEC |

During the execution of a write-only or real-time error correction command and after execution of a repeat correction command, the Header Second byte of the current sector can be read from this register. This register is invalid when the decoder is disabled or a monitor-only command is being executed.

#### (2) DSPCMD (DSP command) register (write)

DSPCMD (DSP command) register

| Adr.    | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Reg.   |

|---------|------|------|------|------|------|------|------|------|--------|

| 05h (W) | b7   | b6   | b5   | b4   | b3   | b2   | b1   | b0   | DSPCMD |

The data to be serially transferred to the CD DSP is written in this register. This register is a three-byte LIFO (last-in, first-out) register.

#### 1-1-7. 06h

#### (1) BFHDRBLK (buffer header block) register (read)

BFHDRBLK (buffer block) register

| Adr.    | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Reg.     |

|---------|------|------|------|------|------|------|------|------|----------|

| 06h (R) |      |      |      |      |      |      |      |      | BFHDRBLK |

During the execution of a write-only or real-time error correction command and after execution of a repeat correction command, the Header Block byte of the current sector can be read from this register. This register is invalid when the decoder is disabled or a monitor-only command is being executed.

#### 1-1-8. 07h

#### (1) BFMD (buffer mode) register (read)

BFMD (buffer mode) register

| Adr.    | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Reg. |

|---------|------|------|------|------|------|------|------|------|------|

| 07h (R) |      |      |      |      |      |      |      |      | BFMD |

During the execution of a write-only or real-time error correction command and after execution of a repeat correction command, the Header Mode byte of the current sector can be read from this register. This register is invalid when the decoder is disabled or a monitor-only command is being executed.

#### 1-1-9. 08h

### (1) BFFILE (buffer file) register (read)

BFFILE (buffer file) register

| Adr.    | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Reg.   |

|---------|------|------|------|------|------|------|------|------|--------|

| 08h (R) |      |      |      |      |      |      |      |      | BFFILE |

During the execution of a write-only or real-time error correction command and after execution of a repeat correction command, the Sub Header File byte of the current sector can be read from this register. This register is invalid when the decoder is disabled or a monitor-only command is being executed.

#### 1-1-10.09h

### (1) BFCHAN (buffer channel) register (read)

BFCHAN (buffer channel) register

| Adr.    | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Reg.   |

|---------|------|------|------|------|------|------|------|------|--------|

| 09h (R) |      |      |      |      |      |      |      |      | BFCHAN |

During the execution of a write-only or real-time error correction command and after execution of a repeat correction command, the Sub Header Channel byte of the current sector can be read from this register. This register is invalid when the decoder is disabled or a monitor-only command is being executed.

#### 1-1-11. 0Ah

#### (1) BFSUBM (buffer sub mode) register (read)

BFSUBM (buffer sub mode) register

| Adr.    | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Reg.   |

|---------|------|------|------|------|------|------|------|------|--------|

| 0Ah (R) |      |      |      |      |      |      |      |      | BFSUBM |

During the execution of a write-only or real-time error correction command and after execution of a repeat correction command, the Sub Header Sub Mode byte of the current sector can be read from this register. This register is invalid when the decoder is disabled or a monitor-only command is being executed.

#### 1-1-12, 0Bh

#### (1) BFDTYP (buffer data type) register (read)

BFDTYP (buffer data type) register

| Adr.    | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Reg.   |

|---------|------|------|------|------|------|------|------|------|--------|

| 0Bh (R) |      |      |      |      |      |      |      |      | BFDTYP |

During the execution of a write-only or real-time error correction command and after execution of a repeat correction command, the Sub Header Data Type byte of the current sector can be read from this register. This register is invalid when the decoder is disabled or a monitor-only command is being executed.

#### 1-1-13. 0Ch

### (1) RAWHDRFLG (raw header flag) register (read)

RAWHDRFLG (raw header flag) register

| Adr.    | bit7 | bit6 | bit5      | bit4 | bit3 | bit2 | bit1 | bit0        | Reg.   |

|---------|------|------|-----------|------|------|------|------|-------------|--------|

| 0Ch (R) | MIN  | SEC  | BLO<br>CK | MODE |      |      |      | CDR<br>DTEN | RAWHDR |

This register indicates the C2PO value for the RAWHDR register.

bit 7 Minute bit 6 Second

bit 5 Block bit 4 Mode

bit 4 Mode bit 3 to 1 RESERVED

bit 0 CD-R Mode Detect Enable

### (2) CDRMOD (CD-R mode) register (write)

CDRMOD (CD-R mode) register

| ſ | Adr.    | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0        | Reg.    |

|---|---------|------|------|------|------|------|------|------|-------------|---------|

|   | 0Ch (W) |      |      |      |      |      |      |      | CDR<br>DTEN | CDRMODE |

### bit 0 CDRDTEN (CD-R mode detect enable)

High: The CDRINT status results when the decoder is operating in the monitor-only, write-only, real-time correction or asynchronous correction mode if either of the conditions below is met.

- (1) Bits 7 to 5 of the Raw Mode byte are not "000".

- (2) The error flag of the Raw Mode byte is not established. (Values after processing by setting of MDBYTCTL (DECCTL0 bit 2))

Low: The CD-R Mode byte is not detected.

#### 1-1-14. 0Dh

#### (1) BFHDRFLG (buffer header flag) register (read)

BFHDRFLG (buffer header flag) register

| Adr.    | bit7 | bit6 | bit5      | bit4 | bit3 | bit2 | bit1        | bit0         | Reg.   |

|---------|------|------|-----------|------|------|------|-------------|--------------|--------|

| 0Dh (R) | MIN  | SEC  | BLO<br>CK | MODE | FILE | CHAN | SUB<br>MODE | DATA<br>TYPE | HDRFLG |

This register shows the error status of each byte in the BFHDR and BFSHDR registers. High means an error.

bit7 Minute bit6 Second bit5 **Block** bit4 Mode bit3 File bit2 Channel bit1 Submode bit0 Data Type

#### 1-1-15. 0Eh

#### (1) DECSTS0 (decoder status 0) register (read)

DECSTS0 (decoder status 0) register

| Adr.    | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Reg.    |

|---------|------|------|------|------|------|------|------|------|---------|

| 0Eh (R) |      |      |      |      |      |      |      |      | DECSTS0 |

#### bit 7: SHRTSCT (short sector)

Indicates that the Sync mark interval was less than 2351 bytes since the previous DECINT. This sector does not remain in the buffer memory.

#### bit 6: NOSYNC

Indicates that the Sync mark was inserted because one was not detected in the prescribed position for the current sector.

#### bit 5: CORINH (correction inhibit)

This is high if the current sector Mode and Form could not be determined when the AUTODIST bit of the DECCTL register is set high. ECC or EDC is not executed in this sector. The CORINH bit is invalid when AUTODIST is set low. It is high in any of the conditions below when the AUTODIST bit is set high.

- (1) When an error was found in the Mode byte.

- (2) When the Mode byte is a value other than 01h or 02h.

- (3) When the Mode byte is 02h and the C2 pointer is high in the Submode byte.

#### bit 4: ERINBLK (erasure in block)

When the decoder is operating in the monitor-only, write-only or real-time mode which prohibits erasure correction, this indicates that at least a 1-byte error flag (C2PO) has been raised in the data excluding the Sync mark from the current sector CD DSP.

#### bit 3: CORDONE (correction done)

Indicates that there is an error corrected byte in the current sector.

#### bit 2: EDCNG

Indicates that an error was found in the current sector through an EDC check.

#### bit 1: ECCNG

Indicates that an uncorrectable error was found somewhere between the Header byte and the Parity byte in the current sector. (Bit 1 = don't care in the Mode2, Form2 sectors.)

#### bit 0: TGTNTMET (target not met)

Indicates that the current sector address and the target address in the TGTMNT, TGTSEC, and TGTBLK registers do not match. The error pointer is not referenced in this instance.

#### 1-1-16. 0Fh

#### (1) DECSTS1 (decoder status 1) register (read)

DECSTS1 (decoder status 1) register

| Adr.    | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Reg.    |

|---------|------|------|------|------|------|------|------|------|---------|

| 0Fh (R) |      |      |      |      |      |      |      |      | DECSTS1 |

bits 7 to 3: RESERVED

bit 2: EDCALL0 (EDC all 0)

This is high when there are no error flags in all the 4 EDC parity bytes of the current sector and their values are all 00h.

bit 1: CMODE (correction mode)

bit 0: CFORM (correction form)

These bits indicate the Mode and Form of the current sector the decoder has discriminated to correct errors when the decoder is operating in the real-time correction or repeat correction mode.

| CFORM | CMODE |              |

|-------|-------|--------------|

| "X"   | "L"   | MODE1        |

| "L"   | "H"   | MODE2, FORM1 |

| "H"   | "H"   | MODE2, FORM2 |

#### 1-1-17. 10h, 11h

#### (1) LSTARA-H, L (last area-high, low) register (read/write)

LSTARA-H, L (last area-high, low) register

| Adr.      | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Reg.     |

|-----------|------|------|------|------|------|------|------|------|----------|

| 10h (R/W) |      |      |      |      |      |      |      | b8   | LSTARA-H |

| 11h (R/W) | b7   | b6   | b5   | b4   | b3   | b2   | b1   | b0   | LSTARA-L |

This register specifies the last order area. Set bits 7 to 1 of the LSTARA-H register low when writing in this register.

#### 1-1-18. 12h, 13h

### (1) LHADR-H, L (last HADR-high, low) register (read/write)

LHADR-H, L (last HADR-high, low) register

| Adr.      | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Reg.    |

|-----------|------|------|------|------|------|------|------|------|---------|

| 12h (R/W) |      |      |      |      |      |      |      | b8   | LHADR-H |

| 13h (R/W) | b7   | b6   | b5   | b4   | b3   | b2   | b1   | b0   | LHADR-L |

When host automatic transfer mode is disabled, this register specifies the upper limit for HADRC (the upper 9 bits); for the subcode buffering command, this register specifies the upper limit for the address (upper 9 bits). The lower 11 bits are 7FFh. Set bits 7 to 1 of the LHADR-H register low when writing in this register.

#### 1-1-19. 14h

#### (1) XFRFMT0 (transfer format 0) register (read/write)

XFRFMT0 (transfer format 0) register

| Adr.     | bit7           | bit6       | bit5 | bit4       | bit3         | bit2         | bit1       | bit0        | Reg.    |

|----------|----------------|------------|------|------------|--------------|--------------|------------|-------------|---------|

| 14h (R/\ | V) 1024<br>XFR | 512<br>XFR | SYNC | HEAD<br>ER | SBHE<br>ADER | USER<br>DATA | PARI<br>TY | AUTO<br>XFR | XFRFMT0 |

The transfer format for automatic data transfer is determined by this register. Before starting to transfer each sector, this IC reads the value of the SCTINF register written in the buffer memory. The buffer memory data is transferred to the host according to the read values and those in the XFRFMT1 and 0 registers. The Mode/Form of bits 3 to 1 depends on the values of bits 2 and 1 in the SCTINF register.

Regarding Mode2 in the Yellow Book, don't care the Form2 (bit 2) of the SCTINF register. Set bits 3 to 1 of the XFRFMT0 register high to transfer 2336 bytes of user data.

bit 7: 1024XFR

When this bit is set high, the user data (2048 bytes) is divided into 1024-byte blocks for transmission. In this case, set bits 6 to 1 in the XFRFMT0 register and bits 7 to 0 in the XFRFMT1 register low. In other words, the Sync mark, Header, Sub Header, and Parity bytes, as well as the block error flag, byte error flag, and subcode cannot be sent to the host. This transfer mode is not supported for Mode2/Form2 sectors.

bit 6: 512XFR (512 bytes transfer mode)

When this bit is set high, the user data (2048 bytes) is divided into 512-byte blocks for transmission. In this case, set bit 7 and bits 5 to 1 in the XFRFMT0 register and bits 7 to 0 in the XFRFMT1 register low. In other words, the Sync mark, Header, Sub Header, and Parity bytes, as well as the block error flag, byte error flag, and subcode cannot be sent to the host. This transfer mode is not supported for Mode2/Form2 sectors.

bit 5: SYNC

High: Sync marks are transferred to the host.

Low: Sync marks are not transferred to the host.

bit 4: HEADER

High: The four Header bytes are transferred to the host.

Low: The four Header bytes are not transferred to the host.

bit 3: SBHEADER

High: Mode1: This bit has no meaning.

Mode2: The eight Sub Header bytes are transferred to the host.

Low: The bytes indicated above are not transferred to the host.

bit 2: USERDATA (user data)

High: Mode1 and Mode2/Form1: User data (2048 bytes) is transferred to the host.

Mode2/Form2: User data (2324 bytes) is transferred to the host.

Low: The bytes indicated above are not transferred to the host.

bit 1: PARITY

High: Mode1: The EDC, ECC parity bytes and the eight 00h bytes, for a total of 288 bytes, are transferred to the host.

Mode2/Form1: The 280 EDC and ECC parity bytes are transferred to the host.

Mode2/Form2: The four reserved bytes (at the end of the sector) are transferred to the host.

Low: The bytes indicated above are not transferred to the host.

bit 0: AUTOXFR

Set this bit high when operating in automatic transfer mode. Set this bit low when operating in manual transfer mode. For CD-DA data, set 3Fh in this register when operating in automatic transfer mode.

CXD1804AR

#### 1-1-20. 15h

#### (1) XFRFMT1 (transfer format 1) register (read/write)

XFRFMT1 (transfer format 1) register

| Adr.      | bit7         | bit6         | bit5         | bit4         | bit3        | bit2       | bit1        | bit0       | Reg.    |

|-----------|--------------|--------------|--------------|--------------|-------------|------------|-------------|------------|---------|

| 15h (R/W) | ENBL<br>KEFL | BLKE<br>FLSL | ENBY<br>TFBT | BYTE<br>FLSL | ENSB<br>CBT | ALL<br>SBC | SBCE<br>STS | ZA<br>SQEF | XFRFMT1 |

bit 7: ENBLKEFL (enable block error flag)

High: The block error flag (1 byte) is transferred to the host.

Low: The byte indicated above is not transferred to the host.

bit 6: BLKEFLSL (block error flag select)

This bit is valid only when ENBLKEFL is high.

High: The value (one byte) written in the BLKESTS register by the sub CPU is transferred to the host as the block error flag.

Low: The OR value of each bit in the byte error flag is transferred to the host as the block error flag.

bit 5: ENBYTFBT (enable byte error flag buffering & transfer)

If this bit is set high, the operations described below are performed. If this bit is set low, the operations described below are not performed.

- (1) The byte error flag is buffered during execution of a write-only, real-time error correction, and CD-DA command.

- (2) When host automatic transfer mode is enabled (the AUTOXFR bit (bit 0) of the XFRFMT0 register is high), the byte error flag is transferred to the host.

The ENBYTFBT and BYTEFLSL bits are valid only when the USERDATA bit (bit 2) of the XFRFMT0 register is high.

bit 4: BYTEFLSL (byte error flag select)

This bit is valid only when ENBYTFBT is high. When this bit is set high, the value of BYTERSTS (the byte error status register, described later) is written in the byte error flag area of the buffer memory. Setting the BLKEFLSL bit low and the BYTEFLSL bit high at the same time is prohibited. If this bit is set low, the value of C2PO from the CD DSP is written in the byte error flag area.

bit 3: ENSBCBT (enable subcode buffering & transfer)

If this bit is set high, the operations described below are performed. If this bit is set low, the operations described below are not performed.

- (1) All subcodes or subcode-Q is buffered while the decoder executes CD-DA commands.

- (2) When host automatic transfer mode is enabled (the AUTOXFR bit (bit 0) of the XFRFMT0 register is high), all subcodes or subcode-Q is transferred to the host.

Note that buffering the CD-ROM data and the subcodes or subcode-Q at the same time is not supported.

bit 2: ALLSBC (all subcode/subcode-Q)

This determines whether to buffer and transfer all subcodes or subcode-Q to the host when ENSBCBT is high.

High: All subcodes Low: Subcode-Q

bit 1: SBCESTS (subcode error status)

This bit is valid only when ENSBCBT is high.

High: The value (one byte) written in the SBCESTS register by the sub CPU is transferred to the host.

Low: The byte indicated above is not transferred to the host.

bit 0: ZASQEF (zero after subcode-Q error flag)

This bit is valid only when ENSBCBT and SBCESTS are both high. (This bit is valid only when subcode-Q and the subcode error flag are transferred to the host.)

High: Five 00h bytes in addition to the subcode-Q error flag are transferred to the host.

Low: Five 00h bytes are not added to the subcode-Q error flag.

#### 1-1-21. 16h

#### (1) DECCTL0 (decoder control 0) register (read/write)

DECCTL0 (decoder control 0) register

| Adr.      | bit7         | bit6        | bit5        | bit4 | bit3         | bit2         | bit1      | bit0         | Reg.    |

|-----------|--------------|-------------|-------------|------|--------------|--------------|-----------|--------------|---------|

| 16h (R/W) | AUTO<br>DIST | MODE<br>SEL | FORM<br>SEL |      | ENFM<br>2EDC | MDBY<br>TCTL | EN<br>DLA | ATDL<br>RNEW | DECCTL0 |

bit 7: AUTODIST (auto distinction)

High: Errors are corrected according to the Mode byte and the Form bit read from the drive.

Low: Errors are corrected according to the MODESEL and FORMSEL bits (bits 6 and 5).

bit 6: MODESEL (mode select)

bit 5: FORMSEL (form select)

When AUTODIST is low, the sector is corrected in the Mode or Form indicated in the table below.

| MODESEL | FORMSEL |              |

|---------|---------|--------------|

| "L"     | "L"     | MODE1        |

| "H"     | "L"     | MODE2, FORM1 |

| "H"     | "H"     | MODE2, FORM2 |

bit 4: RESERVED

Always set low.

bit 3: ENFM2EDC (enable Form2 EDC check)

High: EDC check for Form2 is enabled.Low: EDC check for Form2 is disabled. The EDCNG bit of the DECSTS0 register goes low.

bit 2: MDBYTCTL (mode byte control)

High: Even if there are data other than "0" in the upper six bits of the Mode byte in the Header, an error does not result. Set this bit high when playing back discs such as CD-ROM.

Low: If the upper six bits of the Mode byte in the Header are not "000000", an error results.

#### bit 1: ENDLA (enable drive last area (address))

High: DLAR (Drive Last Area) is enabled. While the decoder is executing a write-only command, real-time error correction command, or CD-DA command, if buffering of the buffer memory area specified by DLAR is completed, the DRVOVRN (drive overrun) status results. Bufferwrite of subsequent sectors is then interrupted.

Also, while the decoder is executing a subcode buffering command, if data is written in the buffer memory address specified by SLADR, the DRVOVRN (Drive Overrun) status results. Buffer-write of subsequent sectors is then interrupted.

Low: DLAR (Drive Last Area) and SLADR are disabled when this is set low.

bit 0: ATDLRNEW (auto DLARA renewal)

High: When the data transfer to the host is completed for one sector, DLARA is renewed in the written area of the sector.

Low: DLARA is renewed by the sub CPU.

#### 1-1-22, 17h

#### (1) DECCTL1 (decoder control 1) register (read/write)

DECCTL1 (decoder control 1) register

| Adr.      | bit7        | bit6 | bit5        | bit4        | bit3        | bit2        | bit1        | bit0        | Reg.    |

|-----------|-------------|------|-------------|-------------|-------------|-------------|-------------|-------------|---------|

| 17h (R/W) | ENSB<br>QRD |      | DEC<br>CMD2 | DEC<br>CMD1 | DEC<br>CMD0 | NTCR<br>CT2 | NTCR<br>CT1 | NTCR<br>CT0 | DECCTL1 |

#### bit 7: ENSBQRD (enable subcode-Q read)

The subcode is fetched from the DSP and the subcode-Q CRC check is performed. The sub CPU can read the subcode-Q from the SUBQ register. Subcode decoding (de-interleave, error correction) is performed.

#### bit 6: RESERVED

Normally set low.

bits 5 to 3: DECCMD2 to 0 (decoder commands 2 to 0)

| DECCMD2 | DECCMD1     | DECCMD0 | Decoder command         |

|---------|-------------|---------|-------------------------|

| "L"     | 'L" "L" "L" |         | DECODER Disable         |

| "L"     | ." "L" "H"  |         | Monitor-only            |

| "L"     | "H"         | "L"     | Write-only              |

| "L"     | "H"         | "H"     | Real-time correction    |

| "H"     | "L"         | "L"     | Asynchronous correction |

| "H"     | "L"         | "H"     | Subcode buffering       |

| "H"     | "H"         | "H"     | CD-DA                   |

### bits 2 to 0: NTCRCT2 to 0 (number of times of correction)

This determines the number of times where error correction is performed when operating in asynchronous correction mode. (1 to 4 times)

#### 1-1-23. 18h

#### (1) XFRSTS (data transfer status) register (read)

XFRSTS (data transfer status) register

| Adr.   | bit7 | bit6 | bit5      | bit4 | bit3         | bit2 | bit1         | bit0         | Reg.   |

|--------|------|------|-----------|------|--------------|------|--------------|--------------|--------|

| 18h (R | REV# | REV# | REV#<br>0 |      | CMDO<br>BUSY |      | CBFW<br>RRDY | CBFR<br>DRDY | XFRSTS |

bits 7 to 5: REV#2 to 0 (revision number bits 2 to 0)

"000" is read out. This can be used to recognize the version.

bit 4: CMDOBUSY (command output busy)

This bit goes high if DSPCMDXFR is set. Once the transfer of contents of the DSPCMD register to the CD DSP is completed, this bit goes low.

bit 1: CBFWRRDY (CPU buffer write ready)

The sub CPU can write in the CPUBWDT register when this bit is high.

bit 0: CBFRDRDY (sub CPU buffer read ready)

The sub CPU can read the CPUBRDT register when this bit is high.

#### (2) CHPCTL0 (chip control 0) register (write)

CHPCTL0 (chip control 0) register

| Adr.    | bit7        | bit6       | bit5       | bit4         | bit3 | bit2         | bit1         | bit0         | Reg.    |

|---------|-------------|------------|------------|--------------|------|--------------|--------------|--------------|---------|

| 18h (W) | CHIP<br>RST | TGT<br>MET | INC<br>TGT | RPCO<br>RTRG | "L"  | CLDS<br>PCMD | DSPC<br>MDXF | DSPC<br>MDLT | CHPCTL0 |

bit 7: CHIPRST (chip reset)

This IC is reset when this bit is set high.

bit 6: TGTMET (target met)

- (1) During execution of a write-only or real-time error correction command, if the target sector is found, the sub CPU sets TGTMET high.

- (2) TGTMET is sampled for 3/4 sectors (depends on the playback speed) after the decoder interrupt. Accordingly, if the target sector is found, the sub CPU must set TGTMET high within this interval after DECINT.

- (3) Once TGTMET is set high, it remains high internally until the decoder is disabled.

- (4) If TGTMET is sampled and found to be low during execution of a write-only or real-time error correction command:

- The main data and subcode buffering areas are not renewed.

- Main data error correction is not performed.

bit 5: INCTGT (increment target register)

If this bit is set high, the target registers (TGTMIN, TGTSEC, and TGTBLK) are incremented. The target registers use BCD code.

TGTMIN, TGTSEC, and TGTBLK are connected in cascading fashion and are incremented as shown below.

- (1) The TGTBLK register is always incremented by this bit. When the TGTBLK register is incremented after reaching "74", it returns to "0".

- (2) The TGTSEC register is incremented when the TGTBLK register is "74" and this bit goes high. When the TGTSEC register is incremented after reaching "59", it returns to "0".

- (3) The TGTMIN register is incremented when the TGTBLK register is "74", the TGTSEC register is "59", and this bit goes high. When the TGTMIN register is incremented after reaching "99", it returns to "0".

CXD1804AR

bit 4: RPCORTRG (repeat correction trigger)

If this bit is set high while the decoder is disabled, the CD-ROM sector error correction begins. The sector that is corrected is specified by the BFARA# register.

bit 3: RESERVED

Always set low.

bit 2: CLDSPCMD (clear DSP data register)

Setting this bit high clears the DSPCMD register.

bit 1: DSPCMDXF (DSP command transfer)

Setting this bit high starts serial transfer of the contents of the DSPCMD register to the CD DSP.

bit 0: DSPCMDLT (DSP command latch)

Setting this bit high outputs a pulse from the XLAT pin.

#### 1-1-24. 19h

### (1) CPUBRDT (CPU buffer read data) register (read)

CPUBRDT (CPU buffer read data) register

| Adr.    | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Reg.    |

|---------|------|------|------|------|------|------|------|------|---------|

| 19h (R) |      |      |      |      |      |      |      |      | CPUBRDT |

The sub CPU reads the Data In the buffer memory through this register.

### (2) CPUBWDT (CPU buffer write data) register (write)

CPUBWDT (CPU buffer write data) register

| Adr.    | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Reg.    |

|---------|------|------|------|------|------|------|------|------|---------|

| 19h (W) | b7   | b6   | b5   | b4   | b3   | b2   | b1   | b0   | CPUBWDT |

The sub CPU writes the data to be written in the buffer memory in this register.

#### 1-1-25. 1Ah

#### (1) SCTINF (sector information) register (read/write)

SCTINF (sector information) register

|     | Adr.    | bit7         | bit6 | bit5 | bit4 | bit3 | bit2  | bit1  | bit0       | Reg.   |

|-----|---------|--------------|------|------|------|------|-------|-------|------------|--------|

| 1AI | h (R/W) | SUBQ<br>FMSL |      |      |      |      | MODE2 | FORM2 | XFR<br>SCT | SCTINF |

While DECINT is active, the current sector information is written in this register. When making transfers to the host automatically, be sure to set the information in this register each time DECINT is active. The value in this register is written in the last address in the buffer memory area.

bit 7: SUBQFMSL (subcode-Q format select)

High: When ENSBCBT is high and ALLSBC is low, the decoder does not write the subcode error flag or 00h after subcode-Q in the buffer. When transferring the subcode error flag and 00h after subcode-Q address data to the host, the sub CPU must write Data In the above address before setting the SCTINF register.

Set this bit high only when ENSBCBT is high and ALLSBC is low is prohibited.

Low: When ENSBCBT is high and ALLSBC is low, the decoder writes the subcode error flag and 00h after subcode-Q in the buffer.

CXD1804AR

bits 6 to 3: RESERVED

Always set low.

bit 2: Mode2

High: This sector is a Mode2 sector.

Low: This sector is a Mode1 or CD-DA sector.

bit 1: Form2

This bit is valid only when the Mode2 bit is high.

High: This sector is a Form2 sector. Low: This sector is a Form1 sector.

This bit can either be high or low in the Mode2 for the Yellow Book.

| MODE2 | FORM2 |             |

|-------|-------|-------------|

| "L"   | "L"   | MODE1       |

| "L"   | "H"   | RESERVED    |

| "H"   | "L"   | MODE2/FORM1 |

| "H"   | "H"   | MODE2/FORM2 |