# LXT441

## Switched 56 / DDS Integrated DSU / CSU

### **General Description**

The LXT441 is an integrated transceiver and data formatter for Switched 56 (SW56) and Digital Data Service (DDS) Data Service Unit/Channel Service Unit (DSU/CSU) and Office Channel Unit (OCU) applications.

The LXT441 line interface section performs transmit pulse shaping and receive signal data and timing recovery at the user-network 4-wire metallic interface. The device operates at loop speeds of 56 kbps and 72 kbps, supporting SW56, 56 kbps DDS with or without secondary channel (SC) and 64 kbps clear channel DDS services.

The integrated DSU circuit provides a DCE interface and connects directly to data terminal equipment (DTE) using standard EIA530 control leads. Data formatting includes DDS framing, control code handling, loop code generation and detection, and zero code suppression processing.

The LXT441 has an on-chip 8-bit microprocessor interface that simplifies device configuration, status reporting, and SW56 call processing, and may be used for parallel data transfer to and from the 4-wire physical link.

### **Features**

- Supports most popular data rates for new DSU/CSUs

- Switched 56 and 56 kbps DDS (DDS-PRI, 56 kbps loop speed)

- 56 kbps DDS with secondary channel (DDS-SC, 72 kbps loop speed)

- 64 kbps clear-channel DDS (CC-64K, 72 kbps loop speed)

- Switched 56 Call Control via EIA control leads or microprocessor

- · Receiver performance monitoring

- Idle Code Transmission (CMI, DMI)

- Transmit timing recovered from network or supplied by system

- Network Control Code Detection and Generation

- CSU and DSU latching and non-latching loopbacks

- Available in 44-pin PLCC

- Single 8.192 MHz crystal or clock input

- 5V only CMOS process technology

## **Applications**

- · Leased-line DDS and Switched 56 DSU/CSUs

- Internet Service Provider (ISP) Equipment

- Internal DSU for Routers, Bridges and PC add-in cards

- Frame Relay Access Devices (FRAD)

- OCU Cards for Channel Banks and DLC Systems

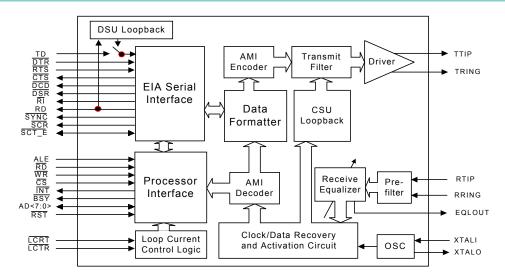

## **LXT441 Block Diagram**

# **TABLE OF CONTENTS**

| PIN ASSIGNMENTS AND SIGNAL DESCRIPTIONS            | 5-22 |

|----------------------------------------------------|------|

| FUNCTIONAL DESCRIPTION                             | 5-25 |

| Initialization                                     |      |

| Frame Alignment                                    |      |

| Reception                                          |      |

| Clock Recovery                                     |      |

| Data Extraction                                    |      |

| Receiver Bipolar to NRZ Conversion                 |      |

| Receiver Code Detection                            | 5-26 |

| Control Code Detection                             | 5-27 |

| Loss of Frame Alignment                            | 5-27 |

| Recovery of Frame Alignment                        | 5-27 |

| Changes in Signal Strength                         | 5-27 |

| Receive Loss of Signal                             | 5-28 |

| Transmission                                       | 5-30 |

| Transmit Serial Interface                          | 5-30 |

| Transmit NRZ to Bipolar Conversion                 | 5-30 |

| Transmit Code Generation                           | 5-30 |

| DSU Loopback Code Generation in an OCU Application | 5-30 |

| Loopback Operation                                 | 5-31 |

| CSU Loopback                                       | 5-31 |

| DSU-Nonlatching-Loopback                           | 5-31 |

| System Serial Interface and Data Formatting        |      |

| Device Configuration                               |      |

| Switched 56 Call Control                           | 5-31 |

| APPLICATION INFORMATION                            | 5-34 |

| Design Considerations                              | 5-34 |

| Microprocessor Interfacing                         | 5-34 |

| BSY Operation                                      |      |

| Crosstalk                                          | 5-34 |

| PCB Layout                                         | 5-34 |

| Power Supply Decoupling                            | 5-35 |

| TEST SPECIFICATIONS                                           | 5-38 |

|---------------------------------------------------------------|------|

| Absolute Maximum Ratings                                      | 5-38 |

| Recommended Operating Conditions                              | 5-38 |

| Electrical Characteristics                                    | 5-39 |

| AC Timing Characteristics                                     | 5-39 |

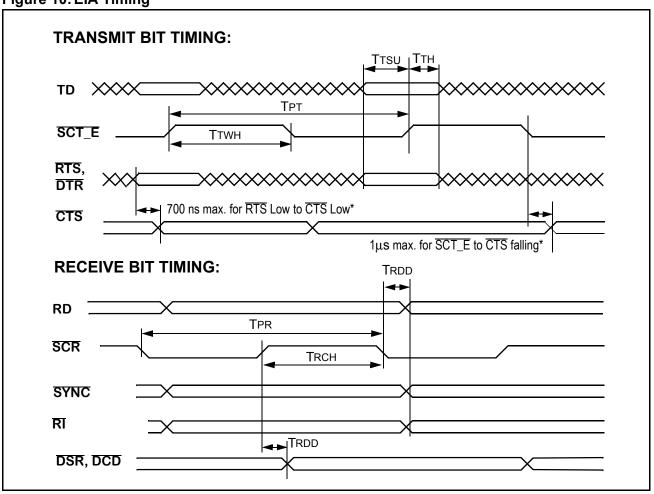

| EIA Timing                                                    | 5-40 |

| Microprocessor Timing Characteristics                         | 5-41 |

| Microprocessor Timing - Read Operations                       | 5-41 |

| Microprocessor Timing - Write Operations                      | 5-42 |

| REGISTER DEFINITIONS                                          | 5-43 |

| Introduction                                                  | 5-43 |

| LXT441 Register Set                                           | 5-43 |

| LXT441 Register Bit Mapping                                   | 5-44 |

| Register WR0 - Device Control - Address 0x00                  | 5-45 |

| Register WR1 - Transmit Control (DDS-PRI Mode) - Address 0x01 | 5-46 |

| Register WR1 - Transmit Control (DDS-SC Mode) - Address 0x01  | 5-46 |

| Register WR2 - Receive Control - Address 0x02                 | 5-47 |

| Register WR5 - EIA select - Address 0x05                      | 5-47 |

| Register WR7 - Transmit EIA Data - Address 0x07               | 5-47 |

| Register WR7 - Transmit EIA Data Formats                      | 5-48 |

| Register RD7 - Rx EIA Data - Address 0x07                     | 5-48 |

| Register WR8 - Interrupt Enable - Address 0x08                | 5-48 |

| Register WR8 - Interrupt Status - Address 0x08                | 5-49 |

| Register WR9 - EIA Control - Address 0x09                     |      |

| Register RD9 - EIA Status - Address 0x09                      | 5-50 |

| Register WRC - Rx Code Interrupt Enable - Address 0x0C        |      |

| Register RDC - Rx Codes - Address 0x0C                        | 5-51 |

| Summary of Transmit and Receive Control Codes                 | 5-52 |

| Register RDA - Device Status - Address 0x0A                   |      |

| Insertion Loss and Line Length Values for bits LL<3:0>        |      |

| Register RDB - Rx Slicer Level - Address 0x0B                 | 5-54 |

| Register RDD - Rx Invalid BPV Count - Address 0x0D            | 5-54 |

## PIN ASSIGNMENTS AND SIGNAL DESCRIPTIONS

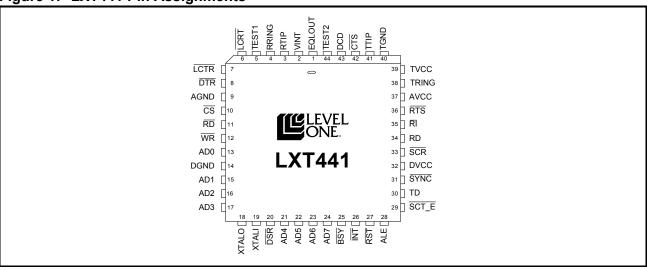

Figure 1: LXT441 Pin Assignments

**Table 1: LXT441 Microprocessor Interface Signal Descriptions**

| Pin | Symbol | I/O | Name / Description                                                                                                                                                                                                               |

|-----|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10  | CS     | I   | <b>Chip Select</b> . Active Low. A Low on this pin enables the 8-bit parallel interface to perform read and write operations.                                                                                                    |

| 11  | RD     | I   | <b>Read</b> . Active Low. During read cycles, a Low on this pin turns on the internal drivers to present data to the 8-bit address/data bus.                                                                                     |

| 12  | WR     | I   | <b>Write</b> . Active Low. During write cycles, a Low-to-High transition on this pin latches data present on the 8-bit bus into internal registers.                                                                              |

| 13  | AD0    | I/O | Address Data Bus. Multiplexed 8-bit parallel address data bus. These pins are used                                                                                                                                               |

| 15  | AD1    |     | to access the read and write registers located within the LXT441.                                                                                                                                                                |

| 16  | AD2    |     |                                                                                                                                                                                                                                  |

| 17  | AD3    |     |                                                                                                                                                                                                                                  |

| 21  | AD4    |     |                                                                                                                                                                                                                                  |

| 22  | AD5    |     |                                                                                                                                                                                                                                  |

| 23  | AD6    |     |                                                                                                                                                                                                                                  |

| 24  | AD7    |     |                                                                                                                                                                                                                                  |

| 25  | BSY    | О   | <b>Busy</b> . Active Low open-drain indication. Signal to host microcontroller that device has not completed read or write operation.                                                                                            |

| 26  | INT    | О   | <b>Interrupt</b> . Active Low open-drain Interrupt. Signal to host microcontroller that an unmasked interrupt condition has been detected.                                                                                       |

| 27  | RST    | I   | <b>Reset</b> . Active Low hardware reset pin. Must be pulsed Low on power-up to initialize all internal circuits. Must also be pulsed Low after changing the data rate setting, and after certain receive line conditions occur. |

| 28  | ALE    | I   | <b>Address Latch Enable</b> . When High, internal address latch is transparent. A Highto-Low transition latches the address present on pins AD<7:0>.                                                                             |

Table 2: LXT441 EIA Serial Interface Signal Descriptions

| Pin | Symbol | I/O | Name / Description                                                                                                                                                                                                                                                            |

|-----|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8   | DTR    | I   | Data Terminal Ready. Active Low EIA signaling lead from DTE.                                                                                                                                                                                                                  |

| 20  | DSR    | О   | Data Set Ready. Active Low EIA signaling lead to DTE.                                                                                                                                                                                                                         |

| 29  | SCT_E  | I/O | <b>Extended Transmit Serial Clock</b> . Input or Output transmit clock dependent upon setting of TCCT control bit.                                                                                                                                                            |

| 30  | TD     | I   | Transmit Data. Transmit NRZ data from DTE.                                                                                                                                                                                                                                    |

| 31  | SYNC   | О   | <b>Word/Bit Synchronization</b> . 1-bit wide active Low output indicates word boundaries at DTE interface.                                                                                                                                                                    |

| 33  | SCR    | О   | <b>Receive Serial Clock</b> . Smooth 56 kHz for DDS-PRI, gapped 72 kHz (64 kHz) for DDS-SC and CC-64K.                                                                                                                                                                        |

| 34  | RD     | О   | Receive Data. Receive NRZ data to DTE.                                                                                                                                                                                                                                        |

| 35  | RI     | О   | <b>Ring Indicator</b> . Indicates the presence of receive data (not control codes) when the receiver is in the control sequence mode (CALLMD = 1). Signifies incoming call for SW56 operation.                                                                                |

| 36  | RTS    | I   | <b>Request to Send</b> . Indicates a request by the DTE to transmit data. When High, CMI is transmitted on the line in DDS-PRI and DDS-SC. When this line goes High for a time greater than one byte period, the transmitter enters data mode for at least four byte periods. |

| 42  | CTS    | О   | <b>Clear to Send</b> . Active Low EIA signaling lead indicates DCE readiness to transmit live data.                                                                                                                                                                           |

| 43  | DCD    | О   | <b>Data Carrier Detect</b> . Active Low EIA signaling lead indicating that the LIU receiver is fully operational; meaning that it is active, and that frame or bit sync is achieved, if enabled.                                                                              |

**Table 3: LXT441 Line Interface Signal Descriptions**

| Pin | Symbol | I/O | Name / Description                                                                                                                                                                                                                              |

|-----|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | EQLOUT | О   | Equalizer Monitor. Must be left open when not used.                                                                                                                                                                                             |

| 2   | VINT   | I   | <b>Intermediate Voltage Reference</b> . Reference voltage used for internal analog circuits. This pin must be connected through a 1 $k\Omega$ resistor (Rv) to the center node between the two termination resistors, Rr, as shown in Figure 8. |

| 3   | RTIP   | I   | Receive Tip and Ring. Receive data input pair. RTIP and RRING are a fully differ-                                                                                                                                                               |

| 4   | RRING  | I   | ential input for the receive line interface.                                                                                                                                                                                                    |

| 6   | LCRT   | I   | <b>Loop Current Rx/Tx</b> . A Low input, supplied by an external current sensing circuit, indicates the presence of loop current flowing from the receive to the transmit twisted pair wires, and initiates a CSU loopback.                     |

| 7   | LCTR   | I   | <b>Loop Current Tx/Rx</b> . A Low input supplied by an external current sensing circuit indicates the presence of loop current flowing from the transmit to the receive twisted pair wires.                                                     |

| 38  | TRING  | О   | Transmit Ring and Tip. Differential driver outputs. Designed to drive $135\Omega$ twisted-                                                                                                                                                      |

| 41  | TTIP   | О   | pair cable through transmit line interface shown in application diagram, Figure 8.                                                                                                                                                              |

Table 4: LXT441 Miscellaneous Signal Descriptions

| Pin      | Symbol         | I/O    | Name / Description                                                                                                                                                                                                                   |  |  |  |  |  |

|----------|----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 39       | TVCC           | _      | Transmit Supply. Line driver power supply.                                                                                                                                                                                           |  |  |  |  |  |

| 40       | TGND           | _      | Transmit Ground. Line driver ground.                                                                                                                                                                                                 |  |  |  |  |  |

| 9        | AGND           | _      | Analog Ground. Reference for all analog LIU circuits except the transmit driver.                                                                                                                                                     |  |  |  |  |  |

| 37       | AVCC           | _      | Analog Supply. Line interface primary power supply.                                                                                                                                                                                  |  |  |  |  |  |

| 18<br>19 | XTALO<br>XTALI | O      | <b>Crystal Oscillator</b> . The required 8.192 MHz master clock may be provided by a crystal connected across these pins, or by a digital clock connected to XTALI. If a clock is provided on XTALI, XTALO must be left unconnected. |  |  |  |  |  |

| 14       | DGND           | _      | Digital Ground. Ground reference for all internal digital circuitry.                                                                                                                                                                 |  |  |  |  |  |

| 32       | DVCC           | _      | Digital Supply. Digital circuitry power supply.                                                                                                                                                                                      |  |  |  |  |  |

| 5<br>44  | TEST1<br>TEST2 | I<br>I | Factory Test Pins. Leave unconnected.                                                                                                                                                                                                |  |  |  |  |  |

### **FUNCTIONAL DESCRIPTION**

The LXT441 is comprised of five basic sections: receiver, transmitter, microprocessor interface, data formatter and back-end system serial interface.

The receive section includes pre-filters and line equalizers, and the timing recovery and data extraction blocks. An internal digital phase-locked loop (DPLL) is used in conjunction with the oscillator circuit to synchronize the recovered clock and data.

The transmit section includes a 50% AMI encoder, a programmable switched-capacitor low-pass filter, a low-pass notch filter, a transmit timing re-synchronizer and a continuous reconstruction filter. An on-chip CMOS driver is also incorporated to drive a  $135\Omega$  line through a coupling transformer.

The microprocessor block employs an 8-bit multiplexed parallel interface to transfer status and control information to and from the system host controller. This processor port connects to both Intel<sup>®</sup> multiplexed and Motorola<sup>®</sup> non-multiplexed controllers with a minimum of external 'glue' logic.

The system serial interface facilitates the connection of a DTE (data terminal equipment) device to the LXT441, which in turn behaves as a DCE (data communication equipment.) The LXT 441 uses 6 standard EIA530 control leads (DTR, RTS, CTS, DCD, DSR and RI) for flow control, status reporting and SW56 signaling. The serial interface supports both DSU and OCU operation, with the transmit clock provided by either the recovered receive clock, or an external reference.

### Initialization

A hardware reset (RST) is required under any of the following circumstances:

- · Initial power-up

- · A change in Data Rate setting

- A change in the local analog loopback configuration

- A local change in the line upon which the transceiver is communicating (for example, configurations for changing lines in a "1 for n" redundancy scheme)

- The detection of an invalid line condition by the LXT441 receiver. (This will be indicated by either an XBPV or V OFL interrupt.)

On receipt of the RST pulse, the LXT441 executes an iterative cycle of level detection and offset cancellation to select the appropriate equalizer settings for the received

signal. When received data has a 50% ones density, full operation is achieved within one second after RST. Under the minimum ones density condition specified in Table 5, full operation is achieved within eight seconds after RST. Correct initialization assumes the presence of an AMI-coded signal at the RTIP and RRING inputs. The LXT441 will not correctly initialize unless a stable signal which meets the network interface specifications of AT&T Pub 62310 is present at the RTIP and RRING inputs during the entire initialization process. The RD output is not valid until full operation is achieved.

**Table 5: Ones Density Requirements**

| Data Rate (kbps) | Minimum Average<br>Ones Density |

|------------------|---------------------------------|

| 56.0             | 1/14                            |

| 72.0             | 1/18                            |

Automatic re-initialization may be triggered by changes in received signal strength as follows:

- If received signal strength increases by more than about 6 dB after full operation is achieved, automatic re-initialization occurs.

- If received signal strength decreases by more than about 4 dB, re-initialization occurs. If the decrease in received signal strength exceeds 6 dB, the LXT441 reports an LOS (Loss of Signal) condition and performs an automatic re-initialization.

The time required to achieve full operation after reinitialization, is the same as required for power-on initialization (i.e., 1 second max with 50% ones density, 8 seconds under minimum ones density conditions). Reinitialization is not triggered by impulse noise events.

## Frame Alignment

When in DDS-SC or CC-64K modes, the LXT441 begins a frame alignment search at channel connection time. Channel connection time is defined as the time when the ACTIVE bit changes to a '1'.

The mean time to Frame Alignment is less than 5 ms. This means that, at 72 kHz on average, fewer than five frame comparisons are required to establish frame alignment.

Frame alignment is declared when the LXT441 detects three consecutive Frame Alignment Word (FAW) sequences matching the FAW. Detection of consecutive FAW sequences requires that each FAW sequence matches the FAW, and that each FAW sequence is exactly one frame apart.

## Reception

RTIP and RRING inputs are differentially detected, then processed through the pre-filters and equalizer section. The continuous pre-filter removes high frequency noise and prevents aliasing problems for the line equalizers which follow. Receive pulses are reconstructed by the receive equalizer, which is comprised of a step equalizer stage and an adaptive decision feedback equalizer (DFE). The DFE eliminates residual inter-symbol interference (ISI) due to echoing by multiple bridged tap connections and time varying line characteristics such as temperature, humidity and age.

### **Clock Recovery**

The clock recovery circuit uses a rate synchronizer to generate a high frequency internal clock from the oscillator input. A DPLL is used to synchronize this internal clock to the received data pulses. The output clock from the DPLL is divided down to generate  $\overline{SCR}$  and all other required clocks (except  $\overline{SCT_E}$  when it is supplied as an external input).

### **Data Extraction**

The data extraction block delivers raw recovered bipolar line data to the data formatter and decoder so that it may output the NRZ RD stream to the EIA interface and the receive EIA microprocessor register. A positive or negative differential pulse received between RTIP and RRING results in a logic 1 sent to the formatter, while no pulse is reported to the formatter as a logic 0. After decoding in the formatter section, the final RD output at the received data rate is valid on the falling edge of  $\overline{SCR}$ .

Receiver operation is not affected by the data patterns, provided the ones density requirements of Table 5 are met, and the receive line signal contains at least one valid pulse every 26 bit periods. Loss of signal is declared after 32 consecutive zeros. However, the SCR output remains synchronized to the RTIP/RRING input for up to 40 consecutive zeros, after which re-initialization occurs. Spurious bipolar violations (due to channel noise, etc.), will not adversely affect long term LXT441 data reception.

#### Receiver Bipolar to NRZ Conversion

The receiver converts Bipolar data into NRZ data in the following manner:

- Bipolar B's are marks (of alternate polarity with respect to last mark) converted to NRZ 1s.

- Bipolar V's are marks (of same polarity with respect to last mark) converted to NRZ 1s.

- Bipolar O's are spaces converted to NRZ 0s.

This conversion process takes 1 byte plus 1 bit period, with corresponding NRZ data available 8 bit periods after the Bipolar data is received. There are, however, a few exceptions to this. Reception of the DSU Loopback control code and reception of the Zero Suppression control code require that a code replacement be performed upon the received data prior to conversion to NRZ format. See Table 28 for RX\_DLP & RX ZSC code replacement.

In DDS-SC mode, there are no violations. Thus, the receiver only converts O's and B's (bipolar data) to NRZ 0s or 1s respectively. Frame synchronization must be established to enable network code detection. Reception of the DSU Loopback code requires a code replacement operation to be performed prior to conversion to NRZ format. See Table 28 for R\_DLP code replacement.

CC-64K mode is very much the same as DDS-SC mode. There are no byte replacements, and the only code is idle data (RX\_DMI). See Table 28 for control codes & replacement policy for various modes.

### **Receiver Code Detection**

The receiver converts bipolar received data into NRZ data. In DDS-PRI mode, this process requires bipolar violation (BPV) detection, valid/invalid BPV detection, and control code detection. A violation is detected upon receipt of Bipolar data which violates the Alternate Mark Inversion (AMI) Rule. A BPV is valid if, and only if, it belongs to a 7-bit Control Code, satisfying the following set of criteria:

- At least seven bit periods have passed without a violation since receipt of the violation in question.

- An odd number of B's (non-violation marks) were received since the last violation.

- The bit received prior to the violation was an O (a space).

#### **Control Code Detection**

The data presented at the RTIP/RRING pins undergoes bipolar to NRZ conversion, with automatic detection and decoding of control codes according to the following criteria:

- Detection of Idle (CMI), OOS, and OOF codes in DDS-PRI mode.

- Detection and conversion of DSU Loop code in DDS-PRI mode, and DSU Loop control code in DDS-SC mode.

- Detection of DDS-SC control codes for DDS-SC mode.

- Detection of the DDS-SC six-bit frame pattern for byte alignment of data and control streams for DDS-SC mode, and 8-bit data for CC-64K mode.

- Control of EIA handshake signals based on receiver status from the line interface unit.

All control codes except RX\_DMI are encoded into valid BPVs. Thus, upon receipt of a valid BPV, control codes are decoded (as listed in Table 28). Any valid BPV which doesn't match a control code listed in the table results in an 'unmatched' code. The exception, RX\_DMI, is detected when an all-marks (all B's and no V's) code is received. All control codes remain active for 7 bit periods after detection.

Bipolar received codes in both DDS-SC and CC-64K modes contain no violations. Therefore, data must be synchronized with the frame pattern, to establish the beginning of each word. The C/S bit is used to determine whether the unit is receiving network codes or data. When two of three consecutive C-bits are 0s the network code detector is enabled which tests if the data matches any of the control codes listed in Table 27. When two of three consecutive C-bits are 1s the unit reverts to data mode.

## **Loss of Frame Alignment**

The LXT441 declares loss of frame alignment when it receives five consecutive Frame Alignment Word (FAW) sequences in error. Here, consecutive FAW sequences implies that each FAW sequence is expected to occur an integral number of frames after the FAW sequence which produced alignment. The initial alignment algorithm is the same as the frame recovery algorithm.

### Recovery of Frame Alignment

The LXT441 begins recovery of frame alignment immediately after detecting loss of frame alignment.

Frame Alignment Recovery is identical to the initial Frame Alignment search process described under Initialization.

# **Changes in Received Signal Strength**

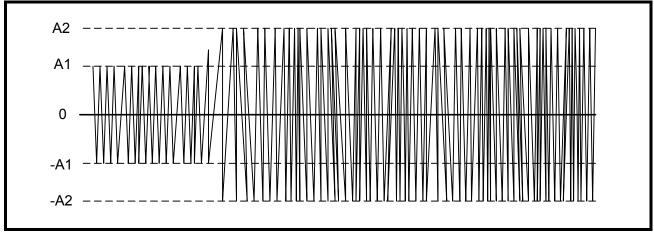

During initialization, the LXT441 selects filters appropriate to the strength of the received signal. After initialization, the LXT441 continually monitors the receive signal strength to ensure the optimum signal/filter match. Data reception is not affected by impulse noise events or by slow changes in signal amplitude caused by normal temperature and humidity variations (The maximum constant rate of change which the LXT441 can track is 6 dB per minute.) However, instantaneous "step" changes (see Figure 2) may temporarily interfere with data reception. Step changes may be caused by sudden changes in loop attenuation, far end transmitter output, etc.

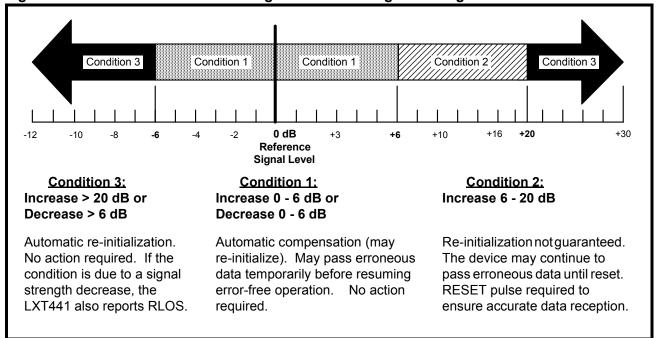

After normal operation has been established, an instantaneous single-step change may cause one of three conditions, as shown in Figure 3.

Under Condition 1, the LXT441 automatically adapts to minor step changes in signal strength (assuming that the new input is a valid DDS signal).

Under Condition 3, the LXT441 responds to significant step changes by re-initializing.

Condition 2, while unlikely to occur in an actual DDS implementation, may be observed in the laboratory when working with artificial line simulators. Condition 2, which results from a 6 - 20 dB step increase in received signal strength, may result in a signal/filter mismatch. This condition is characterized by excessive bipolar violations (BPVs). Excessive BPVs which are not valid code words are detected and counted by the LXT441. The XBPV interrupt flag will be set when excessive BPVs are detected by the LXT441 receiver. The device should be reinitialized via the application of a valid RST pulse in the presence of excessive BPVs.

Under normal operating conditions, step changes in received signal strength are all under local control. Thus, the user can reset the LXT441 once the new receive signal has stabilized at the chip inputs. Remote changes typically involve disconnecting one line and re-connecting another line of different length. These changes trigger the RLOS report and automatic re-initialization.

### Receive Loss of Signal

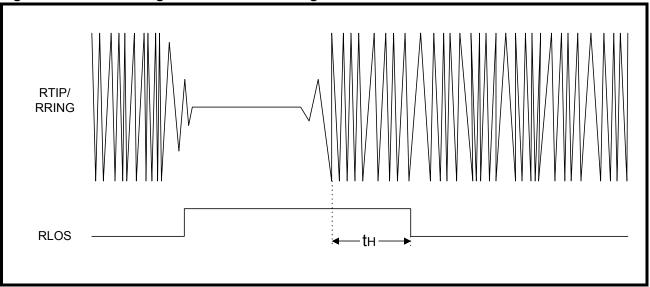

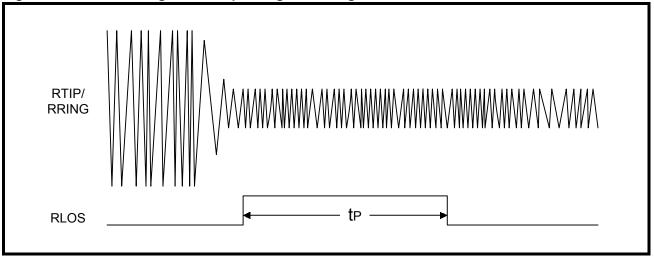

Receive loss of signal (RLOS) is detected when more than 32 consecutive zeros are received, caused either by a true loss of signal, or a signal strength drop greater than 6 dB. The LXT441 automatically re-initializes when RLOS is present, and 40 consecutive zeros are counted. Figure 4 shows the RTIP/RRING input and RLOS control bit timing relationships for a true loss of signal. When signal energy returns to the chip input,

the LXT441 executes one full activation cycle in the presence of this signal. The result is that RLOS will remain active for a period of time (0.13 s < tH < 16 s) after signal energy reappears.

Figure 5 shows the RTIP/RRING input timing and RLOS output timing relationship for a signal strength decrease greater than 6 dB. In this case, RLOS will go High for a time 0.26 s < tP < 16 s.

Figure 2: Step Changes in Receive Signal Strength = 20  $\log_{10}$  ( $^{A2}/A1$ ) dB

Figure 3: Conditions Based on Changes in Receive Signal Strength

Figure 4: RLOS Timing for a True Loss of Signal

Figure 5: RLOS Timing for a Drop in Signal Strength > 6 dB

### **Transmission**

Transmit data (TD) from the DTE is sampled on the rising edge of  $\overline{SCT}$ . The transmit section generates a 50% AMI pulse according to the pulse encoding rules, which is synchronized with the  $\overline{SCT}$  input/output clock. In DSU applications with TCCT=0,  $\overline{SCR}$  is typically routed back out of the  $\overline{SCT}$  input/output pin to serve as a transmit demand clock. If EIAREG=1, then data at the serial interface is ignored, and the Transmit EIA 8-bit microprocessor register is used as the source of transmit data.

Once the transmit data is sampled and encoded, resulting AMI output pulses are processed through a set of frequency dependent filters. Initial filtering at all rates is accomplished by a programmable, switched-capacitor, low-pass filter. This filter is a single-pole type with the pole set at 1.3 times the bit rate (as determined by control bits MODE0 and MODE1.) A continuous filter, common to all data rates, is the final stage. The continuous filter removes high frequency components which remain after processing by the low-pass filter stages. The resulting transmit pulses are then applied to the line driver for transmission onto the twisted-pair line.

### **Transmit Serial Interface**

User data presented at the TD pin undergoes NRZ to bipolar conversion, with automatic generation of zero suppression code for DDS-PRI. In DDS-PRI mode, controlled generation of Control Mode Idle (CMI), and Data Mode Idle (DMI) may be accomplished by manipulating the DTR/RTS control leads, or by writing to the TX\_CMI or TX\_DMI control bits. The microprocessor control bits take precedence over the DTR/RTS for commanding CMI/DMI transmission.

In DDS-SC and CC-64K modes, controlled generation of the DDS-SC control codes may be selected, and the six-bit frame pattern is automatically inserted into the transmitted data stream.

Transmit timing is derived from the receive clock for a loop timed DSU/CSU, or from the SCT\_E input for tail-circuit loop timing, or in OCU applications.

# Transmit NRZ to Bipolar Conversion

The Transmitter converts NRZ data and control codes into bipolar transmitted data. It is possible that several control codes are requested for transmission, thus a priority encoder must resolve which code should be transmitted; if no control code is requested, the transmitter sends out converted NRZ data (see Table 28 for priority of transmit control codes). The position of injected code words is set arbitrarily by a free-running internal bit counter. In DSU operation without a 'tail-circuit' (TCCT=0), the transmit word position is aligned to the receive word position. In DDS-SC and CC-64K modes, the receive word position is determined by the receive frame pattern, while in DDS-PRI mode, the receive word position is arbitrary.

In DDS-PRI MODE, code injection must take into account the polarity of the last transmitted mark (B or V), and whether an even or odd number of B's have been sent since the last V. The first criterion is used to assure that violations are transmitted correctly. The second criterion assures that any X's will be transmitted correctly - as O or B to maintain an odd number of B's since the last V.

In DDS-SC and CC-64K modes, code injection is accompanied by the injection of a frame pattern as the 8th bit of every outgoing data byte or code word. When no code is requested, the transmitter simply converts NRZ 0s and 1s into Bipolar O's and B's, respectively, and injects the frame bit at the proper location. See Table 28 for control codes in DDS-SC and CC-64K modes.

### **Transmit Code Generation**

CONTROL-MODE-IDLE (CMI) can be generated from a logic-Low on EIA handshake signal RTS in DDS-PRI mode and DDS-SC mode.

Clear-To-Send (CTS) goes High after receiving a Request-To-Send (RTS) with delay based upon the time required to transmit the last complete CMI code, plus three idle data bytes.

# DSU Loopback Code Generation in an OCU Application

If the TX\_DLP control is set (register WR2-bit 6), then the controls which normally force transmission of CMI will now force transmission of DSU Loopback Code (DLP). The user can inject test data by pulling RTS High, and waiting for CTS High; indicating the end of a DLP byte and the start of a test data byte. In this case, the RTS-to-CTS delay is not three to four bytes, but is less than one byte.

## **Loopback Operation**

The LXT441 incorporates both a CSU loopback and a DSU loopback.

### **CSU Loopback**

When the LCRT pin is set Low, a CSU loopback is engaged, with the recovered line data and clock being sent back through the transmit section and onto the line interface, as well as being output on the RD and SCR pins. TD and SCT E inputs are ignored in the loopback mode.

### **DSU Nonlatching Loopback**

A nonlatching loopback operates upon receipt of a minimum of four consecutive bytes of the specified loopback code at the proper data rate, and continues for a minimum of four consecutive bytes after receipt of the last loopback code. The loopback is terminated upon receipt of five successive byte intervals without the loopback code (refer to Table 28 for the DSU-Loopback codes for all data rates). The four consecutive bytes must be contiguous; having no "filler" bits between DLP code bytes. In DDS-PRI operation, a loopback code byte is a 7-bit word, and in DDS-SC and CC-64K operation, a loopback code byte is an 8-bit word, with a ninth framing bit injected between the 7th and 8th bits of the code word.

# System Serial Interface and Data Formatting

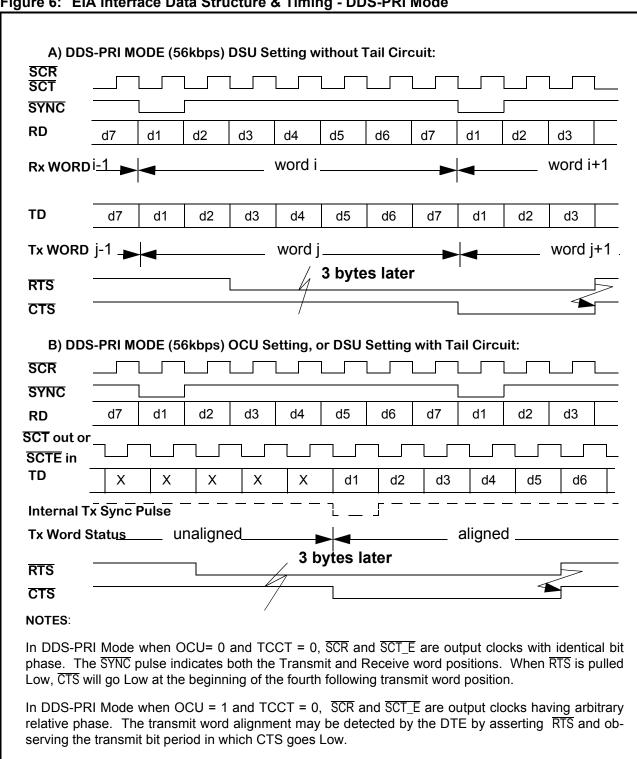

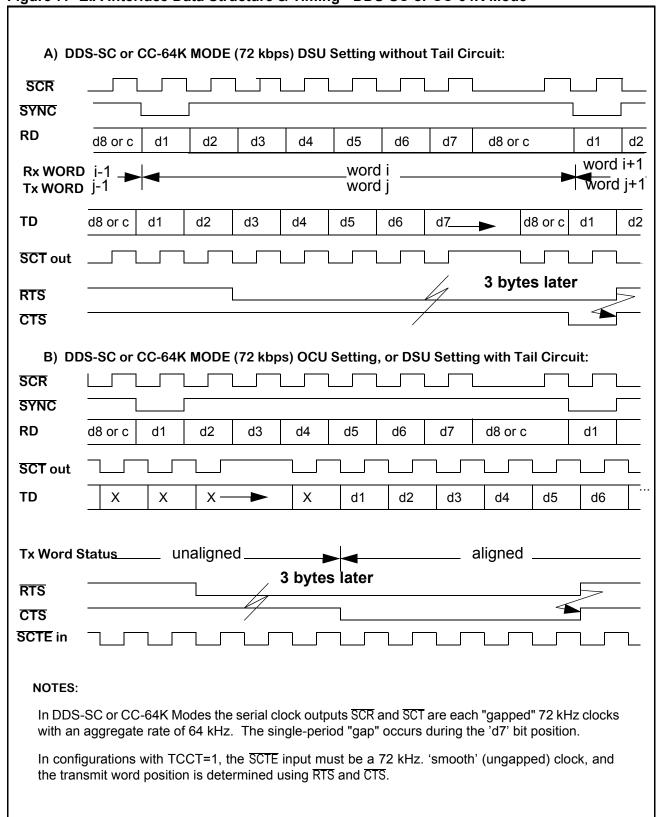

The LXT441 provides a EIA DCE serial interface with TD, RD, SCT/SCT E, SCR, DTR, RTS, DSR, DCD, RI, & CTS pins for attaching data terminal equipment (DTE). The signal levels are TTL/CMOS compatible, allowing a direct connection to Serial Communication Controllers (SCC), while connection to external terminals require standard V.35/RS449 transceivers. User data for transmission undergoes processing in the data formatter to insert required zero suppression codes for DDS-PRI, and framing information for DDS-SC and CC-64K. Receive line data has zero suppression codes removed from DDS-PRI streams, while the framing bits are stripped from DDS-SC and CC-64K data. Secondary channel bits are passed to the RD and TD pins in DDS-SC, allowing transparent secondary channel processing. Refer to Figures 6 and 7 for EIA interface data structure and relative timing. For specific timing parameters, refer to Test Specifications.

### **Device Configuration**

The user can select the operating mode and loop rate (DDS-PRI, DDS-SC, CC-64K) by writing the appropriate values to control bits MODE0 and MODE1.

Transmit timing modes are selected by configuring bits OCU and TCCT. Switched 56 call flow control is performed using either the EIA handshake lines or the microprocessor port. In DDS-SC mode, the secondary channel bandwidth is available transparently by interpreting transmit and receive data in relation to the SYNC signal.

### **Switched 56 Call Control**

Switched 56 call control is performed between OCU and DSU by the interpretation of CMI and DMI codes sent from one end-point to the other. These codes correspond to 'on-hook' and off-hook' conditions on the metallic trunk. Refer to the TIA/EIA-596 specification for specific signalling and timing requirements. The DSU 'dials' a call by seizing the trunk, waiting for a valid network 'wink' and then sending alternating CMI/DMI sequences which are interpreted as dial digits, much in the manner of pulse dialing. The DSU 'answers' a call by detecting non-CMI data from the OCU. CMI/DMI detection is performed by the LXT441 and may be monitored via the host controller. CMI/DMI transmission may be accomplished using either the RTS signal or the TXCODE register.

In DDS-PRI Mode when TCCT = 1, SCR is an output, and SCT\_E is the transmit serial clock input with arbitrary phase position. Again, the DTE may detect the transmit word position by using the RTS and

Figure 6: EIA Interface Data Structure & Timing - DDS-PRI Mode

CTS lines.

Figure 7: EIA Interface Data Structure & Timing - DDS-SC or CC-64K Mode

## **APPLICATION INFORMATION**

## **Design Considerations**

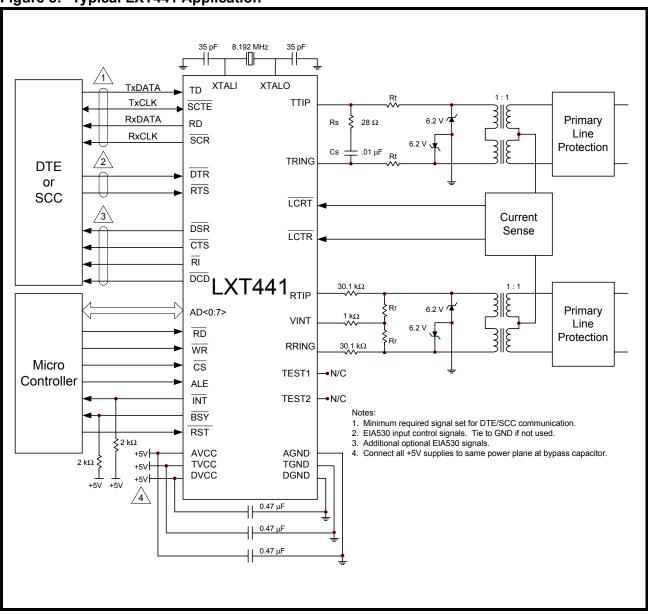

Figure 8 shows a typical LXT441 application circuit. A DSU crystal (8.192 MHz) is connected across XTALI and XTALO, with two grounded loading capacitors. The line interface consists of a pair of 1:1 transformers, centertapped on the line side, with appropriate load resistors. The Rs/Cs shunt network provides high frequency compensation for the transmit driver. The input signal is developed across the Rr/Rin network. Rv limits current into the low-impedance VINT driver during over-voltage conditions on the line.

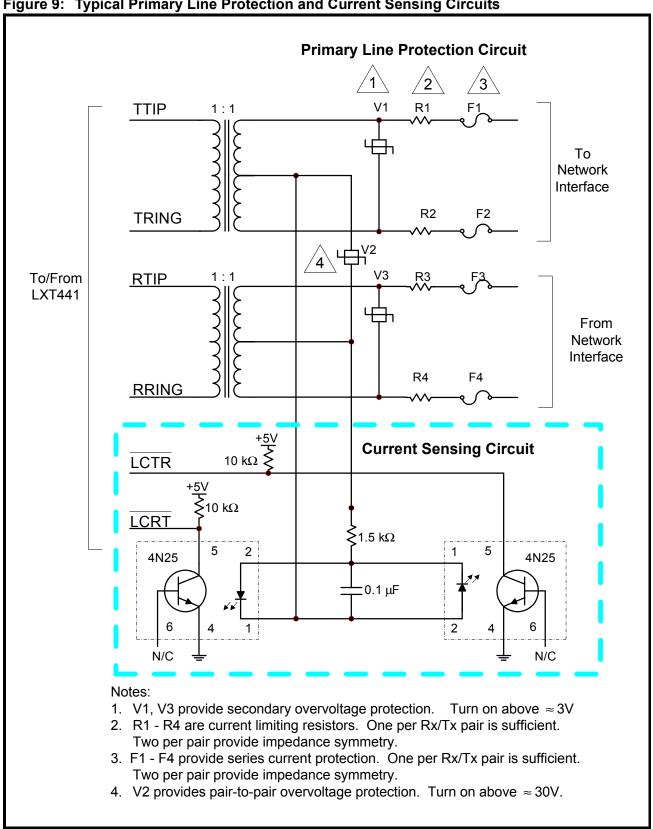

The DTE is connected to the LXT441 EIA interface. NRZ data is required at TD and RD, so level conversion is required for standard bipolar signals such as V.35 and RS-232. Device configuration pins may be tied to Vcc or GND, or may be supplied with logic inputs from an external control circuit. Figure 9 provides details of typical protection and current sensing circuits. Table 6 lists external component recommendations. Refer to the following documents for DDS electrical specifications:

- ANSI T1.410 1992

- AT&T TR 62310 1993

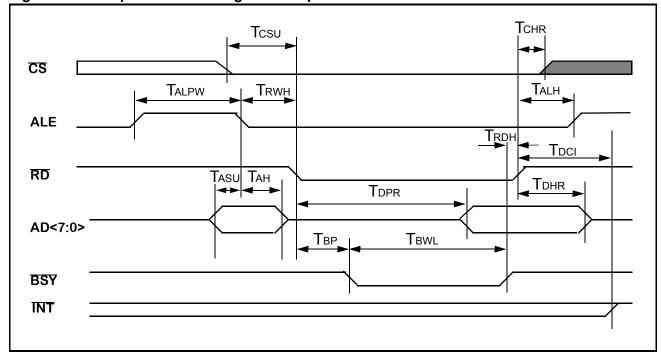

## Microprocessor Interfacing

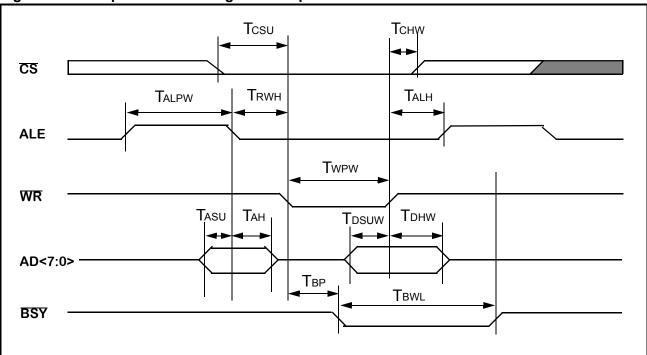

The microprocessor interface is an 8-bit parallel port with multiplexed address/data pins and associated bus control signals. Interfacing to Motorola, Intel and Zilog controllers may be accomplished with a minimum of glue logic by following the guidelines below, and observing the timing parameters in Figures 11 and 12.

CS does not have to be asserted before ALE transitions Low, latching the address present on the multiplexed address/data bus.

The INT signal is cleared to inactive High following a read of the Interrupt Status register at address 08h.

## **BSY Operation**

$\overline{BSY}$  indicates stable data available for read on  $\overline{RD}$  cycles, and the proper internal latching of data on write cycles. Consecutive write cycles require that  $\overline{BSY}$  goes inactive High before the next write.  $\overline{BSY}$  may be used to 'stretch' the RD strobe. RD should not go High before  $\overline{BSY}$  goes inactive High.

### Crosstalk

It is important to prevent crosstalk between the transmitter and receiver circuits. Steps were taken to reduce this interference inside the LXT441, but precautions must be taken with the line interface circuitry outside the chip as well. Crosstalk is especially high when the idle pattern (alternate positive and negative pulses) is being transmitted because the transmit power is concentrated around the Nyquist frequency (half the baud rate).

### **PCB Layout**

The external line interface circuit must be laid out to minimize coupling of other digital and analog signals into RTIP and RRING (see Figure 8.) These inputs, pins 3 and 4, are high impedance nodes which can pick up interference from adjacent PCB traces. The line interface circuit must be designed for loops with up to 50 dB of loss at the Nyquist frequency, even if the product will never be used on such long lines. When no receive signal is present, the LXT441 will switch to the highest gain filter, which produces an internal gain of about 50 dB. Unless precautions are taken, substantial interference coupling into RTIP and RRING could exceed the internal slicer levels and prevent the RLOS report.

Layout considerations for LXT441 application circuits include:

- Minimum PCB trace lengths between the LXT441 and the 8.192 MHz crystal and loading capacitors.

- Minimum PCB trace lengths between resistors Rin and the RTIP and RRING pins. Shield these connections with ground traces.

- Minimum PCB trace lengths between the receive transformer and the receive termination network.

Even with good PCB layout practices, RLOS reporting can be unreliable if the twisted pair line cable is not connected to the OCU or CSU/DSU. The unterminated receive lines can pick up enough noise to trip the data detectors and cause an inaccurate RLOS reading. However, equipment designers can safely assume that the highest-gain filter with 50 dB of signal amplification will never be selected for normal operation on lines with up to 45 dB of attenuation at the Nyquist frequency.

The 50 dB filters were designed for applications in which the line attenuation is 48 dB or greater. The DDS specification requires an insertion loss at 56 and 72 kbps of 43 dB or less. The LXT441 incorporates built-in headroom up to 45 dB. So, for standard applications, the highest-gain filter will never be selected.

## **Power Supply Decoupling**

Each +5V input should be tied to the same power plane, and each should be bypassed by a 0.47  $\mu F$  decoupling capacitor. The bypass caps should be located as closely as possible to the device power and ground pins.

Figure 8: Typical LXT441 Application

Figure 9: Typical Primary Line Protection and Current Sensing Circuits

**Table 6: External Component Recommendations**

| 0                        | D                                         | Recomme                                                                                           | nded Value                                                |  |  |

|--------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|

| Component                | Parameter                                 | LXT400 Compatible                                                                                 | LXT441 Only                                               |  |  |

| Line Transformer         | Turns ratio                               | 1:1, ± 1%                                                                                         | 1:1, ± 1%                                                 |  |  |

| Suggested Manufacturers: | Structure                                 | Center tapped (for line side)                                                                     | Center tapped (for line side)                             |  |  |

| Midcom (800) 643-2661    | Primary Inductance                        | 200 mH minimum                                                                                    | 40 mH minimum                                             |  |  |

| B and H (612) 894-9590   | Leakage Inductance                        | 22 to 43 μH maximum                                                                               | 43 μH maximum                                             |  |  |

| Vitec (209) 651-1535     | DC Resistance (Primary, Rwp)              | 7 - 17 Ω                                                                                          | $8 \Omega$ maximum $(6\Omega \pm 10\% \text{ preferred})$ |  |  |

|                          | DC Resistance (Secondary, Rws)            | 7 - 17 Ω                                                                                          | 8 $\Omega$ maximum (6 $\Omega \pm 10\%$ preferred)        |  |  |

|                          | Interwinding Capacitance                  | 350 pF maximum                                                                                    | 80 pF maximum                                             |  |  |

| Rin                      | Resistance, Tolerance, Rating             | $30.1 \text{ k}\Omega$ , ± 1 %, $\frac{1}{4}$ W                                                   |                                                           |  |  |

| Rt, Rr                   | Resistance Calculation, Tolerance, Rating | $^{\text{e}}$ , $(135 \ \Omega - \text{Rwp} - \text{Rws})/2, \pm 1\%, \frac{1}{4} \text{ W}^{-1}$ |                                                           |  |  |

| Rv                       | Resistance, Tolerance, Rating             | $1 \text{ k}\Omega, \pm 5\%, \frac{1}{4} \text{ W}$                                               |                                                           |  |  |

| DSU Crystal              | Nominal frequency                         | 8.192 MHz                                                                                         |                                                           |  |  |

|                          | Holder style                              | HC-49/U                                                                                           |                                                           |  |  |

|                          | Operating Mode                            | Fundamental, parallel resonant                                                                    |                                                           |  |  |

|                          | Cut                                       | AT                                                                                                |                                                           |  |  |

|                          | Load Capacitance                          | 22 pF nominal (excluding crystal C0)                                                              |                                                           |  |  |

|                          | Tolerance                                 | ± 35 ppm @ 25 °C                                                                                  |                                                           |  |  |

|                          | Range                                     | $\pm$ 50 ppm, -40 to +85 °C                                                                       |                                                           |  |  |

|                          | Aging                                     | 3 ppm per year maximum                                                                            | 1                                                         |  |  |

|                          | Maximum ESR                               | 100 Ω                                                                                             |                                                           |  |  |

|                          | Drive Level                               | 1 mW maximum                                                                                      |                                                           |  |  |

| DSU Crystal Loading      | Capacitance, Tolerance, Rating            | 35 pF, ± 5 %, 10 V                                                                                |                                                           |  |  |

| Capacitors               | Construction                              | NPO ceramic or equivalent                                                                         |                                                           |  |  |

| Transmit Shunt Network   |                                           |                                                                                                   |                                                           |  |  |

| Rs                       | Resistance, Tolerance, Rating             | $28 \Omega, \pm 5 \%, \frac{1}{4} W$                                                              |                                                           |  |  |

| Cs                       | Capacitance, Tolerance, Rating            | $0.01 \mu F$ , $\pm 20 \%$ , $10 \text{ V}$                                                       |                                                           |  |  |

## **TEST SPECIFICATIONS**

#### **NOTE**

The minimum and maximum values in Tables 7 through 11 and Figures 10 through 12 represent the performance specifications of the LXT441 and are guaranteed by test, except where noted by design

**Table 7: Absolute Maximum Ratings**

|                                        | Parameter                        | Symbol | Min        | Max        | Units |

|----------------------------------------|----------------------------------|--------|------------|------------|-------|

| Supply Voltage                         | AVCC referenced to AGND          | Vcc    | -0.3       | 6          | V     |

|                                        | DVCC referenced to DGND          | Vcc    | -0.3       | 6          | V     |

|                                        | TVCC referenced to TGND          | Vcc    | -0.3       | 6          | V     |

| Supply Variation                       | AVCC referenced to DVCC          | Vccv   | -0.3       | 0.3        | V     |

|                                        | DVCC referenced to TVCC          | Vccv   | -0.3       | 0.3        | V     |

|                                        | AVCC referenced to TVCC          | Vccv   | -0.3       | 0.3        | V     |

| Ground Variation                       | AGND referenced to DGND          | GNDV   | -0.3       | 0.3        | V     |

|                                        | DGND referenced to TGND          | Gndv   | -0.3       | 0.3        | V     |

|                                        | AGND referenced to TGND          | GNDV   | -0.3       | 0.3        | V     |

| Input voltage, any p                   | oin <sup>1, 2</sup>              | -      | AGND - 0.3 | AVCC + 0.3 | V     |

| Input or output diod                   | le current, any pin <sup>2</sup> | -      | -          | ±20        | mA    |

| Continuous output of                   | current, any pin <sup>2</sup>    | -      | -          | ±25        | mA    |

| Continuous current, any VCC or GND pin |                                  | -      | -          | ±50        | mA    |

| Storage Temperatur                     | e                                | Tst    | -50        | 150        | °C    |

#### **CAUTION**

Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 1. TTIP and TRING are referenced to DVCC and DGND.

- 2. Except supply pins.

**Table 8: Recommended Operating Conditions**

| Parameter                                      | Symbol | Min  | Тур | Max  | Units |

|------------------------------------------------|--------|------|-----|------|-------|

| Recommended Supply Voltage<br>TVCC, AVCC, DVCC | Vcc    | 4.75 | 5.0 | 5.25 | V     |

| Recommended Operating Temperature              | Тор    | -40  | -   | 85   | °C    |

Table 9: Electrical Characteristics (Over Recommended Range)

| Parameter                               | Symbol | Min | Typ <sup>1</sup> | Max | Units | Test Conditions       |

|-----------------------------------------|--------|-----|------------------|-----|-------|-----------------------|

| Supply Current                          | ICC    | -   | 60               | 80  | mA    | VCC = 5.0  V          |

| Input Low Voltage <sup>2</sup>          | VIL    | -   | -                | 0.8 | V     | Digital Inputs        |

| Input High Voltage <sup>2</sup>         | Vih    | 2.0 | -                | -   | V     | Digital Inputs        |

| Output Low Voltage                      | Vol    | -   | -                | 0.4 | V     | IOL= 1.6 mA (TTL)     |

|                                         | Vol    | -   | 0.2              | -   | V     | IOL< 10μA (CMOS)      |

| Output High Voltage                     | Voh    | 2.4 | -                | -   | V     | IOH= 400μA (TTL)      |

|                                         | Voh    | -   | 4.5              | -   | V     | IOL < 10μA (CMOS)     |

| Input Leakage Current                   | IIL    | -40 | -                | 40  | μΑ    | $0 < V_{IN} < V_{CC}$ |

| Open Drain Leakage Current <sup>3</sup> | IODL   | -   | -                | 10  | μΑ    |                       |

- 1. Typical values are at 25 °C and are for design aid only; not guaranteed and not subject to production testing.

- 2. Limited functional test patterns are performed at these input levels. The majority of functional tests are performed at levels of 0V and 3V.

- 3. Applies to  $\overline{INT}$  and  $\overline{BSY}$  only.

Table 10: AC Timing Characteristics (Over Recommended Range)

|                       | Parameter                                                | Symbol   | Min                                  | Typ <sup>1</sup>    | Max                                       | Units | Test<br>Conditions                    |

|-----------------------|----------------------------------------------------------|----------|--------------------------------------|---------------------|-------------------------------------------|-------|---------------------------------------|

| Receive<br>Timing     | SCR period - out of lock                                 | TPR (ol) | $\frac{1-5x10^{-3}}{\text{fb(rec)}}$ | 1<br>fb(rec)        | $\frac{1+5\times10^{-3}}{\text{fb(rec)}}$ | μs    | no Rx input at<br>RTIP/RRING          |

| ( Figure 10)          | SCR period - in lock                                     | TPR (il) | -                                    | fb(rec)             | -                                         | μs    | Rx input<br>present at RTIP/<br>RRING |

|                       | SCR pulse width High                                     | Trch     | TPR/2<br>- 200                       | TPR<br>2            | TPR/2<br>+ 200                            | ns    |                                       |

|                       | Rx signal input at RTIP/<br>RRING<br>frequency tolerance | RXTOL    | -50                                  | 0                   | +50                                       | ppm   |                                       |

|                       | RD delay from SCR falling edge                           | Trdd     | -500                                 | -                   | 500                                       | ns    | into 20 pF load                       |

|                       | Transition time on any digital output                    | Тто      | -                                    | -                   | 20                                        | ns    | into 20 pF load                       |

| Transmit              | SCT_E period                                             | ТРТ      | -100ppm                              | 1/Data Rate         | +100ppm                                   | μs    |                                       |

| Timing<br>(Figure 10) | SCT_E input pulse width High                             | Ттwні    | 3                                    | $\frac{1}{2fb(tx)}$ | 10                                        | μs    |                                       |

|                       | SCT_E output pulse width High                            | Ттwно    | 1/2fb(tx)<br>-200                    | $\frac{1}{2fb(tx)}$ | 1/2fb(tx)<br>+ 200                        | μs    |                                       |

|                       | TD setup to SCT_E rising edge                            | TTSU     | 700                                  | -                   | -                                         | ns    |                                       |

$<sup>1. \ \, \</sup>text{Typical values are at 25 °C and are for design aid only; not guaranteed and not subject to production testing.}$

<sup>3.</sup>  $fb(tx) = Frequency of transmit bitrate clock on <math>\overline{SCT}$  input.

<sup>2.</sup> fb (rec) = Frequency of incoming recovered datastream.

Table 10: AC Timing Characteristics (Over Recommended Range) – continued

| ı                  | Parameter                                               | Symbol | Min  | Typ <sup>1</sup> | Max  | Units | Test<br>Conditions |

|--------------------|---------------------------------------------------------|--------|------|------------------|------|-------|--------------------|

| Transmit<br>Timing | TD hold time after SCT_E rising edge                    | Ттн    | 700  | -                | -    | ns    |                    |

| (Figure 10)        | Transition time on any digital input                    | Тті    |      |                  | 40   | ns    |                    |

|                    | SCT_E input frequency tolerance (with respect to fb(tx) | TXTOL  | -100 | 0                | +100 | ppm   |                    |

| Crystal            | XTALI input frequency                                   | FXTAL  | _    | 8.192            | _    | MHz   |                    |

| Tolerances         | XTALI frequency tolerance                               | FMTOL  | -100 | 0                | +100 | ppm   |                    |

| Reset Timing       | RST pulse width Low                                     | TRWL   | 1000 | =                | -    | ns    |                    |

- 1. Typical values are at 25 °C and are for design aid only; not guaranteed and not subject to production testing.

- 2. fb (rec) = Frequency of incoming recovered datastream.

- 3.  $fb(tx) = Frequency of transmit bitrate clock on <math>\overline{SCT_E}$  input.

Figure 10: EIA Timing

Table 11: Microprocessor Timing Characteristics (Over Recommended Range)

| Parameter                                                                      | Symbol          | Min        | Тур        | Max         | Units         | Test Conditions                             |

|--------------------------------------------------------------------------------|-----------------|------------|------------|-------------|---------------|---------------------------------------------|

| CS setup to RD or WR falling edge                                              | TCSU            | 15         | -          | -           | ns            | CLOAD = 20 pF                               |

| CS hold from RD or WR rising edge                                              | TCHR<br>TCHW    | 15         | -          | -           | ns            | CLOAD = 20 pF                               |

| ALE pulse width High                                                           | TALPW           | 35         | -          | -           | ns            | CLOAD = 100 pF                              |

| RD or WR hold from ALE rising edge                                             | Trwh            | 10         | -          | -           | ns            | CLOAD = 100 pF                              |

| ALE hold from RD or WR rising edge                                             | TALH            | 15         | -          | -           | ns            | CLOAD = 100 pF                              |

| ADDR setup to ALE falling edge                                                 | TASU            | 15         | -          | -           | ns            | CLOAD = 100 pF                              |

| ADDR hold from ALE falling edge                                                | Тан             | 15         | -          | -           | ns            | CLOAD = 100 pF                              |

| WR pulse width Low                                                             | TWPW            | 95         | -          | -           | ns            | CLOAD = 100 pF                              |

| RD hold time after BSY High                                                    | Trdh            | 0          | -          | -           | ns            | $CLOAD = 100 \text{ pF on } \overline{RD}$  |

| DATA valid from RD falling edge                                                | TDPR            | 5          | -          | 70          | ns            | CLOAD = 100 pF                              |

| DATA hold from RD rising edge                                                  | TDHR            | 2          | -          | 15          | ns            | CLOAD = 100 pF                              |

| BSY Low delay from RD or WR Low                                                | Твр             | 5          | -          | 55          | ns            | CLOAD = $20 \text{ pF} / 2 \text{ k}\Omega$ |

| BSY Low duration                                                               | TBWL            | 122        | -          | 344         | ns            | CLOAD = $20 \text{ pF} / 2 \text{ k}\Omega$ |

| DATA setup to WR rising edge                                                   | TDSUW           | 30         | -          | -           | ns            | CLOAD = 100 pF                              |

| DATA hold from WR rising edge                                                  | TDHW            | 25         | -          | -           | ns            | CLOAD = 100 pF                              |

| $\overline{\text{INT}}$ clear after $\overline{\text{RD}}$ High for ADDR = 08h | TDCI            | 244        | -          | 470         | ns            | Cload = $20 \text{ pF} / 2 \text{ k}\Omega$ |

| 1. Typical values are at 25° C and are for design aid                          | only; not guara | inteed and | l not subj | ect to prod | luction testi | ng.                                         |

Figure 11: Microprocessor Timing - Read Operations

Figure 12: Microprocessor Timing - Write Operations

# **REGISTER DEFINITIONS**

## Introduction

The LXT441 incorporates a total of 19 registers, 8 Write and 11 Read registers. Refer to Table 12 for a complete list of register designations and addresses. Register addresses and other hexadecimal numbers are represented as "0xnn" where "nn" is the hex value.

**Table 12: LXT441 Register Set**

| Address  |          | Write Registers            |     | Read Registers            |

|----------|----------|----------------------------|-----|---------------------------|

| AD<7:0>  | WRx      | Name                       | RDx | Name                      |

| xxx00000 | WR0      | Device Control Register    | RD0 | readback of WR0           |

| xxx00001 | WR1      | Transmit Control Register  | RD1 | readback of WR1           |

| xxx00010 | WR2      | Receive Control Register   | RD2 | readback of WR2           |

| xxx00011 | Reserved |                            |     |                           |

| xxx00100 | Reserved |                            |     |                           |

| xxx00101 | WR5      | EIA Select Register        | RD5 | readback of WR5           |

| xxx00110 | Reserved |                            |     |                           |

| xxx00111 | WR7      | Transmit EIA Data Register | RD7 | Receive EIA Data Register |

| xxx01000 | WR8      | Interrupt Enable Register  | RD8 | Interrupt Status Register |

| xxx01001 | WR9      | EIA Control Register       | RD9 | EIA Status Register       |

| xxx01010 | Reserved |                            | RDA | Device Status Register    |

| xxx01011 | Reserved |                            | RDB | Rx Slicer Level Register  |

| xxx01100 | WRC      | Rx Code Interrupt Enables  | RDC | Rx Codes Register         |

| xxx01101 | Reserved |                            | RDD | Invalid BPV Counter       |

| xxx01110 | Reserved |                            |     |                           |

| xxx01111 | Reserved |                            |     |                           |

Table 13: LXT441 Register Bit Mapping

|                                      |     |      |        |        |         |        |        |        | -      |                    |

|--------------------------------------|-----|------|--------|--------|---------|--------|--------|--------|--------|--------------------|

| Register                             | R/W | Addr | b7     | b6     | b5      | b4     | b3     | b2     | b1     | b0                 |

| Device<br>Control                    | R/W | 0x00 | 0      | OCU    | TCCT    | SCT_EN | 0      | 0      | MODE1  | MODE0              |

| Transmit<br>Control                  | R/W | 0x01 | BONDEN | CALLMD | 0       | TX_MRK | ZS_DIS | TX_CMI | TX_OOS | TX_OOF             |

| Receive<br>Control                   | R/W | 0x02 | DSU_LP | TX_DLP | CSU_LP  | FILFCE | FFILT3 | FFILT2 | FFILT1 | FFILT0             |

| EIA Select                           | R/W | 0x05 | 0      | 0      | EIAREG  | 0      | 0      | 0      | 0      | 0                  |

| Tx EIA Data                          | W   | 0x07 | D1     | D2     | D3      | D4     | D5     | D6     | D7     | X, C, or<br>D8     |

| Rx EIA Data                          | R   | 0x07 | D1     | D2     | D3      | D4     | D5     | D6     | D7     | X, BF, C,<br>or D8 |

| Interrupt<br>Enable                  | W   | 0x08 | EIADEL | IDEL   | RX_CODE | V_OFL  | XBPV   | FSYNC  | RSYNC  | ACTIVE             |

| Interrupt<br>Status                  | R   | 0x08 | EIADEL | IDEL   | RX_CODE | V_OFL  | XBPV   | FSYNC  | RSYNC  | ACTIVE             |

| EIA Control                          | W   | 0x09 | FC_DCE | DSR    | DCD     | RI     | CTS    | FC_DTE | DTR    | RTS                |

| (reset value)                        |     |      | (0)    | (1)    | (1)     | (0)    | (1)    | (0)    | (1)    | (1)                |

| EIA Status                           | R   | 0x09 | FC_DCE | DSR    | DCD     | RI     | CTS    | FC_DTE | DTR    | RTS                |

| Device Status                        | R   | 0x0A | RLOS   | FSYNC  | ACTIVE  | ISTATE | LL3    | LL2    | LL1    | LL0                |

| Rx Slicer<br>Level                   | R   | 0x0B | MAG7   | MAG6   | MAG5    | MAG4   | MAG3   | MAG2   | MAG1   | MAG0               |

| Rx Code                              | W   | 0x0C | MRK_EN | ZSC_EN | CMI_EN  | OOS_EN | OOF_EN | DLP_EN | 0      | UNM_EN             |

| Interrupt<br>Enable<br>(reset value) |     |      | (1)    | (0)    | (1)     | (0)    | (0)    | (0)    | (0)    | (0)                |

| Rx Codes                             | R   | 0x0C | RX_DMI | RX_ZSC | RX_CMI  | RX_OOS | RX_OOF | RX_DLP | RX_UMC | UNMTCH             |

| BPV Count                            | R   | 0x0D | IBPV7  | IBPV6  | IBPV5   | IBPV4  | IBPV3  | IBPV2  | IBPV1  | IBPV0              |

<sup>1.</sup> A Low on the  $\overline{RST}$  input will force all register bits to 0, except where specified.

Table 14: Register WR0 - Device Control - Address 0x00

| b7 | b6  | b5   | b4     | b3 | b2    | b1    | b0    |

|----|-----|------|--------|----|-------|-------|-------|

| -  | OCU | TCCT | SCT_EN | -  | FTEST | MODE1 | MODE0 |

| Bit       | Mnemonic           |                      |                                                                                                                                      | Funct              | tion                                                                              |  |  |

|-----------|--------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------|--|--|

| b7        | -                  | Reserved. Pro        | Reserved. Program to 0.                                                                                                              |                    |                                                                                   |  |  |

| b6        | OCU                |                      | OCU and DSU Mode Selection. Controls timing sources in conjunction with TCCT (see TCCT bit description for additional information).  |                    |                                                                                   |  |  |

| b5        | TCCT               | Tail Circuit.        | Controls timing sources                                                                                                              | s in conjun        | ection with OCU as follows:                                                       |  |  |

|           |                    | Bits<6:5>            | Source for SCT_E                                                                                                                     |                    | Source for TCLK                                                                   |  |  |

|           |                    | 10<br>11<br>00<br>01 | XTALI via Internal<br>N/A<br>RCLK<br>N/A                                                                                             | Oscillator         | XTALI via Internal Oscillator <sup>1</sup> SCT_E input pin  RCLK  SCT_E input pin |  |  |

| b4        | SCT_EN             |                      | Serial Clock Transmit Enable. $0 = \overline{SCT}E$ pin set to high impedance state; $1 = \overline{SCT}E$ pin enabled as an output. |                    |                                                                                   |  |  |

| b3        | -                  | Reserved. Pro        | gram to 0.                                                                                                                           |                    |                                                                                   |  |  |

| b2        | FTEST              | Factory Test (1      | FTEST). Program to                                                                                                                   | 0.                 |                                                                                   |  |  |

| b<1:0>    | MODE<1:0>          | Mode Select (N       | MODE<1:0>). Sets N                                                                                                                   | Mode and I         | Line Rate as follows:                                                             |  |  |

|           |                    | Bits<1:0>            | Operating Mode                                                                                                                       | Line Rate          | <u>1</u>                                                                          |  |  |

|           |                    | 00                   | DDS-PRI                                                                                                                              | 56 kbps            |                                                                                   |  |  |

|           |                    | 11                   | DDS-PRI                                                                                                                              | 56 kbps            |                                                                                   |  |  |

|           |                    | 01<br>10             | DDS-SC<br>CC-64K                                                                                                                     | 72 kbps<br>72 kbps |                                                                                   |  |  |