# SAB 82289 Bus Arbiter for SAB 80286 Processors

#### SAB 82289-6 up to 12 MHz

- Supports multimaster system bus arbitration protocol

- Synchronizes SAB 80286 processor with multimaster bus

- Compatible with IEEE 796 standard bus (Multibus®)

#### SAB 82289 up to 16 MHz

- Three modes of bus release operation for flexible system configuration

- Supports parallel, serial and rotating priority resolving schemes

| in Configuration |              |                 | Pin Names             |                                            |

|------------------|--------------|-----------------|-----------------------|--------------------------------------------|

|                  |              |                 | S0/HOLD               | Status S0 /Hold Input                      |

|                  |              |                 | \$1, M/ <del>IO</del> | Status Inputs                              |

|                  |              |                 | BUSY                  | Busy Input/Output                          |

| =                | <u> </u>     | 20 1/55         | READY                 | Ready Input                                |

| M/10 🔲 1         |              | 20 VCC          | SYSB/RESB             | System/Resident Bus                        |

| READY 2          |              | 19 🔲 .ST        | RESET                 | Processor Reset                            |

| rsb/RESB ☐ 3     |              | 18 30/HOLD      | BCLK                  | Bus Clock                                  |

| RESET 4          |              | 17 CLK          | INIT                  | Initialize                                 |

|                  |              |                 | BREQ                  | Bus Request                                |

| <u>BCLK</u> ☐ 5  | SAB<br>82289 | 16 DOCK ALWAYS/ | BPRO                  | Bus Priority Out                           |

| ĪNĪT ☐6          | 02207        | 15 CBOLCK       | BPRN                  | Bus Priority In                            |

| BREO 7           |              | 14 LLOCK        | CLK                   | System Clock                               |

| BPRÖ ☐ 8         |              | 13 AEN          | AEÑ                   | Address Enable                             |

| BPRN _ 9         |              | 12 CBRQ         | ALWAYS/<br>CBQLCK     | Always Release/<br>Common Bus Request Lock |

| GND 🗖 10         |              | 11 BUSY         | LLOCK                 | Level Lock                                 |

| <u> </u>         |              |                 | CBRQ                  | Common Bus Request                         |

|                  |              |                 | LOCK                  | Bus Lock                                   |

|                  |              |                 | VCC                   | +5V                                        |

|                  |              |                 | GND                   | Ground (0 V)                               |

The SAB 82289 Bus Arbiter is a 5 V, 20-pin MYMOS component for use in multiple bus master SAB 80286 systems. The SAB 82289 provides a compact solution to system bus arbitration for the SAB 80286 CPU.

Multibus® is a registered trademark of Intel Corporation.

The complete IEEE 796 Standard bus arbitration protocol is supported. Three modes of bus release operation support a number of bus usage models.

## **Pin Definitions and Functions**

| Symbol    | Pin   | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |         |                                                                                                                                                                                |  |  |

|-----------|-------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| M/ĬŌ, Ŝī  | 1, 19 | I                       | STATUS INPUTS are the status input signal pins from the SAB 80286 processor. The arbiter decodes these inputs together with the \$\overline{SO}\$/HOLD input to initiate bus request and surrender actions. A bus cycle is started when either \$\overline{SI}\$ or \$\overline{SO}\$ is sampled low at the falling edge of CLK. The SAB 80286's \$\overline{SI}\$ and \$M/IO\$ pins meet the setup and hold time requirement of these pins.  SAB 80286 Bus Cycle Status Encoding                                                                                                                                                                                                                                       |                      |         |                                                                                                                                                                                |  |  |

|           |       |                         | M/IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <u>\$1</u>           | S0/HOLD | Type of Bus Cycle                                                                                                                                                              |  |  |

|           |       |                         | S1 and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | M/ <del>IO</del> pin |         | Interrupt acknowledge I/O read I/O write None, bus idle Halt or shutdown Memory read Memory write None, bus idle utput of another bus master, the d high during TS, the Status |  |  |

| READY     | 2     | 1                       | READY is an active-low signal which indicates the end of the bus cycle. The SAB 80286 halt or shutdown cycle does not require READY to terminate the bus cycle. Setup and hold times for this pin must be met for proper operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |         |                                                                                                                                                                                |  |  |

| SYSB/RESB | 3     | I                       | SYSTEM BUS/RESIDENT BUS is an input signal which determines whether the multimaster system bus is required for the current bus cycle. The signal can originate from address mapping circuitry such as a decoder or PROM attached to the processor address and status pins. The arbiter will request or retain control of the multimaster system bus when the SYSB/RESB pin is sampled high at the end of the TS bus state. During an interrupt acknowledge cycle, this input is sampled on every falling edge of CLK starting at the end of the TS state until either SYSB/RESB is sampled high or the bus cycle is terminated by the READY signal. Setup and hold times for this pin must be met for proper operation. |                      |         |                                                                                                                                                                                |  |  |

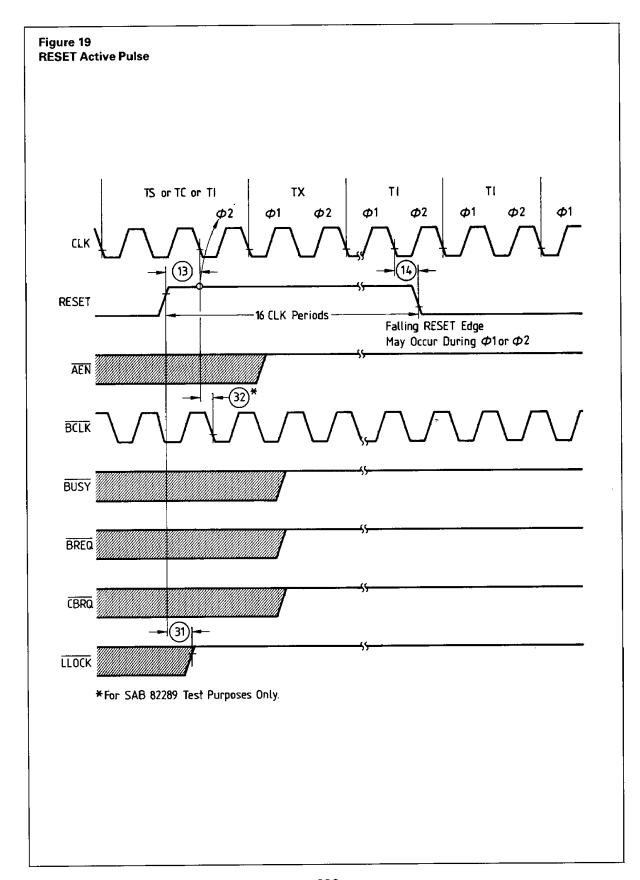

| RESET     | 4     | I                       | PROCESSOR RESET is an active-high input synchronous to the system, clock (CLK). RESET is the processor initialization and an indication to the arbiter to release the multimaster bus and clear any pending request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |         |                                                                                                                                                                                |  |  |

| BCLK      | 5     | ł                       | BUS CLOCK is the multimaster system bus clock to which the multimaster bus interface signals are synchronized.  BCLK can be asynchronous to CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |         |                                                                                                                                                                                |  |  |

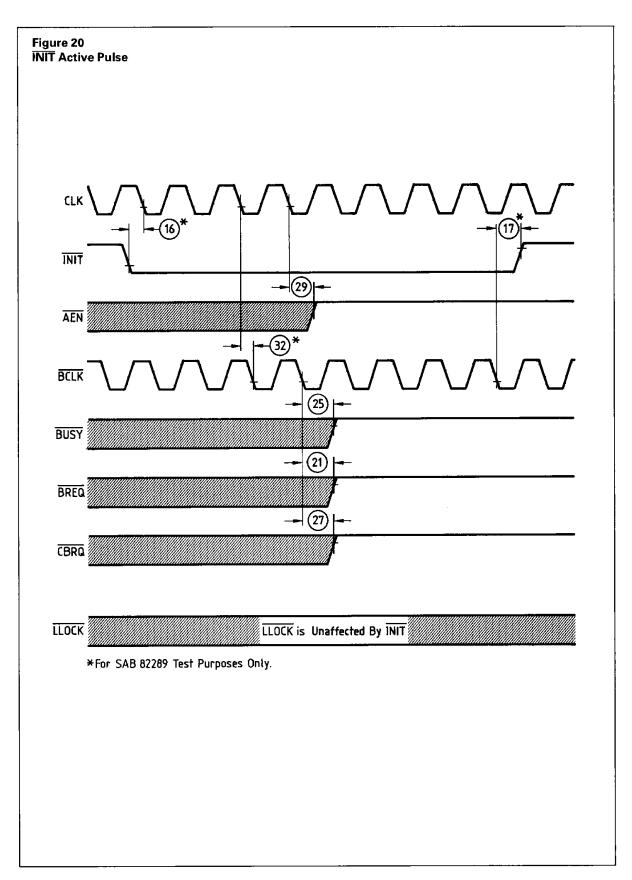

| INIT      | 6     | l                       | INITIALIZE is an active-low Multibus signal used to reset all arbiters on the Multibus system. It will cause the release of the multimaster bus, but will not clear the pending bus master request so that the arbiter can again request the multimaster bus. No arbiters have the use of the multimaster bus immediately after initialization. INIT is an asynchronous signal to CLK.                                                                                                                                                                                                                                                                                                                                  |                      |         |                                                                                                                                                                                |  |  |

# Pin Definitions and Functions (continued)

| Symbol | Pin | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|-----|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BREQ   | 7   | 0                       | BUS REQUEST is an active-low output signal used in the parallel and rotating priority resolving schemes. The arbiter activates BREQ to request the use of the multimaster system bus. The arbiter holds BREQ active as long as it is requesting or has possession of the multimaster system bus.                                                                                                                                                                                                                                                                                                                                                                 |

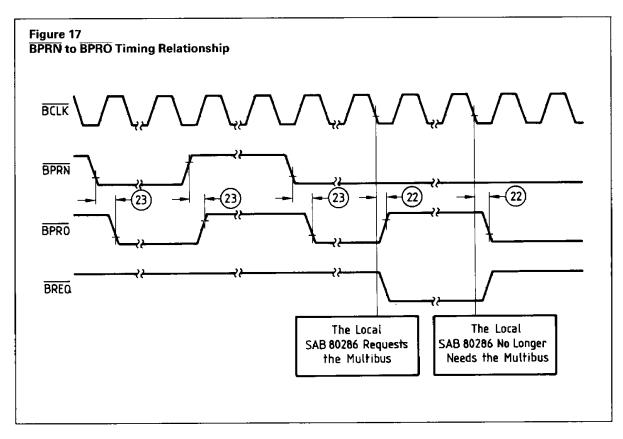

| BPRO   | 8   | 0                       | BUS PRIORITY OUT is an active-low output signal used in serial priority resolving scheme. BPRO is connected to BPRN of the next lower priority arbiter to grant or revoke priority from that arbiter.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BPRN   | 9   | I                       | BUS PRIORITY IN is an active-low input indicating that this arbiter has the highest priority of any arbiter requesting the system bus. BPRN high signals the arbiter that a higher priority arbiter is requesting or has possession of the system bus. Setup and hold times for this pin must be met for proper operation.                                                                                                                                                                                                                                                                                                                                       |

| BUSY   | 11  | I/O<br>(open-<br>drain) | BUSY is a Multibus signal which is asserted when the system bus is in use.  BUSY is an open drain input/output requiring an external pullup resistor.  As an input BUSY asserted indicates when the Multibus is in use. Setup and hold times must be met for proper operation.  As an output BUSY is asserted to signal when this arbiter has taken control of the Multibus.                                                                                                                                                                                                                                                                                     |

| CBRQ   | 12  | I/O<br>(open-<br>drain) | COMMON BUS REQUEST is a Multibus signal that indicates when an arbiter is requesting the Multibus. This pin is an open-drain input/output requiring an external pullup resistor. As an input CBRQ indicates that another arbiter is requesting the multimaster system bus. The input function of this pin is enabled by the CBQLCK signal. Setup and hold times for this pin must be met for proper operation.  As an output CBRQ is asserted to indicate that this arbiter is requesting the Multibus. The arbiter pulls CBRQ low when it issues BREQ. The arbiter releases CBRQ when it obtains the Multibus.                                                  |

| AEN    | 13  | 0                       | ADDRESS ENABLE is the output of the arbiter which goes directly to the processor's address latches, the SAB 82288 bus controller and the SAB 82284 clock generator. AEN asserted causes the bus controller and address latches to enable their output drivers. AEN also drives the clock generator's ARDYEN input to enable its asynchronous ready input (ARDY).  AEN can also be used as an active-low hold acknowledge to a bus master other than the SAB 80286. It signals to the bus master that control of the system bus has been relinquished when AEN is inactive (high).  Note that AEN goes active relative to BCLK and goes inactive relative to CLK. |

# Pin Definitions and Functions (continued)

| Symbol            | Pin | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                              |

|-------------------|-----|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

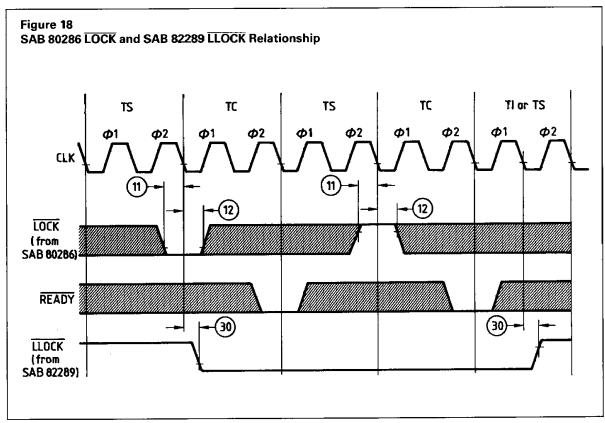

| LLOCK             | 14  | 0                       | LEVEL LOCK is an active-low output signal decoded from the processor LOCK signal. LLOCK can be used as Multibus LOCK when buffered with a tri-state buffer enabled by the AEN signal. LLOCK will be cleared by RESET but not by INIT.                                                                                                                 |

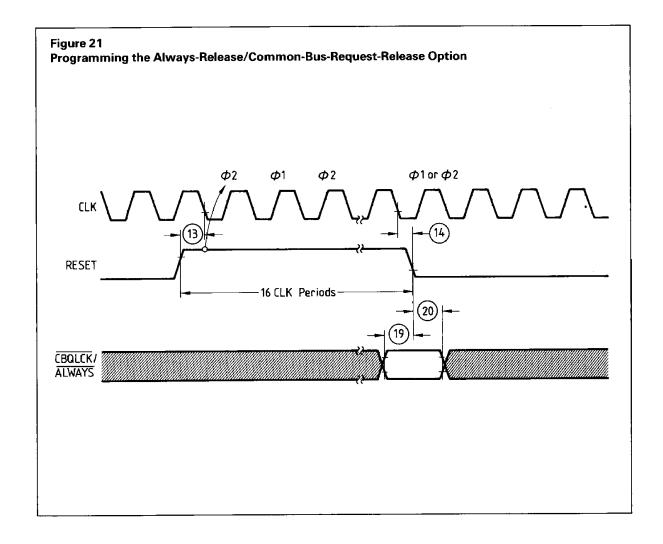

| ALWAYS/<br>CBQLCK | 15  | ı                       | ALWAYS RELEASE or COMMON BUS REQUEST LOCK can be programmed at processor reset to be either the ALWAYS RELEASE (ALWAYS) strapping option or the COMMON BUS REQUEST LOCK (CBQLCK) control input. Setup and hold times for this pin must be met for proper programming.                                                                                 |

|                   |     |                         | When this pin is low during the falling edge of processor reset (ALWAYS option) the arbiter is programmed to surrender the multimaster system bus after each bus transfer cycle. The SAB 82289 will remain in the ALWAYS RELEASE mode until it is reprogrammed during the next processor reset.                                                       |

|                   |     |                         | The bus arbiter is programmed to support the COMMON BUS REQUEST LOCK function by forcing this input pin high during the falling edge of the processor reset.                                                                                                                                                                                          |

|                   |     |                         | CBQLCK itself is an active-low signal which when active prevents the arbiter from surrendering the multimaster system bus to a common bus request through the CBRQ input pin.                                                                                                                                                                         |

| LOCK              | 16  |                         | LOCK is a processor-generated signal which when asserted (low) prevents the arbiter from surrendering the multimaster system bus to any other bus arbiter, regardless of its priority. LOCK is sampled by the arbiter at the end of the TS (status) bus state. Setup and hold times for this pin must be met for proper operation.                    |

| CLK               | 17  | 1                       | SYSTEM CLOCK accepts the CLK signal from the SAB 82284 clock generator chip as the timing reference for the bus arbiter and processor interface signals.                                                                                                                                                                                              |

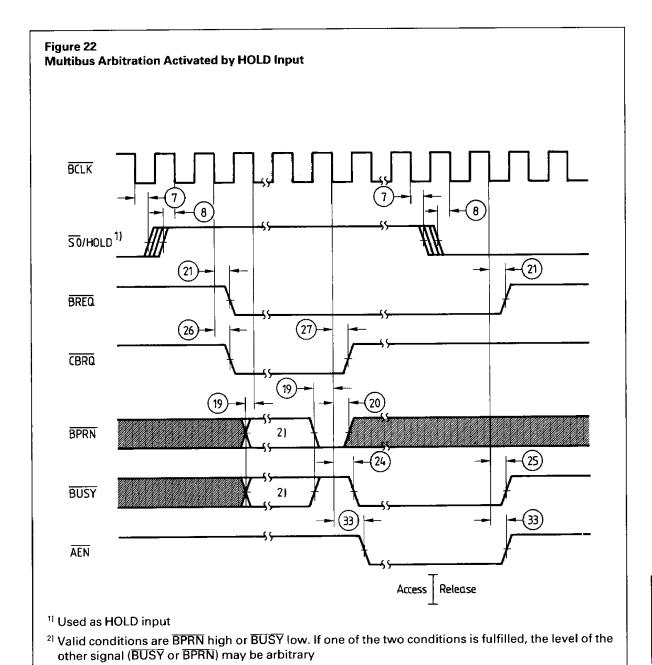

| SÖ/HOLD           | 18  | 9                       | STATUS INPUT \$\overline{S0}\$ or HOLD is either the \$\overline{S0}\$ status signal from the SAB 80286 or the HOLD signal from some other bus master. The function of this input is established during the processor reset of the SAB 82289 bus arbiter. The SAB 80286 \$\overline{S0}\$ pin meets the setup and hold time requirements of this pin. |

|                   |     |                         | The \$\overline{SO}\$ pin function is selected by forcing this input high during the falling edge of processor reset if the SAB 82289 is used to support an SAB 80286 processor, the \$\overline{SO}\$ output of the processor will be high during reset.                                                                                             |

|                   |     |                         | In supporting the SAB 80286 processor, the SAB 82289 decodes the SO pin together with the other status input ST and M/IO to determine the beginning of a processor bus cycle and initiate bus request and surrender actions.                                                                                                                          |

|                   |     |                         | The HOLD function of the \$\overline{S0}\$/HOLD pin is selected by holding this input low during the falling edge of processor reset. When supporting a bus master other than SAB 80286 the SAB 82289 monitors the HOLD signal to initiate bus request and surrender actions.                                                                         |

| VCC               | 20  |                         | POWER SUPPLY (+5V)                                                                                                                                                                                                                                                                                                                                    |

| GND               | 10  |                         | GROUND (0V)                                                                                                                                                                                                                                                                                                                                           |

### **Functional Description**

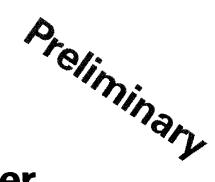

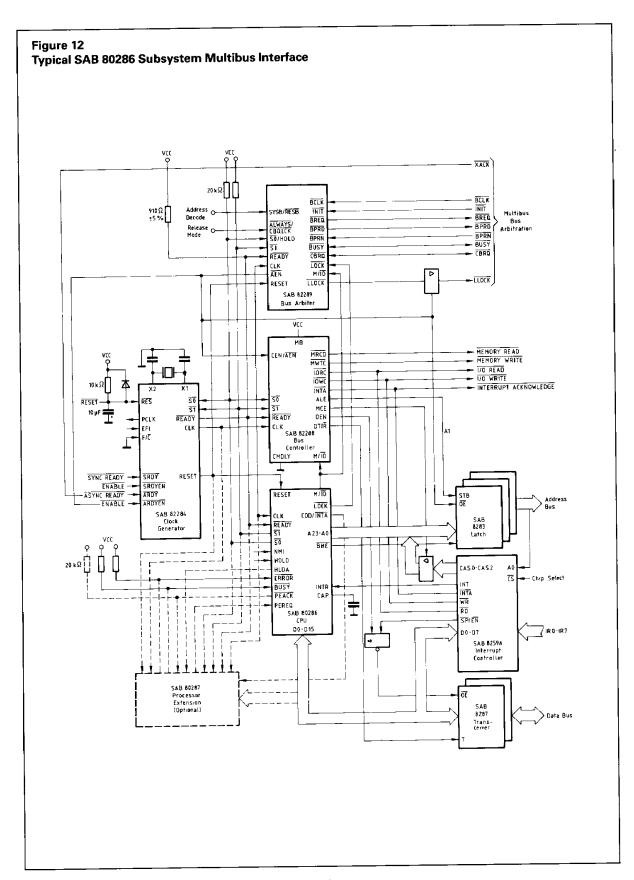

The SAB 82289 bus arbiter in conjunction with the SAB 82288 bus controller and the SAB 82284 clock generator interfaces the SAB 80286 processor or some other bus master to a multimaster system bus. The arbiter multiplexes a processor to a multimaster system bus. It avoids contention with other bus masters.

The SAB 82289 has two separate state machines which communicate through bus request and release logic. The processor interface state machine is synchronous with the local system clock (CLK) and the multimaster system bus interface state machine is synchronous with the bus clock (BCLK).

The SAB 82289 performs all signaling to request, obtain, and release the system bus. External logic is used to determine which bus cycles require the system bus and to resolve priorities of simultaneous requests for control of the system bus.

#### SAB 82289 with SAB 80286

In a SAB 80286 system using a SAB 82289 bus arbiter, the SAB 80286 processor is unaware of the arbiter's existence and issues commands as though it had exclusive use of a multimaster system bus, such as Multibus. If the processor cycle requires Multibus access, the arbiter requests control of the Multibus. Until the request is granted the SAB 82289 keeps  $\overline{\text{AEN}}$  disabled to prevent the SAB 82288 bus controller and the address latches from accessing

the Multibus. AEN inactive also disasserts the asynchronous ready enable (ARDYEN) input of the SAB 82284 clock chip so that the system bus will appear as "NOT READY" to the SAB 80286 processor.

Once the SAB 82289 bus arbiter has acquired the bus, it will assert  $\overline{AEN}$  allowing the SAB 82288 bus controller and the address latches to access the system bus and asserting the  $\overline{ARDYEN}$  input of the SAB 82284 clock chip.

Typically, once the data transfer command has been issued by the SAB 82288 and the data transfer has taken place, a transfer acknowledge (XACK) signal is returned to the processor on the multimaster system bus to indicate "READY" from the accessed slave device. The processor remains in a series of "wait states" (repeated TC states) until the addressed device responds with XACK asserted signal to the SAB 82284's ARDY input and the SAB 82284 asserts READY to the processor. The processor then completes its bus cycle.

#### SAB 82289 with Other Bus Masters

When supporting other bus masters, the \$\overline{S0}\$/HOLD and \$\overline{READY}\$ pins of the bus arbiter can be connected to the "hold" pin of that master. The inverted \$\overline{AEN}\$ signal from the SAB 82289 can be used as the hold acknowledge (HLDA) input for the other bus master.

The bus master sends a HOLD signal to the bus arbiter when it needs the system bus for a memory access. If the arbiter currently controls the system bus,  $\overline{AEN}$  will be active. Otherwise  $\overline{AEN}$  will be inactive and the arbiter will request control of the system bus. The bus master will have to wait until the SAB 82289 has asserted  $\overline{AEN}$  (low) before it starts its bus cycle.

When the bus master no longer requires the Multibus it will have to inactivate the HOLD signal. The arbiter interprets the Multibus access as a single bus cycle which is terminated by HOLD going inactive (low). Thus the arbiter will not release the Multibus to any other bus master during a bus access cycle.

#### **Processor Cycle Definition**

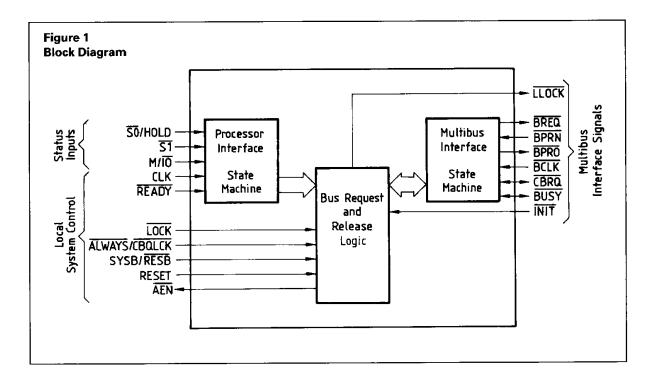

Any SAB 80286 system which gains access to the Multibus through the SAB 82289 bus arbiter uses an internal clock which is one half the frequency of the system clock (CLK) (see figure 2). Knowledge of the phase of the local bus master internal clock is required for proper SAB 82289 control of the SAB 80286 interface to Multibus. The local bus master informs the bus arbiter of its internal clock phase when it asserts the status signals. The SAB 80286's  $\overline{S0}$  and  $\overline{S1}$  status signals are always first asserted in phase 1 of the local bus master's internal clock.

#### **Bus State Definition**

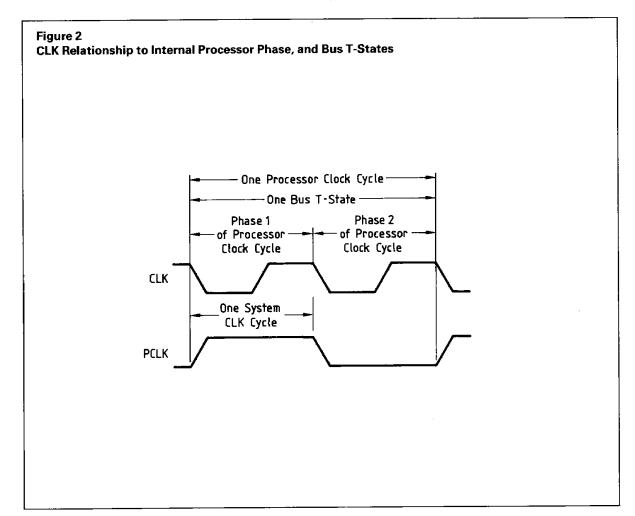

The SAB 82289 bus arbiter has three processor bus states (see figure 3): idle (TI), status (TS), command (TC). Each bus state is two CLK cycles long. Bus state phases correspond to the internal CPU clock phases.

#### **Bus Cycle Definition**

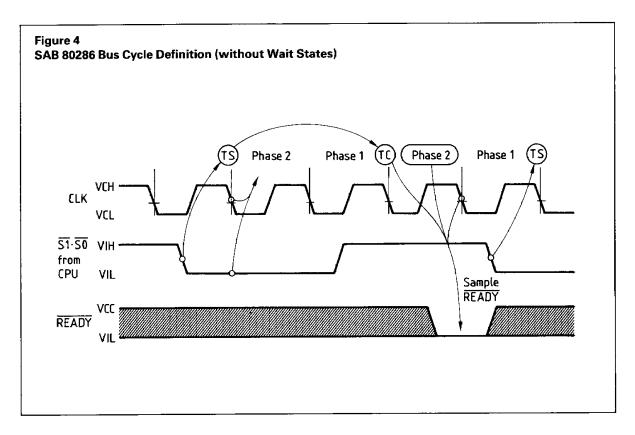

The  $\overline{S1}$  and  $\overline{S0}$  status inputs are sampled by the SAB 82289 on the falling edge of CLK and signal the start of a bus cycle by going active (low). The TS bus state is defined to be the two CLK cycles during which either  $\overline{S1}$  or  $\overline{S0}$  is active (see figure 4). When either  $\overline{S1}$  or  $\overline{S0}$  is sampled low, the next CLK cycle is considered the second phase of the associated processor clock cycle.

The arbiter enters the TC bus state after the TS state. The shortest bus cycle may have one TS state and one TC state. Longer bus cycles are formed by repeating TC states. A repeated TC bus state is called a wait state.

The READY input determines whether the current TC bus state is to be repeated. The READY input has the same timing and effect for all bus cycles. READY is sampled at the end of each TC bus state to see if it is active. If sampled high, the TC bus state is repeated. This is called inserting a wait state.

When READY is sampled low, the current bus cycle is terminated. Note that the bus arbiter may enter the TS bus state directly from TC if the status lines are sampled active (low) at the next falling edge of CLK (see figure 4). If neither of the status lines is sampled active at that time the SAB 82289 will enter the TI bus state. The TI bus state will be repeated until the status inputs are sampled active.

#### **Arbitration between Bus Masters**

The Multibus protocol allows multiple processing elements to compete with each other to access common system resources. Since the local SAB 80286 processor does not have exclusive use of the system bus, if the Multibus is "BUSY" the SAB 80286 processor will have to wait before it can access the system bus.

The SAB 82289 bus arbiter provides an integrated solution for controlling access to a multimaster system bus. The bus arbiter allows both higher and lower priority bus masters to acquire the system bus depending on which release mode is used. In general higher priority masters obtain the bus immediately after any lower priority master completes its present transfer cycle. Lower priority bus masters obtain the bus when a higher priority master is not accessing the system bus or the proper surrender conditions exist. The SAB 82289 handles this arbitration in a manner completely transparent to the bus master (e.g. SAB 80286 processor).

At the end of each transfer, the arbiter may retain or release the system bus. This decision is controlled by the processor state, bus arbitration inputs and arbiter strapping options (see releasing the Multibus, ahead).

#### **Priority Resolving Techniques**

Some means of resolving priority between bus masters requesting the multimaster bus simultaneously must be provided. The SAB 82289 bus arbiter supports parallel, serial and rotating system bus priority resolving techniques. All of these techniques are based on the concept that, at a given time, one bus master will have priority above all the others.

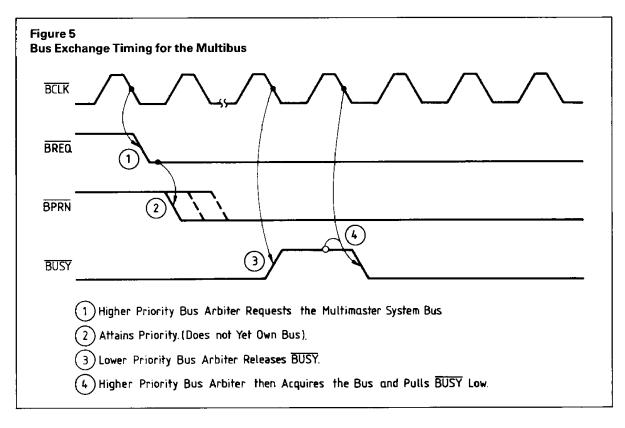

An individual arbiter is the highest priority arbiter requesting the Multibus when its BPRN input is asserted (low). The highest priority requesting arbiter cannot immediately seize the system bus. It must wait until the present bus transaction is completed. Upon completing its current transaction the present bus owner surrenders the bus by releasing BUSY.

BUSY is an active-low "wired OR" Multibus signal connecting all bus arbiters on the system bus. When BUSY goes inactive, the arbiter which has requested the system bus and presently has bus priority (BPRN low), seizes the bus by pulling BUSY low (see waveform in figure 5).

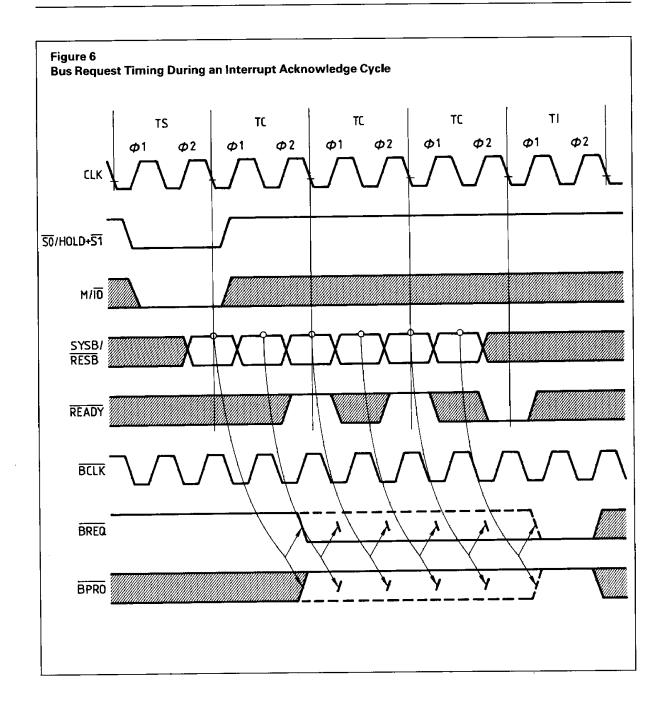

The generation of a multimaster bus request  $(\overline{BREQ})$  is controlled by the type of bus cycle and the SYSB/ $\overline{RESB}$  input. Whenever the processor signals the status for memory read, memory write, I/O read,

I/O write or interrupt acknowledge cycle, and  ${\sf SYSB/\overline{RESB}}$  is high at the end of TS, a bus request is generated.

When the status inputs indicate an interrupt acknowledge bus cycle, the arbiter allows external logic to decide (through the SYSB/RESB input) whether the interrupt acknowledge cycle should use the Multibus.

Figure 6 shows how SYSB/RESB is repeatedly sampled until it is sampled high or the bus cycle is terminated. If the bus cycle is completed (READY is sampled low) before SYSB/RESB is sampled high, the arbiter will not request the Multibus.

The SAB 82289 bus arbiter does not generate a separate BREQ for each bus cycle. Instead the SAB 82289 generates BREQ when it requests the bus and holds BREQ active during the time that it has possession of the bus. Note that all multimaster system bus requests (via BREQ) are synchronized to the system bus clock (BCLK).

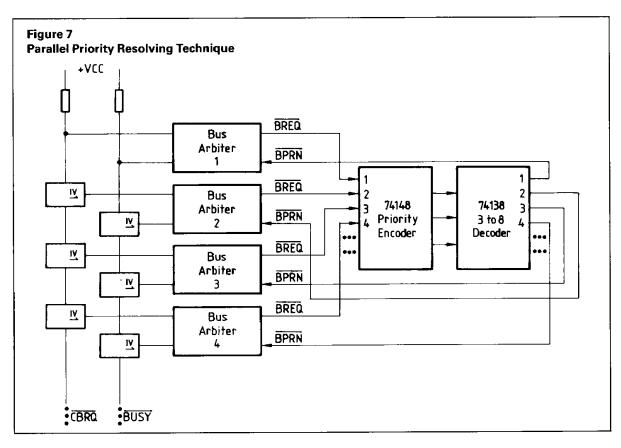

#### **Parallel Priority Resolving Technique**

The parallel priority resolving technique requires a separate bus request line (BREQ) for each arbiter on the multimaster system bus (see figure 7). Each BREQ line enters a priority encoder which generates the binary address of the highest priority BREQ line currently active. The binary address is decoded to select the BPRN line corresponding to the highest priority arbiter requesting the bus. In a parallel scheme, the BPRO output is not used.

The arbiter receiving priority (BPRN low) then allows its associated bus master onto the multimaster system bus as soon as the bus becomes available (i.e. the bus is no longer busy). Any number of bus masters may be accommodated in this way, limited only by the complexity of the external priority resolving circuitry. Such circuitry must resolve the priority within one BCLK period.

#### **Serial Priority Resolving Technique**

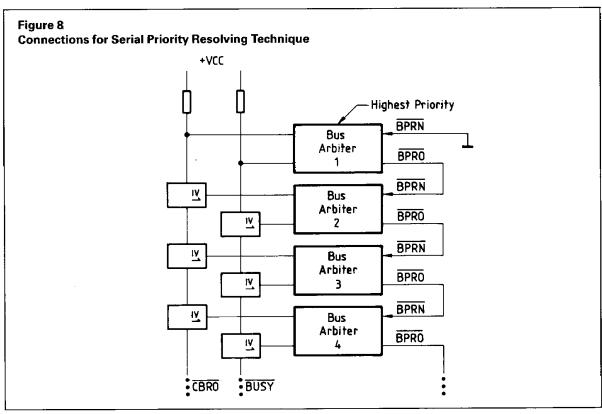

The serial priority resolving technique eliminates the need for the priority circuitry of the parallel technique by daisy-chaining the bus arbiters together, that is, connecting the higher priority arbiter's BPRO output to the BPRN of the next lower priority arbiter (see figure 8). The highest priority bus arbiter would have its BPRN tied low in this configuration, signifying to the arbiter that it always has the highest priority when requesting the system bus. In a serial scheme, the BREQ output is not used.

Since arbitration must be resolved within one BCLK period the number of arbiters connected together in the serial priority is limited by the arbiter's BPRN to BPRO propagation delay (18ns). For a 10 MHz Multibus BCLK, five SAB 82289 bus arbiters may be connected in serial configuration.

Maximum number of chained-priority devices = BCLK period

BPRN to BPRO delay

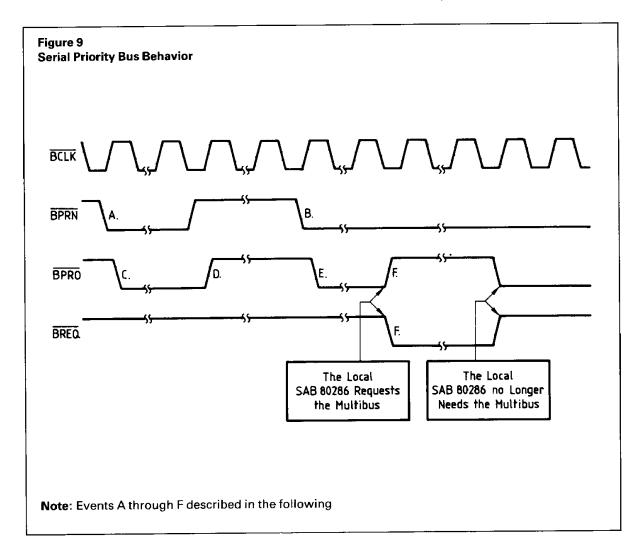

When using the serial priority resolving scheme, a higher priority arbiter (for example, arbiter 2, figure 8) passes priority to the next lower priority arbiter (arbiter 3) by asserting its BPRO signal (low). This asserts BPRN of next arbiter (arbiter 3) as shown in figure 9 event A and event B. An arbiter's BPRO is asserted if the arbiter has priority (BPRN is asserted) but is not accessing or requesting the system bus (as indicated by BREQ inactive as shown in figure 9 event C and event E for arbiter 3). Whenever a higher priority arbiter (arbiter 3) issues a bus request its BPRO goes inactive causing the next lower priority arbiter (arbiter 4) to lose its bus priority (figure 9 event F). Any arbiter (arbiter 3) will also bring its BPRO inactive if its BPRN goes inactive (from arbiter 2), thereby passing the loss of bus priority on to the lower priority arbiters (e.g. arbiter 4) as shown in figure 9 event D.

#### **Rotating Priority Resolving Technique**

The rotating priority resolving technique is similar to the parallel priority resolving technique except that priority is dynamically re-assigned. The priority encoder is replaced by a more complex circuitry which rotates priority between requesting arbiters, thus allowing each arbiter an equal chance to use the multimaster system bus over a given period of time.

# Selecting the Appropriate Priority Resolving Technique

The choice of a priority resolving technique involves a trade-off between external logic complexity and ease of Multibus access for the different bus masters in the system. The rotating priority resolving technique requires a substantial amount of external logic, but guarantees all the bus masters an equal opportunity to access the system bus. The serial priority resolving technique uses no external logic but has fixed bus master priority levels and can accomodate only a limited number of bus arbiters.

The parallel priority resolving technique is in general a compromise between the other two techniques (for example parallel priority configuration in figure 7 allows up to eight arbiters to be present on the Multibus, with fixed priority levels, while not requiring a large amount of complex external logic to implement).

#### Releasing the Multibus

Following a data transfer cycle on the Multibus, the SAB 82289 bus arbiter can either retain control of the system bus or release the bus for use by some other bus master. The SAB 82289 can operate in one of three modes, defining different conditions under which the arbiter relinquishes control of the multimaster system bus. These release modes are described in the table below.

If the arbiter was programmed to operate in Always Release Mode (mode 1) during the previous reset, it will surrender the Multibus after each complete transfer cycle. If the arbiter is not in Always Release Mode, it will not surrender the bus until the local SAB 80286 processor enters a halt state, the arbiter is forced off the bus by the loss of BPRN (mode 2 or 3), or by a common bus request when the CBRQ input is enabled by the CBQLCK input (mode 2).

CBRQ can save the bus exchange overhead in many cases. If CBRQ is high, it indicates to the bus master that no other master is requesting the bus and therefore the present bus master can retain the bus. Without CBRQ, only BPRN indicates whether or not another master is requesting the bus and that only if the other master is of higher priority. Between its bus transfer cycles the master must give up the bus in order to allow lower priority masters to take the bus if they need it. At the start of the master's next transfer cycle, the bus must be regained. If no other master has the bus, this can take approximately two BCLK periods. To avoid this overhead of unnecessarily giving up and regaining the bus when no other masters needs it, CBRQ is

#### SAB 82289 Release Modes

| Release Mode | Conditions under which the bus arbiter releases the system bus (unless cycles are LOCKed)                                                                                      |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode 1       | The bus arbiter always releases the bus at the end of each transfer cycle                                                                                                      |

| Mode 2       | The bus arbiter ratains the bus until:  ■ a higher-priority bus master requests the bus, driving BPRN high  ■ a lower-priority bus master requests the bus by pulling CBRQ low |

| Mode 3       | The bus arbiter retains the bus until:  • a higher-priority bus master requests the bus, driving BPRN high (CBRQ low ignored)                                                  |

extremely useful. Any master that wants but does not have the bus, must assert  $\overline{\text{CBRQ}}$  (low). If  $\overline{\text{CBRQ}}$  line is not asserted the bus does not have to be released, thereby eliminating the delay of regaining the bus at the start of the next cycle.

The LOCK input to the arbiter can be used to override any of the conditions shown in the table before. While LOCK is asserted, the arbiter will not surrender control of the Multibus to any other requesting arbiter. Note that the arbiter will surrender the Multibus (synchronous to BCLK) either in response to RESET or INIT signals independent of the current release mode or the state of the arbiter inputs.

The three bus release modes have the same operation when supporting either the SAB 80286 processor or some other bus master.

#### Selecting the Appropriate Release Mode

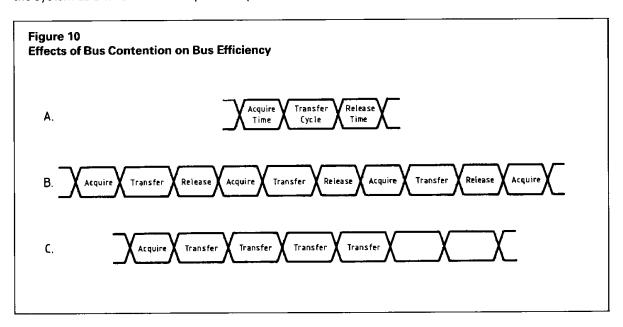

The choice of which release mode to use may affect the bus utilization of the individual subsystems, and the system as a whole. Mode-dependent performance variations are due to the bus acquisition/ release overhead. The effect of these acquire and release times on system bus efficiency is illustrated in figure 10.

An isolated transfer on the multimaster system bus is depicted in figure 10-A. Figure 10-B shows utilization for the bus arbiter operation in mode 1. The arbiter must request and release the system bus for each transfer cycle. Lower priority arbiters have easy access to the system bus, but overall bus efficiency is low. Bus utilization for a bus arbiter operating in mode 2 or 3 is shown in the figure 10-C. In this situation the arbiter acquires the bus once for a sequence of transfers. The arbiter retains the bus until forced off by another bus master's request as defined in table before.

The three release modes of the SAB 82289 allow the designer to optimize the system use of the Multibus.

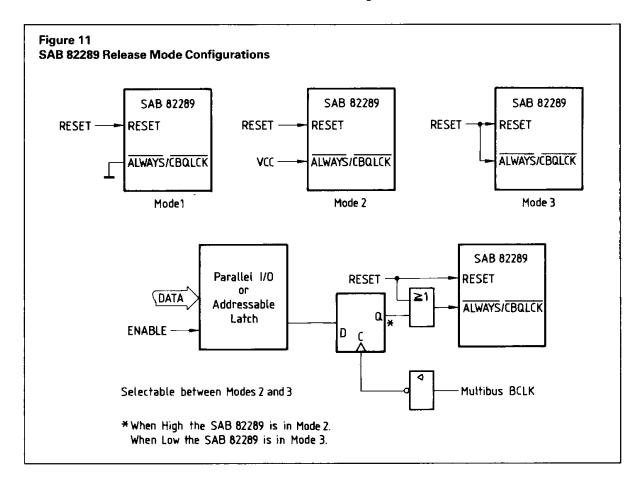

#### Configuring the SAB 82289 Release Mode

The SAB 82289 bus arbiter can be configured in any of its three bus release modes without additional hardware. It can also be configured to switch between mode 2 and mode 3 under software

control of the SAB 80286 processor, requiring that a parallel port or addressable latch be used to drive the ALWAYS/CBQLCK input pin of the SAB 82289 (see figure below).

#### Asserting the LOCK Signal

Independent of the particular release mode of the SAB 82289 bus arbiter, the SAB 80286 processor can assert a  $\overline{LOCK}$  signal synchronously to CLK to prevent the arbiter from releasing the Multibus. This software-controlled  $\overline{LOCK}$  signal prevents the SAB 82289 from surrendering the system bus to any other bus master, whether that bus master is of higher or lower priority. The  $\overline{LOCK}$  signal is typically used for implementing software semaphores for shared resources or for critical processes that must run in real-time.

The SAB 82289 LLOCK output is the Multibus timing-compatible signal asserted during all bus cycles which are locked together. The LLOCK is set or reset depending on processor LOCK at the end of the TS cycle. LLOCK will delay going inactive until the termination of the current transfer cycle.

The SAB 82289 will continue to assert the LLOCK signal retaining control of the Multibus until the end of the first "unLOCKed" SAB 80286 bus cycle (SAB 80286 disables its LOCK output on the last bus cycle indicating that no future locked cycles are needed). While the LOCK signal will force the arbiter presently in control to hold the system bus, it cannot force another arbiter to surrender the bus any earlier than it normally would.

The LLOCK signal from the SAB 82289 must be connected to a tri-state buffer in order to drive the Multibus LOCK signal. This tri-state buffer should be enabled by the AEN signal from the arbiter going active.

#### SAB 82289 Reset and Initialization

The SAB 82289 bus arbiter provides the RESET and INIT pins for initialization. RESET is a CLK synchronous signal from the SAB 82284 clock generator and INIT is an asynchronous signal on the multimaster system bus. By having RESET pin high or INIT pin low the BREQ, BUSY and AEN output pins will all become inactive. RESET will also deactivate the LLOCK signal. Unlike RESET, INIT will not clear any pending bus request, the bus request would be asserted after the INIT signal goes inactive.

Note that when the SAB 82289 is initialized by the RESET input it does not wait until the end of the current bus cycle to reset. Any bus cycle in process when RESET goes active will be aborted by the arbiter. Although the INIT signal will also interrupt an active bus cycle, the arbiter can request the Multibus and complete the bus cycle when INIT goes inactive.

As mentioned in the pin description and figure 11 the functions of the \$\overline{50}/HOLD pin and the release mode (ALWAYS/CBOLCK pin) are programmed at the falling edge of RESET.

# Absolute Maximum Ratings 1)

#### **DC Characteristics**

TA = 0 to 70°C, VCC = 5V  $\pm 5\%$

|        | _                                                    | Limi | t values  | Unit                     | Test condition                         |  |

|--------|------------------------------------------------------|------|-----------|--------------------------|----------------------------------------|--|

| Symbol | Parameter                                            | min. | max.      | ————                     | Test condition                         |  |

| VIL    | Input low Voltage                                    | -0.5 | 0.8       | V                        |                                        |  |

| VIH    | Input High Voltage                                   | 2.0  | VCC+0.5   | ٧                        |                                        |  |

| VILC   | CLK Input Low Voltage                                | -0.5 | 0.6       | <b>&gt;</b> _            |                                        |  |

| VIHC   | CLK Input High Voltage                               | 3.8  | VCC+1.0   | ٧                        | _                                      |  |

| VOL    | Output Low Voltage: BUSY, CBRQ BPRO, BREQ, AEN LLOCK | _    | 0.45      | V                        | IOL = 32mA<br>IOL = 16 mA<br>IOL = 5mA |  |

| VOH    | Output High Voltage                                  | 2.4  | _         | v                        | IOH = 400 μA                           |  |

| ILI    | Input Leakage Current                                | -    | ±10<br>±1 | μ <b>A</b><br>m <b>A</b> | 0.45 V ≤VIN ≤VCC<br>0 V ≤VIN <0.45 V   |  |

| ILO    | Output Leakage Current                               | _    | ±10       | μΑ                       | 0.45 V ≤VOUT ≤VCC                      |  |

| ICC    | Power Supply Current                                 |      | 120       | mA                       |                                        |  |

| CCLK   | CLK, BCLK Input Capacitance                          | -    | 12        | рF                       | fC = 1MHz                              |  |

| CIN    | Input Capacitance                                    | _    | 10        | pF                       | fC = 1 MHz                             |  |

| CIO    | Input/Output Capacitance                             |      | 20        | pF                       | fC = 1 MHz                             |  |

<sup>1)</sup> Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **AC Characteristics SAB 82289**

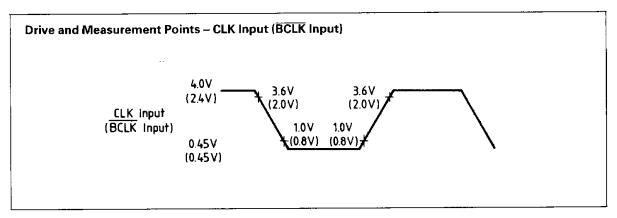

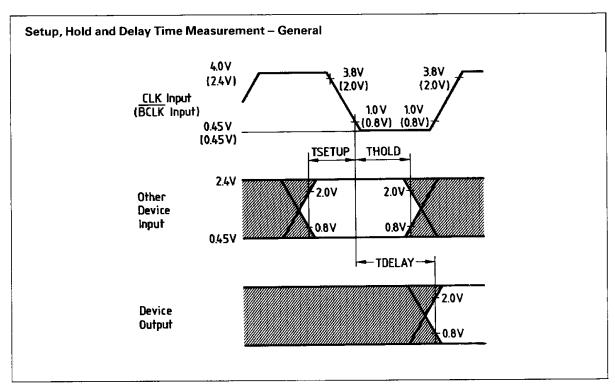

TA = 0 to  $70^{\circ}$ C, VCC = 5V  $\pm 5\%$ AC timings are referenced to 0.8 and 2.0 V points of signals as illustrated in data sheet waveforms, unless otherwise noted.

| Symbol | Parameter                                                         |                   | values *<br>MHz | Unit | Test condition | Shown<br>in       |

|--------|-------------------------------------------------------------------|-------------------|-----------------|------|----------------|-------------------|

|        |                                                                   | min.              | max.            |      |                | Figure            |

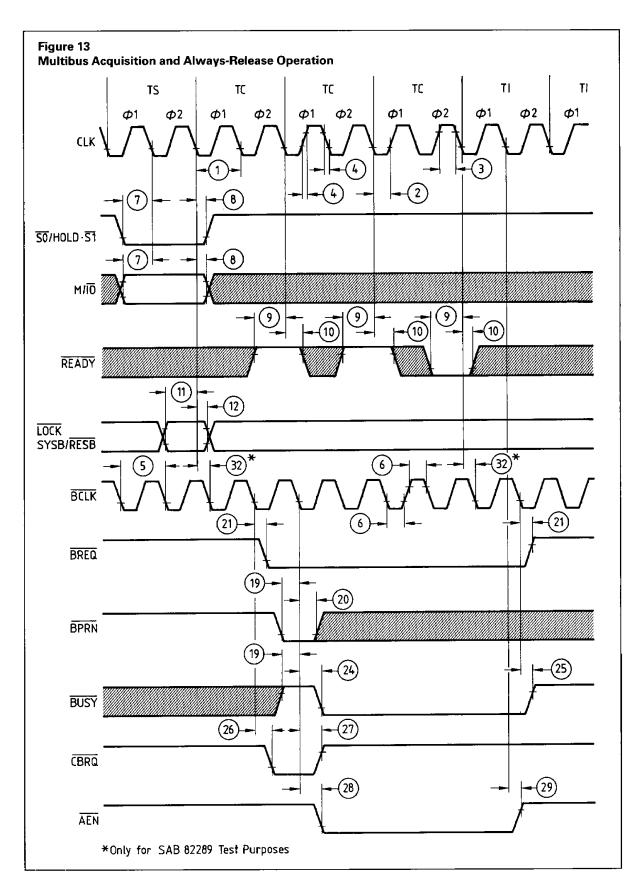

| 1      | CLK Cycle Period                                                  | 62                | t5+50           | ns   | _              | 13                |

| 2      | CLK Low Time                                                      | 15                | 230             | ns   | at 1.0 V       | 13                |

| 3      | CLK High Time                                                     | 20                | 235             | ns   | at 3.6V        | 13                |

| 4      | CLK Rise/Fall Time                                                | _                 | 10              | ns   | 1.0 to 3.6V    | 13                |

| 5      | BCLK Cycle Time                                                   | 100               | œ               | ns   | _              | 13                |

| 6      | BCLK High/Low Time                                                | 30                | _               | ns   | _              | 13                |

| 7      | SO/HOLD, \$1, M/IO Setup                                          | 22                | _               | ns   | _              | 13, 22            |

| 8      | SO/HOLD, \$1, M/10 Hold                                           | 1                 | _               | ns   | -              | 13, 22            |

| 9      | READY Setup                                                       | 38                | _               | ns   | _              | 13                |

| 10     | READY Hold Time                                                   | 25                | _               | ns   | _              | 13                |

| 11     | LOCK, SYSB/RESB Setup Time                                        | 20                | _               | ns   | _              | 13, 18            |

| 12     | LOCK, SYSB/RESB Hold Time                                         | 1                 | _               | ns   | -              | 13, 18            |

| 13     | RESET Setup Time                                                  | 20                | _               | ns   |                | 19                |

| 14     | RESET Hold Time                                                   | 1                 | _               | ns   | _              | 19                |

| 15     | RESET Active Pulse Width                                          | 16                | _               | CLKs | _              | 19                |

| 16     | INIT Setup Time                                                   | 45                | -               | ns   | 9)             | 20                |

| 17     | INIT Hold Time                                                    | 1                 | _               | ns   | 9)             | 20                |

| 18     | INIT Active Pulse Width                                           | 3 (t1)<br>+3(t14) | _               | ns   | _              | 20                |

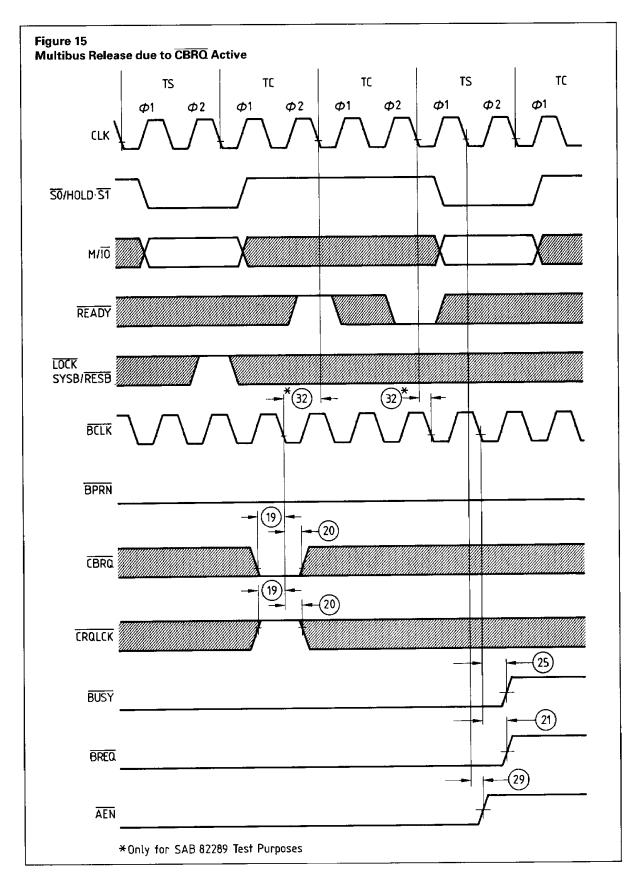

| 19     | BUSY, BPRN, CBRQ,<br>CBQLCK/ALWAYS Setup<br>to BCLK (or to RESET) | 20                | _               | ns   | _              | 13, 15,<br>21, 22 |

| 20     | BUSY, BPRN, CBRQ,<br>CBQLCK/ALWAYS Hold<br>to BCLK (or to RESET)  | 1                 | _               | ns   | _              | 13, 15,<br>21, 22 |

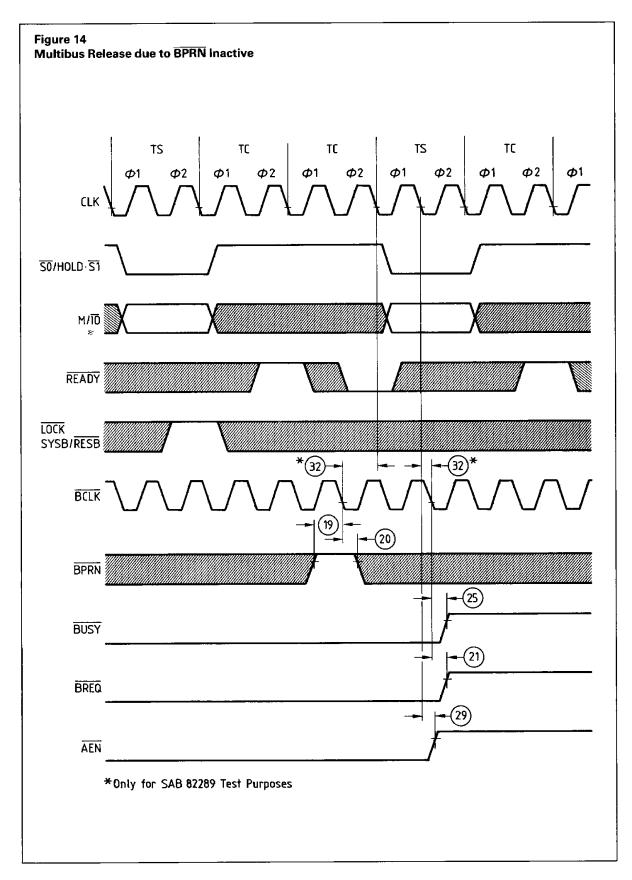

| 21     | BCLK to BREQ Delay                                                |                   | 30              | ns   | 1)             | 13,14,22          |

| 22     | BCLK to BPRO Delay                                                | _                 | 35              | ns   | 2)             | 17                |

| 23     | BPRN to BPRO Delay                                                | _                 | 25              | ns   | 2)             | 17                |

| 24     | BCLK to BUSY Active Delay                                         | 1                 | 60              | ns   | 3)             | 13, 22            |

For notes see next page.

## AC Characteristics SAB 82289 (continued)

| Symbol | Parameter                 | Limit values *<br>8 MHz |      | Unit | Test condition | Shown<br>in |

|--------|---------------------------|-------------------------|------|------|----------------|-------------|

|        |                           | min.                    | max. |      |                | Figure      |

| 25     | BCLK to BUSY Float Delay  | _                       | 35   | ns   | 4)             | 13, 14      |

| 26     | BCLK to CBRQ Active Delay | _                       | 55   | ns   | 5)             | 13, 22      |

| 27     | BCLK to CBRQ Float Delay  | _                       | 35   | ns   | 4)             | 13,20,22    |

| 28     | BCLK to AEN Active Delay  | 1                       | 25   | ns   | 6)             | 13          |

| 29     | CLK to AEN Inactive Delay | 3                       | 25   | ns   | 6)             | 13, 14      |

| 30     | CLK to LLOCK Delay        | _                       | 20   | ns   | 7)             | 18          |

| 31     | RESET to LLOCK Delay      |                         | 35   | ns   | 7)             | 19          |

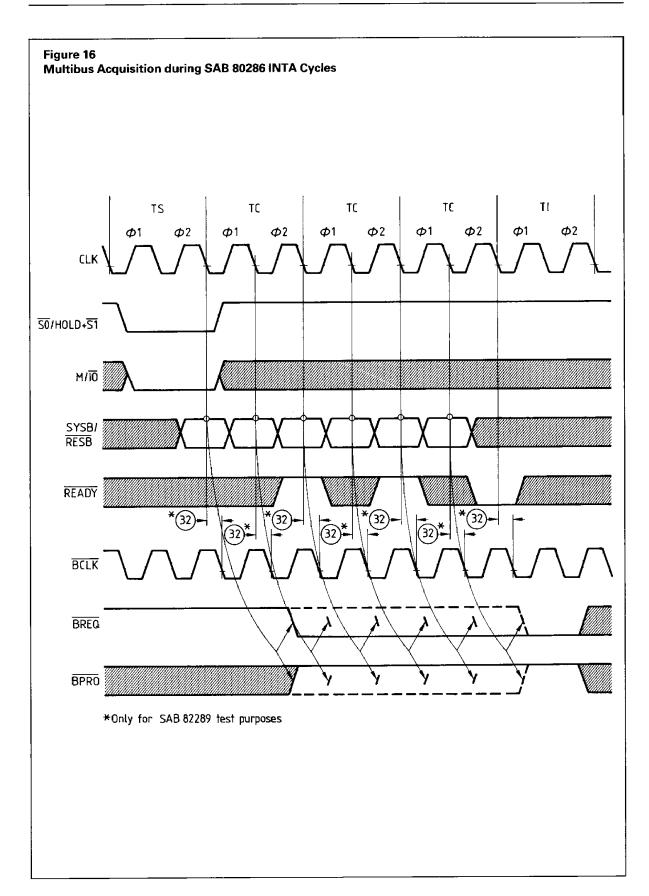

| 32     | CLK to BCLK Setup Time    | 38                      | _    | ns   | 8)             | 13,16, 20   |

| 33     | BCLK to AEN Output Delay  | 1                       | 30   | ns   | 6)             | 22          |

<sup>\*)</sup> Preliminary

- 1)  $\overline{BREQ}$  load CL = 60 pF

- 2) BPRO load CL = 60 pF

- 3)  $\overline{BUSY}$  load CL = 300 pF

- 4) Float condition occurs when output current is less than ILO in magnitude

- 5)  $\overline{\text{CBRQ}}$  load CL = 300 pF

- 6)  $\overline{AEN}$  load CL = 150 pF

- 7) LLOCK load CL = 60 pF

- 8) In actual use, CLK and BCLK are usually asynchronous to each other. However, for component testing purposes this specification is required to assure signal recognition at specific CLK and BCLK edges.

- 9) INIT is asynchronous to CLK and to BCLK. However, for component testing purposes, this specification is required to assure signal recognition at specific CLK and BCLK edges.

## **AC Characteristics SAB 82289-6**

TA = 0 to 70°C, VCC = 5V  $\pm 5\%$

AC timings are referenced to 0.8 and 2.0 V points of signals as illustrated in data sheet waveforms, unless otherwise noted.

| Symbol | Parameter                                                         |                   | Limit values *<br>6 MHz |      | Test condition | Shown<br>in       |

|--------|-------------------------------------------------------------------|-------------------|-------------------------|------|----------------|-------------------|

|        |                                                                   | min.              | max.                    |      |                | Figure            |

| 1      | CLK Cycle Period                                                  | 83                | t5+50                   | ns   | -              | 13                |

| 2      | CLK Low Time                                                      | 20                | 225                     | ns   | at 1.0 V       | 13                |

| 3      | CLK High Time                                                     | 25                | 230                     | ns   | at 3.6 V       | 13                |

| 4      | CLK Rise/Fall Time                                                | _                 | 10                      | ns   | 1.0 to 3.6 V   | 13                |

| 5      | BCLK Cycle Time                                                   | 100               | œ                       | ns   | -              | 13                |

| 6      | BCLK High/Low Time                                                | 30                | _                       | ns   | _              | 13                |

| 7      | S0/HOLD, S1, M/IO Setup                                           | 28                | _                       | ns   | _              | 13, 22            |

| 8      | \$0/HOLD, \$1, M/10 Hold                                          | 1                 | _                       | ns   | _              | 13, 22            |

| 9      | READY Setup                                                       | 50                | -                       | ns   | _              | 13                |

| 10     | READY Hold Time                                                   | 35                | _                       | ns   | _              | 13                |

| 11     | LOCK, SYSB/RESB Setup Time                                        | 28                | _                       | ns   | _              | 13, 18            |

| 12     | LOCK, SYSB/RESB Hold Time                                         | 1                 | _                       | ns   | _              | 13, 18            |

| 13     | RESET Setup Time                                                  | 28                | _                       | ns   | -              | 19                |

| 14     | RESET Hold Time                                                   | 1                 | _                       | ns   | _              | 19                |

| 15     | RESET Active Pulse Width                                          | 16                | _                       | CLKs | _              | 19                |

| 16     | INIT Setup Time                                                   | 45                | _                       | ns   | 9)             | 20                |

| 17     | INIT Hold Time                                                    | 1                 | _                       | ns   | 9)             | 20                |

| 18     | INIT Active Pulse Width                                           | 3 (t1)<br>+3(t14) | _                       | ns   | _              | 20                |

| 19     | BUSY, BPRN, CBRQ,<br>CBQLCK/ALWAYS Setup<br>to BCLK (or to RESET) | 20                | _                       | ns   | -              | 13, 15,<br>21, 22 |

| 20     | BUSY, BPRN CBRO,<br>CBQLCK/ALWAYS Hold<br>to BCLK (or to RESET)   | 1                 | _                       | ns   | _              | 13, 15,<br>21, 22 |

| 21     | BCLK to BREQ Delay                                                | _                 | 30                      | ns   | 1}             | 13,14,22          |

| 22     | BCLK to BPRO Delay                                                | -                 | 35                      | ns   | 2)             | 17                |

| 23     | BPRN to BPRO Delay                                                | _                 | 25                      | ns   | 2)             | 17                |

| 24     | BCLK to BUSY Active Delay                                         | 1                 | 60                      | ns   | 3)             | 13, 22            |

For notes see next page.

# AC Characteristics SAB 82289-6 (continued)

| Symbol | ymbol Parameter           | Limit values *<br>6 MHz |      | Unit | Test condition | Shown in  |

|--------|---------------------------|-------------------------|------|------|----------------|-----------|

|        |                           | min.                    | max. |      |                | Figure    |

| 25     | BCLK to BUSY Float Delay  | -                       | 35   | ns   | 4)             | 13, 14    |

| 26     | BCLK to CBRQ Active Delay | _                       | 55   | ns   | 5)             | 13, 22    |

| 27     | BCLK to CBRQ Float Delay  | _                       | 35   | ns   | 4)             | 13,20,22  |

| 28     | BCLK to AEN Active Delay  | 1                       | 25   | ns   | 6)             | 13        |

| 29     | CLK to AEN Inactive Delay | 3                       | 25   | ns   | 6)             | 13, 14    |

| 30     | CLK to LLOCK Delay        | -                       | 20   | ns   | 7)             | 18        |

| 31     | RESET to LLOCK Delay      | -                       | 35   | ns   | 7)             | 19        |

| 32     | CLK to BCLK Setup Time    | 38                      | -    | ns   | 8)             | 13,16, 20 |

| 33     | BCLK to AEN Output Delay  | 1                       | 30   | ns   | 6)             | 22        |

<sup>\*)</sup> Preliminary

- 1)  $\overline{BREQ}$  load CL = 60 pF

- 2)  $\overline{BPRO}$  load CL = 60 pF

- 3) BUSY load CL = 300 pF

- 4) Float condition occurs when output current is less than ILO in magnitude

- 5)  $\overline{\text{CBRQ}}$  load CL = 300 pF

- 6)  $\overline{AEN}$  load CL = 150 pF

- 7)  $\overline{\text{LLOCK}}$  load CL = 60 pF

- 8) In actual use, CLK and BCLK are usually asynchronous to each other. However, for component testing purposes this specification is required to assure signal recognition at specific CLK and BCLK edges.

- 9) INIT is asynchronous to CLK and to BCLK. However, for component testing purposes, this specification is required to assure signal recognition at specific CLK and BCLK edges.

## **AC Testing Waveforms**

#### **Waveforms**

The waveforms (figures 13 to 21) show the timing relationships of the inputs and the outputs and do not show all possible transitions of all signals in all modes. Instead, all signal timing relationships are shown via the general cases. Special cases are shown when needed.

To find the timing specification for a signal transition in a particular mode, first look for a special case in the waveforms. If no special case applies, then use a timing specification for the same or related function in another mode.

The SAB 82289 bus arbiter serves as an interface between the SAB 80286 subsystem which operates synchronously to the CLK signal and Multibus which operates synchronously to  $\overline{BCLK}$  signal. CLK and  $\overline{BCLK}$  generally operate asynchronously to each other and at different frequencies. Thus, the exact clock period in which an input synchronous to one clock will cause a response synchronous to the other clock depends on the relative phase and frequency of CLK and  $\overline{BCLK}$  at the time the input is sensed.

One strict relation between CLK and BCLK must be maintained for proper Multibus arbitration. If the CLK period is too long relative to BCLK period (t1 greater than t5 +50 ns), another arbiter could gain control of the system bus before this arbiter has released AEN synchronously to its CLK. This situation arises since the release of AEN is synchronous to the next falling CLK edge after the processor cycle ends but the release of BREQ and BUSY is synchronous to the next falling BCLK edge after the processor cycle ends. In practice, any CLK frequency greater than 6.66 MHz (i.e. SAB 80286 processor speeds greater than 3.33 MHz) will avoid conflict with a 10 MHz BCLK. Therefore all SAB 80286 speed selections are Multibus compatible.

# **Ordering Information**

| Туре          | Ordering code | Description                  |

|---------------|---------------|------------------------------|

| SAB 82289-P   | Q67020-Y77    | Bus Arbiter 16 MHz (plastic) |

| SAB 82289-6-P | Q67120-Y111   | Bus Arbiter 12 MHz (plastic) |