PRELIMINARY

# 1/4 DUTY LCD DRIVER

## GENERAL DESCRIPTION

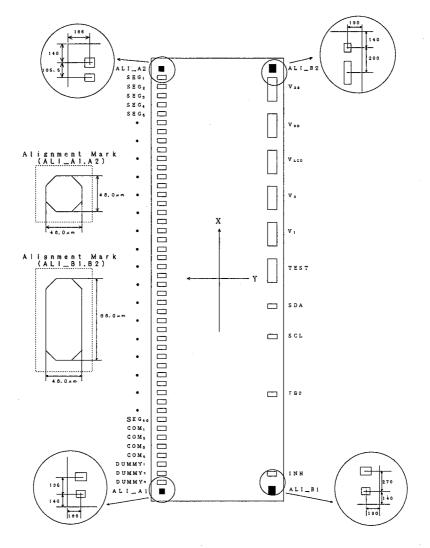

PACKAGE OUTLINE

The NJU6438 is a 1/4 duty LCD driver for segment type LCD panel.

The LCD driver consists of 4-common and 40-segment drives up to 160 segments.

The rectangle outline is useful the COG applications.

NJU6438CH

### FEATURES

• 40 Segment Drivers

• Duty and Bias Ratio : 1/4Duty, 1/3Bias(up to 160 segments)

- I<sup>2</sup>C BUS Interface<sup>\*</sup> (Shift Clock 100kHz max.)

- Oscillation Circuit On-chip

- Display Off Function (INH Terminal or Command Input Data)

- Operating Voltage --- 2.4~3.6V

- LCD Driving Voltage 6.0V Max.

- Package Outline ---- Chip / Bumped Chip

- C-MOS Technology

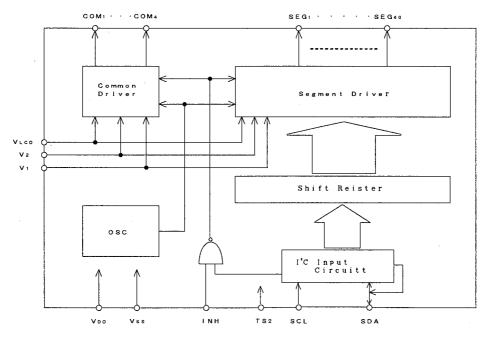

# BLOCK DIAGRAM

\*1°C BUS Interface is trademark of Philips Corporation.

New Japan Radio Co.,Ltd.

# PAD LOCATION

| Chip size      | : | 5.12mm x 1.56mm                                                                       |             |                                 |

|----------------|---|---------------------------------------------------------------------------------------|-------------|---------------------------------|

| Chip center    | : | X=0μm,Y=0μm                                                                           | <b>I</b> :4 | th Mark is the Alignment Mark.  |

| Chip thickness | : | $400 \pm 30 \mu$ m                                                                    |             |                                 |

| Pad size       | : | 50μm x 100μm                                                                          | 1           | he Alignment Mark is useful the |

|                |   | $V_1$ , $V_2$ , $V_{LCD}$ , $V_{DD}$ , $V_{SS}$ Terminal is $250 \mu$ m x $100 \mu$ m | 0           | XXG Assembly.                   |

| Bump height    | : | 25μmTYP.                                                                              |             |                                 |

| Bump material  | : | Au                                                                                    |             |                                 |

# COORDINATES

JRC

Chip Size 5.12x1.56mm (Chip Center X=0  $\mu$ m, Y=0  $\mu$ m)

| No | Terminal           | X=(μm)  | Y=(μm)   | No | Terminal           | X=(μm)   | Y=(μm)  |

|----|--------------------|---------|----------|----|--------------------|----------|---------|

| 1  | INH                | -2150.0 | - 590.0  | 32 | SEG <sub>22</sub>  | 214. 5   | 594. 0  |

| 2  | TS₂                | -1240.0 | - 590.0  | 33 | SEG <sub>2 3</sub> | 114.5    | 594. 0  |

| 3  | SCL                | - 494.0 | - 590.0  | 34 | SEG <sub>24</sub>  | 14.5     | 594. 0  |

| 4  | SDA                | - 178.0 | - 590.0  | 35 | SEG25              | - 85.5   | 594. 0  |

| 5  | TEST               | 206. 0  | - 590.0  | 36 | SEG <sub>28</sub>  | - 185.5  | 594. 0  |

| 6  | V1                 | 660. 0  | - 590, 0 | 37 | SEG <sub>27</sub>  | - 285.5  | 594. 0  |

| 7  | V <sub>2</sub>     | 1040. 0 | - 590.0  | 38 | SEG <sub>28</sub>  | - 385.5  | 594. 0  |

| 8  | VLCD               | 1430.0  | - 590.0  | 39 | SEG <sub>29</sub>  | - 485.5  | 594. 0  |

| 9  | VDD                | 1820. 0 | - 590.0  | 40 | SEG₃₀              | - 585.5  | 594. 0  |

| 10 | Vss                | 2220. 0 | - 590.0  | 41 | SEG <sub>31</sub>  | - 685.5  | 594. 0  |

| 11 | SEG 1              | 2314.5  | 594. 0   | 42 | SEG32              | - 785.5  | 594. 0  |

| 12 | SEG <sub>2</sub>   | 2214. 5 | 594.0    | 43 | SEG33              | - 885.5  | 594. 0  |

| 13 | SEG₃               | 2114.5  | 594. 0   | 44 | SEG34              | - 985.5  | 594. 0  |

| 14 | SEG₄               | 2014. 5 | 594.0    | 45 | SEG35              | -1085.5  | 594. 0  |

| 15 | SEG₅               | 1914. 5 | 594. 0   | 46 | SEG36              | -1185.5  | 594. 0  |

| 16 | SEG <sub>6</sub>   | 1814. 5 | 594.0    | 47 | SEG37              | -1285.5  | 594. 0  |

| 17 | SEG7               | 1714. 5 | 594.0    | 48 | SEG38              | -1385.5  | 594. 0  |

| 18 | SEG <sub>8</sub>   | 1614. 5 | 594.0    | 49 | SEG <sub>39</sub>  | -1485.5  | 594. 0  |

| 19 | SEG <sub>9</sub>   | 1514.5  | 594.0    | 50 | SEG₄₀              | -1585.5  | 594. 0  |

| 20 | SEG <sub>10</sub>  | 1414. 5 | 594.0    | 51 |                    | -1685.5  | 594. 0  |

| 21 | SEG <sub>11</sub>  | 1314. 5 | 594.0    | 52 | . COM2             | -1785.5  | 594. 0  |

| 22 | SEG12              | 1214. 5 | 594.0    | 53 | COM₃               | -1885. 5 | 594. 0  |

| 23 | SEG <sub>13</sub>  | 1114. 5 | 594.0    | 54 | COM4               | -1985. 5 | 594. 0  |

| 24 | SEG14              | 1014. 5 | 594.0    | 55 | DUMMY1 💥           | -2085. 5 | 594. 0  |

| 25 | SEG <sub>15</sub>  | 914.5   | 594.0    | 56 | DUMMY2 💥           | -2185. 5 | 594. 0  |

| 26 | SEG 1 6            | 814. 5  | 594.0    | 57 | DUMMY3 💥           | -2285. 5 | 594. 0  |

| 27 | SEG <sub>17</sub>  | 714. 5  | 594.0    |    | ALI_A1             | -2420.0  | 594. 0  |

| 28 | SEG <sub>18</sub>  | 614. 5  | 594.0    |    | ALI_A2             | 2420. 0  | 594. 0  |

| 29 | SEG19              | 514.5   | 594.0    |    | AL1_B1             | -2420.0  | - 590.0 |

| 30 | SEG <sub>20</sub>  | 414.5   | 594.0    |    | ALI_B2             | 2420. 0  | - 590.0 |

| 31 | SEG <sub>2</sub> 1 | 314. 5  | 594.0    |    |                    |          | -       |

XDUMMY PAD

### TERMINAL DESCRIPTION

| NO.            | SYMBOL             | FUNCTION                                                                                                                                                                                                                                                                   |

|----------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | INH                | Display-Off Control Terminal :<br>When display goes to off, the display data in the shift-<br>register is retained.<br>"H" : Display-Off<br>"L" : Display-Off<br>X Display-off control changed by command input data.<br>In case of difference command, priority is "off". |

| 2              | TS₂                | Connect to the $V_{\text{DD}}$ or $V_{\text{SS}}.$                                                                                                                                                                                                                         |

| 3              | SCL                | Serial Data Transmission Clock Input Terminal :<br>LCD display data are input synchronized SCL clock signal<br>rise edge.                                                                                                                                                  |

| 4              | SDA                | Serial Data Input Terminal<br>Data input timing : SCL clock rise edge                                                                                                                                                                                                      |

| 5              | TEST               | Maker Testing Terminal (Normally Open)                                                                                                                                                                                                                                     |

| 6, 7           | V1, V2             | LCD Driver Voltage Adjust Terminal(Note:1-6)                                                                                                                                                                                                                               |

| 8              | VLCD               | Power Supply for LCD Driving                                                                                                                                                                                                                                               |

| 9              | VDD                | Power Supply (+3V)                                                                                                                                                                                                                                                         |

| 10             | Vss                | Power Supply (OV)                                                                                                                                                                                                                                                          |

| 11~50          | SEG1 ~ SEG40       | LCD Segment Output Terminals                                                                                                                                                                                                                                               |

| 51 <b>~</b> 54 | $COM_1 \sim COM_4$ | LCD Common Output Terminals                                                                                                                                                                                                                                                |

### FUNCTIONAL DESCRIPTION

# (1) Operation of each block

(1-1)Oscillation Circuit

This circuits supply the basical clock signal to other circuits like as common driver and segment driver.

#### (1-2) Shift-Register

This register is to read display data for 160-bit. When the display "ON", this register data outputs into SEG terminals usually. In this time, when the data input, take care about the frequency of shift clock.

#### (1-3) Common Divider Circuit

This circuit divides the oscillating signal to generate the common timing.

### (1-4) Segment Divider Circuit

This circuit divides the oscillating signal to generate the segment timing.

### (1-5) I<sup>2</sup>C Input Circuit

This circuit change the  $l^2C$  format input data(SCL, SDA) to control signal of the circ -uit. This circuit generate the confirmation signal, decode of command (display on/off), CLK/data supply with shift register.

New Japan Radio Co.,Ltd.

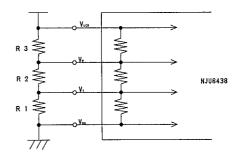

(1-6) The LCD Driver Voltage Adjust circuit The internal Bleeder Resistance sets 1/3 bias, and LCD Driver ability can be increased by connecting external resistance.

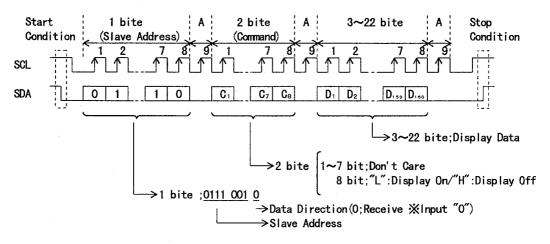

(2) Display Data input timing, correspond to segment and common terminal

NJU6438 is controlled by  $1^{2}$ C bus using the SCL and the SDA terminals. Attention is shown below. ONJU6438 is a receive-only slave.

©Slave address data is "0111 0010". (LSB data is direction. 0;receive) ©NJU6438 also doesn't correspond to the general call address. ※

XThe address is addressing all of installation connected by 1°C bus. (Address Data:0000 0000)

The data transfer is available, when this flow-chart is executed shown bellow.

(1-bite = 8-bit)

| Start condition | ]→ Slave address | > | Command | $\rightarrow$ | Display data | <b> </b> → | Stop condition |  |

|-----------------|------------------|---|---------|---------------|--------------|------------|----------------|--|

|-----------------|------------------|---|---------|---------------|--------------|------------|----------------|--|

When the data transferred exactly, NJU6438 output "L" level signal from SDA terminal as acknowledge signal each 8-bit.

#### [start condition]

A fall-edge of the SDA line while the SCL is "H" level is defined as a start condition.

#### [1st bite:slave address]

1st bite defines the slave address of NJU6438 and the data direction. The 8-bit data "0111 0010" is required as the 1st bite, 1st---7th bits mean the slave address and 8th bit means the direction. NJU6438 is a receive-only slave IC, so if "1" is input to the 8th bit, the acknowledge bit doesn't output. NJU6438 also doesn't correspond to the general call address.

### [2nd bite:command]

2nd bite defines a command. In case of "0" into the 8th bit, all of the segment terminals output non-display waves regardless of the contents of the sift-register. In case of "1", they output normal display waves. The common waves don't change in both cases. However while the INH terminal is "H" level, all segment terminals output non-display

waves in spite of "0" into the 8th bit. In this case the contents of the sift-register aren't reset but the last data remain in them.

#### [3-22bite:display data]

3rd — 22nd byte define the display data The acknowledge bit outputs after the each byte through the SDA terminal. The display data are required 160-bit(20-bite).

#### [stop condition]

A rise-edge of the SDA line while the SCL is "H" level is defined as a stop condition. The transmission is stopped by the rise-edge into the SDA terminal when the SCL terminal is "H" level. The writing data hasn't been accepted since stop condition.

New Japan Radio Co., Ltd.

• Display Data Correspond to Segment Status (I<sup>2</sup>C bus mode)

Whole 160bits data transfer to the shift register. When the input data in less than 160 bits, parts which bit data is inputed corresponded to display, and segment which correspond to the rest part in "off".

In care of over then 160bits, front 160bits from Stop condition is valid.

New Japan Radio Co.,Ltd.

Input data correspond to Segment Status The "H" input data correspond to segment "ON" and "L" correspond to "OFF".

| Data (D1…D160) | Segment Status |  |  |  |

|----------------|----------------|--|--|--|

| <i>"</i> H"    | ON             |  |  |  |

| ″L″            | 0FF            |  |  |  |

• Display Data Correspond to Segment and Common Terminals

| Segment           | Data                         | COM1 | COM2 | COM₃ | COM <sub>4</sub> |

|-------------------|------------------------------|------|------|------|------------------|

| SEG1              | D1<br>D2<br>D3<br>D4         | 0    | 0    | 0    | 0                |

| SEG <sub>2</sub>  | D₅<br>D6<br>D7<br>D8         | 0    | 0    | 0    | 0                |

| :                 | :                            | :    |      | :    |                  |

| SEG <sub>39</sub> | D153<br>D154<br>D155<br>D156 | 0    | 0    | 0    | 0                |

| SEG40             | D157<br>D158<br>D159<br>D160 | 0    | 0    | 0    | 0                |

■ ABSOLUTE MAXIMUM RATINGS

( Ta=25°C )

| PARAMETER             | SYMBOL | RATING                 | UNIT |

|-----------------------|--------|------------------------|------|

| Operating Voltage (1) | Vod    | -0.3 ~ +7.0            | v    |

| Operating Voltage (2) | VLCD   | -0.3 ~ +7.0            | v    |

| Operating Voltage (3) | V1, V2 | -0.3 ~ +7.0            | v    |

| Input Voitage         | VIN    | -0.3 ~ V <sub>DD</sub> | v    |

| Operating Temperature | Topr   | -20 ~ +75              | °C   |

| Storage Temperature   | T'stg  | -55 ~ +125             | °C   |

- Note 1) If the LSI are used on condition above the absolute maximum ratings, the LSI may be destroyed. Using the LSI within electrical characteristics is strongly recommended for normal operation. Use beyond the electric characteristics conditions will cause malfunction and poor reliability.

- Note 2) All voltage values are specified as  $V_{ss} = 0 V$

- Note 3) The relation:  $V_{LCD} \ge V_2 \ge V_1 \ge V_{ss}$  must be maintained.

- Note 4) Decoupling capacitor should be connected between  $V_{\text{DD}}$  and  $V_{\text{SS}}$  due to the stabilized operation.

# ELECTRICAL CHARACTERISTICS

• DC Characteristics

(Ta=25°C, VDD=3. 0V, VSS=0V, VLCD=6. 0V)

| PARAM                 | ETER           | SYMBOL          | CONDITIONS                                                                | MIN                         | TYP                 | MAX                         | UNIT | NOTE |

|-----------------------|----------------|-----------------|---------------------------------------------------------------------------|-----------------------------|---------------------|-----------------------------|------|------|

| Operating             | Recommend      | VDD             | Vod Terminal                                                              | 2.4                         | 3.0                 | 3.6                         | V    |      |

| Voltage<br>(1)        | Available      | Vdd             | Vod Terminal                                                              | 2.4                         | 3.0                 | 5.5                         | V    |      |

| Operating V           | oltage (2)     | VLCD            | VLCD Terminal                                                             | 2.0                         |                     | 6.0                         | V    |      |

| Operating V           | oltage (3)     | V2              | V2 Terminal                                                               | <b>V</b> 1                  | 2/3VLCD             | VLCD                        | V    |      |

| Operating V           | oltage (4)     | V1              | V1 Terminal                                                               | 0.7                         | 1/3V <sub>LCD</sub> | V2                          | ۷    |      |

| "H" Input V           | oltage         | $V_{1H}$        | SCL, SDA, INH Terminals                                                   | 0. 7V <sub>DD</sub>         |                     | VDD                         | V    |      |

| "L" Input V           | oltage         | VIL             | SCL,SDA,INH Terminals                                                     | Vss                         |                     | 0. 3V <sub>DD</sub>         | V    |      |

| "H" Input C           | urrent         | Гін             | SCL, SDA, INH Terminals $V_{IN} = V_{DD}$                                 |                             |                     | 5                           | μA   |      |

| "L" Input C           | urrent         | Πις             | SCL, SDA, INH Terminals<br>VIN=Vss                                        |                             |                     | 5                           | μA   |      |

| "H" Output            | Voltage(1)     | <b>V</b> он (1) | SEG <sub>1</sub> ~SEG <sub>40</sub> Term , $I_0 = -1 \mu A$               | VLCD-0.6                    |                     |                             | V    | 5    |

| "L" Output            | Voltage(1)     | Vol (1)         | SEG <sub>1</sub> ~SEG <sub>40</sub> Term., $I_0 = 1 \mu A$                |                             |                     | Vss+0.6                     | V    | 5    |

| Middle Leve<br>Voltag | l<br>e 1/3 (1) | <b>V</b> мs1/3  | SEG <sub>1</sub> ~SEG <sub>40</sub> Term, $I_0=\pm 1 \mu A$               | 1/3V <sub>LCD</sub><br>-0.6 | 1/3V <sub>LCD</sub> | 1/3V∟c⊅<br>+0.6             | V    | 5    |

| Middle Leve<br>Voltag | l<br>e 2/3 (1) | Vms2/3          | SEG <sub>1</sub> ~SEG <sub>40</sub> Term , $I_0=\pm 1 \mu A$              | 2/3V <sub>LCD</sub><br>-0.6 | 2/3VLCD             | 2/3V <sub>LCD</sub><br>+0.6 | V    | 5    |

| "H" Output            | Voltage(2)     | <b>V</b> он (2) | $COM_1 \sim COM_4$ Term., $I_0 = -30 \mu \text{ A}$                       | VLCD-0.6                    |                     |                             | V    | 6    |

| "L" Output            | Voltage(2)     | Vol (2)         | $COM_1 \sim COM_4$ Term., $I_0 = 30 \mu A$                                |                             |                     | Vss+0.6                     | v    | 6    |

| Middle Leve<br>Voltag | l<br>e 1/3 (2) | <b>V</b> мс1/3  | $COM_1 \sim COM_4$ Term , $I_0 = \pm 1 \mu A$                             | 1/3V <sub>LCD</sub><br>-0.6 | 1/ <b>3V</b> lcd    | 1/3V <sub>LCD</sub><br>+0.6 | v    | 6    |

| Middle Leve<br>Voltag | l<br>e 2/3 (2) | Vмс₂∕з          | $COM_1 \sim COM_4$ Term , $I_0 = \pm 1 \mu A$                             | 2∕3V⊾с⊅<br>~0.6             | 2/3VLCD             | 2/3V <sub>LCD</sub><br>+0.6 | v    | 6    |

| "L" Output            | Voltage(3)     | Vol (3)         | SDA Io= 3mA                                                               |                             |                     | Vss+0.4                     | v    | 6    |

| Operating C           | urrent (1)     | IDD             | VDD Terminal VDD=3.0V<br>VLCD OPEN                                        |                             | 15                  | 25                          | μA   | 7    |

| Operating C           | urrent (2)     | LCD             | V <sub>LCD</sub> Terminal V <sub>DD</sub> =3.0V<br>V <sub>LCD</sub> =6.0V |                             | 18                  | 28                          | μA   | 8    |

| Hysteresis            | Voltage        | VH              | SCL_Terminal, V₀₀=3.0V                                                    | 0.3                         |                     |                             | V    |      |

Note 5) Segment terminals except measurement terminal are open.

Note 6) Common terminals except measurement terminal are open.

Note 7) SCL, SDA terminals are connected  $V_{ss.}/INH$  terminal is connected  $V_{DD.}/TEST$  terminal is open.

Note 8) SCL, SDA, INH terminals are measurement terminal are connected  $V_{ss.}$  /TEST terminal is open.

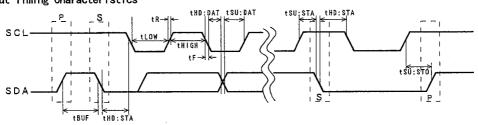

· AC Characteristics

$(Ta=25^{\circ}C, V_{DD}=3. OV, V_{SS}=0V, V_{LCD}=6. OV)$

| PARAMETER                | SYMBOL               | CONDITIONS | MIN  | TYP | MAX | UNIT |

|--------------------------|----------------------|------------|------|-----|-----|------|

| SCL Frequency            | tour                 | SCL        | 0    |     | 100 | KHz  |

| Bus Open Time            | tBUF                 | SCL, SDA   | 4.7  | -   |     | μs   |

| Start Condi. Hold Time   | t <sub>HD</sub> :STA | SCL, SDA   | 4.0  |     | _   | μs   |

| "L" SCL Pulse Width      | t∟ow                 | SCL        | 4. 7 | _   | 155 | μs   |

| "H" SCL Pulse Width      | <b>t</b> нтан        | SCL        | 4.0  | _   | 415 | μs   |

| Start Condi. Set-up Time | tsu:STA              | SCL, SDA   | 4. 7 | _   | 155 | μs   |

| SDA Data Hold Time       | thd:DAT              | SCL, SDA   | 0    | _   |     | μs   |

| SDA Data Set-up Time     | tsu:DAT              | SDA, SDA   | 250  | _   | -   | ns   |

| SCL Rise Time            | tR                   | SCL, SDA   |      |     | 1   | μs   |

| SCL Fall Time            | tr                   | SCL, SDA   |      |     | 300 | ns   |

| Stop Condi. Set-up Time  | tsu:STO              | SCL, SDA   | 4. 7 | _   | _   | μs   |

Input Timing Characteristics

Frame Frequency

| PARAMETER       | SYMBOL | CONDITIONS      | MIN | TYP | MAX | UNIT |

|-----------------|--------|-----------------|-----|-----|-----|------|

| Frame Frequency | fo     | COM1~4, SEG1~32 | 45  | 70  | 140 | KHz  |

NJU6438

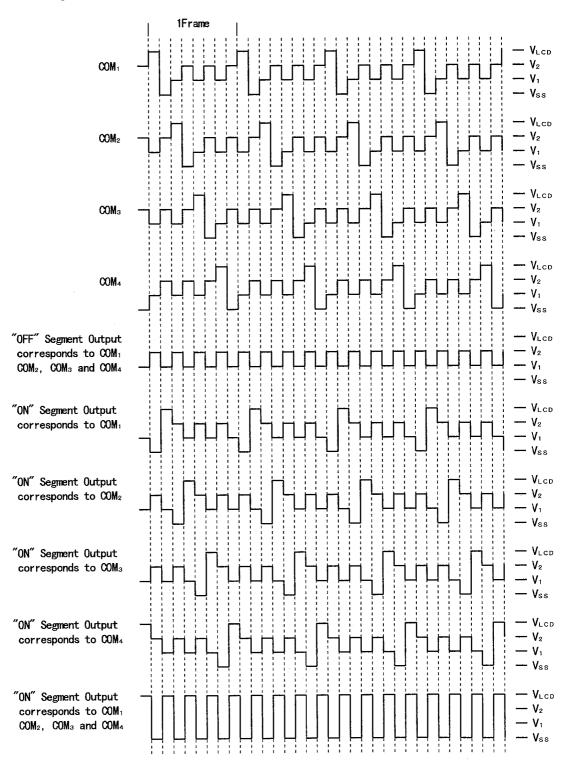

■ LCD Driving Waveform(1/4DUTY • 1/3BIAS)

New Japan Radio Co., Ltd.

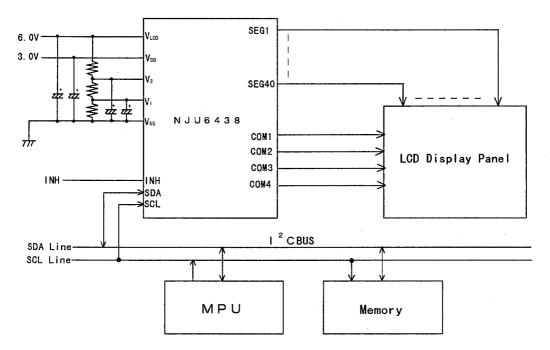

# APPLICATION CIRCUIT 1

• 1/4 DUTY LCD Driver • 1<sup>2</sup>C Bus Interface

(Note) The internal display data is undefined when  $V_{\text{DD}}$  is just turned on.

To avoid the meaningless display, please keep the INH terminal at "H" until proper display data has been transferred.

In order to set the initial condition, 160-bit blank data or the first 160-bit data to be displayed should be transferred.

-New Japan Radio Co., Ltd.

MEMO

[CAUTION] The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.