## **LG1605DXB Limiting Amplifier**

#### **Features**

- 28 dB gain, 34 dB differential

- Large dynamic range: >60 dB

- Wideband response: 8 kHz to 3 GHz

- Extremely low ±4 ps delay skew across input range

- Complementary 50 Ω I/Os

- Surface-mount package

- Standard ECL supply (400 mW)

### **Applications**

Data/clock main amplifier SONET/SDH OC-48/ STM-16 transmission systems, DWDM systems

- Digital video transmission

- Interface between 1319 receiver and LG1600 clock and data regenerator

- High-speed comparator

#### **Functional Description**

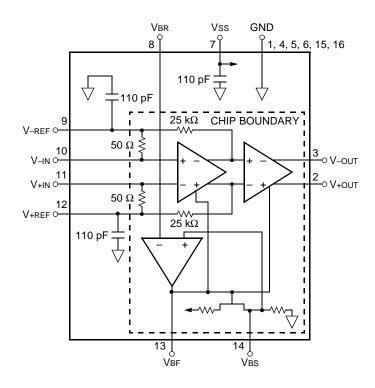

The LG1605DXB is a GaAs wideband limiting amplifier with differential inputs and outputs that provides 28 dB of gain (34 dB differential) and 3 GHz of bandwidth in a 50  $\Omega$  environment (Figure 1 shows the block diagram). At low input levels, below 10 mV to 20 mV, the circuit behaves as a linear amplifier. At higher levels, the device goes smoothly into limiting. The device matches the performance of an AGC amplifier but shows none of the AGC bouncing and attack characteristics.

Figure 1. LG1605DXB Block Diagram

### Functional Description (continued)

The amplifier has a virtually constant output delay for input signal levels, varying across three decades. As a result, the device has very low amplitude-to-phase conversion, which makes it ultimately suitable for applications in highly sensitive fiber-optic systems. Although the amplifier is most sensitive when the input is ac coupled (see Figure 3), a low offset (<25 mV) and a large common-mode input range of 2 V make it useful in applications that require a high-speed comparator as well.

A unique input coupling arrangement allows for a frequency response down into the low kHz range while using coupling capacitors that are small enough to maintain a good input return loss at high frequencies.

The outputs, when ac coupled, provide a good RF termination up to very high frequencies. The associated

ability to absorb reflections returning from the receiving end is essential for preventing intersymbol interference in fiber-optic systems.

The amplifier is a natural step-up interface between receivers, such as the Lucent Technologies Microeletronics Group Optoelectronics unit 1319 and regenerators like the Lucent Technologies Microelectronics Group LG1600. The referred wideband input noise (168  $\mu$ Vrms typical) allows for a <1e–9 bit error rate (BER) for inputs down to 2 mVp-p (S/N ratio of 21.5 dB).

In SAW based clock recovery systems, with clock frequencies as high as 2.5 GHz, the device can provide a clock-limiting function in systems.

The LG1605DXB is available in a hermetically sealed, 16-lead, glass-metal surface-mount package and uses a standard ECL supply.

#### Pin Information

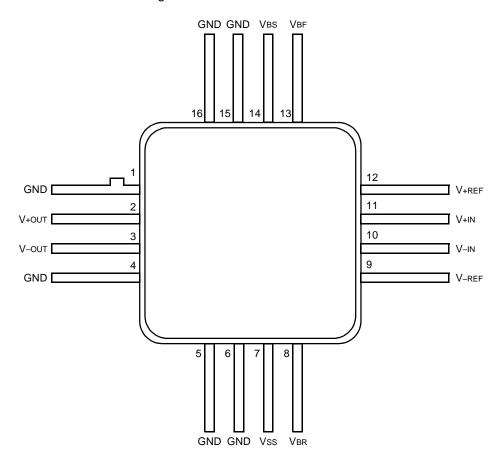

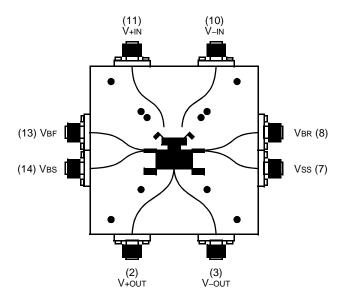

The pinout for the LG1605DXB is shown in Figure 2.

12-3223(F)

Figure 2. Pin Diagram

# Pin Information (continued)

The pin descriptions for the LG1605DXB are given in Table 1.

**Table 1. Pin Descriptions**

| Pin                                       | Symbol | Name/Description                                                                                                                                                                     |  |  |  |

|-------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 2                                         | V+out  | Positive Data Output.                                                                                                                                                                |  |  |  |

| 3                                         | V-out  | Negative Data Output.                                                                                                                                                                |  |  |  |

| 7                                         | Vss    | dc Supply Voltage.                                                                                                                                                                   |  |  |  |

| 8                                         | VBR    | Bias Reference Voltage. Connect to nominal –1.5 V stable voltage reference, bypassed to GND with a capacitor ≥0.047 µF.                                                              |  |  |  |

| 9                                         | V-REF  | Data Negative Reference. Internally bypassed with 110 pF. Broadband operation requires up-close external bypassing with a capacitor ≥0.047 μl matching the input coupling capacitor. |  |  |  |

| 10                                        | V-IN   | <b>Negative Data Input.</b> Requires ac-coupling capacitor and 50 $\Omega$ source or termination.                                                                                    |  |  |  |

| 11                                        | V+IN   | Positive Data Input.                                                                                                                                                                 |  |  |  |

| 12                                        | V+REF  | Data Positive Reference. See pin 9 above.                                                                                                                                            |  |  |  |

| 13                                        | VBF    | Bias Force Voltage. Obsolete function, do not connect.                                                                                                                               |  |  |  |

| 14                                        | VBS    | <b>Bias Sense Voltage.</b> Internal test point, tracking VBR. Normally not connected.                                                                                                |  |  |  |

| 1, 4, 5, 6,<br>15, 16,<br>Package<br>Back | GND    | <b>Ground.</b> For optimum performance, package back should contact board ground plane. (See the Mounting and Connections section.)                                                  |  |  |  |

#### **Absolute Maximum Ratings**

Stresses in excess of the absolute maximum ratings can cause permanent or latent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

**Table 2. Absolute Maximum Ratings**

| Parameter                        | Min        | Max | Unit |

|----------------------------------|------------|-----|------|

| Supply Voltage Range (Vss)       | <b>-</b> 7 | 0.5 | V    |

| Power Dissipation                | _          | 1   | W    |

| Voltage (all pins)               | Vss        | 0.5 | V    |

| V+REF - V+IN                     | _          | ±2  | V    |

| V-REF - V-IN                     | _          | ±2  | V    |

| Storage Temperature Range        | -40        | 125 | °C   |

| Operating Case Temperature Range | 0          | 100 | °C   |

### **Recommended Operating Conditions**

**Table 3. Recommended Operating Conditions**

| Parameter        | Symbol | Min          | Max  | Unit |

|------------------|--------|--------------|------|------|

| Case Temperature | tCASE  | 0            | 70   | °C   |

| Power Supply     | Vss    | <i>–</i> 5.7 | -4.7 | V    |

## **Handling Precautions**

Although protection circuitry has been designed into this device, proper precautions should be taken to avoid exposure to electrostatic discharge (ESD) during handling and mounting. Lucent employs a human-body model (HBM) and a charged-device model (CDM) for ESD-susceptibility testing and protection design evaluation. No industry-wide standard has been adopted for the CDM. However, a standard HBM (resistance = 1500  $\Omega$ , capacitance = 100 pF) is widely used and, therefore, can be used for comparison purposes. The HBM ESD threshold presented here was obtained by using these circuit parameters.

Table 4. ESD Threshold

| HBM ESD Threshold |         |  |  |

|-------------------|---------|--|--|

| Device            | Voltage |  |  |

| LG1605DXB         | ≥200 V  |  |  |

## **Mounting and Connections**

Certain precautions must be taken when using solder. For installation using a constant temperature solder, temperatures of under 300 °C may be employed for periods of time up to 5 s, maximum. For installation with a soldering iron (battery operated or nonswitching only), the soldering tip temperature should not be greater than 300 °C and the soldering time for each lead must not exceed 5 s. This device is supplied with solder on the back of the package. Due to the high gain of the device, it is recommended to solder the back of the package to ground.

#### **Mounting and Connections** (continued)

Lucent Technologies/FORCE ICs assembly procedure recommendations for the LG1605DXB are as follows:

- Board solder pattern for the 1605DXB package base should not exceed 50% of the package base area.

- Back lighting can be used during the pick and place operation to silhouette the package in order to eliminate reflection problems with the solder on the bottom.

- Set the lead spacing tolerance to ±0.012 in.

- Insertion pressure should not exceed 125 g.

#### **Electrical Characteristics**

tcase = 0 °C to 70 °C, VBR = -1.5 V, Vss = -4.7 V to -5.7 V, bit rate = 2.488 Mbits/s NRZ, and data pattern =  $2^{23} - 1$  PRBS, unless otherwise indicated.

**Note:** Minimum and maximum values are testing requirements. Typical values are characteristics of the device and are the result of engineering evaluations. Typical values are for information purposes only and are not part of the testing requirements.

| Parameter                                   | Symbol        | Conditions <sup>1</sup>                                                  | Min | Тур      | Max  | Unit  |

|---------------------------------------------|---------------|--------------------------------------------------------------------------|-----|----------|------|-------|

| Data Input Voltage <sup>2</sup>             | V±IN          | Single-ended source                                                      |     | _        | 800  | mVp-p |

| Data Input Voltage <sup>2</sup>             | V+IN - V-IN   | Differential source                                                      | _   | _        | 1600 | mVp-p |

| Input Offset Voltage                        | V+REF – V-REF | 40 °C/-5.2 V; 70 °C/-5.7 V                                               |     | _        | 25   | mV    |

| Common-mode Input<br>Voltage Range          | VCMIN         | 25 °C, Vss = -5.2 V,<br>dc input coupling                                | _   | −2 to −4 | _    | V     |

| Output Voltage                              | V±OUT         | _                                                                        | 400 | 550      | _    | mVp-p |

| Output Pulse Width Relative to Bit Period   | PW%           | Measured on V+OUT,<br>@ 40 °C and 70 °C                                  | 90  | 100      | 110  | %     |

| Small-signal Output<br>Transition Time      | tr, tf        | 25 °C, 20% to 80%,<br>VIN = 8 mVp-p                                      | _   | 100      | _    | ps    |

| Small-signal Gain                           | G             | 40 °C to 70 °C, VIN = 8 mVp-p                                            | 26  | 28       | 35   | dB    |

| Small-signal –3 dB<br>Bandwidth             | f3dB          | 25 °C, VIN = 8 mVp-p                                                     | _   | 3        | _    | GHz   |

| Low-frequency –3 dB<br>Cut-off <sup>2</sup> | fLF           | $V_{IN} = 8 \text{ mVp-p}$ , input coupling and bypassing as in Figure 3 | _   | 2.5      | 8    | kHz   |

| Supply Current                              | Iss           | _                                                                        | _   | 85       | 100  | mA    |

| Noise Figure <sup>2</sup>                   | NF            | 25 °C, single-ended input                                                |     | 15       | 16   | dB    |

| Input Referred Wideband<br>Noise            | Vnr           | 25 °C, single-ended input,<br>7 kHz—18 GHz                               | _   | 168      | _    | μVrms |

| Thermal Resistance                          | θЈС           | Junction to case                                                         | _   | 30       | _    | °C/W  |

<sup>1.</sup> All temperatures are case temperature, tCASE.

<sup>2.</sup> Parameter guaranteed by design or characterization and not production tested.

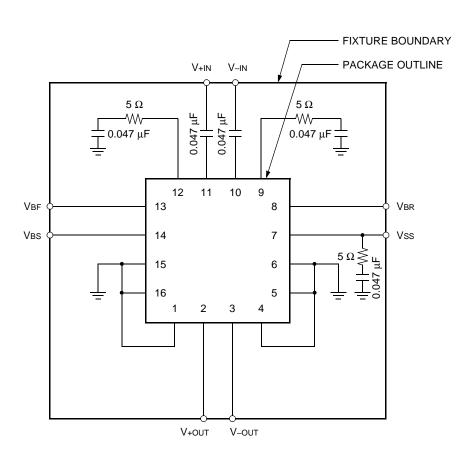

#### **Test Circuit**

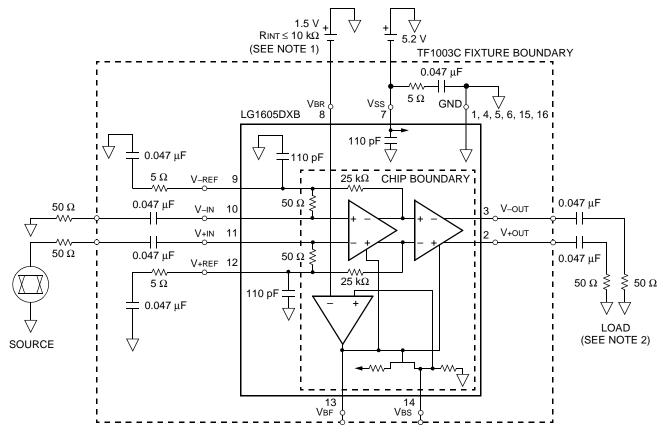

12-3215(F)r.6

- 1. Depending on the desired supply rejection, VBR can be biased with a simple resistive divider, or resistor/zener diode network.

Alternatively, when the LG1605DXB is followed by the LG1600 clock and data regenerator, a resistive divider with bypassing capacitor may be connected to pin 7 (VREF) of the LG1600 (VREF ≈ −3.2 V). This arrangement provides excellent temperature stability and power supply rejection.

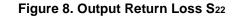

- 2. The outputs may be either ac coupled, as indicated, or dc terminated into 50 Ω. In the first case, good output return loss (see Figure 8) can be obtained. The latter configuration provides a 0 mV to –600 mV output swing (when limiting) for easy interface to dc-coupled circuits. No input coupling capacitors are needed when interfacing with the LG1600 or the 1319 receiver.

Figure 3. LG1605DXB Test Circuit (with TF1003C Test Fixture)

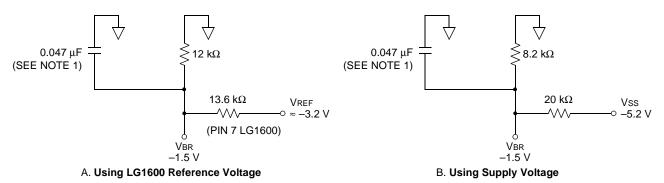

12-3216(F)r.3

1. Depending on the desired supply rejection, VBR can be biased with a simple resistive divider, or resistor/zener diode network. Alternatively, when the LG1605DXB is followed by the LG1600 clock and data regenerator, a resistive divider with bypassing capacitor may be connected to pin 7 (VREF) of the LG1600 (VREF ≈ −3.2 V). This arrangement provides excellent temperature stability and power supply rejection.

Figure 4. Bias Options

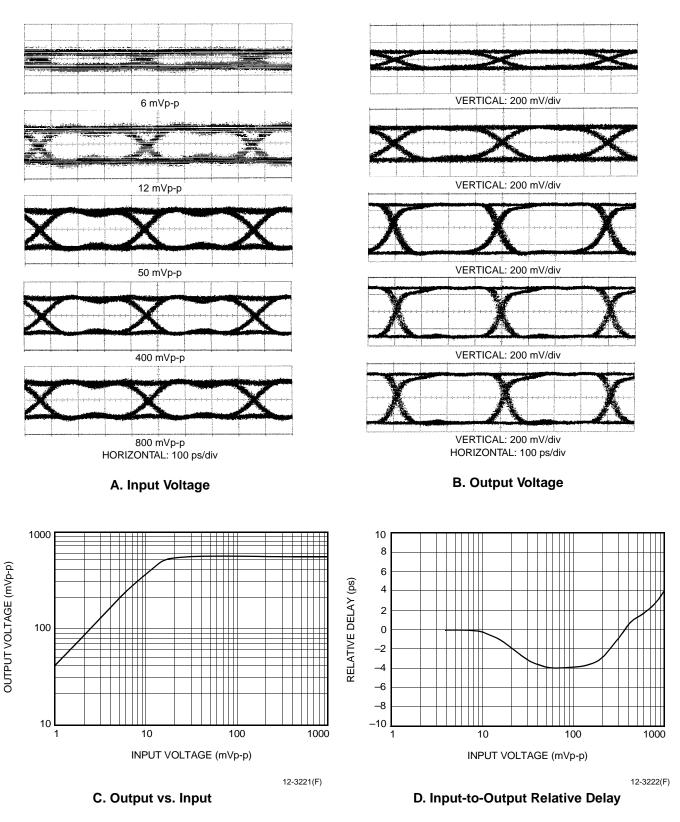

## **Typical Performance Characteristics**

-10 -20 -30 -40 -50 -60 -70 -80 FREQUENCY (GHz) 12-3219(F)

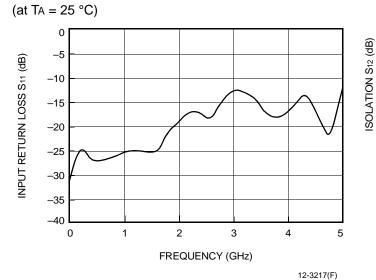

Figure 5. Input Return Loss S<sub>11</sub>

OUTPUT RETURN LOSS  $\mathbf{S}_{22}$  (dB) -5 -10 -15 -20 -25 -30 -35 FREQUENCY (GHz)

Figure 7. Isolation S<sub>12</sub>

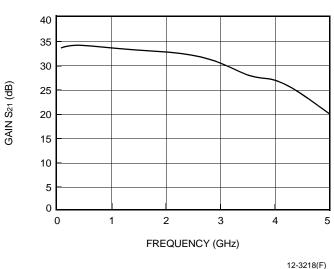

Figure 6. Gain S<sub>21</sub>

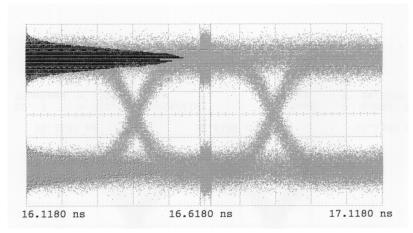

HORIZONTAL: 100 ps/div, VERTICAL: 12 mV/div; VIN = 2.23 mVp-p, VIN = 58.8 mVp-p,

Figure 9. Output Noise Histogram

12-3220(F)

### Typical Performance Characteristics (at TA = 25 °C) (continued)

Figure 10. Limiting Characteristics

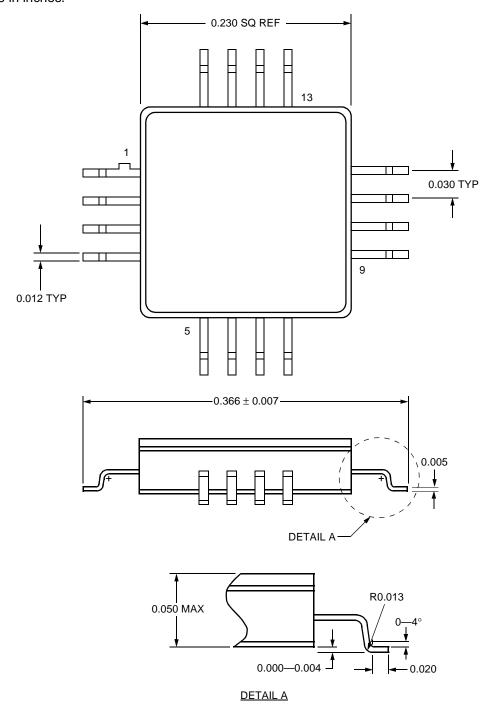

# **Outline Diagram**

## 16-Pin, Glass-Metal, Surface-Mount Package

Dimensions are in inches.

12-3224(F).b

# **Ordering Information**

| Device Code    | Package                        | Temperature   | Comcode<br>(Ordering Number) |

|----------------|--------------------------------|---------------|------------------------------|

| LG1605DXB-TR16 | Package on 16 mm tape and reel | 0 °C to 70 °C | 107142614                    |

| LG1605DXB-FLP  | Package in flat pack container | 0 °C to 70 °C | 107412025                    |

| TF1003C        | Test fixture                   | _             | 106990138                    |

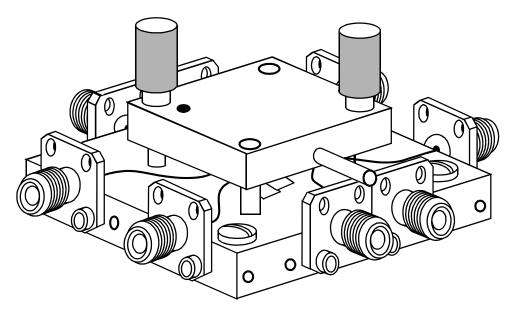

# **Appendix**

The test fixture mentioned in the data sheet is sold separately and is described in detail below.

Note: Dot on test fixture lid indicates position of pin 1.

Figure 11. TF1003C Test Fixture

Figure 12. TF1003C Electrical Diagram

5-7209(F)

5-7208(F).r1

#### **Appendix** (continued)

5-7210(F)

Figure 13. TF1003C Connector Assignment (Pressure ring not shown.)

For additional information, contact your Microelectronics Group Account Manager or the following:

INTERNET: http://www.lucent.com/micro E-MAIL: docmaster@micro.lucent.com

N. AMERICA: Microelectronics Group, Lucent Technologies Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18103

1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106)

ASIA PACIFIC: Microelectronics Group, Lucent Technologies Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256 Tel. (65) 778 8833, FAX (65) 777 7495

Microelectronics Group, Lucent Technologies (China) Co., Ltd., A-F2, 23/F, Zao Fong Universe Building, 1800 Zhong Shan Xi Road, Shanghai 200233 P. R. China Tel. (86) 21 6440 0468, ext. 316, FAX (86) 21 6440 0652

JAPAN: Microelectronics Group, Lucent Technologies Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan

Tel. (81) 3 5421 1600, FAX (81) 3 5421 1700

Data Requests: MICROELECTRONICS GROUP DATALINE: Tel. (44) 1189 324 299, FAX (44) 1189 328 148 EUROPE:

Technical Inquiries:GERMANY: (49) 89 95086 0 (Munich), UNITED KINGDOM: (44) 1344 865 900 (Ascot), FRANCE: (33) 1 40 83 68 00 (Paris), SWEDEN: (46) 8 594 607 00 (Stockholm), FINLAND: (358) 9 4354 2800 (Helsinki), ITALY: (39) 02 6608131 (Milan), SPAIN: (34) 1 807 1441 (Madrid)

Lucent Technologies Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information. FASTCAT is a trademark of Lucent Technologies Inc.

**Lucent Technologies**

microelectronics group

CHINA: