#### TOSHIBA BI-CMOS INTEGRATED CIRCIUTS

## **TB62718AF**

### Full color LED module and panel special controller and LED driver

TB62718AF

Weight:

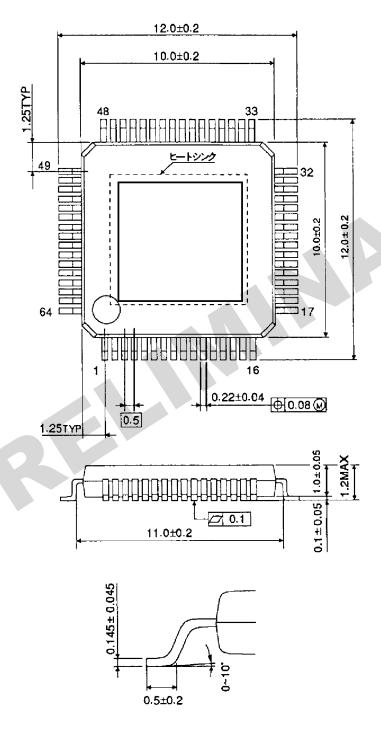

HQFP64-P-1010-0.50

@ @ @ @(Typ.)

TB62718AF is the LED-driver which is suitable for lighting of the full color LED module. This device builds in a PWM gray scale function and each output current value compensation function, and 16s LED can turn it on. Then, heat-sink connection side is on the surface of the package, and heat-sink is used, and this device can ease rise in temperature of the device. Furthermore, this device builds in TSD (ThermalShutDown) and an output open detection function as a protection function.

- \*Constant Current Range: 5 to 90mA

- \*Application Output Voltage: 0.7V (output current 5 to 80 mA)

- \*Various Adjustment Functions

- 1:Standard Current Adjustment (Input 8bits by the serial data.)

This function supports standard current adjustment by the REXT resistance.

MSB side 2 bits --- Adjust Output Current 25%-100 % range in 4 step.

LSB side 6 bits --- Adjust Output Current 40%-100 % range in 64 step.

2:Dot Adjustment (Input it 128 bits by the serial data.)

This function adjusts the current value of each output.

- --- Adjust Output Current 20-100% range in 64 step.

- 3: All Bit Adjustment 1(Input it 8bits by the parallel data.)

This function adjusts brightness for each LED module.

LSB side 5 bits --- Adjust Output Current 50%-100 % range in 32 step.

4: All Bit Adjustment 2 (Input it 8bits by the parallel data.)

This function changes the frequency of PWM clock, and adjusts brightness of the display greatly.

MSB side 3 bits --- Adjust PWM clock frequency 1/1 - 1/8 renge in 8 step.

5: 256 gray scale PMW function (Input it 8 bits by the parallel data.)

This function controls the pulse width of each output with 256 gray scale.

PWM clock frequency 10MHz (all the temperature ranges, muximum). Minimum pulse width 2 micro second.

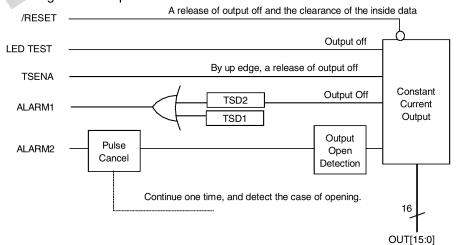

- \*Protection Function

- 1: The Thermal Shut Down Function (TSD)

This function watches rise in temperature of the junction.

Connect pull up resistor with the ALARM1 terminal, and it can be monitored.

2: Output Terminal Open Detection Function

This function detects that output terminal opens.

Connect pull up resistor with the ALARM2 terminal, and it can be monitored.

- \*For Annode Common LED

- \*Input Signal Voltage Level: CMOS Level (Shmitt Triggered Input)

- \*Power Supply Voltage Range VDD=4.5 to 5.5V

- \*Muximum output terminal voltage 26V

- \*Serial and Pararell Data Transfer Rate 20MHz (max, Cascade Connection)

- \*Operation Temperature Range Topr= -40 to 85 degrees

- \*Package: HQFP64-P-1010-0.50. Heat-Sink can be connected.

- \*Attention point in application:

There is fear of the device destruction in the short circuit of the output terminal to GND and the power supply.

Be fully careful of wiring of the output terminal, the power supply terminal, the GND terminal (VSS, VSS2).

Don't do soldering, increasing electric potential (Plus, minus aren't asked to it.) to heat-sink terminal.

120 Broadway • Menands, New York 12204

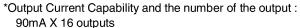

Pin layout(TOP VIEW) and marking Pakage type: HQFP64-P-1010-0.50

Note: Indicate device name on the upside of the package. Indicate weekly code bottomside of the package.

The details of the weekly code of the bottom side:

From the left of the weekly code,

1st Character = A.D. rightmost digit.

Write 0 in the case of 2000, and write 1 in the case of 2001.

2nd and 3rd Character = Write that it was manufactured in a what week of the year. Muximum 52. 4th Character = Manufacture factory indication.

("K" is the meaning of our Kita Kyushu factory production.)

5th to 7th Character = Write manufacture lot number out of 1 week.

Write the 1st Lot with A11. 2nd Lot with A1 and 3rd Lot with A.

Write the 4th Lot with B11. 5th Lot with B1 and 6th Lot with B.

Write the 64th Lot with Z11. 65th Lot with Z1 and 66th Lot with Z.

Four characters of "I", "M", "O", "W" aren't used in consideration of the correctness of marking.

120 Broadway • Menands, New York 12204

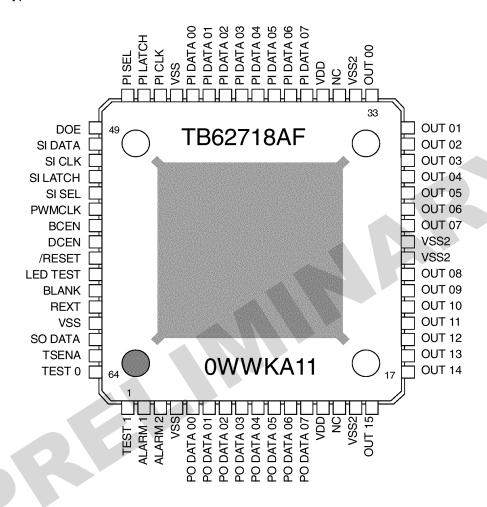

Block Diagram (whole figure)

120 Broadway • Menands, New York 12204

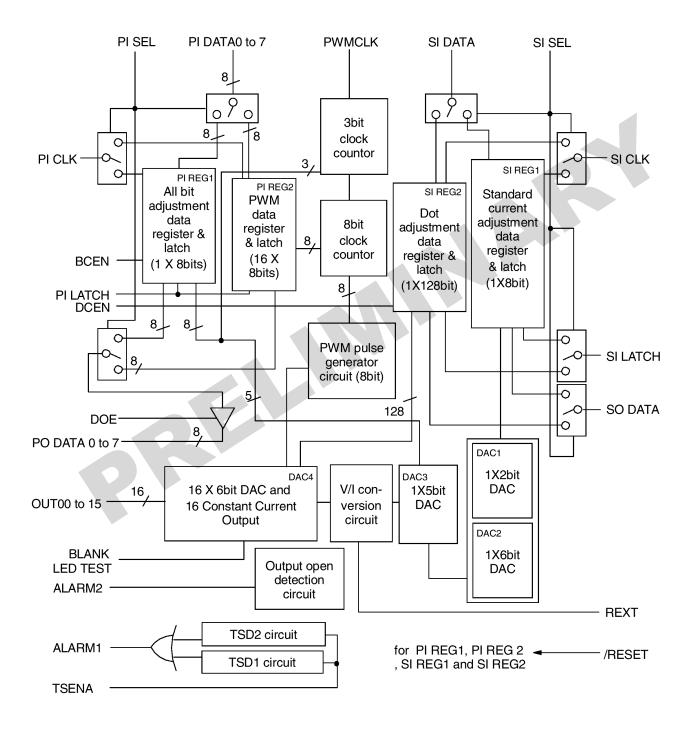

Constant current adjustment range (image)

GRAPH: : Currnet adjustment range that it was done based on 100%

Note: The mutual relationship of the front step DAC and the rear step DAC makes the adjustment result of the former step 100%.

#### Reference:

About each current adjustment function.

DAC1 to DAC3 is the current adjustment function of all the output.

The adjustment width of DAC1 is big and rough. (about 1LSB= 25%)

The adjustment width of DAC2 is the smallest, and the error of it is big. (about 1LSB= 0.9%)

The adjustment width of DAC3 is small, and it is the high performance DAC whose error is small. (about 1LSB=1.61%)

Therefore, recommend using it for the change of the absolute value of the REXT resistance and the adjustment of the REXT resistance dispersion with DAC1 and DAC2.

Recommend using it for brightness adjustment between the module with DAC3.

(After it was set and it had DAC4 adjusted to the dot.)

The beginning is set in about 75% of the middle value, and it is effective to use +- 25% of set width.

DAC4 is the current adjustment function of each output.

The adjustment width of DAC4 is small, and it is the high performance DAC whose error is small. (about 1LSB= 1.27%)

And, DAC4 has very wide set range.

Therefore, adjust DAC4 including brightness dispersion of LED which rank classification hasn't been carried out on.

Then, it is presumed that brightness dispersion of all the output is adjusted to the one within 1.27%(Note1).

Note 1: It is when it guesses that there is correlation between the output current and LED brightness.

120 Broadway • Menands, New York 12204

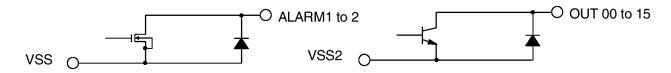

# Equivalent input and output schematics (Resistance value is standard value)

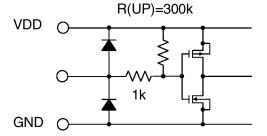

1. Input terminal with the pull up resistor TSENA, BLANK, BCEN, DCEN

2. Input terminal with the pull down resistor. SI/PI LATCH, PI DATA0 to 7. LEDTEST

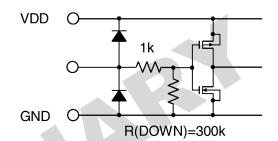

3. Input terminal.

SI DATA, SI/PI CLK, PWMCLK -(A)

/RESET, DOE, PI/SI SEL -(B)

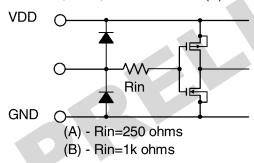

4. Output terminal ALARM1 to 2, PO DATA 0 to 7, SO DATA

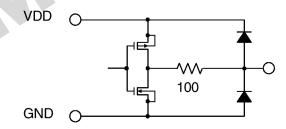

5. Protection circuit monitor terminal

6. Constant current output terminal

## TERMINAL FUNCTION EXPLANATION TABLE

|                 | TERMINAL          |       |           |                                                                                                                                                                                                                                                                                                                     |

|-----------------|-------------------|-------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.             | NAME              | 1/0   |           | FUNCTION EXPLANATION                                                                                                                                                                                                                                                                                                |

| 4,45            | VSS               | Р     | -         | These are logic ground terminals. Please, must use all.                                                                                                                                                                                                                                                             |

| 35,14           | NC                | -     | -         | These are the terminals which haven't been used.                                                                                                                                                                                                                                                                    |

| 63              | TSENA             | ***   | Pull Up   | This is the terminal which does resetting of the TSD circuit.  Cancel it on the edge of the rise of this input signal when TSD circuit moves and the condition that it offs all has all the output.  The data that latch is worn aren't reset.  TSD circuit moves regardless of the voltage level of this terminal. |

| 15,24,2<br>5,34 | VSS2              | Р     | -         | These are the ground terminals of the output. Please, must use all.                                                                                                                                                                                                                                                 |

| 13,35           | VDD               | Р     | -         | These are logic power supply input term in als. Please, must use all.                                                                                                                                                                                                                                               |

| 16,23,2<br>6,33 | OUT00 to<br>15    | 0     | -         | These are LED drive output terminals. Connect cathode of LED.                                                                                                                                                                                                                                                       |

| 50              | SI DATA           |       | <u>.</u>  | This is a serial data input terminal. Input standard current adjustment data and dot adjustment data.                                                                                                                                                                                                               |

| 51              | SI CLK            |       | -         | This is a serial data transfer clock input terminal. Transfer data by up edge.                                                                                                                                                                                                                                      |

| 52              | SILATCH           | -     | Pull Down | This is a serial data latch signal input terminal. Hold data by up edge.                                                                                                                                                                                                                                            |

| 53              | SI SEL            | 1     | -         | This is a serial data choice terminal. Choose either standard current adjustment data or dot adjustment data.                                                                                                                                                                                                       |

| 62              | SO DATA           | 0     | -         | This is a serial data output terminal. Output data are chosen with SI SEL.                                                                                                                                                                                                                                          |

| 37 to<br>44     | PI DATA<br>0 to 7 | 1     | Pull Down | These are pararell data input terminals. Input all the output adjustment data and PWM data.                                                                                                                                                                                                                         |

| 45              | PI CLK            | 1     | -         | This is pararell data transfer clock input terminal. Transfer data by up edge.                                                                                                                                                                                                                                      |

| 47              | PLATCH            | ****  | Pull Down | This is pararell data latch signal input terminal. Hold data by up edge.                                                                                                                                                                                                                                            |

| 48              | PI SEL            | ı     | -         | This is pararell data choice terminal. Choose either all the output adjustment data or PWM data.                                                                                                                                                                                                                    |

| 5 to 12         | PO DATA<br>0 to 7 | 0     |           | This is pararell data output terminal. Output data are chosen with PISEL.                                                                                                                                                                                                                                           |

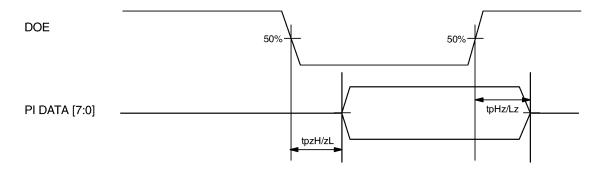

| 49              | DOE               |       |           | This is the control terminal of pararell data output PODATA. PIDATA is outputted by input of H level. And, it is set up in the high impedance by input of L level.                                                                                                                                                  |

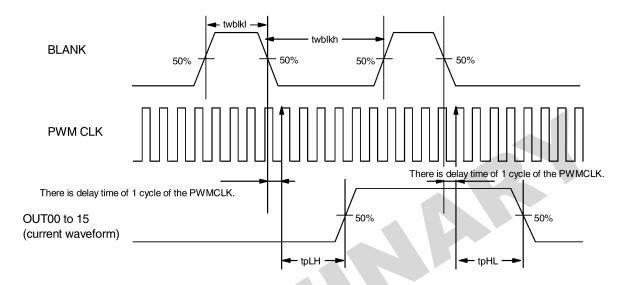

| 59              | BLANK             | 1     | Pull Up   | This terminal is a PWM circuit movement control signal input terminal. It becomes output off by input of H level. And, start PWM output by input of L level.                                                                                                                                                        |

| 54              | PWMCLK            |       | -         | This is the standard clock input terminal of the PWM circuit. This clock 1 cycle is equivalent to the minimum pulse width of the PWM output.                                                                                                                                                                        |

| 55              | BCEN              | ****  | Pull Up   | This is the use choice signal input terminal of all the output adjustment functions. All output adjustment is fixed on 100% in the L level. And, all bit adjustment becomes effective in the H level.                                                                                                               |

| 56              | DCEN              | 1     | Pull Up   | This is the use choice signal input terminal of the dot adjustment function. Dot adjustment value is fixed on 100% in the L level. And, dot adjustment becomes effective in the H level.                                                                                                                            |

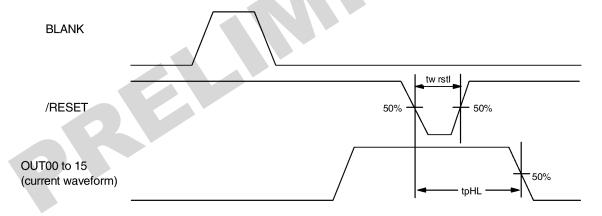

| 57              | /RESET            | ***** | -         | This is a reset signal input terminal. Reset all the register data in the L level. Or, use it for a release of TSD.                                                                                                                                                                                                 |

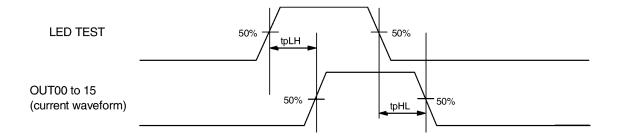

| 58              | LED TEST          | 1     | Pull Down | This is the connection confirmation signal input terminal of LED. All the output ons in the H level. Use it in the L level usually.                                                                                                                                                                                 |

| 60              | REXT              | Р     | -         | This is the connection terminal of the standard current set resistance.                                                                                                                                                                                                                                             |

| 2               | ALARM1            | 0     | -         | This is open drain type with the monitor terminal of the TSD circuit. TSD circuit detects unusual temperature, and ons. Pull up does by the resistance to monitor it. ALARM1 moves independently in the /RESET signal.                                                                                              |

| 3               | ALARM2            | 0     | -         | This is open drain type with the monitor terminal of the output open detection circuit. Output opening is detected, and ALARM2 ons.                                                                                                                                                                                 |

| 1,64            | TEST<br>0 to 1    | ***   | -         | These are the terminals to use for the device test. Connect all with the L level.                                                                                                                                                                                                                                   |

Terminal attribute ) P: Power Supply/Ground/Others, I: Input Terminal, O: Output Terminal Recommend not making terminal with the pull up/down resistor open.

There is fear of faulty operation by the circumference noise.

120 Broadway • Menands, New York 12204

Absolute Maximum Ratings (Topr = 25 degC, unless otherwise noted.)

| DC Characteristic               | Symbol   | Rating          | Unit   | Notes                                                                                                      |

|---------------------------------|----------|-----------------|--------|------------------------------------------------------------------------------------------------------------|

| Supply voltage                  | VDD      | -0.3 to 7       | V      |                                                                                                            |

| Constant current output voltage | VO       | -0.3 to 26      |        |                                                                                                            |

| Output current                  | IOUT     | 90              | mA/bit |                                                                                                            |

| Logic output voltage            | VOUT     | -0.3 to VDD+0.3 | V      |                                                                                                            |

| Logic input voltage             | VIN      | -0.3 to VDD+0.3 | V      |                                                                                                            |

| VSS2 current in total           | IVSS2    | 1440            | mA     | Must use VSS2 (4 terminal) all.<br>When all isn't used, all<br>characteristic guarantees can't be<br>done. |

|                                 |          | 1.00            |        | Free Air                                                                                                   |

| Power dissipation               | Pd       | 1.19            | W      | On PCB 100X100X 1.6mm                                                                                      |

|                                 |          | 5.0             |        | On PCB of the Infinity                                                                                     |

| Saturation heat resistance of   | Rth(j-a) | 125             |        | Free Air                                                                                                   |

| package                         |          | 105             | degC/W | On PCB 100 X 100 X 1.6mm                                                                                   |

|                                 | Rth(j-c) | 25              |        | On PCB of the Infinity                                                                                     |

| Operating temperature           | Topr     | -40 to 85       | degC   |                                                                                                            |

| Strage temperature              | Tstg     | -55 to 150      |        |                                                                                                            |

#### NOTE:

Subtract 0.95 mW/degC from the muximum rating value about 1 degC if operation temperature exceeds 25 degC. On PCB 100 X 100 X 1.6mm.

## **Recommended Operating Condition**

| DC characteristic         | Symbol | Condition & Terminal                                                                  | Min    | Тур | Max    | Unit   |

|---------------------------|--------|---------------------------------------------------------------------------------------|--------|-----|--------|--------|

| Supply voltage            | VDD    |                                                                                       | 4.5    | 5.0 | 5.5    |        |

| High level input voltage  | VIH    | PI DATA, PI CLK, PI SEL,<br>PI LATCH, SI DATA,<br>SI CLK, SI SEL, SI<br>LATCH, PWMCLK | 0.7VDD |     | VDD    | V      |

| Low level input voltage   | VIL    | BLANK, LED TEST,<br>TSENA,DOE, DCEN,<br>BCEN                                          | VSS    |     | 0.3VDD |        |

| High level output current | IOH    | DATA PO0 to 7 , DATA<br>SO                                                            |        |     | -1     |        |

| Low level output current  | IOL    | VDD=4.5V, ALARM1 to 2                                                                 |        |     | +1     | mA     |

| Constant current cutput   | IOUT   | OUT00 to 15                                                                           | +5     |     | +80    | mA/bit |

| Output voltage            | VO     | OUT00 to 15 off.                                                                      |        |     | +26    | V      |

|                           | VOH    | ALARM1 to 2 off.                                                                      |        |     | +5     |        |

| Operating temperature     | Topr   |                                                                                       | -40    |     | +85    | degC   |

120 Broadway • Menands, New York 12204

## Recommended Operating Condition (continue) (VDD= 4.5 to 5.5V, Topr = -40 to 85 degC, unless otherwise noted.)

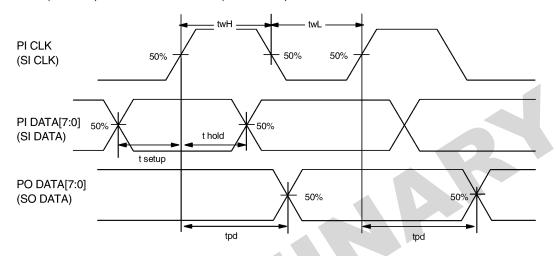

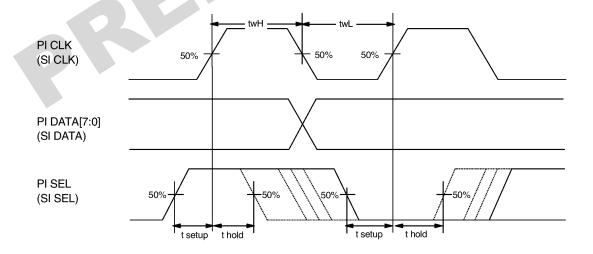

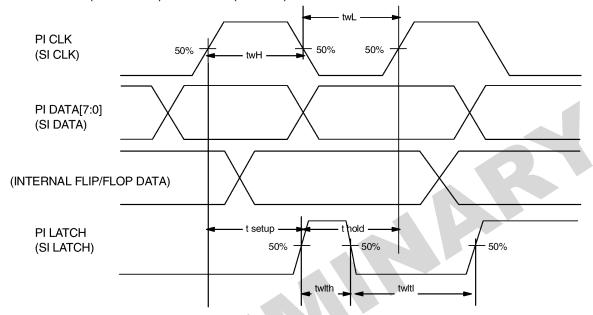

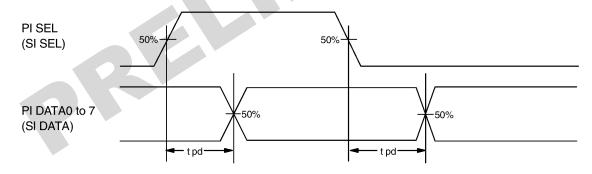

| AC characteristics  | Symbol        | Condition & Terminal                  | Min | Тур | Max | Unit |

|---------------------|---------------|---------------------------------------|-----|-----|-----|------|

|                     | fPWM          | Ratio of High/Low Level = 50%, PWMCLK |     |     | 10  |      |

| Clock frequency     | fPI1          | PI CLK, Solo                          |     |     | 15  | MHz  |

|                     | fPI2          | PI CLK, cascade connected             |     |     | 10  |      |

|                     | fSI1          | SICLK                                 |     |     | 15  |      |

|                     | fSI2          | SI CLK, cascade connected             |     |     | 10  |      |

|                     | twH/twL       | PWM CLK                               | 30  |     |     | ns   |

|                     |               | PI CLK, SI CLK                        | 30  |     |     |      |

|                     | twltH/tpltL   | PI LATCH. SI LATCH                    | 50  |     |     |      |

| Minimum pulse width | twrstH/twrstL | /RESET                                | 50  |     | _   | ns   |

|                     | twblkH/twblkL | BLANK                                 | 400 |     |     |      |

|                     | twledH/twledL | LED TEST                              | 400 |     |     |      |

|                     |               | PI DATA -> PI CLK                     | 10  |     |     |      |

|                     |               | PI LATCH -> PI CLK                    | 10  |     |     |      |

| Setup time          | tsetup        | SI DATA -> SI CLK                     | 10  |     |     |      |

|                     |               | SI LATCH -> SI CLK                    | 10  |     |     |      |

|                     |               | SI LATCH -> SI SEL                    | 50  |     |     | ns   |

|                     |               | PI DATA -> PI CLK                     | 5   |     |     |      |

|                     |               | PI LATCH -> PI CLK                    | 5   |     |     |      |

| Hold time           | thold         | SI DATA -> SI CLK                     | 5   |     |     |      |

|                     |               | SI LATCH -> SI CLK                    | 5   |     |     |      |

|                     |               | SI LATCH -> SI SEL                    | 50  |     |     |      |

120 Broadway • Menands, New York 12204

### **Electrical Characteristics 1**

( Typ:VDD=5.0V, Topr=25degC, Min/Max:VDD=4.5 to 5.5V, Topr=-40 to 85 degC )

| Parameter                       | Symbol | Test Condition & Terminal                                                                            | Min         | Тур   | Max | Unit |

|---------------------------------|--------|------------------------------------------------------------------------------------------------------|-------------|-------|-----|------|

| High level output voltage       | VOH    | IOH=-1mA, PO DATA0 to 7, SO DATA                                                                     | VDD<br>-0.4 |       |     |      |

| Low level output voltage        | VOL    | IOL=1mA, PO DATA0 to 7, SO DATA                                                                      |             |       | 0.4 | V    |

|                                 |        | IOL=+1.0mA, ALARM1 to 2                                                                              |             |       | 0.3 |      |

| Tristate output leakage current | IOZ    | VOUT=VDD or VSS, PO DATA0 to 7                                                                       |             | +-0.5 | +-5 | uA   |

| Input current                   | 11     | All terminal which pull up/pull down resistor is not in.                                             |             |       | +-1 |      |

|                                 | IDD1   | PI DATA=1/2 PI CLK SI DATA=1/2 SI CLK PI CLK=SI CLK=20MHz PWMCLK = "L", BLANK = "H" Set condition *1 |             | 20    | 30  |      |

|                                 | IDD2   | PI DATA=SI DATA="L" PI CLK=SI CLK="L" PWM CLK=20MHz Set condition *5a                                |             | 75    | 105 |      |

| Supply current                  | IDD3   | PI DATA=1/2 PI CLK<br>SI DATA=1/2 SI CLK<br>PI CLK=SI CLK=PWMCLK=20MHz<br>Set condition *5a          |             | 80    | 115 | mA   |

|                                 | IDD4   | PI DATA=SI DATA="L" PI CLK=SI CLK="L" PWM CLK=20MHz, Set condition *6a                               |             | 90    | 140 |      |

|                                 | IDD5   | PI DATA=1/2 PI CLK<br>SI DATA=1/2 SI CLK<br>PI CLK=SI CLK=PWM CLK=20MHz<br>Set condition *6a         |             | 95    | 150 |      |

## NOTE: Electrical Characteristics Set Condition (OUT0 to 15 All on, VO=0.7V and REXT=2.7kohms, unless otherwise norted)

| No. | Set Condition                                  | All bit adjustment<br>"DAC3" | Constant Output Currnet (typ) |

|-----|------------------------------------------------|------------------------------|-------------------------------|

| *1  | Output all off, VO=26V, DAC1-2- 4=MSB, BLANK=H |                              | IOUT=0mA                      |

| *2  | DAC1=0, DAC2= 0, DAC4=63, BLANK=L              |                              | IOUT=7.1mA                    |

| *3a | DAC1=0, DAC2=17, DAC4=63, BLANK=L              |                              | IOUT=10mA                     |

| *4a | DAC1=1, DAC2=17, DAC4=63, BLANK=L              | DAC3=31                      | IOUT=20mA                     |

| *5a | DAC1=2, DAC2=37, DAC4=63, BLANK=L              |                              | IOUT=40mA                     |

| *6a | DAC1=3, DAC2=51, DAC4=63, BLANK=L              |                              | IOUT=60mA                     |

| *7  | DAC1=3, DAC2=63, DAC4=63, BLANK=L              |                              | IOUT=71mA                     |

| *3b | DAC1=0, DAC2=17, DAC4=63, BLANK=L              |                              | IOUT=5mA                      |

| *4b | DAC1=1, DAC2=17, DAC4=63, BLANK=L              | DAC3=00                      | IOUT=10mA                     |

| *5b | DAC1=2, DAC2=37, DAC4=63, BLANK=L              |                              | IOUT=20mA                     |

| *6b | DAC1=3, DAC2=51, DAC4=63, BLANK=L              |                              | IOUT=30mA                     |

120 Broadway • Menands, New York 12204

## **Electrical Characteristics 2**

( Typ:VDD=5.0V, Topr=25degC, Min/Max:VDD=4.5 to 5.5V, Topr=-40 to 85 degC )

| Parameter                                         | Symbol      | Test Condition                                                      | Min  | Тур     | Max  | Unit        |

|---------------------------------------------------|-------------|---------------------------------------------------------------------|------|---------|------|-------------|

|                                                   | IO1         | Set condition *7                                                    | 60.4 | 71      | 81.6 |             |

| Constant Cuurnet Output                           | 102         | Set condition *6a                                                   | 51.2 | 60      | 69.2 |             |

|                                                   | IO3         | Set condition *5a                                                   | 34.1 | 40      | 46.1 | mA          |

| (within current                                   | 104         | Set condition *4a                                                   | 16.5 | 20      | 23.2 |             |

| error between bits)                               | 105         | Set condition *3a                                                   | 7.8  | 10      | 12.2 |             |

|                                                   | 106         | Set condition *2                                                    | 4.54 | 7.1     | 9.65 |             |

| Constant current output                           | %TOPR1      | Set condition *6a,VOUT=1.0V,<br>Topr is changed from -40 to 85degC. |      | +-50    | +-80 | uA<br>/degC |

| depends on temperature                            | %TOPR2      | Set condition *4a,VOUT=1.0V,<br>Topr is changed from -40 to 85degC. |      | +-25    | +-50 |             |

| Leakage current of the constant current output    | IOLK        | Set condition *1, VOUT=26V                                          |      | 0.05    | 0.1  | uA          |

|                                                   | dIOUT1      | Set condition *6a, VOUT=0.7V                                        |      | +-2.5   | +-6  |             |

| Constant Current                                  | dIOUT2      | Set condition *5a, VOUT=0.7V                                        |      | +-3.5   | +-6  |             |

| Error bitween bits                                | dIOUT3      | Set condition *4a, VOUT=0.7V                                        |      | +-5.5   | +-7  |             |

|                                                   | dIOUT4      | Set condition *3a, VOUT=0.7V                                        |      | +-7     | +-12 |             |

| Dot adjustment deviation                          | %IOUT1      | Set condition is changed from *6a to *6b.                           |      | +-1     | +-3  |             |

| between bits (When DAC3                           | %IOUT2      | Set condition is changed from *5a to *5b.                           |      | +-1.5   | +-3  | %           |

| data were changed from                            | %IOUT3      | Set condition is changed from *4a to *4b.                           |      | +-3.5   | +-5  |             |

| MSB to LSB.)                                      | %IOUT4      | Set condition is changed from *3a to *3b.                           |      | +-6     | +-12 |             |

| Constant current output                           | %VOUT       | Set condition *6a,<br>VO is changed from 0.7V to 3V.                |      | +-5     | +-8  |             |

| depends on output voltage                         |             | Set condition *4a,<br>VO is changed from 0.7V to 3V.                |      | +-3     | +-6  |             |

| Constant current output depends on supply voltage | %VDD        | Set condition *6a,<br>VDD is changed from 4.5V to 5.5V              |      | +-1     | +-2  |             |

| TSD detection                                     | Tsd1        |                                                                     | 120  | 140     | 160  | degC        |

| temperature                                       | Tsd2        |                                                                     | 140  | 160     | 180  | ]           |

| Output open detection voltage                     | VARL        | ALARM2                                                              |      | 0.04VDD |      | ٧           |

| Pull up/down resistor                             | Rup<br>/Rdw |                                                                     | 150k | 300k    | 600k | ohms        |

## NOTE: Electrical Characteristics Set Condition

(OUT0 to 15 All on, VO=0.7V and REXT=2.7kohms, unless otherwise norted)

| No. | Set Condition                                  | All bit adjustment<br>"DAC3" | Constant Output Currnet (typ) |

|-----|------------------------------------------------|------------------------------|-------------------------------|

| *1  | Output all off, VO=26V, DAC1-2- 4=MSB, BLANK=H |                              | IOUT=0mA                      |

| *2  | DAC1=0, DAC2= 0, DAC4=63, BLANK=L              |                              | IOUT=7.1mA                    |

| *3a | DAC1=0, DAC2=17, DAC4=63, BLANK=L              |                              | IOUT=10mA                     |

| *4a | DAC1=1, DAC2=17, DAC4=63, BLANK=L              | DAC3=31                      | IOUT=20mA                     |

| *5a | DAC1=2, DAC2=37, DAC4=63, BLANK=L              |                              | IOUT=40mA                     |

| *6a | DAC1=3, DAC2=51, DAC4=63, BLANK=L              |                              | IOUT=60mA                     |

| *7  | DAC1=3, DAC2=63, DAC4=63, BLANK=L              |                              | IOUT=71mA                     |

| *3b | DAC1=0, DAC2=17, DAC4=63, BLANK=L              |                              | IOUT=5mA                      |

| *4b | DAC1=1, DAC2=17, DAC4=63, BLANK=L              | DAC3=00                      | IOUT=10mA                     |

| *5b | DAC1=2, DAC2=37, DAC4=63, BLANK=L              |                              | IOUT=20mA                     |

| *6b | DAC1=3, DAC2=51, DAC4=63, BLANK=L              |                              | IOUT=30mA                     |

120 Broadway • Menands, New York 12204

## Switchin characterictics

(Typ: VDD=5V, Topr=25degC, CL=50pF,

Min/Max: VDD=4.5 to 5.5V, Topr=-40 to 85degC, CL=50pF, unless otherwise noted.)

| Parameter                                       | eter Symbol Test Condition |                          | Min | Тур | Max | Unit |

|-------------------------------------------------|----------------------------|--------------------------|-----|-----|-----|------|

| Tristate output propagation delay for enable    | tpZH/ZL                    | DOE -> PO DATA 0 to 7    | 8   | 16  | 30  |      |

| Tristate output propagation delay for disenable | tpHZ/LZ                    | DOE -> PO DATA 0 to 7    | 8   | 16  | 30  | ns   |

| Rise time                                       | tr                         | OUT 00 to 15             | 10  | 17  | 30  |      |

|                                                 |                            | ALARM1 to 2              | 0.2 | 0.4 | 0.8 | us   |

| Fall time                                       | tf                         | OUT 00 to 15             | 20  | 40  | 70  | ns   |

|                                                 |                            | ALARM1 to 2              | 2   | 4   | 8   | ns   |

|                                                 | tpHL                       | BLANK -> OUT 00 to 15    | 30  | 60  | 120 |      |

|                                                 | tpLH                       | PWM CLK -> OUT 00 to 15  | 70  | 120 | 200 |      |

|                                                 | tpHL                       |                          | 40  | 70  | 140 |      |

| Propagation delay                               | tpLH                       | LED TEST -> OUT00 to 15  | 60  | 110 | 190 |      |

|                                                 | tpHL                       |                          | 30  | 60  | 130 | ns   |

|                                                 | tpHL                       | /RESET -> OUT 00 to 15   | 30  | 60  | 130 |      |

|                                                 |                            | PI CLK -> PO DATA 0 to 7 | 20  | 30  | 70  |      |

| tpd PI SEL -> PO DATA 0 to 7                    |                            | PI SEL -> PO DATA 0 to 7 | 20  | 30  | 70  |      |

|                                                 |                            | SI CLK -> SO DATA        | 10  | 18  | 40  |      |

|                                                 |                            | SI SEL -> SO DATA        | 10  | 20  | 40  |      |

120 Broadway • Menands, New York 12204

Operating explanation and truth value table (1/12 pages)

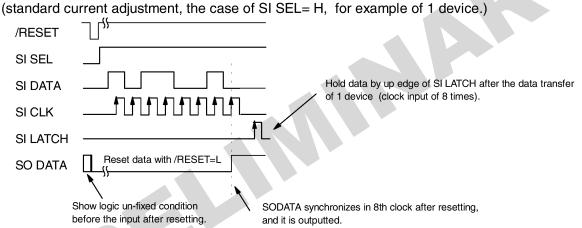

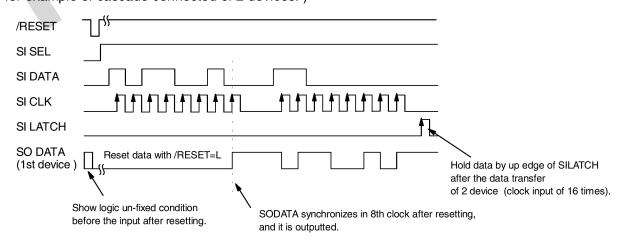

Serial data transfer: standard current adjustment DAC1 and DAC2 (about the data register SI REG[7:0])

|   | SI DATA | SI CLK   | SI LATCH | SI SEL | SO DATA      | Operating and function                                                                                                                                   |

|---|---------|----------|----------|--------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 |         | (8times) | L        | I      | H or L       | Choose the input data of standard current adjustment (8 bits,2bits and 6bits) with SI SEL=H. Transfer data to SI REG1 by up edge 8times input of SI CLK. |

| 2 | H or L  | L        | (1time)  | I      | No<br>Change | Hold the data transferred to SI REG1 by up edge of SI LATCH. Set is reflected on standard current adjustment from the moment when it is held.            |

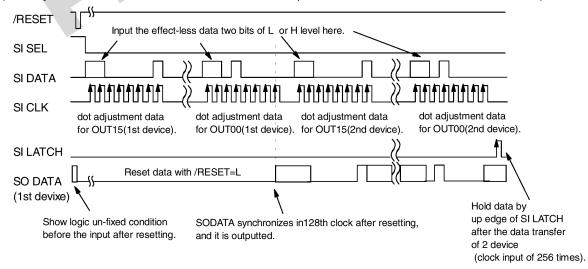

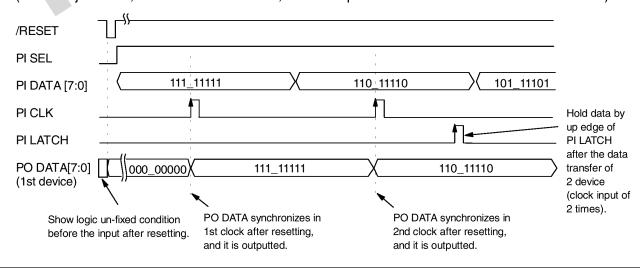

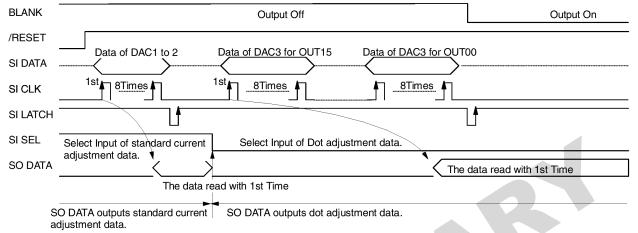

Figure 1-1: serial data transfer timing figure

Figure 1-2: serial data transfer timing figure (standard current adjustment, the case of SI SEL=H, for example of cascade connected of 2 devices.)

120 Broadway • Menands, New York 12204

## Operating explanation and truth value table (2/12 pages)

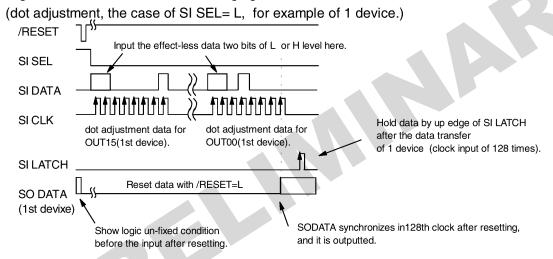

Serial data transfer: dot adjustment DAC4. (about the data register SI REG2[127:0])

|   | SI<br>DATA  | SI CLK | SI LATCH | SI SEL | SO<br>DATA                                                                                                                       | Operating and function                                                                                                           |

|---|-------------|--------|----------|--------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 1 | (128 times) |        | L        | H or L | Choose the input data of dot adjustment (128 bits) with SI SEL=L. Transfer data to SI REG2 by up edge 128 times input of SI CLK. |                                                                                                                                  |

| 2 | HorL        | L      | (1time)  | L      | No<br>Change                                                                                                                     | Hold the data transferred to SI REG2 by up edge of SI LATCH. Set is reflected on dot adjustment from the moment when it is held. |

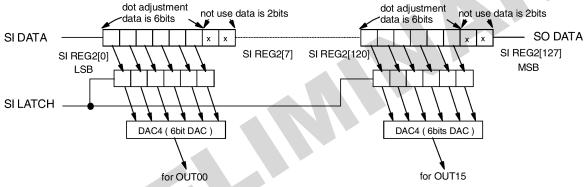

Figure 2-1: serial data transfer timing figure

Figure 2-2: serial data transfer timing figure

(dot adjustment, the case of SI SEL=L, for example of cascade connected of 2 devices.)

120 Broadway • Menands, New York 12204

Operating explanation and truth value table (3/12 pages)

**DAC1** Set details of standard current adjustment DAC1 (about data SIREG1[7:6])

| /RESET | SI<br>SEL | SI<br>REG<br>[7:6] | SI REG<br>[5:0] | Current<br>Rate | Operation and function                                            | Notes                                                                              |

|--------|-----------|--------------------|-----------------|-----------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Н      | н         | НН                 | xxxxxx          | 100[%]          | It is based on the current value set with REXT, and set in 100 %. | When SI SEL= H is chosen,<br>MSB sides 2 bits are<br>equivalent to set of standard |

| Н      | Н         | HL                 | xxxxx           | 75[%]           | It is set in the same way in 75 %.                                | current adjustment DAC1. Output current is set in 4 step.                          |

| Н      | Ι         | I                  | xxxxx           | 50[%]           | It is set in the same way in 50 %.                                |                                                                                    |

| Н      | Ι         | L                  | xxxxx           | 25[%]           | It is set in the same way in 25 %.                                |                                                                                    |

|        | Х         | LL                 | LLLLLL          | 25[%]           | Early condition after resetting is set by 25 %.                   |                                                                                    |

DAC2 Set details of standard current adjustment DAC2 (about data SIREG1[5:0])

| /RESET | SI<br>SEL | SI<br>REG<br>[7:6] | SI REG<br>[5:0]  | Current<br>Rate | Operation and function                                                    | Notes                                                                       |

|--------|-----------|--------------------|------------------|-----------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Н      | Н         | xx                 | ННННН<br>Н       | 100[%]          | It is based on the current value set with DAC1, and set in 100 %.         | When SI SEL= H is chosen,                                                   |

|        |           |                    | НННННЬ           | 99.0[%]         |                                                                           | LSB sides 6 bits are equivalent to set of standard current adjustment DAC2. |

| Н      | Н         | xx                 | to               | to              | Set 64 steps is possible from the current range 100 to 40%. (1LSB=0.95 %) | Output current is set in 64 step.                                           |

|        |           |                    | LLLLLH           | 40.9[%]         |                                                                           |                                                                             |

| Н      | Н         | xx                 | LLLLLL           | 40[%]           | It is set in the same way in 40 %.                                        |                                                                             |

|        | Х         | LL                 | LL LLLLLL 40 [%] |                 | Early condition after resetting is set by 40 %.                           |                                                                             |

120 Broadway • Menands, New York 12204

Operating explanation and truth value table (4/12 pages)

The polarity of the input serial data of standard current adjustment(SI REG1[7:0]) and dot adjustment(SI REG2[127:0])

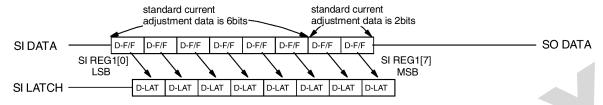

Figure 3-1: the case of serial data transfer timing figure

(SI SEL=H, select data input of standard current adjustment for DAC1 and DAC2)

Figure 3-2: the case of serial data transfer timing figure (SI SEL=L, select data input of dot adjustment for DAC4.)

DAC4 Set details of dot adjustment DAC4 (about data SIREG2[127:0])

| /RE<br>SE<br>T | SI<br>SE<br>L | DC<br>EN | About 8bits<br>unit of<br>SIREG2[127:0] | Current<br>Rate | Operation and function                                                   | Notes                                                                                                               |

|----------------|---------------|----------|-----------------------------------------|-----------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Н              | 4             | I        | ххнннннн                                | 100[%]          | It is based on the current value set with DAC1 to DAC3 and set in 100 %. | When SISEL= "L" is chosen,<br>8 bits out of 128 bits are equivalent to                                              |

|                |               |          | XXHHHHHL                                | 98.7[%]         | Set 64 steps is possible                                                 | set of each output, and the LSB sides 6 bits of 8 bits are data on dot adjustment.                                  |

| Н              | L             | Н        | to                                      | to              | from the current range<br>100 to 20%.<br>(1LSB=1.27 %)                   | Output current is set in 64 step.                                                                                   |

|                |               |          | XXLLLLLH                                | 21.3[%]         |                                                                          | SIREG2[7:0] -> adjustment data of OUT00. SIREG2[15:8]                                                               |

| Н              | L             | Н        | XXLLLLLL                                | 20[%]           | It is set in the same way in 20 %.                                       | -> adjustment data of OUT01. SIREG2[127:120]                                                                        |

| 7              | Х             | Н        | XXLLLLLL                                | 20[%]           | Early condition after resetting is set by 20 %.                          | -> adjustment data of OUT15.                                                                                        |

| Н              | X             | L        | ХХНННННН                                | 100[%]          | It is set in the same way in 100 %.                                      | Input of data is possible in the case of the DCEN=L level as well. Adjustment is done when it is made DCEN=H level. |

120 Broadway • Menands, New York 12204

## Operating explanation and truth value table (5/12 pages)

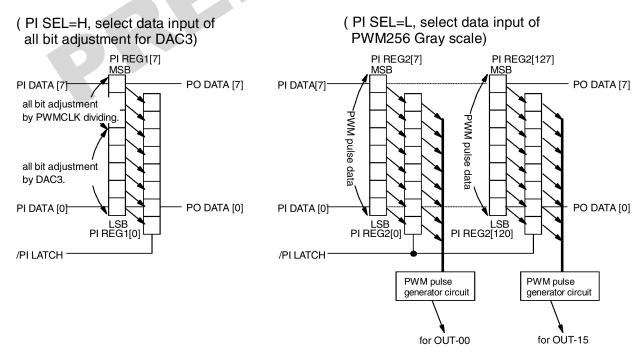

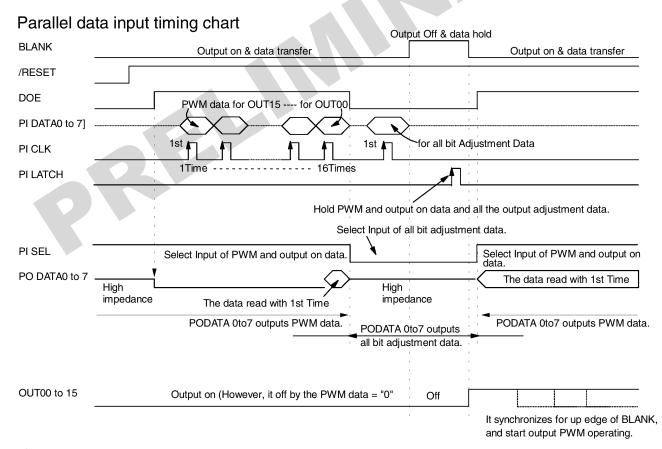

Pararell data transfer: all bit adjustment DAC3.

(about the data register PI REG1[7:0])

|   | PI DATA<br>[7:0] | PI CLK  | PI<br>LATCH | PI SEL | PO DATA<br>[7:0] | Operation and function                                                                                                                       |

|---|------------------|---------|-------------|--------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1 |                  | (1time) | L           | Н      | H or L           | Choose the input data of all bit adjustment (8bit, 5bit and 2bit) with PI SEL=H. Transfer data to PI REG1 by up edge 1 time input of PI CLK. |

| 2 | H or L           | L       | (1time)     | Н      | No<br>change     | Hold the data transferred to PI REG1 by up edge of PI LATCH. Set is reflected on all bit adjustment from the moment when it is held.         |

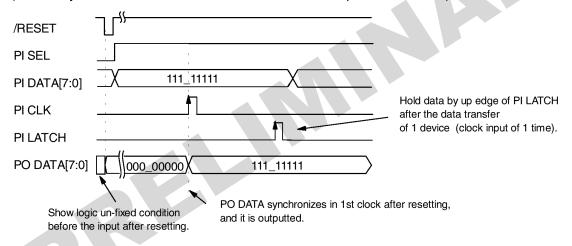

Figure 4-1: pararell data transfer timing figure (all bit adjustment, the case of PI SEL= H, for example of 1 device.)

Figure 4-2: pararell data transfer timing figure

(all bit adjustment, the case of PI SEL=H, for example of cascade connected of 2 devices.)

120 Broadway • Menands, New York 12204

Operating explanation and truth value table (6/12 pages)

Pararell data transfer: PMW 256 Gray Scale. (about the data register PI REG2[127:0])

|   | PI<br>DATA<br>[7:0] | PICLK     | PI<br>LATCH | PI SEL | PO<br>DATA<br>[7:0] | Operation and function                                                                                                                     |

|---|---------------------|-----------|-------------|--------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 1 |                     | (16times) | L           | L      | H or L              | Choose the input data of PWM 256 Gray scale (8bit X 16) with PI SEL=L. Transfer data to PI REG2 by up edge 16 times input of PI CLK.       |

| 2 | H or L              | L         | (1time)     | L      | No<br>change        | Hold the data transferred to PI REG2 by up edge of PI LATCH. Set is reflected on PWM 256 Gray scale from the next BLANK=L when it is held. |

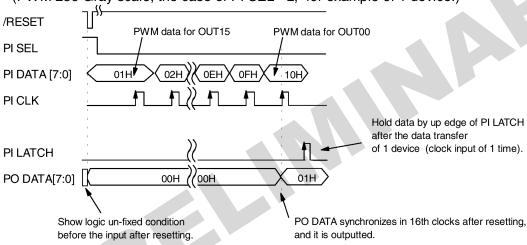

Figure 5-1: pararell data transfer timing figure

(PWM 256 Gray scale, the case of PI SEL= L, for example of 1 device.)

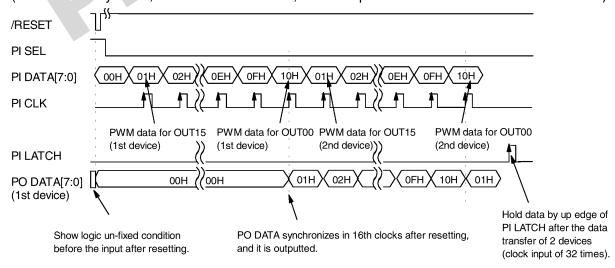

Figure 5-2: pararell data transfer timing figure

(PWM 256 Gray scale, the case of PI SEL= L, for example of cascade connected of 2 devices.)

120 Broadway • Menands, New York 12204

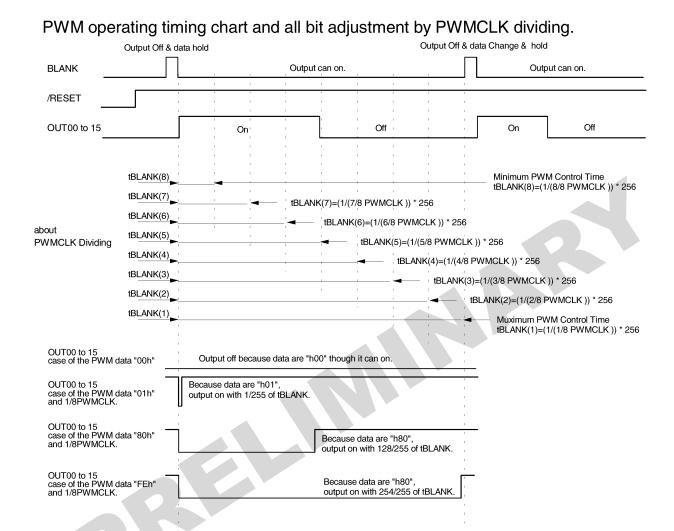

## Operating explanation and truth value table (7/12 pages)

Set details of all bit adjustment by PWMCLK dividing. ( about data PIREG1[7:5])

| /RE<br>SE<br>T | PI<br>SE<br>L | BC<br>EN | PI<br>REG1<br>[7:5] | PWMCLK<br>dividing rate       | Operation and function                                                                                | Notes                                                                                                                           |

|----------------|---------------|----------|---------------------|-------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Н              | Н             | Ι        | LLL                 | PWMCLK<br>=8/8PWMCLK          | The time width of 1 cycle of PWMCLK becomes the amount of change in pulse width of the PWM data 1LSB. | When PI SEL= H is chosen, MSB sides 3 bits are                                                                                  |

| Н              | I             | П        | to<br>HHL           | 7/8PWMCLK<br>to<br>2/8PWMCLK  | Variable does the frequency of PWMCLK to 1/8 of the minima. It is set in 8 step.                      | equivalent to set of all bit adjustment by PWMCLK dividing.  PIREG1[7:5] varies                                                 |

| Н              | Н             | I        | ННН                 | PWM CLK<br>=1/8PWMCLK<br>[Hz] | The time width of 8 cycle of PWMCLK becomes the amount of change in pulse width of the PWM data 1LSB. | the minimum pulse width of the PWM pulse output in 8 step. This set influences                                                  |

| T              | х             | Ι        | LLL                 | PWM CLK<br>=8/8PWM<br>CLK[Hz] | The time width of 1 cycle of PWMCLK becomes the amount of change in pulse width of the PWM data 1LSB. | all output.                                                                                                                     |

| н              | Н             | L        | xxx                 | It doesn't<br>influence it.   | It doesn't influence it.                                                                              | Input of data is possible in<br>the case of the BCEN=L<br>level as well. Adjustment is<br>done when it is made<br>BCEN=H level. |

## DAC3 Set details of all bit adjustment DAC3 (about data PI REG2[4:0])

| /RE<br>SET | PI<br>SEL | PI REG1<br>[4:0] | BC<br>EN | Current<br>Rate | Operation and function                                                          | Notes                                                                                                               |

|------------|-----------|------------------|----------|-----------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Н          | H         | ннннн            | Н        | 100[%]          | It is based on the current value set with DAC1 to DAC2 and set in 100 %.        | When PI SEL= "H" is chosen,                                                                                         |

|            |           | HHHHL            |          | 98.3[%]         |                                                                                 | LSB side 5 bits are equivalent to set of all bit adjustment, Output current is                                      |

| н          | Н         | to               | Н        | to              | Set 32 steps is possible from<br>the current range 100 to<br>50%. (1LSB=1.61 %) | set in 32 step.                                                                                                     |

|            |           | LLLLH            |          | 51.6[%]         |                                                                                 |                                                                                                                     |

| Н          | Н         | LLLLL            | Н        | 50[%]           | It is set in the same way in 50 %.                                              |                                                                                                                     |

| 7          | Х         | ННННН            | Η        | 100 [%]         | Early condition after resetting is set by 100 %.                                |                                                                                                                     |

| Н          | х         | ННННН            | L        | 100 [%]         | It is set in the same way in 100 %.                                             | Input of data is possible in the case of the BCEN=L level as well. Adjustment is done when it is made BCEN=H level. |

120 Broadway • Menands, New York 12204

## Operating explanation and truth value table (8/12 pages)

Set details of all PWM 256 Gray scale (about data PI REG2 [127:0], 8bit X 16)

| /RESE<br>T | PI SEL | 1words(8bit)<br>of PI REG2 | Outpiut<br>Pulse<br>Rate | Operation and function                                                              | Notes                                                                                                                                                              |

|------------|--------|----------------------------|--------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Н          | L      | ннннннн                    | 255/255                  | Output pulse width is muximum value when input data are "FF".                       | PISEL= "L" is chosen,<br>and PWM gray scale controls<br>output pulse width.                                                                                        |

| н          | L      | HHHHHHHL<br>to<br>LLLLLLLH | 254/255<br>to<br>1/255   | The PWM pulse control of 1 - 255 gray scale is possible by the input data.          | Transfer 1 word (eight bits) X 16 word as pararell data. 1 word is the PWM data of each Output pulse width is set in 256 step.  PI REG2[7:0] -> PWM data of OUT00. |

| Н          | L      | LLLLLLL                    | 0/255                    | It is output off when input data are "00".                                          | PIREG2[15:8]<br>-> PWM data of OUT01.<br>PIREG2[127:120]                                                                                                           |

| T          | х      | LLLLLLLL                   | 0/255                    | Early condition after<br>the reset signal input<br>is set in 0/255 (output<br>off). | -> PWM data of OUT15.  Output minimum pulse width is 1/PWMCLK.                                                                                                     |

The polarity of the input serial data of all bit adjustment(PI REG1[7:0]) and PWM256Gray sclae (PI REG2[127:0])

Figure 6-1: the case of Pararell data transfer timing figure

120 Broadway • Menands, New York 12204

## Operating explanation and truth value table (9/12 pages)

Reference table : output current set value (1)

| 1 10101                                |                                                  |                                                   | tput cu               |                                                | ot value                         | \''/          |          |          |                  |                                      |                  |

|----------------------------------------|--------------------------------------------------|---------------------------------------------------|-----------------------|------------------------------------------------|----------------------------------|---------------|----------|----------|------------------|--------------------------------------|------------------|

|                                        | DAC1                                             | (2 bit)                                           |                       | DAC2                                           | (6 bit)                          |               | DAC3     | (5bit)   |                  | DAC4                                 | (6bit)           |

| ٠.                                     | Input                                            | Current                                           |                       | Input                                          | Current                          |               | Input    | Current  |                  | Input                                | Current          |

| No                                     | Data                                             | rate1                                             | No                    | Data                                           | rate2                            | No            | Data     | rate3    | No               | Data                                 | rate4            |

| 3                                      | 11                                               | 1.00                                              | 63                    | 111111                                         | 1.000                            | 31            | **11111  | **1.000  | 63               | 111111                               | 63               |

| 2                                      | 10                                               | 0.75                                              | 62                    | 111110                                         | 0.990                            | 30            | 11110    | 0.984    | 62               | 111110                               | 62               |

|                                        |                                                  |                                                   |                       |                                                |                                  |               |          |          |                  |                                      |                  |

| 1                                      | 01                                               | 0.50                                              | 61                    | 111101                                         | 0.981                            | 29            | 11101    | 0.968    | 61               | 111101                               | 61               |

| 0                                      | **00                                             | **0.25                                            | 60                    | 111100                                         | 0.971                            | 28            | 11100    | 0.952    | 60               | 111100                               | 60               |

| ١                                      |                                                  |                                                   | 59                    | 111011                                         | 0.962                            | 27            | 11011    | 0.936    | 59               | 111011                               | 59               |

| /                                      |                                                  |                                                   | 58                    | 111010                                         | 0.952                            | 26            | 11010    | 0.919    | 58               | 111010                               | 58               |

| 1                                      |                                                  |                                                   | 57                    | 111001                                         | 0.943                            | 25            | 11001    | 0.903    | 57               | 111001                               | 57               |

| 1                                      |                                                  |                                                   | 56                    | 111000                                         | 0.933                            | 24            | 11000    | 0.887    | 56               | 111000                               | 56               |

| $\overline{}$                          | <b>-</b>                                         |                                                   | 55                    |                                                |                                  |               |          |          |                  |                                      |                  |

|                                        |                                                  |                                                   |                       | 110111                                         | 0.924                            | 23            | 10111    | 0.871    | 55               | 110111                               | 55               |

|                                        |                                                  |                                                   | 54                    | 110110                                         | 0.914                            | 22            | 10110    | 0.855    | 54               | 110110                               | 54               |

| 1                                      |                                                  |                                                   | 53                    | 110101                                         | 0.905                            | 21            | 10101    | 0.839    | 53               | 110101                               | 53               |

|                                        |                                                  |                                                   | 52                    | 110100                                         | 0.895                            | 20            | 10100    | 0.823    | 52               | 110100                               | 52               |

| 1                                      |                                                  |                                                   | 51                    | 110011                                         | 0.886                            | 19            | 10011    | 0.807    | 51               | 110011                               | 51               |

|                                        | <b>-</b>                                         |                                                   | 50                    | 110010                                         | 0.876                            | 18            | 10010    | 0.790    | 50               | 110010                               | 50               |

| <del>- \</del>                         |                                                  |                                                   |                       |                                                |                                  | 17            |          | 0.774    |                  | 110001                               |                  |

|                                        |                                                  |                                                   | 49                    | 110001                                         | 0.867                            |               | 10001    |          | 49               |                                      | 49               |

|                                        |                                                  |                                                   | 48                    | 110000                                         | 0.857                            | 16            | 10000    | 0.758    | 48               | 110000                               | 48               |

|                                        |                                                  |                                                   | 47                    | 101111                                         | 0.848                            | 15            | 01111    | 0.742    | 47               | 101111                               | 47               |

|                                        |                                                  |                                                   | 46                    | 101110                                         | 0.838                            | 14            | 01110    | 0.726    | 46               | 101110                               | 46               |

| \ \ \                                  |                                                  |                                                   | 45                    | 101101                                         | 0.829                            | 13            | 01101    | 0.710    | 45               | 101101                               | 45               |

| <del>\</del>                           | 1                                                |                                                   | 44                    | 101100                                         | 0.819                            | 12            | 01100    | 0.694    | 44               | 101100                               | 44               |

| $\overline{}$                          | <b> </b>                                         |                                                   | 43                    | 101101                                         | 0.820                            | 11            | 01011    | 0.677    | 43               | 101101                               | 43               |

| —————————————————————————————————————— | <b> </b>                                         |                                                   |                       |                                                |                                  |               |          |          |                  |                                      |                  |

|                                        | ļ                                                |                                                   | 42                    | 101010                                         | 0.800                            | 10            | 01010    | 0.661    | 42               | 101010                               | 42               |

|                                        |                                                  |                                                   | 41                    | 101001                                         | 0.791                            | 9             | 01001    | 0.645    | 41               | 101001                               | 41               |

|                                        | <b>l</b>                                         |                                                   | 40                    | 101000                                         | 0.781                            | 8             | 01000    | 0.629    | 40               | 101000                               | 40               |

|                                        | Ι\                                               |                                                   | 39                    | 100111                                         | 0.771                            | 7             | 00111    | 0.613    | 39               | 100111                               | 39               |

|                                        | l\                                               |                                                   | 38                    | 100110                                         | 0.762                            | 6             | 00110    | 0.597    | 38               | 100110                               | 38               |

|                                        | H                                                |                                                   | 37                    | 100101                                         | 0.752                            | 5             | 00101    | 0.581    | 37               | 100101                               | 37               |

|                                        | H                                                |                                                   |                       | 100101                                         |                                  |               |          |          |                  | 100101                               |                  |

|                                        | <del> </del>                                     |                                                   | 36                    |                                                | 0.743                            | 4             | 00100    | 0.565    | 36               |                                      | 36               |

|                                        |                                                  |                                                   | 35                    | 100011                                         | 0.733                            | 3             | 00011    | 0.549    | 35               | 100011                               | 35               |

|                                        | L \                                              |                                                   | 34                    | 100010                                         | 0.724                            | 2             | 00010    | 0.532    | 34               | 100010                               | 34               |

|                                        | l \                                              |                                                   | 33                    | 100001                                         | 0.714                            | 1             | 00001    | 0.516    | 33               | 100001                               | 33               |

|                                        |                                                  |                                                   | 32                    | 100000                                         | 0.705                            | 0             | 00000    | 0.500    | 32               | 100000                               | 32               |

|                                        |                                                  |                                                   | 31                    | 011111                                         | 0.695                            |               |          |          | 31               | 011111                               | 31               |

|                                        | $\vdash$                                         |                                                   | 30                    | 011110                                         | 0.686                            | \             |          |          | 30               | 011110                               | 30               |

|                                        |                                                  |                                                   |                       |                                                |                                  | <b>\</b>      |          |          |                  |                                      |                  |

|                                        | <del>                                     </del> |                                                   | 29                    | 011101                                         | 0.676                            |               |          |          | 29               | 011101                               | 29               |

|                                        | 1                                                |                                                   | 28                    | 011100                                         | 0.667                            |               |          |          | 28               | 011100                               | 28               |

|                                        | l \                                              |                                                   | 27                    | 011011                                         | 0.657                            | \             |          |          | 27               | 011011                               | 27               |

|                                        | \ \                                              |                                                   | 26                    | 011010                                         | 0.648                            |               |          |          | 26               | 011010                               | 26               |

|                                        |                                                  |                                                   | 25                    | 011001                                         | 0.638                            | \             |          |          | 25               | 011001                               | 25               |

|                                        |                                                  |                                                   | 24                    | 011001                                         | 0.629                            | <b>\</b>      |          |          | 24               | 011000                               | 24               |

|                                        |                                                  |                                                   |                       |                                                |                                  | $\vdash$      | <b>-</b> |          |                  |                                      |                  |