## CMOS SINGLE-COMPONENT 8-BIT MICROCOMPUTER

### FEATURES

- O Pin-to-pin compatible with intel's 80C48/80C35/80C49/80C39

- O 80C48/80C49 Low power mask programmable ROM.

- O 80C35/80C39 Low power, CPU only.

- 1.36 μsec instruction cycle.

All instruction 1 or 2 cycles.

- Ability to maintain operation during AC power line interruptions.

- O Exit idle mode with an external or internal interrupt signal.

- O Battery operation.

- O 3 power consumption selections

- ─ Normal operation: 12mA @ 11MHz @5V

- Idle mode

- : 4.8mA @ 11mHz @5V

- Power down : 2μA @2V

- O 80C49 is also available as a standard cell.

- 11MHz operation @5V ± 10%

## MAXIMUM RATINGS

- O Ambient temperature under bias

- O Storage temperature

- O Voltage on any pin with respect to ground

- O Maximum voltage on any pin with respect to ground

- O Power dissipation

: 0°C ~ + 70°C

: -65°C ~ + 150°C

: −0.5V~V<sub>cc</sub>+1V

: 7∨

: 1.5 Watt.

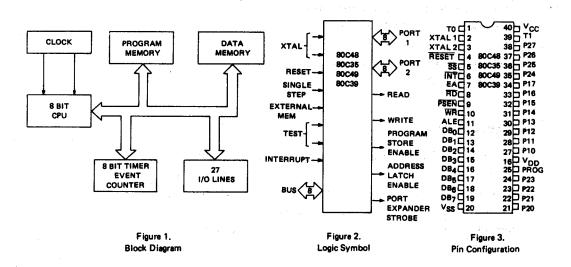

#### ☐ BLOCK DIAGRAM AND DESCRIPTION

DAEWOO ZyMOS TECHNOLOGY' 80C48/80C35/80C49/80C39 are low power, CHMOS version of the popular MCS-48 HMOS family members. CHMOS is a technology built on HMOS II and features high resistivity P substrate, diffused N well, and scaled N and P channel devices. The 80C48/80C35/80C49/80C39 have been designed to provide low power consumption and high performance.

The 80C48/80C49 contains a 1Kx8/2Kx8 program memory, a 64x8/128x8 RAM data memory, 27 I/O lines, and an 8bit timer/counter in addition to on-board oscillator and clock circuits. The 80C35/80C39 is the equivalent of the 80C48/80C49 without program memory on-board.

The CMOS design of the 80C48/80C49 opens new application areas that require battery operation, low power standby, wide voltage range, and the ability to maintain operation during AC power line interruptions.

These applications include portable and hand-held instruments, telecommunication consumer and automotive.

## ] PIN DESCRIPTION

| Symbol          | Pin No.  | Eurotion                         |

|-----------------|----------|----------------------------------|

| <u> </u>        |          | Function                         |

| Vss             | 20       | Circuit GND potential            |

| V <sub>DD</sub> | 26       | Low Power standby pin            |

| V <sub>cc</sub> | 40       | Main power supply; +5V dur-      |

|                 |          | ing operation                    |

| PROG            | 25       | Output strobe for 82C43 I/O      |

| 7. N. 1         |          | expander.                        |

| P10-P17         | 27-34    | 8-bit quasi-bidirectional port   |

| Port 1          |          | o pit quasi bidii ectional port  |

| P20-P23         | 21-24    | 8-bit quasi-bidirectional port   |

| P24-P27         | 35-38    | P20-P23 contain the four high    |

| Port 2          |          | order program counter bits       |

|                 |          | during an external program       |

|                 |          | memory fetch and serve as a      |

|                 |          | 4-bit I/O expander bus for       |

| the parties     | 30 51 19 | 8243.                            |

| DB0-DB7         | 12-19    | True bidirectional port which    |

| BUS             |          | can be written or read           |

| 16 × 25 5 5     | 1,000    | synchronously using the RD,      |

| 18 2 .          | P. P. J. | WR strobes. The port can also    |

|                 |          | be statically latched.           |

|                 |          |                                  |

|                 |          | Contains the 8 low order pro-    |

|                 |          | gram counter bits during an      |

|                 |          | external program memory          |

| *****           |          | fetch, and receives the          |

|                 |          | addressed instruction under      |

|                 |          | the control of PSEN. Also con-   |

|                 |          | tains the address and data dur-  |

|                 |          | ing an external RAM data         |

|                 |          | store instruction, under control |

|                 |          | of ALE, RD, and WR.              |

| T0              | 1        | Input pin testable using the     |

|                 |          | conditional transfer instruc-    |

| 1               | 1.1      | tions JT0 and JNT0. T0 can be    |

|                 |          | designated as a clock output     |

|                 |          | using ENTO CLK instuction.       |

|                 |          |                                  |

| L               | L        | <u> </u>                         |

| Symbol  | Pin No. | Function                              |

|---------|---------|---------------------------------------|

| T1      |         |                                       |

| 11.     | 39      | Input pin testable using the          |

| 1.      |         | JT1, and JNT1 instructions.           |

| . *     |         | Can be designated the timer/          |

|         |         | counter input using the STRT          |

|         |         | CNT instruction.                      |

| INT     | 6       | Interrupt input. Initiates an in-     |

|         |         | terrupt if interrupt is enabled.      |

|         |         | Interrupt is disabled after a         |

|         |         | reset. Also testable with condi-      |

|         |         | tional jump instruction.(Active       |

| # 15    | 100     | low)                                  |

|         |         | Interrupt must remain low for         |

|         |         | at least 3 machine cycles for         |

|         |         | proper operation.                     |

| RD      | 8       | Output strobe activated during        |

| 1       |         | a BUS read. Can be used to            |

|         |         | enable data onto toe bus from         |

| 1.74    | 1.50    | an external device.                   |

| 191     |         | Used as a read strobe to ex-          |

|         |         | ternal data memory.                   |

|         |         | (Active low)                          |

| RESET   | 4       | Input which is used to initialize     |

|         |         | the processor.                        |

|         |         | (Active low) (Non TTL VIH)            |

| WR      | 10      | Ouput strobe during a bus             |

|         |         | write.(Active low)                    |

|         |         | Used as write strobe to exter-        |

| 1       |         | nal data memory.                      |

| ALE     | 11      | Address latch enable. This sig-       |

| - Vinda | ''      | nal occurs once during each           |

|         |         | cycle and is useful as a clock        |

|         |         | output.                               |

|         | e trans | · · · · · · · · · · · · · · · · · · · |

|         | 1       | The negative edge of ALE              |

|         |         | strobes address into external         |

| -       |         | data and program memory.              |

| PSEN    | 9       | Program store enable. This            |

|         |         | output occurs only during             |

## **DMC 80C49**

### PIN DESCRIPTION(Continued)

| Symbol  | Pin No. | Function                                                                                                                     |  |

|---------|---------|------------------------------------------------------------------------------------------------------------------------------|--|

| PSEN    |         | a fetch to external program                                                                                                  |  |

| (Con't) | -       | memory.(Actibe low)                                                                                                          |  |

| SS      | 5       | Single step input can be used in conjunction with ALE to "single step" the processor through each instruction.  (Active low) |  |

| EA      | 7       | External access input which forces all program memory fetches to reference external                                          |  |

| Symbol | Pin No. | Function                          |

|--------|---------|-----------------------------------|

|        |         | memory. Useful for emulation      |

|        |         | and debug, and essential for      |

|        | -       | testing and program verifica-     |

|        |         | tion.(Active high)                |

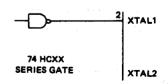

| XTAL1  | 2       | One side of crystal input for in- |

|        | -       | ternal oscillator. Also input for |

|        |         | external source.                  |

|        |         | (Non TTL V <sub>IH</sub> )        |

| XTAL2  | 3       | Other side of crystal input.      |

|        |         |                                   |

#### IDLE MODE DESCRIPTION

The 80C48/80C35/80C49/80C39, when placed in idle mode, keeps the oscillator, the internal timer and the external interrupt and counter pins functioning, and maintains the internal register and RAM status.

To place the 80C48/80C35/80C49/80C39 in idle mode, a command instruction(op code 01H) is executed. To terminate idle mode, a reset must be performed or interrupts must be enabled and an interrupt signal generated.

There are two interrupt sources that can restore normal operation.

One is an external signal applied to the interrupt pin. The other is form the overflow of the timer/counter. When either interrupt is invoked, the CPU is taken out of Idle mode and vectors to the interrupt's service routine address.

Along with the idle mode, the standard MCS-48 power-down mode is still maintained. During normal operation,  $V_{CC}$  serves as the 5V supply pin for the bulk of the circuitry while the  $V_{DD}$  pin supplies only the RAM array.

In normal operation both  $V_{cc}$  and  $V_{DD}$  are at 5V. However, for power-down operation,  $V_{cc}$  is at ground and  $V_{DD}$  is reduced to its standby value.

To be certain that RAM is not inadvertently accessed and altered during power down, reset should be applied to the processor until  $V_{cc}$  is at ground level.

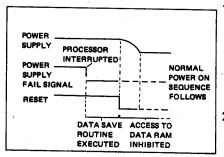

#### POWER DOWN MODE DESCRIPTION

Extra circuitry has been added to the 80C48/80C49 ROM version to allow power to be removed from all but the data RAM array for low power standby operation. In the power down mode the contents of data RAM can be maintained while drawing typically 10% to 15% of normal operating power requirements.

$V_{cc}$  serves as the 5V supply pin for the bulk of circuitry while the  $V_{DD}$  pin supplies only the RAM array. In normal operation both pins are a 5V while in standby,  $V_{cc}$  is at ground and  $V_{DD}$  is maintained at its standby value. Applying Reset to the processor through the  $\overline{RESET}$  pin inhibits any access to the RAM by the processor and guarantees that RAM cannot be inadvertently altered as power is removed from  $V_{cc}$ .

#### A typical power down sequence occurs as follows:

- Imminent power supply failure is detected by user defined circuitry.

- Signal must be early enough to allow 80C48 to save all necessary data before  $V_{\rm CC}$  falls below normal operating limits.

- Power fail signal is used to interrupt processor and vector it to a power fail service routine.

- 3) Power fail routine saves all important data and machine status in the internal data RAM array. Routine may also initiate transfer of backup supply to the V<sub>DD</sub> pin and indicate to external circuitry that power fail routine is complete.

- 4) Reset is applied to guarantee data will not be altered as the power supply falls out of limits.

Reset must be held how until  $V_{cc}$  is at ground level.

## ☐ INSTRUCTION SET

| Accumulator    |                         |       |        |

|----------------|-------------------------|-------|--------|

| Mnemonic       | Description             | Bytes | Cycles |

| ADD A, R       | Add register to A       | , 1   | 1      |

| ADD A, @R      | Add data memory to A    | 1     | 1      |

| ADD A, #data   | Add immediate to A      | 2     | 2      |

| ADDC A, R      | Add register with carry | 1     | 1      |

| ADDC A, @R     | Add data memory         | 1     | 1 :    |

|                | with carry              |       |        |

| ADDC A, #data  | Add immediate with      | 2     | 2      |

|                | carry                   |       |        |

| ANLA,R         | And register to A       | 1     | 1      |

| ANL A, @R      | And data memory to A    | 1     | 1      |

| ANL A, # data  | And immediate to A      | 2     | 2      |

| ORL A, R       | Or register to A        | 1     | 1      |

| ORL A, @R      | Or data memory to A     | 1     | 1      |

| ORLA,# data    | Or immediate to A       | 2     | 2      |

| XRL A, R       | Exclusive or register   | 1     | 1      |

|                | to A                    |       |        |

| XRL A, @R      | Exclusive or data       | 1     | 1      |

|                | memory to A             |       |        |

| XRL. A, # data | Exclusive or            | 2     | . 2    |

|                | immediate to A          |       |        |

| INC A          | Increment A             | 1     | 1      |

| DEC A          | Decrement A             | 1     | 1      |

| CLR A          | Clear A                 | 1     | 1      |

| CPL A          | Complement A            | 1     | 1      |

| DA A           | Decimal adjust A        | 1     | 1 .    |

| SWAP A         | Swap nibbles of A       | 1     | 1      |

| RLA            | Rotate A left           | 1     | 1      |

| RLC A          | Rotate A left           | 1     | 1      |

| ,              | through carry           |       |        |

| RR A           | Rotate A right          | 1     | 1      |

| RRC A          | Rotate A right          | 1     | 1      |

|                | through carry           |       |        |

| Input/Output  |                       |       |        |  |

|---------------|-----------------------|-------|--------|--|

| Mnemonic      | Description           | Bytes | Cycles |  |

| IN A, P       | Input port to A       | 1     | 2      |  |

| OUTL P, A     | Output A to port      | 1     | 2      |  |

| ANL P, # data | And immediate to port | 2     | 2      |  |

| ORL P, # data | Or immediate to port  | 2     | 2      |  |

| INS A, BUS    | Input BUS to A        | 1     | 2      |  |

| OUTL BUS, A   | Output A to BUS       | 1     | 2      |  |

| ANL BUS,      | And immediate to      | 2     | 2      |  |

| # data        | BUS                   |       |        |  |

| Mnemonic           | Description               | Bytes | Cycle |

|--------------------|---------------------------|-------|-------|

| ORL BUS,<br># dats | Or immediate to BUS       | 2     | 2     |

| MOVD A, P          | Input expender port to A  | 1     | 2     |

| MOVD P, A          | Output A to expander port | . 1   | 2     |

| ANLD P, A          | And A to expander port    | 1     | 2     |

| ORLD P, A          | Or A to expander port     | . 1   | 2     |

| Registers |                    |       |       |

|-----------|--------------------|-------|-------|

| Mnemonic  | Description        | Bytes | Cycle |

| INC R     | Increment register | 1     | 1     |

| INC @R    | Increment data     | 1     | 1     |

|           | memory             |       |       |

| DEC R     | Decrement register | 1     | 1     |

| Branch       |                     |       |       |

|--------------|---------------------|-------|-------|

| Mnemonic     | Description         | Bytes | Cycle |

| JMP addr     | Jump unconditional  | 2     | 2     |

| JMPP @A      | Jump indirect       | 1     | 2     |

| DJNZ R, addr | Decrement register  | 2     | 2     |

|              | and skip            |       |       |

| JC addr      | Jump on carry = 1   | 2     | 2     |

| JNC addr     | Jump on carry = 0   | 2     | 2     |

| JZ addr      | Jump on A zero      | 2     | 2     |

| JNZ addr     | Jump on A not zero  | 2     | 2     |

| JT0 addr     | Jump on TO = 1      | 2     | 2     |

| JNT0 addr    | Jump on TO = 0      | 2     | 2     |

| JT1 addr     | Jump on T1 = 1      | 2     | 2     |

| JNT1 addr    | Jump on T1 = 0      | 2     | 2     |

| JF0 addr     | Jump on F0 = 1      | 2     | 2     |

| JF1 addr     | Jump on F1 = 1      | 2     | 2     |

| JTF addr     | Jump on timer flag  | 2     | 2     |

| JN1 addr     | Jump on INT = 0     | 2     | 2     |

| JBb addr     | Jump on accumulator | 2.    | 2     |

|              | bit                 |       |       |

| Subroutine |                    |       |       |

|------------|--------------------|-------|-------|

| Mnemonic   | Description        | Bytes | Cycle |

| CALL addr  | Jump to subroutine | 2     | 2     |

## INSTRUCTION SET (Continued)

| Subroutine (C | Con't)             |       |        |

|---------------|--------------------|-------|--------|

| Mnemonic      | Description        | Bytes | Cycles |

| RET           | Return             | 1     | 2      |

| RETR          | Return and restore | 1     | 2      |

|               | status             |       |        |

| Flags    |                   |       |        |

|----------|-------------------|-------|--------|

| Mnemonic | Description       | Bytes | Cycle# |

| CLR C    | Clear carry       | 1     | 1      |

| CPL C    | Complement carry  | 1     | 1      |

| CLR FO   | Clear flag 0      | 1     | 1      |

| CPL FO   | Complement flag 0 | 1     | 1      |

| CLR F1   | Clear flag 1      | 1     | 1      |

| CPL F1   | Complement flag 1 | 1     | . 1    |

| Data Moves        | ,                                 |       |        |

|-------------------|-----------------------------------|-------|--------|

| Mnemonic          | Description                       | Bytes | Cycles |

| MOV A, R          | Move register to A                | 1     | 1      |

| MOV A, @R         | Move data memory<br>to A          | 1     | 1      |

| MOV A, # data     | Move immediate to A               | 2     | 2      |

| MOV R, A          | Move A to register                | 1     | 1      |

| MOV @R, A         | Move A to data<br>memory          | 1     | 1      |

| MOV R, # deta     | Move immediate to register        | 2     | 2      |

| MOV @R, # data    | Move immediate to data memory     | 2     | 2      |

| MOV A, PSW        | Move PSW to A                     | 1     | 1      |

| MOV PSW, A        | Move A to PSW                     | 1     | 1      |

| XCH A, R          | Exchange A and register           | 1     | 1      |

| XCH A, <b>⊕</b> R | Exchange A and data memory        | 1     | 1      |

| XCHD A, @R        | Exchange nibble of A and register | 1     | 1      |

| MOVX A, @R        | Move external data<br>memory to A | 1     | 2      |

| MOVX @R, A        | Move A to external data memory    | 1     | 2      |

| MOVP A, @A        | Move to A from<br>current page    | 1     | 2      |

| MOVP3 A, @        | Move to A from page 3             | 1     | 2      |

| Timer/Counter |                                 |       |        |

|---------------|---------------------------------|-------|--------|

| Mnemonic      | Description ,                   | Bytes | Cycles |

| MOV A, T      | Read timer/counter              | 1.    | 1      |

| MOV T, A      | Load timer/counter              | . 1   | 1      |

| STRTT         | Start timer                     | 1     | 1      |

| STRT CNT      | Start timer                     | 1     | 1      |

| STOP TONT     | Stop timer/counter              | 1     | 1      |

| EN TONTI      | Enable timer/counter interrupt  | 1     | 1      |

| DIS TONTI     | Disable timer/counter interrupt | 1     | 1      |

| Control  |                              |       |        |

|----------|------------------------------|-------|--------|

| Mnemonic | Description                  | Bytes | Cycles |

| EN I     | Enable external              | . 1   | 1      |

|          | interrupt                    |       |        |

| DISI     | Disable external             | 1     | 1      |

|          | interrupt                    |       |        |

| SEL RBO  | Select register bank 0       | 1     | 1      |

| SEL RB1  | Select register bank 1       | 1     | 1      |

| SEL MBO  | Select memory bank 0         | 1     | 1      |

| SEL MB1  | Select memory bank 1         | 1.    | 1 .    |

| ENTO CLK | Enable clock output<br>on T0 | 1     | 1      |

| Mnemonic | Description           | Bytes | Cycles |

|----------|-----------------------|-------|--------|

| NOP      | No operation          | 1     | 1      |

| IDL      | Select Idle Operation | 1     | 1      |

# IDMC 80C491

## ☐ ELECTRICAL CHARACTERISTICS(D.C)

$(T_A=0\sim70^{\circ}C, V_{CC}=V_{DD}=5V\pm10\%, IV_{CC}-V_{DD}I\leq1V, V_{SS}=0V$

| Symbol           | Parameter                          | Limits              |      |                     | 11.24 | T O                                               |  |

|------------------|------------------------------------|---------------------|------|---------------------|-------|---------------------------------------------------|--|

|                  |                                    | Min.                | Typ. | Max.                | Unit  | Test Conditions                                   |  |

| V <sub>IL</sub>  | Input Low Voltage                  | -0.5                |      | 0.18V <sub>cc</sub> | V     |                                                   |  |

|                  | (All Except X1, RESET)             | :                   |      |                     |       | +                                                 |  |

| VILI             | Input Low Voltage X1, RESET        | -5                  |      | 0.13V <sub>cc</sub> | ٧     |                                                   |  |

| VIH              | Input High Voltage                 | 2                   |      | V <sub>cc</sub>     | V     |                                                   |  |

|                  | (All Except XTAL1, RESET)          |                     |      |                     |       |                                                   |  |

| Villi            | Input High Voltage(X1, RESET)      | 0.7V <sub>cc</sub>  |      | Vα                  | ٧     |                                                   |  |

| V <sub>OL</sub>  | Output Low Voltage(BUS)            |                     |      | 0.45                | ٧     | I <sub>OL</sub> =2mA                              |  |

| V <sub>OL1</sub> | Output Low Voltage                 |                     |      | 0.45                | ٧     | I <sub>OL</sub> =1.8mA                            |  |

|                  | (RD, WR, PSEN, ALE)                |                     |      |                     |       |                                                   |  |

| V <sub>OL2</sub> | Output Low Voltage(PROG)           |                     |      | 0.45                | ٧     | I <sub>ot.</sub> = 1mA                            |  |

| V <sub>OL3</sub> | Output Low Voltage                 |                     |      | 0.45                | ٧     | I <sub>ot</sub> = 1.6mA                           |  |

|                  | (All Other Outputs)                |                     |      |                     |       |                                                   |  |

| V <sub>oH</sub>  | Output High Voltage(BUS)           | 0.75V <sub>cc</sub> |      |                     | V     | $I_{OH} = -400 \mu A$                             |  |

| Vohi             | Output High Voltage                | 2.4                 |      |                     | V     | $I_{OH} = -20\mu A$                               |  |

|                  | (RD, WR, PSEN, ALE)                |                     |      |                     |       |                                                   |  |

| $V_{OH2}$        | Output High Voltage                | 0.75V <sub>cc</sub> |      |                     | V     | $I_{OH} = -40 \mu A$                              |  |

|                  | (All Other Outputs)                |                     |      |                     | -     |                                                   |  |

| LI               | Input Leakage Current(T1, INT, EA) |                     |      | ±5                  | μА    | $V_{SS} \leq V_{IN} \leq V_{CC}$                  |  |

| l <sub>ւո</sub>  | Input Leakage Current              |                     |      | -500                | μА    | V <sub>SS</sub> ≦V <sub>IN</sub> ≤V <sub>CC</sub> |  |

|                  | (P10-P17, P20-27, <del>SS</del> )  |                     |      |                     |       |                                                   |  |

| LO               | Output Leakage Current(BUS, TO)    |                     |      | ±5                  | μА    | $V_{SS} \leq V_{IN} \leq V_{CC}$                  |  |

|                  | (High Impedance State)             |                     |      |                     |       |                                                   |  |

| LR               | Input Leakage Current(RESET)       | -20                 |      | -300                | μΑ    | $V_{SS} \leq V_{IN} \leq V_{CC}$                  |  |

| PD               | Power Down Standby Current         |                     |      | 2                   | μА    | V <sub>DD</sub> =2V RESET                         |  |

|                  |                                    |                     |      |                     |       | ≤V <sub>II</sub>                                  |  |

## $I_{CC}$ Active Current(mA)

| Vcc   | 4.5∨ | 5V  | 5.5∨ |

|-------|------|-----|------|

| 1MHz  | 2.5  | 3.3 | 4    |

| 6MHz  | 5    | 6.8 | 8.5  |

| 11MHz | 9    | 12  | 15   |

| $V_{cc}$ | 4.5∨ 5∨ |     | 5.5∨ |

|----------|---------|-----|------|

| 1MHz     | 1.7     | 2   | 2.2  |

| 6MHz     | 2       | 3   | 4    |

| 11MHz    | 3.5     | 4.8 | 6    |

Absolute Maximum Unloaded Current

## DMC 80C49

## ☐ ELECTRICAL CHARACTERISTICS(A.C)

$(T_A=0\sim70^{\circ}C,\ V_{CC}=V_{DD}=5V\pm10\%,\ |V_{CC}-V_{DD}|\leq1V,\ V_{SS}=0V)$

| Symbol                 | Parameter                    | f(t)         | 111  | 11MHz |      | Conditions |

|------------------------|------------------------------|--------------|------|-------|------|------------|

|                        |                              | (Note 3)     | Min. | Max.  | Unit | (Note 1)   |

| t                      | Clock Period                 | 1/xtal freq. | 90.9 | 1000  | ns   | (Note 3)   |

| t <sub>LL</sub>        | ALE Pulse Width              | 3.5t-170     | 150  |       | ns   |            |

| t <sub>AL</sub>        | Addr Setup to ALE            | 2t-110       | 70   |       | ns   | (Note 2)   |

| t <sub>LA</sub>        | Addr Hold from ALE           | t-40         | 50   |       | ns   |            |

| t <sub>CC1</sub>       | Control Pulse Width(RD, WR)  | 7.5t-200     | 480  |       | ns   |            |

| t <sub>CC2</sub>       | Control Pulse Width(PSEN)    | 6t-200       | 350  |       | ns   |            |

| t <sub>DW</sub>        | DAta Setup before WR         | 6.5t-200     | 390  |       | ns   |            |

| t <sub>WD</sub>        | Data Hold after WR           | t-50         | 40   |       | ns   |            |

| t <sub>DR</sub>        | Data Hold(RD, PSEN)          | 1.5t-30      | 0    | 110   | ns   |            |

| t <sub>RD1</sub>       | RD to Data in                | 6t-170       |      | 350   | ns   |            |

| t <sub>RD2</sub>       | PSEN to Data in              | 4.5t-170     |      | 190   | ns   |            |

| t <sub>AW</sub>        | Addr Setup to WR             | 5t-150       | 300  |       | ns   |            |

| t <sub>AD1</sub>       | Addr Setup to Data(RD)       | 10.5t-220    |      | 730   | ns   |            |

| t <sub>AD2</sub>       | Addr Setup to Data(PSEN)     | 7.5t-220     |      | 460   | ns   |            |

| t <sub>APC1</sub>      | Addr Float to RD, WR         | 2t-40        | 140  |       | ns   | (Note 2)   |

| t <sub>AFC2</sub>      | Addr Float to PSEN           | 0.5t-40      | 10   |       | ns   | (Note 2)   |

| t <sub>i.AFC1</sub>    | ALE to Control(RD, WR)       | 3t-75        | 200  |       | ns   | ``         |

| t <sub>LAFC2</sub>     | ALE to Control(PSEN)         | 1.5t-75      | 60   |       | ns   |            |

| t <sub>CAI</sub>       | Control to ALE(RD, WR, PROG) | t-40         | 50   |       | ns   |            |

| t <sub>CA2</sub>       | Control to ALE(PSEN)         | 4t-40        | 320  |       | ns   |            |

| <b>t</b> <sub>CP</sub> | Port Control Setup to PROG   | 1.5t-80      | 50   |       | ns   |            |

| <b>t</b> <sub>PC</sub> | Port Control Hold to PROG    | 4t-260       | 100  |       | ns   |            |

| t <sub>PR</sub>        | PROG to P2 Input Valid       | 8.5t-120     |      | 650   | ns   |            |

| <b>t</b> <sub>PF</sub> | Input Data Hold from PROG    | 1.5t         | 0    | 140   | ns   |            |

| t <sub>DP</sub>        | Output Data Setup            | 6t-290       | 250  |       | ns   |            |

| t <sub>PD</sub>        | Output Data Hold             | 1.5t-90      | 40   |       | ns   |            |

| <b>t</b> pp            | PROG Pulse Width             | 10.5t-250    | 700  |       | ns   |            |

| t <sub>PL</sub>        | Port 2 I/O Setup to ALE      | 4t-200       | 160  |       | ns   |            |

| <b>t</b> <sub>LP</sub> | Port 2 I/O Hold to ALE       | 1.5t-120     | 15   |       | ns   |            |

| t <sub>PV</sub>        | Port Output from ALE         | 4.5t + 100   |      | 510   | ns   |            |

| toper                  | T0 Rep Rate                  | 3t           | 270  |       | ns   |            |

| t <sub>CY</sub>        | Cycle Time                   | 15t          | 1.36 | 15    | μS   | -          |

Note : 1. Control output  $C_L\!=\!80 pF$ , Bus outputs  $C_L\!=\!150 pF$

2. Bus high impedance Load 20pf

3. f(t) assumes 50% duty cycle on X1, X2 Max. clock period is for a 1MHz crystal input.

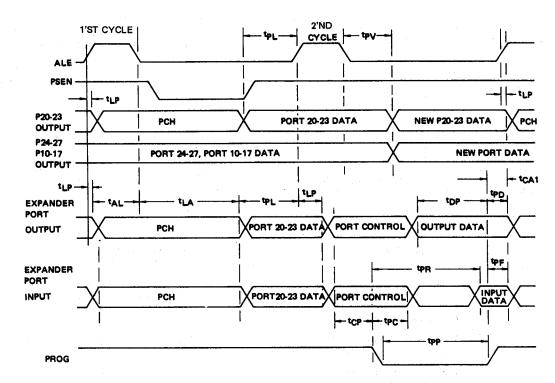

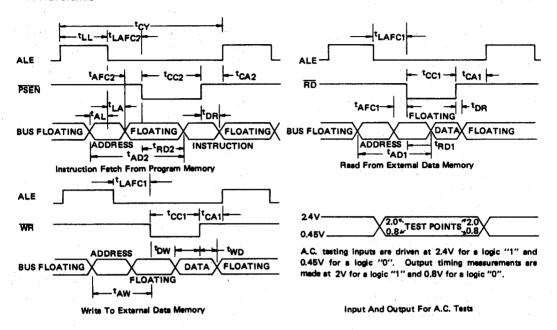

#### ☐ TIMING DIAGRAM

#### Waveforms

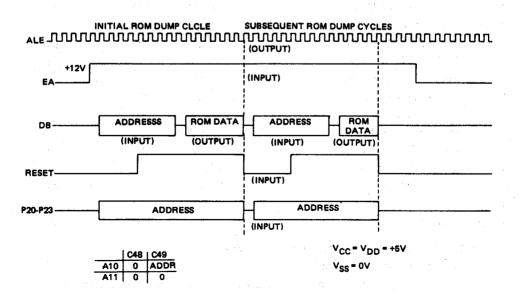

#### Suggested ROM verification algorithm for CMOS devices only

## DMC 80C49

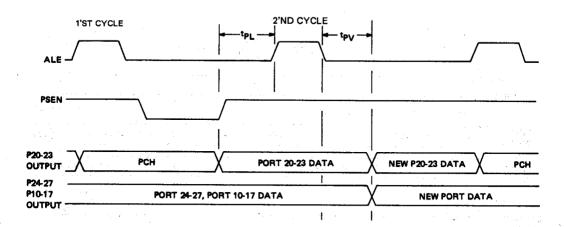

### ☐ TIMING DIAGRAM(Continued)

O I/O Port timing

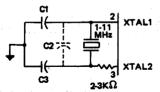

#### OSCILLATOR MODE

C1 = 20pF ± 2pF - STRAY < 5pF

C2 = CRYSTAL - STRAY < 8pF

C3 = 20pF ± 2pF - STRAY <5pF

Crystal series resistance should be less than  $30\Omega$  at 11 MHz; less than  $75\Omega$  at 6 MHz; less than  $180\Omega$  at 3.6 MHz.

XTAL1 must be high 35-65% of the period.

Rise and fall times must not be slower than 20 nS.

# IDMC 80C49

### TIMING DIAGRAM(Continued)

O Port 1/Port 2 timing