Dual Watchdog Timers

# HITACHI

The HA16113FPJ is a multifunction device that provides microprocessor systems with the necessary regulated power supply, monitors the supply voltage, and generates power-on reset and watchdog reset signals. It is ideally suited for battery-operated systems such as instrumentation systems.

#### Functions

- Regulated power supply

- Power-on reset

- Two built-in auto-reset circuits

- Two built-in watchdog timer circuits (WDT)

- Output voltage monitoring (LVI)

#### Features

- Simultaneous or independent control of auto-reset outputs.

- Precisely regulated output voltage and accurate  $\overline{\text{NMI}}$  trigger voltage (both  $\pm 2\%$ ).

- Low-voltage control with  $\overline{\text{NMI}}$ , simultaneous  $\overline{\text{RES1}}$  and  $\overline{\text{RES2}}$ , and  $\overline{\text{STBY}}$  outputs.

- Independently selectable durations for power-on reset and auto-reset: power-on duration is common to both reset outputs; auto-reset durations can be selected independently.

- Reset command input pin  $(\overline{\text{CONT}})$  for second reset output  $(\overline{\text{RES2}})$ .

- WDT filter function detects minimum pulse width and maximum period of P-RUN input pulses.

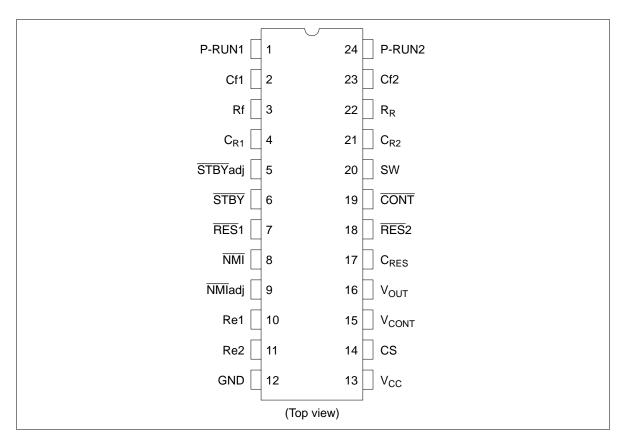

#### **Pin Arrangement**

#### **Pin Description**

| Pin No. | Symbol          | Function                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | P-RUN1          | Input from main CPU to watchdog timer 1 (WDT1)                                                                                                                                                                                                                                                                                                                                                                                  |

| 2       | Cf1             | For connecting capacitor Cf1 to determine WDT1 filter characteristic (frequency band)                                                                                                                                                                                                                                                                                                                                           |

| 3       | Rf              | For connecting common bias resistor Rf to determine WDT1 and WDT2 filter characteristics (frequency band), power-on reset time ( $t_{on}$ , common to RES1 and RES2), clock-off time of auto-reset circuits 1 and 2, reset high time ( $t_{RH1}$ and $t_{RH2}$ ),reset low time ( $t_{RL1}$ and $t_{RL2}$ ), and reset pulse delay at voltage drop and recovery. Use the resistor value from 100 k $\Omega$ to 500 k $\Omega$ . |

| 4       | C <sub>R1</sub> | For connecting capacitor $C_{R1}$ to determine $t_{on}$ for power-on reset and $t_{off1}$ , $t_{RH1}$ , and $t_{RL1}$ of auto-reset circuit 1.                                                                                                                                                                                                                                                                                  |

| 5       | STBY adj        | For adjusting standby trigger voltage (insert a resistor between this pin and ground) Recommended range: $V_{H2}$ = 2.8 to 4.0 V                                                                                                                                                                                                                                                                                                |

| 6       | STBY            | Standby signal output                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7       | RES1            | Reset signal output to main CPU                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8       | NMI             | Low-voltage interrupt signal output for memory backup                                                                                                                                                                                                                                                                                                                                                                           |

## **Pin Description** (cont)

| pin and Vout or ground)<br>Recommended range: V <sub>H1</sub> = 4.4 to 5.2 V10Re111For connecting resistor Re1 to determine voltage Vout for microprocessor and I<br>internal circuits (insert between this pin and Re2)11Re212GND13V <sub>cc</sub> 14CS15V <sub>c</sub> 16Vout for detecting power supply current15V <sub>c</sub> 16Vout17Regulated voltage supplied to microprocessor and IC internal circuits Connect to<br>collector of external pnp transistor16Vout17C <sub>RES</sub> 18Determines reset pulse delay at voltage drop and recovery. IMI output goes low<br>soon as Vout drops below IMI trigger level. If Yout remains below this level for<br>taces, both reset outputs also go low. When Vout recovers above IMI trigger level<br>NMI output goes low<br>soon as Vout drops below IMI trigger level. If yout remains below this level for<br>taces, both reset outputs also go high. Times t<br>t, are adjusted by capacitor C <sub>RES</sub> inserted between this pin and ground.18RES220SWSelects simultaneous control, in which main and sub CPU save both reset wher<br>CPU crashes, or independent control, in which sub CPU is reset independently<br>main CPU<br>Open—independent control; connected to ground—simultaneous control21C <sub>R2</sub> For connecting capacitor C <sub>R2</sub> to determine t <sub>off2</sub> , t <sub>RH2</sub> , and t <sub>RL2</sub> of auto-reset circuit f<br>2222R <sub>R</sub> For connecting capacitor C <sub>R2</sub> to determine t <sub>off2</sub> , t <sub>RH2</sub> , t <sub>RH2</sub> , t <sub>RL1</sub> , and t <sub>RL2</sub> . Use<br>resistor value from 100 kΩ to 500 kΩ.23Cf2For connecting capacitor Cf2 to determine WDT2 fil | Pin No. | Symbol           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| internal circuits (insert between this pin and Re2)         11       Re2       For connecting resistor Re2 to determine voltage Vout for microprocessor and I internal circuits (insert between this pin and ground)         12       GND       Ground         13       V <sub>cc</sub> Power supply input pin (operating range: 6 to 40 V)         14       CS       Input for detecting power supply current         15       V <sub>c</sub> For base control of external pnp transistor         16       Vout       Regulated voltage supplied to microprocessor and IC internal circuits Connect to collector of external pnp transistor         17       C <sub>RES</sub> Determines reset pulse delay at voltage drop and recovery. NMI output goes low soon as Vout drops below NMI trigger level. If Vout remains below this level for transis both reset outputs also go low. When Vout recovers above NMI trigger leve NMI output goes high, then after time t, both reset outputs also go high. Times t t, are adjusted by capacitor C <sub>RES</sub> inserted between this pin and ground.         18       RES2       Reset signal output to sub CPU         19       CONT       Input pin for resetting sub CPU on command, or when sub CPU sare both reset wher CPU crashes, or independent control, in which main and sub CPUs are both reset wher CPU crashes, or independent control, in which sub CPU is reset independently main CPU         20       SW       Selects simultaneous control, connected to ground—simultaneous control         21       C <sub>R2</sub> For connecting capacitor                                                                                               | 9       | NMI adj          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| internal circuits (insert between this pin and ground)         12       GND         13       V <sub>cc</sub> Power supply input pin (operating range: 6 to 40 V)         14       CS         15       V <sub>c</sub> For base control of external pnp transistor         16       Vout         Regulated voltage supplied to microprocessor and IC internal circuits Connect to collector of external pnp transistor         17       C <sub>RES</sub> Determines reset pulse delay at voltage drop and recovery. NMI output goes low soon as Vout drops below NMI trigger level. If Vout remains below this level for transis both reset outputs also go low. When Vout recovers above NMII trigger levet. If Vout remains below this level for transis both reset outputs goes high, then after time t, both reset outputs also go high. Times t t, are adjusted by capacitor C <sub>RES</sub> inserted between this pin and ground.         18       RES2         Reset signal output to sub CPU         19       CONT         Input pin for resetting sub CPU on command, or when sub CPU crashes Low in CONT causes low output at RES2         20       SW         Selects simultaneous control, in which main and sub CPU is reset independently main CPU         Open—independent control; connected to ground—simultaneous control         21       C <sub>R2</sub> For connecting capacitor C <sub>R2</sub> to determine t <sub>off2</sub> , t <sub>RH2</sub> , and t <sub>RL2</sub> , d <sub>RL1</sub> , and t <sub>RL2</sub> . Use resistor value from 100 kΩ                                                                                                                                          | 10      | Re1              | For connecting resistor Re1 to determine voltage Vout for microprocessor and IC internal circuits (insert between this pin and Re2)                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 13       V <sub>cc</sub> Power supply input pin (operating range: 6 to 40 V)         14       CS       Input for detecting power supply current         15       V <sub>c</sub> For base control of external pnp transistor         16       Vout       Regulated voltage supplied to microprocessor and IC internal circuits Connect t collector of external pnp transistor         17       C <sub>RES</sub> Determines reset pulse delay at voltage drop and recovery. NMI output goes low soon as Vout drops below NMI trigger level. If Vout remains below this level for t <sub>RES</sub> , both reset outputs also go low. When Vout recovers above NMI trigger level. NMI output goes high, then after time t, both reset outputs also go high. Times t t, are adjusted by capacitor C <sub>RES</sub> inserted between this pin and ground.         18       RES2       Reset signal output to sub CPU         19       CONT       Input pin for resetting sub CPU on command, or when sub CPU crashes Low in CONT causes low output at RES2         20       SW       Selects simultaneous control, in which main and sub CPUs are both reset where CPU crashes, or independent control, in which sub CPU is reset independently main CPU         21       C <sub>R2</sub> For connecting capacitor C <sub>R2</sub> to determine t <sub>off2</sub> , t <sub>RH2</sub> , and t <sub>RL2</sub> , f <sub>RL1</sub> , and t <sub>RL2</sub> . Use resistor value from 100 kΩ to 500 kΩ.         23       Cf2       For connecting capacitor Cf2 to determine WDT2 filter characteristic (frequency                                                                                                            | 11      | Re2              | For connecting resistor Re2 to determine voltage Vout for microprocessor and IC internal circuits (insert between this pin and ground)                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 14       CS       Input for detecting power supply current         15       V <sub>c</sub> For base control of external pnp transistor         16       Vout       Regulated voltage supplied to microprocessor and IC internal circuits Connect t collector of external pnp transistor         17       C <sub>RES</sub> Determines reset pulse delay at voltage drop and recovery. NMI output goes low soon as Vout drops below NMI trigger level. If Vout remains below this level for t <sub>RES</sub> , both reset outputs also go low. When Vout recovers above NMI trigger leve. NMI output goes high, then after time t, both reset outputs also go high. Times t t, are adjusted by capacitor C <sub>RES</sub> inserted between this pin and ground.         18       RES2       Reset signal output to sub CPU         19       CONT       Input pin for resetting sub CPU on command, or when sub CPU crashes Low in CONT causes low output at RES2         20       SW       Selects simultaneous control, in which main and sub CPU is reset independently main CPU Open—independent control; connected to ground—simultaneous control         21       C <sub>R2</sub> For connecting capacitor C <sub>R2</sub> to determine t <sub>off1</sub> , t <sub>fn12</sub> , t <sub>RH1</sub> , t <sub>RH2</sub> , t <sub>RL1</sub> , and t <sub>RL2</sub> . Use resistor value from 100 kΩ to 500 kΩ.         23       Cf2       For connecting capacitor Cf2 to determine WDT2 filter characteristic (frequency                                                                                                                                                                                           | 12      | GND              | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 15       V <sub>c</sub> For base control of external pnp transistor         16       Vout       Regulated voltage supplied to microprocessor and IC internal circuits Connect t collector of external pnp transistor         17       C <sub>RES</sub> Determines reset pulse delay at voltage drop and recovery. NMI output goes low soon as Vout drops below NMI trigger level. If Vout remains below this level for t <sub>RES</sub> , both reset outputs also go low. When Vout recovers above NMI trigger level NMI output goes high, then after time t, both reset outputs also go high. Times t t, are adjusted by capacitor C <sub>RES</sub> inserted between this pin and ground.         18       RES2       Reset signal output to sub CPU         19       CONT       Input pin for resetting sub CPU on command, or when sub CPU crashes Low in CONT causes low output at RES2         20       SW       Selects simultaneous control, in which main and sub CPUs are both reset when CPU crashes, or independent control, in which sub CPU is reset independently main CPU         0pen—independent control; connected to ground—simultaneous control         21       C <sub>R2</sub> For connecting capacitor C <sub>R2</sub> to determine t <sub>off2</sub> , t <sub>RH2</sub> , and t <sub>RL2</sub> of auto-reset circuit 2 resistor value from 100 kΩ to 500 kΩ.         23       Cf2       For connecting capacitor Cf2 to determine WDT2 filter characteristic (frequency                                                                                                                                                                                                                   | 13      | V <sub>cc</sub>  | Power supply input pin (operating range: 6 to 40 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 16       Vout       Regulated voltage supplied to microprocessor and IC internal circuits Connect t collector of external pnp transistor         17       C <sub>RES</sub> Determines reset pulse delay at voltage drop and recovery. NMI output goes low soon as Vout drops below NMI trigger level. If Vout remains below this level for t <sub>RES</sub> , both reset outputs also go low. When Vout recovers above NMI trigger level. NMI output goes high, then after time t, both reset outputs also go high. Times t t, are adjusted by capacitor C <sub>RES</sub> inserted between this pin and ground.         18       RES2       Reset signal output to sub CPU         19       CONT       Input pin for resetting sub CPU on command, or when sub CPU crashes Low in CONT causes low output at RES2         20       SW       Selects simultaneous control, in which main and sub CPUs are both reset when CPU crashes, or independent control, in which sub CPU is reset independently main CPU         21       C <sub>R2</sub> For connecting capacitor C <sub>R2</sub> to determine t <sub>off2</sub> , t <sub>RH2</sub> , and t <sub>RL2</sub> of auto-reset circuit 2         22       R <sub>R</sub> For connecting bias resistor R <sub>R</sub> to determine t <sub>off1</sub> , t <sub>off2</sub> , t <sub>RH1</sub> , t <sub>RL2</sub> , t <sub>RL1</sub> , and t <sub>RL2</sub> . Use resistor value from 100 kΩ to 500 kΩ.         23       Cf2       For connecting capacitor Cf2 to determine WDT2 filter characteristic (frequency                                                                                                                                                    | 14      | CS               | Input for detecting power supply current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| collector of external prip transistor         17       C <sub>RES</sub> Determines reset pulse delay at voltage drop and recovery. NMI output goes low soon as Vout drops below NMI trigger level. If Vout remains below this level for t <sub>RES1</sub> both reset outputs also go low. When Vout recovers above NMI trigger level NMI output goes high, then after time t, both reset outputs also go high. Times t t, are adjusted by capacitor C <sub>RES</sub> inserted between this pin and ground.         18       RES2         19       CONT         Input pin for resetting sub CPU on command, or when sub CPU crashes Low in CONT causes low output at RES2         20       SW         Selects simultaneous control, in which main and sub CPUs are both reset when CPU crashes, or independent control, in which sub CPU is reset independently main CPU         Open—independent control; connected to ground—simultaneous control         21       C <sub>R2</sub> 22       R <sub>R</sub> For connecting bias resistor R <sub>R</sub> to determine t <sub>off2</sub> , t <sub>RH1</sub> , t <sub>RH2</sub> , t <sub>RL1</sub> , and t <sub>RL2</sub> . Use resistor value from 100 kΩ to 500 kΩ.         23       Cf2                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15      | V <sub>c</sub>   | For base control of external pnp transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| soon as Vout drops below NMI trigger level. If Vout remains below this level for<br>t_RES1 both reset outputs also go low. When Vout recovers above NMI trigger level<br>NMI output goes high, then after time t, both reset outputs also go high. Times t<br>t, are adjusted by capacitor CRES inserted between this pin and ground.18RES2Reset signal output to sub CPU19CONTInput pin for resetting sub CPU on command, or when sub CPU crashes Low in<br>CONT causes low output at RES220SWSelects simultaneous control, in which main and sub CPUs are both reset when<br>CPU crashes, or independent control, in which sub CPU is reset independently<br>main CPU21CR2For connecting capacitor CR2 to determine toff2, tRH2, and tRL2 of auto-reset circuit 2<br>resistor value from 100 kΩ to 500 kΩ.23Cf2For connecting capacitor Cf2 to determine WDT2 filter characteristic (frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16      | Vout             | Regulated voltage supplied to microprocessor and IC internal circuits Connect to collector of external pnp transistor                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 19       CONT       Input pin for resetting sub CPU on command, or when sub CPU crashes Low in CONT causes low output at RES2         20       SW       Selects simultaneous control, in which main and sub CPUs are both reset when CPU crashes, or independent control, in which sub CPU is reset independently main CPU         0       Open—independent control; connected to ground—simultaneous control         21       C <sub>R2</sub> For connecting capacitor C <sub>R2</sub> to determine t <sub>off2</sub> , t <sub>RH2</sub> , and t <sub>RL2</sub> of auto-reset circuit 2         22       R <sub>R</sub> For connecting bias resistor R <sub>R</sub> to determine t <sub>off1</sub> , t <sub>off2</sub> , t <sub>RH1</sub> , t <sub>RH2</sub> , t <sub>RL1</sub> , and t <sub>RL2</sub> . Use resistor value from 100 kΩ to 500 kΩ.         23       Cf2       For connecting capacitor Cf2 to determine WDT2 filter characteristic (frequency)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17      | C <sub>RES</sub> | Determines reset pulse delay at voltage drop and recovery. $\overline{\text{NMI}}$ output goes low as soon as Vout drops below $\overline{\text{NMI}}$ trigger level. If Vout remains below this level for time $\underline{t}_{\text{RES}}$ both reset outputs also go low. When Vout recovers above $\overline{\text{NMI}}$ trigger level, first $\overline{\text{NMI}}$ output goes high, then after time t, both reset outputs also go high. Times $t_{\text{RES}}$ and t, are adjusted by capacitor $C_{\text{RES}}$ inserted between this pin and ground. |  |  |

| CONT causes low output at RES2         20       SW         Selects simultaneous control, in which main and sub CPUs are both reset when CPU crashes, or independent control, in which sub CPU is reset independently main CPU         Open—independent control; connected to ground—simultaneous control         21       C <sub>R2</sub> For connecting capacitor C <sub>R2</sub> to determine t <sub>off2</sub> , t <sub>RH2</sub> , and t <sub>RL2</sub> of auto-reset circuit 2         22       R <sub>R</sub> For connecting bias resistor R <sub>R</sub> to determine t <sub>off1</sub> , t <sub>off2</sub> , t <sub>RH1</sub> , t <sub>RH2</sub> , t <sub>RL1</sub> , and t <sub>RL2</sub> . Use resistor value from 100 kΩ to 500 kΩ.         23       Cf2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18      | RES2             | Reset signal output to sub CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| CPU crashes, or independent control, in which sub CPU is reset independently main CPU         Open—independent control; connected to ground—simultaneous control         21       C <sub>R2</sub> For connecting capacitor C <sub>R2</sub> to determine t <sub>off2</sub> , t <sub>RH2</sub> , and t <sub>RL2</sub> of auto-reset circuit 2         22       R <sub>R</sub> For connecting bias resistor R <sub>R</sub> to determine t <sub>off1</sub> , t <sub>off2</sub> , t <sub>RH1</sub> , t <sub>RH2</sub> , t <sub>RL1</sub> , and t <sub>RL2</sub> . Use resistor value from 100 kΩ to 500 kΩ.         23       Cf2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19      | CONT             | Input pin for resetting sub CPU on command, or when sub CPU crashes Low input at $\overrightarrow{\text{CONT}}$ causes low output at $\overrightarrow{\text{RES2}}$                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 21 $C_{R2}$ For connecting capacitor $C_{R2}$ to determine $t_{off2}$ , $t_{RH2}$ , and $t_{RL2}$ of auto-reset circuit 222 $R_R$ For connecting bias resistor $R_R$ to determine $t_{off1}$ , $t_{off2}$ , $t_{RH1}$ , $t_{RH2}$ , $t_{RL1}$ , and $t_{RL2}$ . Use<br>resistor value from 100 k $\Omega$ to 500 k $\Omega$ .23Cf2For connecting capacitor Cf2 to determine WDT2 filter characteristic (frequency)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20      | SW               | Selects simultaneous control, in which main and sub CPUs are both reset when main CPU crashes, or independent control, in which sub CPU is reset independently of main CPU                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 22 $R_R$ For connecting bias resistor $R_R$ to determine $t_{off1}$ , $t_{off2}$ , $t_{RH1}$ , $t_{RH2}$ , $t_{RL1}$ , and $t_{RL2}$ . Use23Cf2For connecting capacitor Cf2 to determine WDT2 filter characteristic (frequency)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |                  | Open-independent control; connected to ground-simultaneous control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| resistor value from 100 kΩ to 500 kΩ.23Cf2For connecting capacitor Cf2 to determine WDT2 filter characteristic (frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 21      | C <sub>R2</sub>  | For connecting capacitor $C_{_{R2}}$ to determine $t_{_{off2}},t_{_{RH2}},$ and $t_{_{RL2}}$ of auto-reset circuit 2                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 22      | R <sub>R</sub>   | For connecting bias resistor R <sub>R</sub> to determine $t_{off1}$ , $t_{off2}$ , $t_{RH1}$ , $t_{RH2}$ , $t_{RL1}$ , and $t_{RL2}$ . Use the resistor value from 100 k $\Omega$ to 500 k $\Omega$ .                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 24 D DI N2 Input from out CDI to watchdog timer 2 (WDT2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23      | Cf2              | For connecting capacitor Cf2 to determine WDT2 filter characteristic (frequency band)                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24      | P-RUN2           | Input from sub CPU to watchdog timer 2 (WDT2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

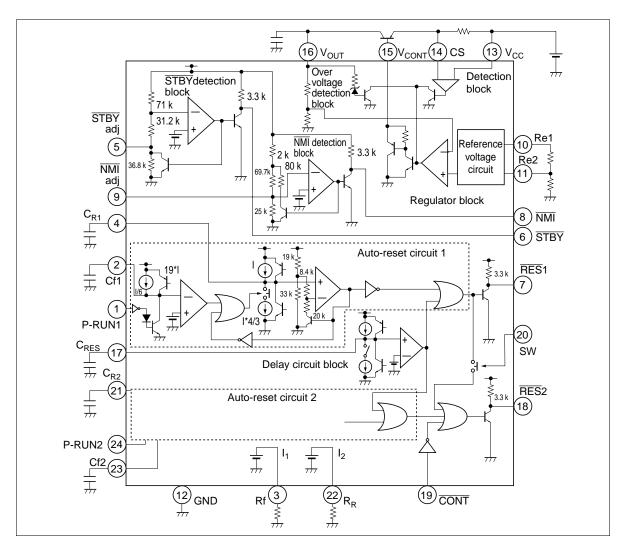

#### **Block Diagram**

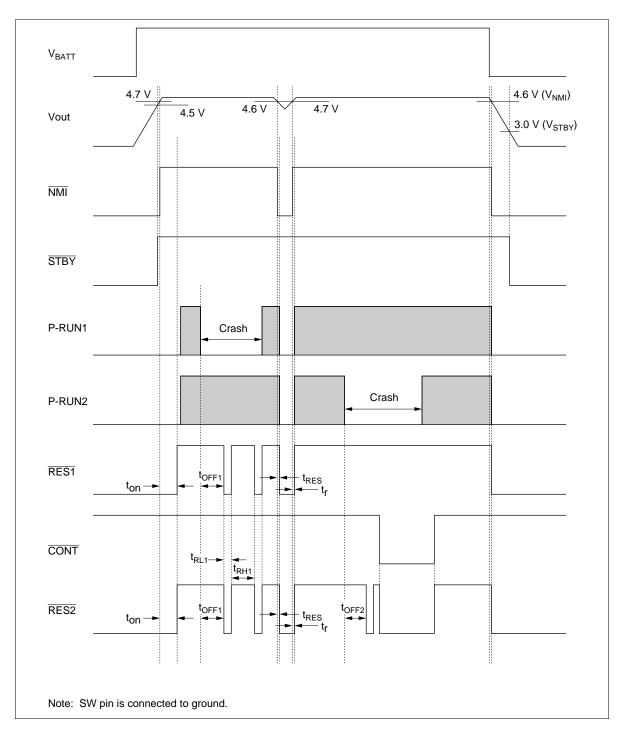

#### **Timing Waveforms**

## Absolute Maximum Ratings ( $Ta = 25^{\circ}C$ )

| Item                                 | Symbol            | Value       | Unit |  |

|--------------------------------------|-------------------|-------------|------|--|

| V <sub>cc</sub> power supply voltage | V <sub>cc</sub>   | 40          | V    |  |

| CS voltage                           | V <sub>cs</sub>   | 40          | V    |  |

| Control pin voltage                  | V <sub>c</sub>    | 40          | V    |  |

| Control pin current                  | Ι <sub>c</sub>    | 20          | mA   |  |

| Vout voltage                         | Vout              | 10          | V    |  |

| P-RUN voltage                        | $V_{PRUN}$        | Vout        | V    |  |

| SW voltage                           | V <sub>sw</sub>   | Vout        | V    |  |

| CONT voltage                         | V <sub>cont</sub> | Vout        | V    |  |

| RES current                          | I <sub>RES</sub>  | 5           | mA   |  |

| NMI current                          | I <sub>NMI</sub>  | 5           | mA   |  |

| STBY current                         | I <sub>STBY</sub> | 5           | mA   |  |

| Power dissipation <sup>Note</sup>    | P <sub>T</sub>    | 600         | mW   |  |

| Operating temperature                | Topr              | -40 to +85  | °C   |  |

| Storage temperature                  | Tstg              | -50 to +125 | °C   |  |

Note: At ambient temperatures up to  $Ta = 60^{\circ}C$ . Derated by 9.8 mW/°C above this point.

| Item                      |                                                | Symbol                     | Min   | Тур  | Max   | Unit       | Test Conditions                                                                  |

|---------------------------|------------------------------------------------|----------------------------|-------|------|-------|------------|----------------------------------------------------------------------------------|

| Chip                      | Power supply current                           | I <sub>cc</sub>            |       | 10   | 15    | mA         |                                                                                  |

| Regulator                 | Output voltage                                 | Vo1                        | 4.875 | 5.00 | 5.125 | V          | $V_{cc} = 6$ to 17.5 V<br>$V_c$ current = 5 mA                                   |

|                           |                                                | Vo2                        | 4.80  | 5.00 | 5.20  | V          | $V_{cc} = 6 \text{ to } 17.5 \text{ V}$<br>$V_c \text{ current} = 10 \text{ mA}$ |

|                           | Stability with respect to lin voltage          | e Voline                   | -50   | —    | 50    | mV         | $V_{cc} = 6 \text{ to } 17.5 \text{ V}$<br>$V_c \text{ current} = 10 \text{ mA}$ |

|                           | Stability with respect to<br>load current      | Voload                     | -100  | —    | 100   | mV         | $V_c$ current = 0.1 to 15 mA                                                     |

|                           | Ripple rejection                               | RREJ                       | 45    | 75   |       | dB         | Vi = 0.5 Vrms<br>fi = 1 kHz                                                      |

|                           | Short-circuit detection voltage                | Vos                        | 0.08  | 0.14 | 0.20  | V          |                                                                                  |

|                           | Temperature coeffi-<br>cient of output voltage | σVo/σΤ                     | _     | -40  | _     | ppm/<br>°C |                                                                                  |

|                           | Maximum adjustable output voltage              | Vomax                      | _     | —    | 7.0   | V          |                                                                                  |

| P-RUN1/2                  | Low input voltage                              | $V_{\rm IL1,2}$            | _     |      | 0.8   | V          |                                                                                  |

| input section             | High input voltage                             | $V_{\rm IH1,2}$            | 2.0   | —    | —     | V          |                                                                                  |

|                           | High input current                             | <b>I</b> <sub>IH1, 2</sub> |       | 0.3  | 0.5   | mA         | $V_{IH} = V_{OL}$                                                                |

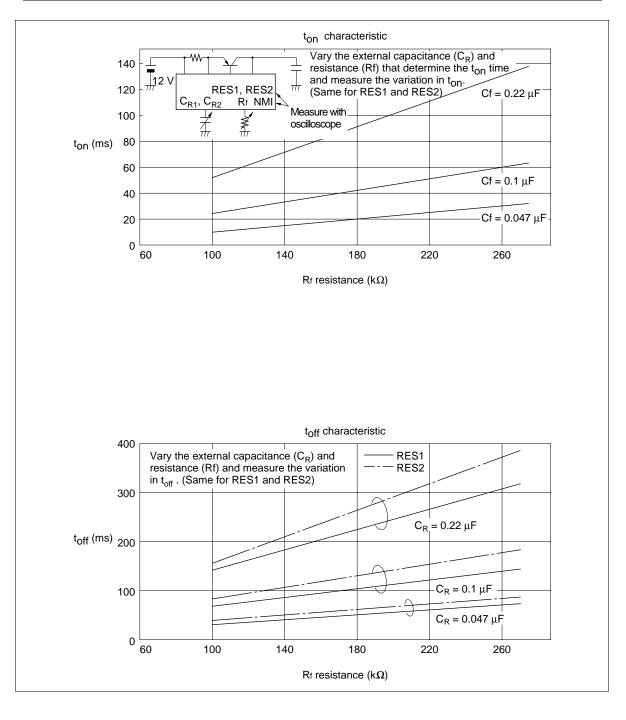

| Watchdog                  | Power-on time                                  | t <sub>on</sub>            | 25    | 40   | 60    | ms         |                                                                                  |

| section (both<br>RES1 and | Clock-off time (1)                             | t <sub>off1</sub>          | 80    | 130  | 190   | ms         | R <sub>R</sub> : open                                                            |

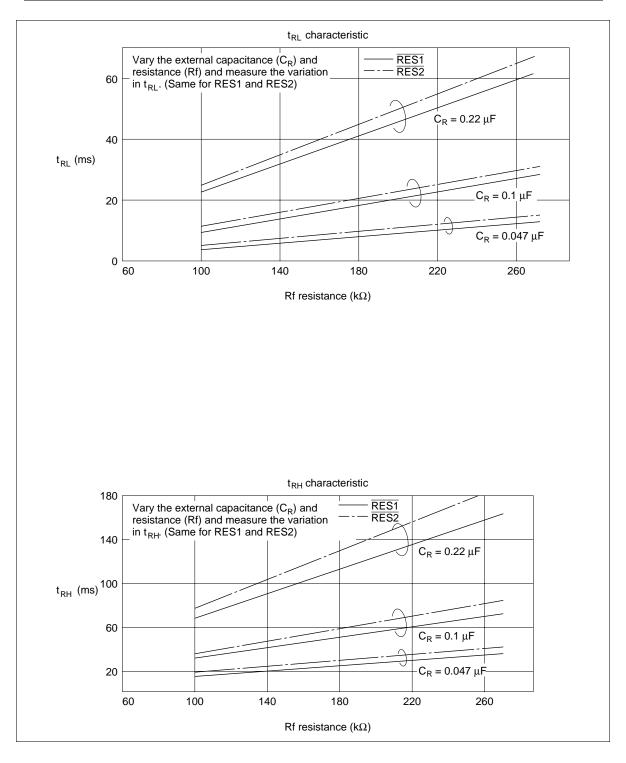

| RES2 outputs)             | Reset low time (1)                             | t <sub>RL1</sub>           | 15    | 20   | 30    | ms         | R <sub>R</sub> : open                                                            |

| . ,                       | Reset high time (1)                            | t <sub>RH1</sub>           | 40    | 60   | 90    | ms         | R <sub>R</sub> : open                                                            |

|                           | Clock-off time (2)                             | t <sub>off2</sub>          | 25    | 40   | 60    | ms         | $R_R$ : = 75 k $\Omega$                                                          |

|                           | Reset low time (2)                             | t <sub>RL2</sub>           | 4     | 6    | 9     | ms         | $R_{R}$ : = 75 k $\Omega$                                                        |

|                           | Reset high time (2)                            | t <sub>RH2</sub>           | 15    | 20   | 30    | ms         | $R_R$ : = 75 k $\Omega$                                                          |

| LVI section               | NMI trigger voltage                            | V <sub>NMI</sub>           | 4.45  | 4.60 | 4.75  | V          |                                                                                  |

|                           | Hysteresis width of above                      | $V_{\rm HYSN}$             | 25    | 50   | 100   | mV         |                                                                                  |

|                           | STBY trigger voltage                           | $V_{STBY}$                 | 2.70  | 3.00 | 3.30  | V          |                                                                                  |

|                           | Hysteresis width of above                      | $V_{\rm HYSS}$             | 1.35  | 1.50 | 1.65  | V          |                                                                                  |

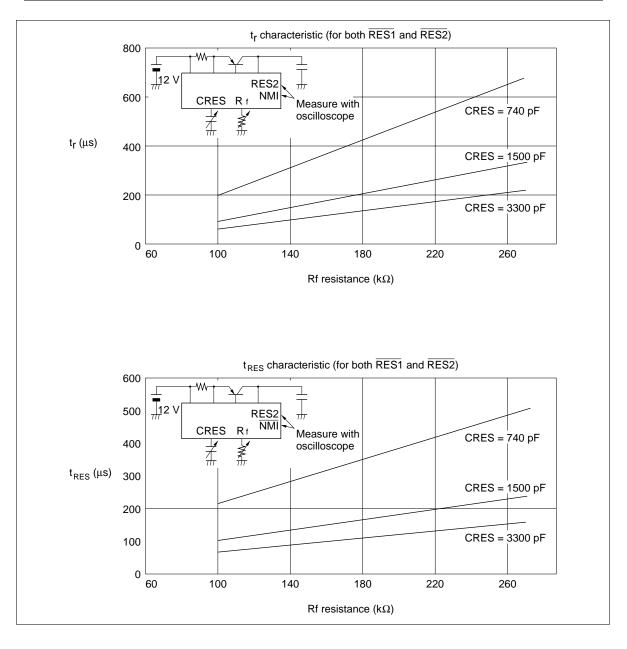

|                           | RES pulse Drop                                 | t <sub>res</sub>           | —     | 200  |       | μs         | C <sub>RES</sub> = 1500 pF                                                       |

|                           | delay time Recovery                            | t,                         |       | 200  | _     | μs         | C <sub>RES</sub> = 1500 pF                                                       |

## Electrical Characteristics (Ta = 25°C, Rf = 180 k , Cf1 = Cf2 = 0.01 $\mu F,$ $C_{\rm R1}$ = $C_{\rm R2}$ = 0.1 $\mu F)$

| ltem          |                                                   | Symbol                   | Min  | Тур          | Max | Unit       | Test Conditions            |

|---------------|---------------------------------------------------|--------------------------|------|--------------|-----|------------|----------------------------|

| NMI output    | NMI low voltage                                   | V <sub>OL1</sub>         |      | —            | 0.4 | V          | I <sub>OL1</sub> = 2 mA    |

| section       | NMI high voltage                                  | V <sub>OH1</sub>         |      | $V_{\rm O1}$ | —   | V          |                            |

|               | NMI function initial voltage                      | $V_{\rm STN}$            |      | 0.7          | 1.0 | V          |                            |

| STBY output   | STBY low voltage                                  | V <sub>OL2</sub>         |      | —            | 0.4 | V          | I <sub>0L2</sub> = 2 mA    |

| section       | STBY high voltage                                 | V <sub>OH2</sub>         |      | $V_{\rm O1}$ | —   | V          |                            |

|               | STBY function initial voltage                     | $V_{\rm STS}$            | _    | 0.7          | 1.0 | V          |                            |

| RES1/2 output | RES1/2 low voltage                                | $V_{\text{OL3}}$         | _    | —            | 0.4 | V          | I <sub>OL3, 4</sub> = 2 mA |

| section       | RES1/2 high voltage                               | V <sub>OH3</sub>         |      | $V_{\rm O1}$ | —   | V          |                            |

|               | RES1/2 function initial voltage                   | $V_{STR}$                | _    | 0.7          | 1.0 | V          |                            |

| CONT and SW   | Low input voltage                                 | V <sub>IL3</sub>         |      | —            | 0.8 | V          |                            |

| input section | High input voltage                                | V <sub>IH3</sub>         | 2.0  | —            | —   | V          |                            |

|               | Low input current                                 | I <sub>IL3</sub>         | -120 | -60          | —   | μΑ         | $V_{IL3} = 0 V$            |

|               | High input current                                | I <sub>IH3</sub>         |      | 0.3          | 0.5 | mA         | $V_{IH3} = V_{OL}$         |

| LVI section   | Temperature coefficient of<br>NMI trigger voltage | $\delta V_{H1}/\delta T$ | —    | 100          | _   | ppm/<br>°C |                            |

|               | Temperature coefficient of STBY trigger voltage   | $\delta V_{H2}/\delta T$ | —    | 200          | _   | ppm/<br>°C |                            |

## $\label{eq:electrical Characteristics} (Ta=25^{\circ}C,\,Rf=180\;k\;,\,Cf1~=Cf2=0.01\;\mu F,\,C_{_{R1}}=C_{_{R2}}=0.1\;\mu F) ~~(cont)$

#### **External Circuit Constant Calculations**

Equations for the various functions are given below.  $C_{R1}$  and Cf1 are for  $\overline{RES1}$ .  $C_{R2}$  and Cf2 are for  $\overline{RES2}$ . (Values given in equations are for reference.)

| ltem                                                | Equation                                                                                                                                                                                    | Remarks                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Regulated<br>output voltage                         | $Vout = 0.388 \times \frac{Re2}{Re1} + 2.63$                                                                                                                                                | If the desired Vout is 5 V<br>$\pm$ 2.5%, recommended<br>values are Re1 = 1.5 kΩ<br>and Re2 = 9.1 kΩ<br>HA16113FPJ<br>Re1 Re2                                                                                                                                                                               |

| Short-circuit<br>detection<br>voltage               | $V_{cs}$ < lout × $R_{cs}$                                                                                                                                                                  | When this function<br>operates, $V_{CONT}$ stops<br>drawing current from the<br>base of the external<br>transistor, so Vout output<br>stops                                                                                                                                                                 |

| Maximum<br>output voltage                           | Vout Max < 7.0 V                                                                                                                                                                            | Prevents microprocessor damage that would result if<br>the output voltage were raised too high by mistake.<br>The maximum output voltage is fixed.                                                                                                                                                          |

| $t_{RH}$ , $t_{RL}$ (for both RES1 and RES2)        | $t_{\rm RH} = 3.2 \times C_{\rm R} \times {\rm R}' \\ t_{\rm RL} = 1.1 \times C_{\rm R} \times {\rm R}' \left( {\rm R}' = \frac{1}{\frac{1}{{\rm Rf}} + \frac{1}{{\rm R}_{\rm R}}} \right)$ | Determines the t <sub>RL</sub><br>frequency and duty cycle<br>of the reset pulse RES                                                                                                                                                                                                                        |

| $t_{oN}$ (for both RES1 and RES2)                   | $t_{on} = 2.2 \times C_{R} \times Rf$                                                                                                                                                       | Sets the time from the rise of Vout to the clearing of RES output RES                                                                                                                                                                                                                                       |

| $\frac{t_{OFF}}{RES1}$ and RES2)                    | $t_{OFF} = 6.1 \times C_R \times R' \left( R' = \frac{1}{\frac{1}{Rf} + \frac{1}{R_R}} \right)$                                                                                             | Sets the time from when<br>P-RUN pulses stop until<br>the reset pulse is output<br>RES                                                                                                                                                                                                                      |

| tr, t <sub>RES</sub> (for<br>both RES1<br>and RES2) | $t_{r} = 0.75 \times C_{RES} \times Rf$<br>$t_{RES} = 0.625 \times C_{RES} \times Rf$                                                                                                       | tr sets the time from the rise of $\overline{\text{NMI}}$ to the rise of $\overline{\text{RES}}$ , when Vout drops by more than the $\overline{\text{STBY}}$ trigger voltage, then recovers. t <sub>RES</sub> is the time from the fall of $\overline{\text{NMI}}$ to the fall of $\overline{\text{RES}}$ . |

|                                                     |                                                                                                                                                                                             | Vout         4.65 V (typ)           NMI         4.67 V (typ)                                                                                                                                                                                                                                                |

|                                                     |                                                                                                                                                                                             | RES t <sub>r</sub> t <sub>RES</sub>                                                                                                                                                                                                                                                                         |

#### **External Circuit Constant Calculations (cont)**

| Item              | Equation                                                                                                                                                                                                                                                                                                                                                                                                      | Remarks                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>NMI</sub>  | $\begin{split} V_{\text{NMI}} &= 1.2 \times \left[ 1 + \frac{(\text{R1 // 71.7})}{(\text{R2 // 25})} \right] \\ \hline \text{NMI recovery voltage} \\ (V_{\text{NMI}} \text{ high}) \text{ is:} \\ V_{\text{NMI}} \text{ high} &= \\ & \left( \frac{86.65}{\text{R1}} + \frac{86.65}{\text{R2 // 25}} + 1.2 \right) \\ & \left( 1 + \frac{73.8}{\text{R1}} \right) \\ \end{split}$ (R1 and R2 are in k\Omega) | Voltage at which the $\overline{\text{NMI}}$ signal is output when Vout<br>drops. The $\overline{\text{NMI}}$ trigger voltage and $\overline{\text{NMI}}$ recovery voltage<br>can be trimmed by connecting resistors between the<br>$\overline{\text{NMI}}$ adj pin and Vout (R1), and between $\overline{\text{NMI}}$ adj and $\overline{\text{GND}}$<br>(R2).                                        |

| V <sub>STBY</sub> | V <sub>STBY</sub> =<br>1.47× $\left\{ 1 + \frac{71}{31.2 + (36.8 // R3)} \right\}$<br>(R3 is in kΩ)                                                                                                                                                                                                                                                                                                           | Voltage at which the $\overline{STBY}$ signal is output when Vout<br>drops. The $\overline{STBY}$ trigger voltage can be adjusted by<br>connecting a resistor (R3) between the $\overline{STBY}$ adj pin and<br>GND. The $\overline{STBY}$ recovery voltage cannot be adjusted.                                                                                                                        |

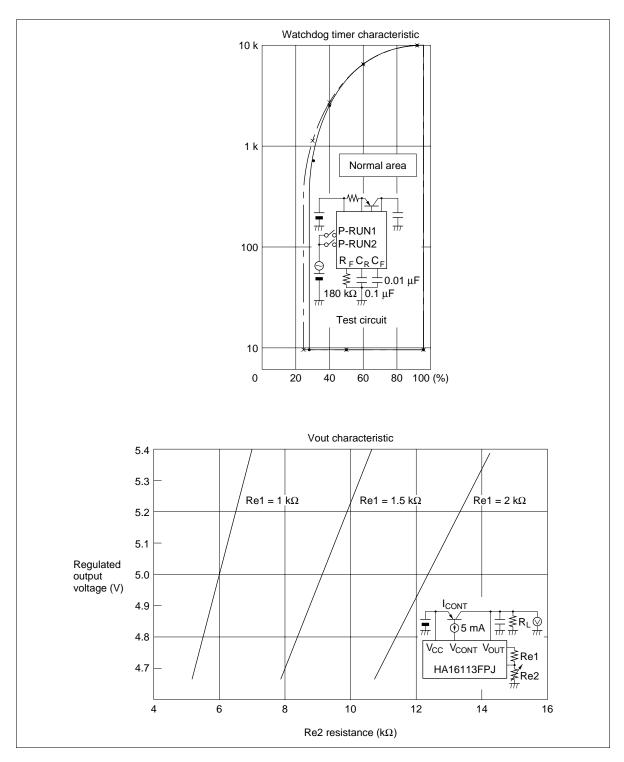

| WDT.              | Line1 = $\frac{0.31 \times (Du - 24)}{Cf \times Rf}$<br>Line2 = Du (= 25%)*<br>Line3 = $\frac{0.015}{Cf \times Rf}$<br>Line4 = $\frac{1 - Du}{2.1 \times t_{RH}}$<br>Line5 = 99%*<br>Du is the duty cycle of the P-RUN pulse.<br>Du = $\frac{t_{RH}}{t_{RL} + t_{RH}}$<br>Note: Line2 and Line5 are fixed.                                                                                                    | The watchdog timer function determines whether the P-<br>RUN pulse is normal or not. A reset pulse is output if P-<br>RUN is determined to be abnormal. The normal region is<br>the part bounded by Line1 to Line3 (or Line4) in the<br>diagram. Line4 applies in certain cases, depending on<br>$C_R$ , Cf, and the state of P-RUN.<br>(Hz)<br>Line1<br>Normal area<br>Line2<br>Line2<br>Line3<br>(%) |

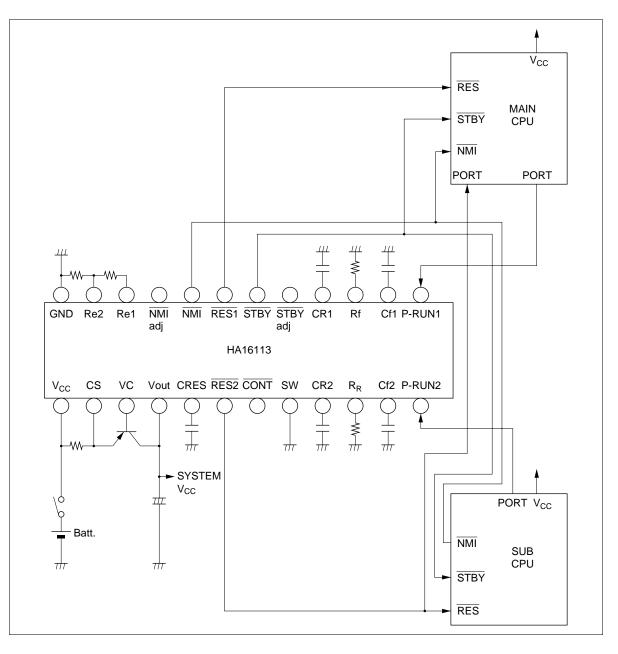

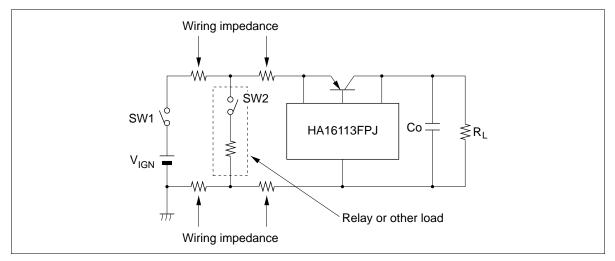

### **Operating Interconnections (example)**

#### **Characteristic Curves**

#### Precautions

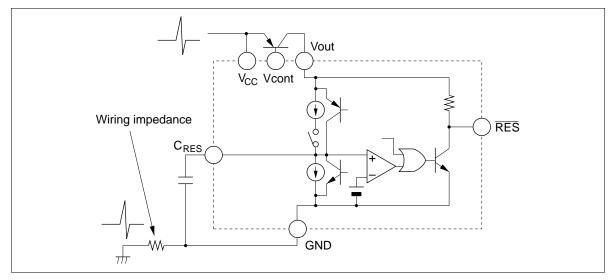

If the IC's ground potential varies suddenly by several volts due to wiring impedance (see figure 7), a false  $\overline{\text{RES}}$  pulse may be output. The reason for this is that potentials in the  $\overline{\text{RES}}$  pulse generating circuit change together with the Vout-GND potential. The reference potential of the comparator in figure 8 and the potential of the external capacitor have different impedances as seen from the comparator, causing a momentary inversion. The solution is to stabilize the ground potential. Two ways of stabilizing the IC's ground line are:

- Separate the IC's ground line from high-current ground lines.

- Increase the capacitance (Co) used to smooth the Vout output.

Figure 1 Typical Circuit

Figure 2 **RES** Comparator

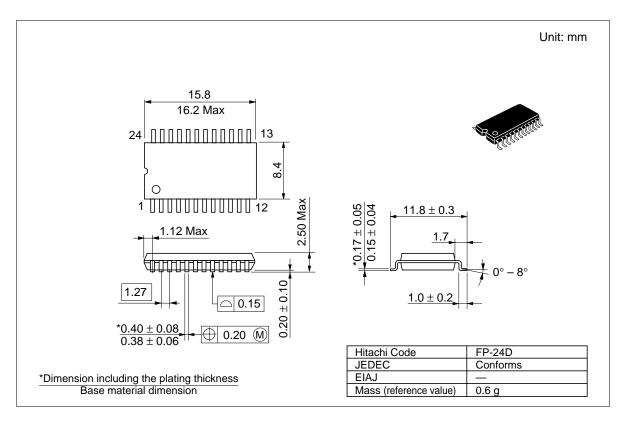

#### **Package Dimensions**

#### Cautions

- Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

## HITACHI

| Semiconductor & Integrate<br>Nippon Bldg., 2-6-2, Ohte-<br>Tel: Tokyo (03) 3270-2111<br>URL NorthAmerica<br>Europe<br>Asia (Singapo<br>Asia (Taiwan<br>Asia (HongKo<br>Japan | machi, Chiyoda-ku, Tokyo 100-0004,<br>Fax: (03) 3270-5109<br>a : http:semiconductor.hita<br>: http://www.hitachi-eu.c<br>ore) : http://www.has.hitachi.<br>) : http://www.hitachi.com. | achi.com/<br>om/hel/ecg<br>com.sg/grp3/sicd/index.htm<br>.tw/E/Product/SICD_Frame.htr<br>hk/eng/bo/grp3/index.htm                                                                                                                                                                                  | n                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| For further informatic<br>Hitachi Semiconductor<br>(America) Inc.<br>179 East Tasman Drive,<br>San Jose, CA 95134<br>Tel: <1> (408) 433-1990<br>Fax: <1>(408) 433-0223       |                                                                                                                                                                                        | Hitachi Asia Pte. Ltd.<br>16 Collyer Quay #20-00<br>Hitachi Tower<br>Singapore 049318<br>Tel: 535-2100<br>Fax: 535-1533<br>Hitachi Asia Ltd.<br>Taipei Branch Office<br>3F, Hung Kuo Building. No.167,<br>Tun-Hwa North Road, Taipei (105)<br>Tel: <886> (2) 2718-3666<br>Fax: <886> (2) 2718-8180 | Hitachi Asia (Hong Kong) Ltd.<br>Group III (Electronic Components)<br>7/F., North Tower, World Finance Centre,<br>Harbour City, Canton Road, Tsim Sha Tsui,<br>Kowloon, Hong Kong<br>Tel: <852> (2) 735 9218<br>Fax: <852> (2) 735 0281<br>Telex: 40815 HITEC HX |