#### FAIRCHILD

SEMICONDUCTOR

#### April 1988 Revised November 1999

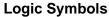

## 74F109 Dual JK Positive Edge-Triggered Flip-Flop

#### **General Description**

The F109 consists of two high-speed, completely independent transition clocked JK flip-flops. The clocking operation is independent of rise and fall times of the clock waveform. The JK design allows operation as a D-type flip-flop (refer to F74 data sheet) by connecting the J and  $\overline{K}$  inputs.

#### Asynchronous Inputs:

LOW input to  $\overline{S}_{D}$  sets Q to HIGH level LOW input to  $\overline{C}_D$  sets Q to LOW level Clear and Set are independent of clock Simultaneous LOW on  $\overline{C}_D$  and  $\overline{S}_D$  makes both Q and  $\overline{Q}$  HIGH

#### **Ordering Code:**

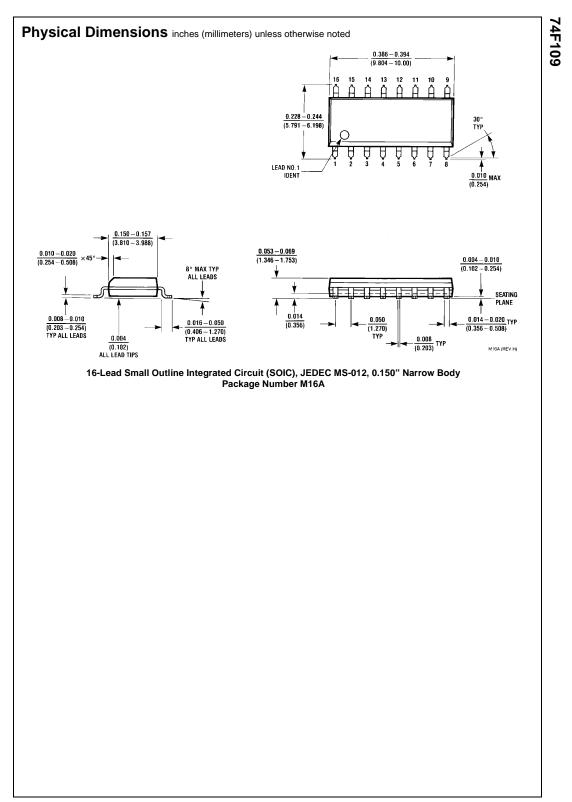

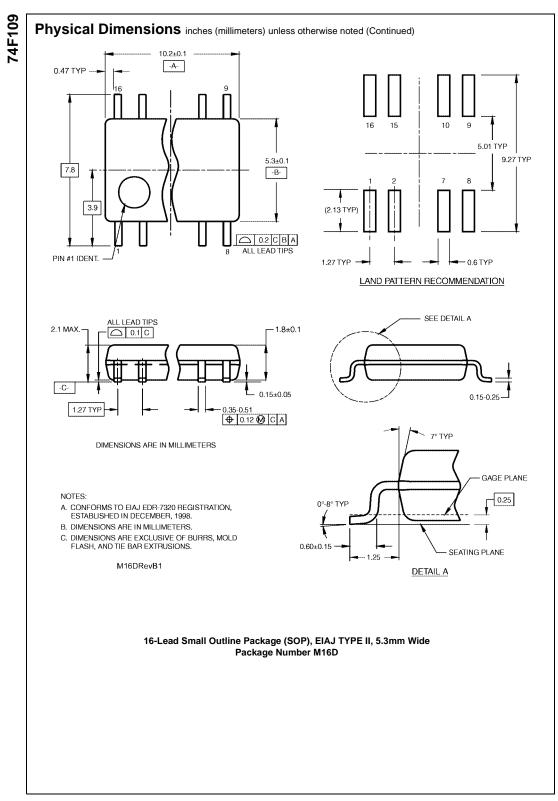

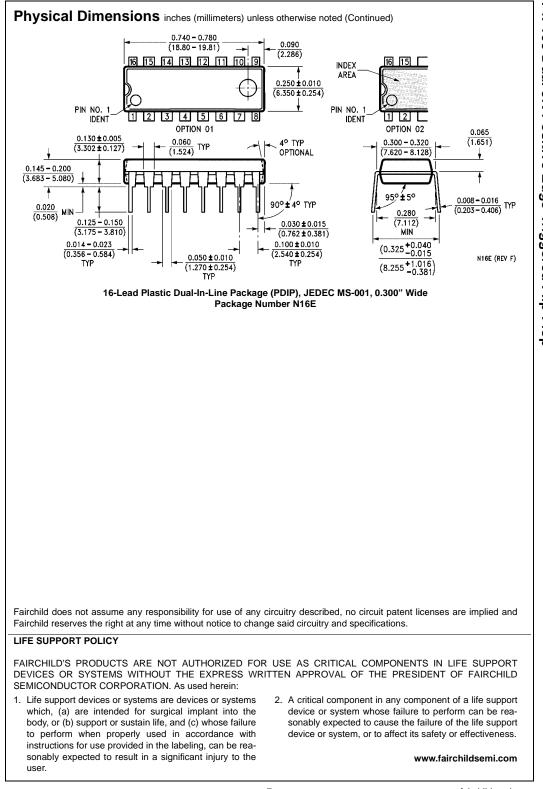

| Order Number | Package Number | Package Description                                                               |

|--------------|----------------|-----------------------------------------------------------------------------------|

| 74F109SC     | M16A           | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow Body |

| 74F109SJ     | M16D           | 16-Lead Small Outline Package (SOP), EIAJ TYPE 11, 5.3mm Wide                     |

| 74F109PC     | N16E           | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide            |

Devices also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering code.

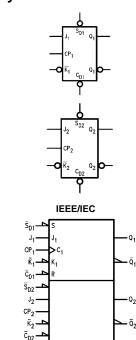

#### **Connection Diagram**

© 1999 Fairchild Semiconductor Corporation DS009471

Q.,

# 74F109

#### **Truth Table**

| Inputs |                       |   |    |   | Outputs |      |  |

|--------|-----------------------|---|----|---|---------|------|--|

| SD     | C <sub>D</sub> CP J K |   |    |   | Q       | Q    |  |

| L      | н                     | Х | Х  | Х | Н       | L    |  |

| н      | L                     | Х | Х  | Х | L       | н    |  |

| L      | L                     | Х | Х  | Х | н       | н    |  |

| н      | н                     | ~ | I. | 1 | L       | н    |  |

| н      | н                     | ~ | h  | 1 | Тор     | jgle |  |

| н      | н                     | ~ | I. | h | Q       | Q    |  |

| н      | н                     | ~ | h  | h | н       | L    |  |

| Н      | н                     | L | Х  | Х | Q       | Q    |  |

H (h) = HIGH Voltage Level L (l) = LOW Voltage Level  $\checkmark$  = LOW-to-HIGH Transition X = Immaterial Q<sub>0</sub> ( $\overline{Q_0}$ ) = Before LOW-to-HIGH Transition of Clock

Lower case letters indicate the state of the referenced output one setup time prior to the LOW-to-HIGH clock transition.

#### **Unit Loading/Fan Out**

| Dia Manag                                  | Description                             | U.L.     | Input I <sub>IH</sub> /I <sub>IL</sub>  |  |

|--------------------------------------------|-----------------------------------------|----------|-----------------------------------------|--|

| Pin Names                                  | Description                             | HIGH/LOW | Output I <sub>OH</sub> /I <sub>OL</sub> |  |

| $J_1, J_2, \overline{K}_1, \overline{K}_2$ | Data Inputs                             | 1.0/1.0  | 20 µA/–0.6 mA                           |  |

| CP <sub>1</sub> , CP <sub>2</sub>          | Clock Pulse Inputs (Active Rising Edge) | 1.0/1.0  | 20 µA/–0.6 mA                           |  |

| $\overline{C}_{D1}, \overline{C}_{D2}$     | Direct Clear Inputs (Active LOW)        | 1.0/3.0  | 20 µA/–1.8 mA                           |  |

| $\overline{S}_{D1}, \overline{S}_{D2}$     | Direct Set Inputs (Active LOW)          | 1.0/3.0  | 20 µA/–1.8 mA                           |  |

| $Q_1, Q_2, \overline{Q}_1, \overline{Q}_2$ | Outputs                                 | 50/33.3  | –1 mA/20 mA                             |  |

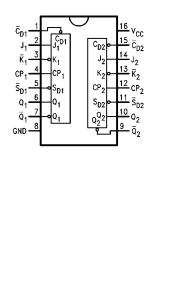

#### **Block Diagram**

#### Absolute Maximum Ratings(Note 1)

| Storage Temperature                 | -65°C to +150°C               |

|-------------------------------------|-------------------------------|

| Ambient Temperature under Bias      | -55°C to +125°C               |

| Junction Temperature under Bias     | -55°C to +175°C               |

| V <sub>CC</sub> Pin Potential to    |                               |

| Ground Pin                          | -0.5V to +7.0V                |

| Input Voltage (Note 2)              | -0.5V to +7.0V                |

| Input Current (Note 2)              | -30 mA to +5.0 mA             |

| Voltage Applied to Output           |                               |

| in HIGH State (with $V_{cc} = 0V$ ) |                               |

| Standard Output                     | -0.5V to V <sub>CC</sub>      |

| 3-STATE Output                      | -0.5V to +5.5V                |

| Current Applied to Output           |                               |

| in LOW State (Max)                  | twice the rated $I_{OL}$ (mA) |

|                                     |                               |

# Recommended Operating Conditions

| Free Air Ambient Temperature |  |

|------------------------------|--|

| Supply Voltage               |  |

74F109

0°C to +70°C

+4.5V to +5.5V

Note 1: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

$+5.5V \qquad \text{Note 2: Either voltage limit or current limit is sufficient to protect inputs.}$

#### **DC Electrical Characteristics**

| Symbol           | Parameter                               | Min  | Тур  | Max  | Units | v <sub>cc</sub> | Conditions                                                 |

|------------------|-----------------------------------------|------|------|------|-------|-----------------|------------------------------------------------------------|

| V <sub>IH</sub>  | Input HIGH Voltage                      | 2.0  |      |      | V     |                 | Recognized as a HIGH Signal                                |

| V <sub>IL</sub>  | Input LOW Voltage                       |      |      | 0.8  | V     |                 | Recognized as a LOW Signal                                 |

| V <sub>CD</sub>  | Input Clamp Diode Voltage               |      |      | -1.2 | V     | Min             | $I_{IN} = -18 \text{ mA}$                                  |

| V <sub>OH</sub>  | Output HIGH Voltage 10% V <sub>CC</sub> | 2.5  |      |      | v     |                 | $I_{OH} = -1 \text{ mA}$                                   |

|                  | 5% V <sub>CC</sub>                      | 2.7  |      |      | v     | Min             | $I_{OH} = -1 \text{ mA}$                                   |

| V <sub>OL</sub>  | Output LOW Voltage 10% V <sub>CC</sub>  |      |      | 0.5  | V     | Min             | I <sub>OL</sub> = 20 mA                                    |

| I <sub>IH</sub>  | Input HIGH Current                      |      |      | 5.0  | μA    | Max             | $V_{IN} = 2.7V$                                            |

| I <sub>BVI</sub> | Input HIGH Current Breakdown Test       |      |      | 7.0  | μA    | Max             | $V_{IN} = 7.0V$                                            |

| I <sub>CEX</sub> | Output HIGH Leakage Current             |      |      | 50   | μA    | Max             | $V_{OUT} = V_{CC}$                                         |

| V <sub>ID</sub>  | Input Leakage Test                      | 4.75 |      |      | V     | 0.0             | $I_{ID} = 1.9 \ \mu A$                                     |

|                  |                                         | 4.75 |      |      | v     | 0.0             | All Other Pins Grounded                                    |

| I <sub>OD</sub>  | Output Leakage                          |      |      | 3.75 |       | 0.0             | $V_{IOD} = 150 \text{ mV}$                                 |

|                  | Circuit Current                         |      |      | 3.75 | μΑ    | 0.0             | All Other Pins Grounded                                    |

| IIL              | Input LOW Current                       |      |      | -0.6 | mA    | Max             | $V_{IN} = 0.5V (J_n, \overline{K}_n)$                      |

|                  |                                         |      |      | -1.8 | mA    | Max             | $V_{IN} = 0.5V \ (\overline{C}_{Dn}, \ \overline{S}_{Dn})$ |

| I <sub>OS</sub>  | Output Short-Circuit Current            | -60  |      | -150 | mA    | Max             | $V_{OUT} = 0V$                                             |

| I <sub>CC</sub>  | Power Supply Current                    |      | 11.7 | 17.0 | mA    | Max             | CP = 0V                                                    |

74F109

### **AC Electrical Characteristics**

|                  |                                               |                       | $\textbf{T}_{\textbf{A}}=+25^{\circ}\textbf{C}$ |     | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$<br>$V_{CC} = +5.0V$ |      | Unite |

|------------------|-----------------------------------------------|-----------------------|-------------------------------------------------|-----|-----------------------------------------------------------------|------|-------|

|                  | Parameter                                     |                       | V <sub>CC</sub> = +5.0V                         |     |                                                                 |      |       |

| Symbol           |                                               | $C_L = 50 \text{ pF}$ |                                                 |     | $C_L = 50 \text{ pF}$                                           |      | Units |

|                  |                                               | Min                   | Тур                                             | Max | Min                                                             | Max  |       |

| f <sub>MAX</sub> | Maximum Clock Frequency                       | 100                   | 125                                             |     | 90                                                              |      | MHz   |

| t <sub>PLH</sub> | Propagation Delay                             | 3.8                   | 5.3                                             | 7.0 | 3.8                                                             | 8.0  |       |

| t <sub>PHL</sub> | $CP_n$ to $Q_n$ or $\overline{Q}_n$           | 4.4                   | 6.2                                             | 8.0 | 4.4                                                             | 9.2  | ns    |

| t <sub>PLH</sub> | Propagation Delay                             | 3.2                   | 5.2                                             | 7.0 | 3.2                                                             | 8.0  | ns    |

| t <sub>PHL</sub> | $\overline{C}_{Dn}$ or $\overline{S}_{Dn}$ to | 3.5                   | 7.0                                             | 9.0 | 3.5                                                             | 10.5 |       |

|                  | $Q_n$ or $\overline{Q}_n$                     | 3.5                   | 7.0                                             | 9.0 | 3.5                                                             | 10.5 | ns    |

#### **AC Operating Requirements**

|                    | Parameter                                                         | $T_{A} = +25^{\circ}C$ $V_{CC} = +5.0V$ |     | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$<br>$V_{CC} = +5.0V$ |     | Units |

|--------------------|-------------------------------------------------------------------|-----------------------------------------|-----|-----------------------------------------------------------------|-----|-------|

| Symbol             |                                                                   |                                         |     |                                                                 |     |       |

|                    |                                                                   | Min                                     | Max | Min                                                             | Max |       |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW                                           | 3.0                                     |     | 3.0                                                             |     |       |

| t <sub>S</sub> (L) | $J_n$ or $\overline{K}_n$ to $CP_n$                               | 3.0                                     |     | 3.0                                                             |     | ns    |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW                                            | 1.0                                     |     | 1.0                                                             |     |       |

| t <sub>H</sub> (L) | $J_n$ or $\overline{K}_n$ to $CP_n$                               | 1.0                                     |     | 1.0                                                             |     |       |

| t <sub>W</sub> (H) | CP <sub>n</sub> Pulse Width                                       | 4.0                                     |     | 4.0                                                             |     |       |

| t <sub>W</sub> (L) | HIGH or LOW                                                       | 5.0                                     |     | 5.0                                                             |     | ns    |

| t <sub>W</sub> (L) | $\overline{C}_{Dn}$ or $\overline{S}_{Dn}$ Pulse Width LOW        | 4.0                                     |     | 4.0                                                             |     | ns    |

| t <sub>REC</sub>   | Recovery Time<br>$\overline{C}_{Dn}$ or $\overline{S}_{Dn}$ to CP | 2.0                                     |     | 2.0                                                             |     | ns    |

74F109 Dual JK Positive Edge-Triggered Flip-Flop