# **ML2751 Power Amplifier and LNA**

### **GENERAL DESCRIPTION**

The 2751 is a 900 MHz ISM band radio front-end intended for use in half duplex radio applications such as cordless phones and FCC Part 15 compliant devices. It integrates a power amplifier (PA), a Low Noise Amplifier (LNA), Pin Diode drivers for an external transmit/receive switch, and control circuits. The 100mW power amplifier has output power control with a >20dB range. The ML2751 can be used to increase battery life and offers output power ramp control in TDMA applications. An internal LNA eliminates the need for a discrete design. PIN diode drivers control the transmit/receive switch directly. Internal logic individually enables the LNA, PA, and PIN diode drivers. A power down mode to minimize current consumption is included.

#### **FEATURES**

- Fully integrated Power Amplifier, Low Noise Amplifier, and PIN diode drivers

- 100mW Power Amplifier

- Single supply, 2.7V to 4.5V operating range

- PA output: +21 dBm at 3.0V, 35dB gain, 35% efficiency at 3.3V after harmonic filter; integrated PA ramp control

- LNA: noise figure of 2.5dB, −15dBm 3<sup>rd</sup>-order intercept point, and −25dBm

### **APPLICATIONS**

- 900 MHz FCC Part 15 Radios

- 900 MHz Cordless Telephones

- TDD / TDMA Radios

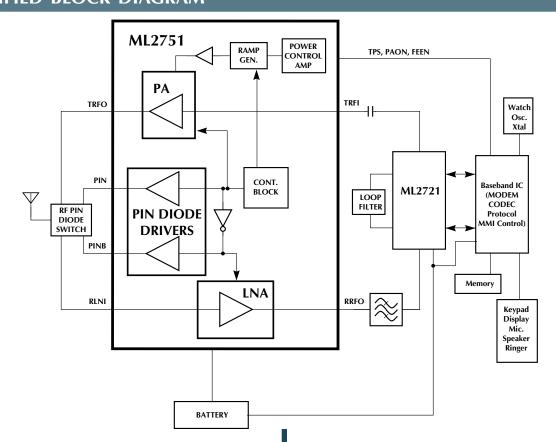

### SIMPLIFIED BLOCK DIAGRAM

#### TABLE OF CONTENTS

| General Description        | 1  |

|----------------------------|----|

| Features                   |    |

| Applications               | 1  |

| Simplified Block Diagram   |    |

| Warranty Information       |    |

| Block Diagram              | 3  |

| Pin Configuration          | 4  |

| Pin Descriptions           | 4  |

| Functional Description     | 6  |

| Electrical Characteristics |    |

| Electrical Tables          | 8  |

| Physical Dimensions        | 12 |

| Order Information          |    |

### **WARRANTY**

Micro Linear makes no representations or warranties with respect to the accuracy, utility, or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, express or implied, by estoppel or otherwise, to any patents or other intellectual property rights is granted by this document. The circuits contained in this document are offered as possible applications only. Particular uses or applications may invalidate some of the specifications and/or product descriptions contained herein. The customer is urged to perform its own engineering review before deciding on a particular application. Micro Linear assumes no liability whatsoever, and disclaims any express or implied warranty, relating to sale and/or use of Micro Linear products including liability or warranties relating to merchantability, fitness for a particular purpose, or infringement of any intellectual property right. Micro Linear products are not designed for use in medical, life saving, or life sustaining applications.

© Micro Linear 2000. is a registered trademark of Micro Linear Corporation. All other trademarks are the property of their respective owners.

Products described herein may be covered by one or more of the following U.S. patents: 4,897,611; 4,964,026; 5,027,116; 5,281,862; 5,283,483; 5,418,502; 5,508,570; 5,510,727; 5,523,940; 5,546,017; 5,559,470; 5,565,761; 5,592,128; 5,594,376; 5,652,479; 5,661,427; 5,663,874; 5,672,959; 5,689,167; 5,714,897; 5,717,798; 5,742,151; 5,747,977; 5,754,012; 5,757,174; 5,767,653; 5,777,514; 5,793,168; 5,798,635; 5,804,950; 5,808,455; 5,811,999; 5,818,207; 5,818,669; 5,825,165; 5,825,223; 5,838,723; 5,844,378; 5,844,941. Japan: 2,598,946; 2,619,299; 2,704,176; 2,821,714. Other patents are pending.

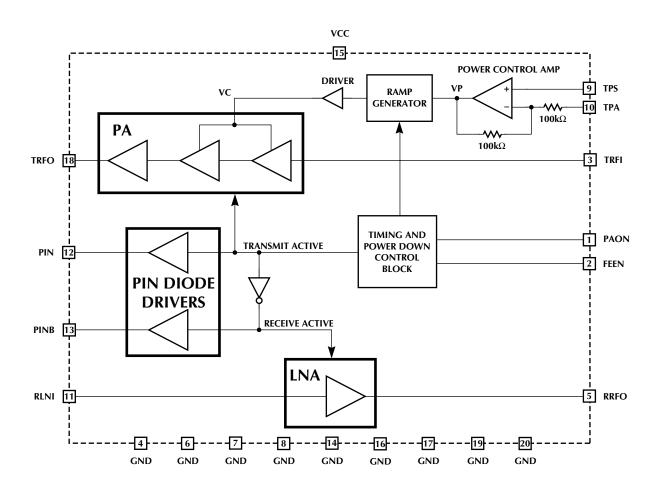

## **BLOCK DIAGRAM**

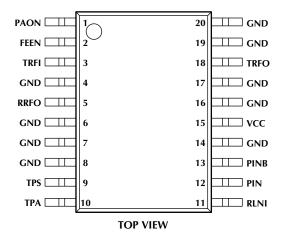

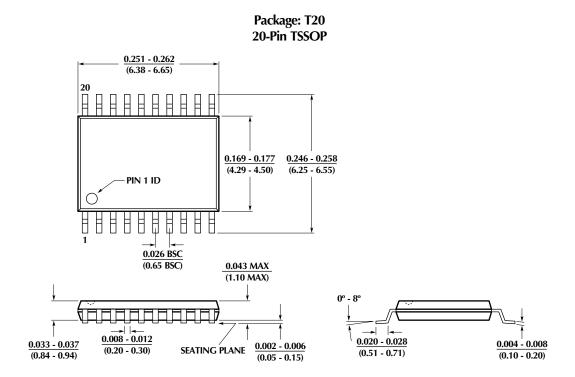

### PIN CONFIGURATION

#### ML2751 20-Pin TSSOP (T20)

## PIN DESCRIPTIONS

| Pin #       | Signal Name | І/О Туре   | Description                                                                                                                                                                                                                                                                                                           |

|-------------|-------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LNA Section |             |            |                                                                                                                                                                                                                                                                                                                       |

| 5           | RRFO        | O (analog) | Receive RF Output. LNA RF Output. This is an open collector output that requires an external load to VCC. This pin requires matching for optimum gain                                                                                                                                                                 |

| 11          | RLNI        | I (analog) | Receive LNA RF input. This pin is directly connected to the base of an NPN transistor. The input to this pin should be AC coupled using an external capacitor. This input will require matching for optimum performance                                                                                               |

| PA Section  |             |            |                                                                                                                                                                                                                                                                                                                       |

| 3           | TRFI        | I (analog) | Transmit RF Power Amplifier (PA) input. Requires RF choke to VCC that can handle up to 150mA. The VCC end of the choke requires both RF and low frequency decoupling to ground to minimize supply modulation                                                                                                          |

| 9           | TPS         | I (analog) | This pin is the non-inverting input of an op amp. The voltage on this pin sets the RF power produced by the PA, permitting variable power operation under control of the baseband circuits (see Figure 2)                                                                                                             |

| 10          | TPA         | I (analog) | This pin is the inverting input of an operational amplifier. A resistor from this pin to GND scales the TPS input voltage control range to match that of the external baseband control circuits. If scaling of the TPS input range is not required the TPA pin can either be grounded or left floating (see Figure 2) |

| 18          | TRFO        | O (analog) | Transmit RF Power Amplifier output. Open collector output. Requires RF choke to VCC that can handle up to 150mA. The VCC end of the choke requires both RF and low frequency decoupling to ground to minimize supply modulation                                                                                       |

| PIN D       | ESCRIPTIONS    | (continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|----------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin #       | Signal Name    | I/O         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PIN Diode   | Driver Section |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 12          | PIN            | O (analog)  | This output is a low impedance voltage source that switches between VCC and GND to drive an external PIN diode switch. This totem pole output is tri-stated when FEEN = 0. When active it pulls either to VCC (if PAON = 1) or to GND (if PAON = 0), and has a nominal output impedance of $50\Omega$ when sourcing and $120\Omega$ when sinking                                                                                                    |

| 13          | PINB           | O (analog)  | This output is a low impedance voltage source that switches between VCC and GND to drive an external PIN diode switch. This totem pole output is tri-stated when FEEN = 0. When active it pulls either to VCC (if PAON = 0) or to GND (if PAON = 1) , and has a nominal output impedance of $50\Omega$ when sourcing and $120\Omega$ when sinking. PINB is the complement of PIN, providing a bipolar drive for PIN diodes from a single power rail |

| Control and | Interface      |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1           | PAON           | I (CMOS)    | Power Amplifier on pin. The PA is active when PAON = 1, and the LNA is active when PAON = 0. Rising and falling edges of this signal initiate a controlled ramp of the PA bias circuits to eliminate AM generated sidebands on the transmitter output. The PIN diode drivers are synchronized with PAON (see Figure 3). When the ML2751 is in standby mode this pin has no effect                                                                   |

| 2           | FEEN           | I (CMOS)    | Front-end enable. FEEN is the master power down pin. When FEEN = 0 the ML2751 is in standby mode. When FEEN = 1 either the PA or the LNA is enabled (determined by the state of PAON). See Figure 3                                                                                                                                                                                                                                                 |

| Power & Gro | ound           |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15          | VCC            | Power       | Positive power supply for the LNA, the first stages of the PA, the PIN diode drivers, and the control logic. Care should be exercised in PCB layout to minimize the trace length, and the inductance and resistance both in the connection to the capacitor and from the capacitor to ground                                                                                                                                                        |

| 4           | GND            | Ground      |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6           | GND            | Ground      |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7           | GND            | Ground      |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8           | GND            | Ground      |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 14          | GND            | Ground      |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 16          | GND            | Ground      |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 17          | GND            | Ground      |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 19          | GND            | Ground      |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 20          | GND            | Ground      |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### **FUNCTIONAL DESCRIPTION**

#### **TRANSMIT FUNCTIONALITY**

#### **Power Amplifier**

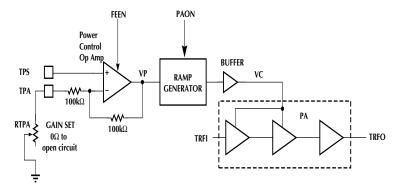

The power amplifier (PA) consists of three cascaded gain stages. The last stage (output stage) is powered directly from the unregulated supply to increase end-product battery life. The TPS and TPA pins are used to control its output power. The TPS and TPA pins are connected to an internal power control op amp as shown in Figure 1. The op amp's output voltage (VP) determines the PA's gain. The voltage at VP drives a buffer that serves as a collector supply for the first two stages of the power amplifier.

A ramp generator circuit between the power control op amp and the buffer facilitates a gradual transition from the on-state to the off-state of the PA on the rising/falling edge of the PAON signal.

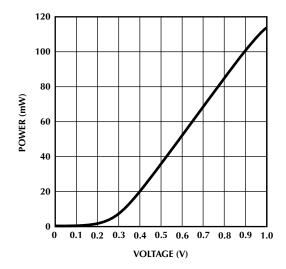

The DC voltage on the TPS pin determines VP, and may be varied between 0V and 1V, with a nominal 100mW/V sensitivity to this pin as shown in Figure 2. To compensate for the IC manufacturing process variations of the power amplifier the TPS voltage can be scaled by varying the resistance between the TPA pin and ground. The value of

Figure 1. PA Power Setting and Ramp Generator

Figure 2. Output vs. TPS Curve

resistor RTPA effectively determines the gain of the op amp. RTPA can range in value from  $0\Omega$  to open circuit. For +20dBm output power the typical full-scale signal on the TPS will lie between 0.5V and 1V with TPA grounded.

#### **RECEIVE FUNCTIONALITY**

#### **Low Noise Amplifier (LNA)**

The LNA is a two-stage transistor amplifier designed with internal inter-stage impedance matching. The output is an open collector that requires a load to a DC supply and external matching. All associated bias circuits are integrated internally. The LNA is controlled by the PAON signal, as shown in Figure 3.

A nominal gain of 20dB and a noise figure of 2.5dB complement the ML2721, optimizing the balance between sensitivity and high signal performance. The open-collector LNA output provides flexibility in matching the impedance that an RF filter presents to the LNA. The input can be matched for low noise using a small value series capacitor, and the two-stage design minimizes the interaction between the input and output match. The RF filter is placed between the ML2751 and the ML2721.

#### **PIN Diode Driver**

A pair of driver circuits is used to drive an external PIN diode Transmit/Receive switch. The PIN diode drivers are controlled from the timer's internal enable signals. The PIN and PINB output pins act as low impedance voltage sources that switch between VCC and GND, with the ability to both source and sink current.

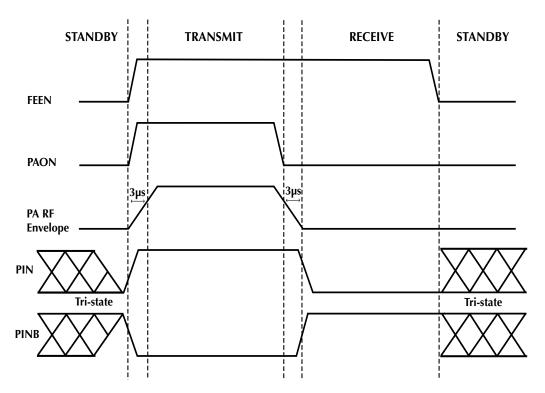

The PIN and PINB outputs are under control of the FEEN and PAON control input pins (see Figure 3). The switching between the transmit and receive paths is synchronized with the PA ramp function, so that the transmit path is selected at the rising edge of the transmit ramp (when PAON = 1) and held until the PA has ramped down (about  $3\mu$ s after PAON = 0).

Simple PIN diode switches can be driven directly, without the need for current limiting resistors, as each output has a nominal  $100\Omega$  series impedance. This reduces the total component count. For more complex (or lower power) switches individual current limiting resistors may be used, forcing the PIN and PINB pins to act as voltage sources. The total current drawn from each output must not exceed the current source/sink specification limits.

### **FUNCTIONAL DESCRIPTION**

# OPERATION MODES AND CONTROL INTERFACE DESCRIPTION

The signals FEEN and PAON determine the mode of operation. The three standard modes of operation are STANDBY, TRANSMIT, and RECEIVE. The control logic is shown in Table 1.

STANDBY: All circuits are off (LNA bias off), PIN driver outputs are Tri-stated.

TRANSMIT: PA and the PIN diode drivers are enabled. The LNA is off (zero current).

RECEIVE: The LNA bias circuits and the PIN diode drivers are enabled, PA is disabled.

In addition to the two mode control inputs, FEEN and PAON, there is an analog voltage input that can be used to set the power output of the amplifier. The voltage range

required to set the output power level can be controlled by an external resistor.

Note that the ML2751 has an internal power amplifier ramp-on and ramp-off circuit. The power amplifier turn on/off relative to the ramp is shown in Figure 3. The ramp-on starts when the PA is enabled, the ramp-off starts when it is disabled.

Two outputs, PIN and PINB, are provided from the ML2751 to drive the external PIN diodes in the Transmit/ Receive switch. The timing for these voltage outputs is shown in Figure 3 relative to the control pins FEEN and PAON.

Figure 3. Signals vs. Mode Relationships

| FEEN | PAON | Mode     | PIN       | PINB      | LNA | PA  |

|------|------|----------|-----------|-----------|-----|-----|

| 0    | X    | STANDBY  | Tri-state | Tri-state | Off | Off |

| 1    | 0    | RECEIVE  | VCC/-10mA | VCC/+10mA | On  | Off |

| 1    | 1    | TRANSMIT | VCC/+10mA | VCC/-10mA | Off | On  |

**Table 1. Control Logic**

### **ELECTRICAL CHARACTERISTICS**

### **ABSOLUTE MAXIMUM RATINGS**

#### Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

| Junction Temperature              | 150°C                      |

|-----------------------------------|----------------------------|

| Storage Temperature Range         |                            |

| Lead Temperature (Soldering, 10s) | 260℃                       |

| Thermal Resistance )              |                            |

| Input Voltage, VCC Pin            | 6.0V                       |

| Input Voltage, GND Pin            | 0.3V to 0.3V               |

| Input Voltage, Other Pins         | $-0.3V$ to $V_{CC} + 0.3V$ |

### **OPERATING CONDITIONS**

| Normal Temperature Range | 10°C to 60°C |

|--------------------------|--------------|

| VCC Range                |              |

| Thermal Resistance       |              |

### **ELECTRICAL TABLES**

Unless otherwise specified, VCC = 3.3V,  $T_A$  = Operating Temperature Range. (Note 1)

| SYMBOL    | PARAMETER                              | CONDITIONS                                      | MIN | TYP  | MAX | UNITS |

|-----------|----------------------------------------|-------------------------------------------------|-----|------|-----|-------|

| GENERAL   | SPECIFICATIONS                         |                                                 |     |      |     |       |

| VCC       | Supply Voltage                         |                                                 | 3.0 | 3.3  | 4.5 | V     |

| ICC       | Supply Current                         |                                                 |     | 20   |     | μΑ    |

| tON       | Turn on time                           | Standby to Transmit or Receive (Note            | 2)  | 3    |     | μs    |

| tSW       | Turn around time                       | Transmit to Receive/<br>Receive to Transmit     |     | 3    |     | μs    |

| Tx ICC    | Transmit active current                | 3v, FEEN & PAON high, P <sub>OUT</sub> = +20dBm |     | 110  |     | mA    |

|           |                                        | 3v, FEEN & PAON high, P <sub>OUT</sub> = 0dBm   |     | 15   |     | mA    |

| Rx ICC    | Receive active current                 | 3v, FEEN & PAON low                             |     | 4    |     | mA    |

| TRANSMI   | F POWER AMPLIFIER                      |                                                 |     |      |     |       |

| PMAX      | Maximum output power                   | TPS = 1.0V (Note 3), Input power 0dBm           |     | 20.5 |     | dBm   |

| PMID      | Mid range output power                 | TPS = 0.3V (Note 3)                             |     | 10   |     | dBm   |

| PMIN      | Low output power                       | TPS = 0.15V (Note 3)                            |     | 0    |     | dBm   |

| PGAIN     | Power gain                             | Maximum power setting                           |     | 37   |     | dB    |

| RECEIVE L | OW NOISE AMPLIFIER                     |                                                 |     |      |     |       |

| GAIN      | Power gain                             | Input power <-30dBm                             |     | 18   |     | dB    |

| NF        | Noise figure                           |                                                 |     | 2.5  |     | dB    |

| IP3       | 3 <sup>rd</sup> -order intercept point |                                                 |     | -15  |     | dBm   |

| P1dB      | 1dB compression point                  |                                                 |     | -25  |     | dBm   |

| P1dB      | 1dB compression point                  |                                                 |     | -25  |     |       |

# **PRELIMINARY**

## **ELECTRICAL TABLES** (Continued)

| SYMBOL   | PARAMETER   | CONDITIONS | MIN | TYP             | MAX | UNITS |

|----------|-------------|------------|-----|-----------------|-----|-------|

| PIN DIOD | DE DRIVERS  |            |     |                 |     |       |

| VOUT     | High<br>Low |            |     | VCC -0.3<br>0.3 |     | V     |

| IOUT     | High<br>Low |            |     | 10<br>–10       |     | mA    |

Note 1: Limits are guaranteed by 100% testing, sampling, or correlation with worst case test conditions.

Note 2: PA turn on is measured from the rising edge of either PAON or FEEN to 90% of the programmed power output.

Note 3: PA power measurements are made at the output of the external harmonic filter under the following conditions: 0dBm input drive at 915MHz; the resistor on TPA is set for +20dBm ±0.5dB output power; the TPS signal is 1V.

### PHYSICAL DIMENSIONS

### ORDERING INFORMATION

| PART NUMBER | TEMPERATURE RANGE | PACKAGE       |

|-------------|-------------------|---------------|

| ML2751DT    | −10°C to 60°C     | 20P Pin TSSOP |

Micro Linear Corporation 2092 Concourse Drive San Jose, CA 95131 Tel: (408) 433-5200 Fax: (408) 432-0295

www.microlinear.com