#### CDS/AGC & 10-bit A/D Converter

## **HITACHI**

ADE-207-262A (Z) 2nd Edition Apr. 1999

#### **Description**

The HD49323AF-01 is a CMOS IC that provides CCD-AGC analog processing (CDS/AGC) suitable for CCD camera digital signal processing systems together with a 10-bit A/D converter in a single chip.

#### **Functions**

- Correlated Double Sampling

- AGC

- Sample hold

- Offset compensation

- Serial interface control

- 10-bit ADC

- 3 V single operation (2.7 V to 3.6 V)

- Power dissipation: 198 mW (Typ)

- Maximum frequency: 20 MHz (Min)

#### **Features**

- Good suppression of CCD output low-frequency noise is achieved through the use of S/H type correlated double sampling.

- A high S/N ratio is achieved through the use of a AGC type amplifier, and high sensitivity is provided by a wide cover range.

- An auto offset circuit provides compensation of output DC offset voltage fluctuations due to variations in AGC amplifier gain.

- AGC, standby mode, offset control, etc., is possible via a serial interface.

- High precision is provided by a 10-bit-resolution A/D converter.

- Version of Hitachi's previous-generation HD49322BF with improved functions and performance, including in particular an approximately 3.0 dB improvement in S/N.

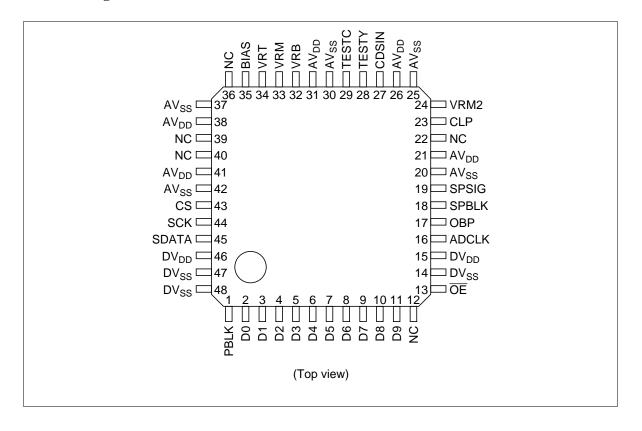

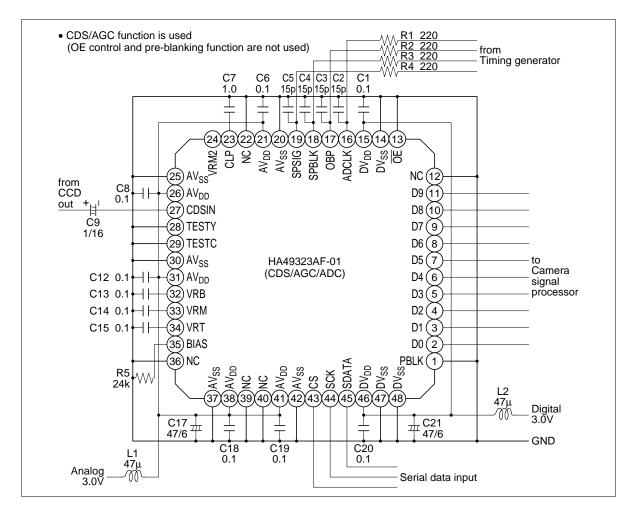

### **Pin Arrangement**

## **Pin Description**

| 1         PBLK         Pre-blanking pin         I         D           2         D0         Digital output (LSB)         O         D           3 to 10         D1 to D8         Digital output (MSB)         O         D           11         D9         Digital output (MSB)         O         D           12         NC         No connection pin         —         —           13         OE         Digital output enable control pin         I         D           14         DV <sub>ss</sub> Digital ground (0 V)         —         D           15         DV <sub>ss</sub> Digital power supply (3 V)<br>Connect off-chip in common with AV <sub>co</sub> .         —         D           16         ADCLK         ADC conversion clock input pin         I         D           17         OBP         Optical black pulse input pin         I         D           18         SPBLK         Black level sampling clock input pin         I         D           19         SPSIG         Signal level sampling clock input pin         I         D           20         AV <sub>ss</sub> Analog ground (0 V)         —         A           21         AV <sub>co</sub> Analog power supply (3 V)<br>Connect off-chip in common with DV <sub>co</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Pin No. | Symbol             | Description                                   | I/O | Analog(A) or<br>Digital(D) |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|-----------------------------------------------|-----|----------------------------|

| 3 to 10         D1 to D8         Digital output         O         D           11         D9         Digital output (MSB)         O         D           12         NC         No connection pin         —         —           13         OE         Digital output enable control pin         I         D           14         DV <sub>ss</sub> Digital pround (0 V)         —         D           15         DV <sub>ss</sub> Digital power supply (3 V)<br>Connect off-chip in common with AV <sub>sp</sub> .         —         D           16         ADCLK         ADC conversion clock input pin         I         D           17         OBP         Optical black pulse input pin         I         D           18         SPBLK         Black level sampling clock input pin         I         D           19         SPSIG         Signal level sampling clock input pin         I         D           20         AV <sub>ss</sub> Analog ground (0 V)         —         A           21         AV <sub>ss</sub> Analog power supply (3 V)         —         A           22         NC         No connection pin         —         —         A           23         CLP         Clamp voltage pin common with DV po         —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1       | PBLK               | Pre-blanking pin                              | I   | D                          |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2       | D0                 | Digital output (LSB)                          | 0   | D                          |

| 12 NC No connection pin — — —  13 OE Digital output enable control pin I D  14 DV <sub>ss</sub> Digital ground (0 V) — D  15 DV <sub>DD</sub> Digital power supply (3 V) — D  16 ADCLK ADC conversion clock input pin I D  17 OBP Optical black pulse input pin I D  18 SPBLK Black level sampling clock input pin I D  19 SPSIG Signal level sampling clock input pin I D  20 AV <sub>ss</sub> Analog ground (0 V) — A  21 AV <sub>DD</sub> Analog power supply (3 V) — A  22 NC No connect off-chip in common with DV <sub>DD</sub> .  23 CLP Clamp voltage pin Connect a 0.22 μF or more capacitor between CLP and AV <sub>ss</sub> .  24 VRM2 Reference voltage pin (for CCD offset cancel) — A  25 AV <sub>ss</sub> Analog ground (0 V) — A  26 AV <sub>Ss</sub> Analog ground (0 V) — A  27 CDSIN CDS input pin I A  28 TESTY Test input pin-Y I A  29 TESTC Test input pin-C  30 AV <sub>ss</sub> Analog power supply (3 V) — A  31 AV <sub>DD</sub> Analog power supply (3 V) — A  32 VRB Reference voltage pin 3  Connect off-chip in common with DV <sub>DD</sub> .  33 VRM Reference voltage pin 3  Connect off-chip in common with DV <sub>DD</sub> .  34 VRT Reference voltage pin 2  Connect of 1. μF ceramic capacitor between VRM and AV <sub>ss</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3 to 10 | D1 to D8           | Digital output                                | 0   | D                          |

| DE   Digital output enable control pin   I   D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11      | D9                 | Digital output (MSB)                          | 0   | D                          |

| 14 DV <sub>SS</sub> Digital ground (0 V) — D  15 DV <sub>DD</sub> Digital power supply (3 V) — D  16 ADCLK ADC conversion clock input pin I D  17 OBP Optical black pulse input pin I D  18 SPBLK Black level sampling clock input pin I D  19 SPSIG Signal level sampling clock input pin I D  20 AV <sub>SS</sub> Analog ground (0 V) — A  21 AV <sub>DD</sub> Analog power supply (3 V) — A  22 NC No connection pin — — —  23 CLP Clamp voltage pin Connect a 0.22 µF or more capacitor between CLP and AV <sub>SS</sub> .  24 VRM2 Reference voltage pin (for CCD offset cancel) — A  25 AV <sub>SS</sub> Analog ground (0 V) — A  26 AV <sub>DD</sub> Analog power supply (3 V) — A  27 CDSIN CDS input pin I A  28 TESTY Test input pin-Y I A  29 TESTC Test input pin-C I A  30 AV <sub>SS</sub> Analog ground (0 V) — A  31 AV <sub>DD</sub> Analog power supply (3 V) — A  32 VRB Reference voltage pin 3 Connect off-chip in common with DV <sub>DD</sub> .  33 VRM Reference voltage pin 2 — A  24 VRM Reference voltage pin 2 Connect a 0.1 µF ceramic capacitor between VRB and AV <sub>SS</sub> .  34 VRT Reference voltage pin 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12      | NC                 | No connection pin                             | _   | _                          |

| DV   Digital power supply (3 V)   Connect off-chip in common with AV   Connect off-chip in common with DV   Connect off   | 13      | ŌĒ                 | Digital output enable control pin             | I   | D                          |

| Connect off-chip in common with AV <sub>DD</sub> .  16 ADCLK ADC conversion clock input pin I D  17 OBP Optical black pulse input pin I D  18 SPBLK Black level sampling clock input pin I D  19 SPSIG Signal level sampling clock input pin I D  20 AV <sub>SS</sub> Analog ground (0 V) — A  21 AV <sub>DD</sub> Analog power supply (3 V) — A  22 NC No connect off-chip in common with DV <sub>DD</sub> .  23 CLP Clamp voltage pin Connect a 0.22 μF or more capacitor between CLP and AV <sub>SS</sub> .  24 VRM2 Reference voltage pin (for CCD offset cancel) — A  25 AV <sub>SS</sub> Analog ground (0 V) — A  26 AV <sub>DD</sub> Analog power supply (3 V) — A  27 CDSIN CDS input pin I A  28 TESTY Test input pin-Y I A  30 AV <sub>SS</sub> Analog ground (0 V) — A  31 AV <sub>DD</sub> Analog power supply (3 V) — A  32 VRB Reference voltage pin 3  Connect off-chip in common with DV <sub>DD</sub> .  32 VRB Reference voltage pin 2  Connect a 0.1 μF ceramic capacitor between VRB and AV <sub>SS</sub> .  34 VRT Reference voltage pin 1 — A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14      | $DV_{SS}$          | Digital ground (0 V)                          | _   | D                          |

| 17 OBP Optical black pulse input pin I D  18 SPBLK Black level sampling clock input pin I D  19 SPSIG Signal level sampling clock input pin I D  20 AV <sub>ss</sub> Analog ground (0 V) — A  21 AV <sub>DD</sub> Analog power supply (3 V) — A  22 NC No connect off-chip in common with DV <sub>DD</sub> .  23 CLP Clamp voltage pin Connect a 0.22 μF or more capacitor between CLP and AV <sub>ss</sub> .  24 VRM2 Reference voltage pin (for CCD offset cancel) — A  25 AV <sub>ss</sub> Analog ground (0 V) — A  26 AV <sub>DD</sub> Analog power supply (3 V) — A  27 CDSIN CDS input pin I A  28 TESTY Test input pin-Y I A  29 TESTC Test input pin-Y I A  30 AV <sub>ss</sub> Analog ground (0 V) — A  31 AV <sub>DD</sub> Analog power supply (3 V) — A  32 VRB Reference voltage pin 3  Connect off-chip in common with DV <sub>DD</sub> .  33 VRM Reference voltage pin 3  Connect a 0.1 μF ceramic capacitor between VRB and AV <sub>ss</sub> .  34 VRT Reference voltage pin 1 — A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15      | $DV_{DD}$          |                                               | _   | D                          |

| 18 SPBLK Black level sampling clock input pin I D  19 SPSIG Signal level sampling clock input pin I D  20 AV <sub>ss</sub> Analog ground (0 V) — A  21 AV <sub>DD</sub> Analog power supply (3 V) — A  22 NC No connect off-chip in common with DV <sub>DD</sub> .  23 CLP Clamp voltage pin — — A  24 VRM2 Reference voltage pin (for CCD offset cancel) — A  25 AV <sub>ss</sub> Analog ground (0 V) — A  26 AV <sub>DD</sub> Analog power supply (3 V) — A  27 CDSIN CDS input pin I A  28 TESTY Test input pin-Y I A  29 TESTC Test input pin-C I A  30 AV <sub>ss</sub> Analog ground (0 V) — A  31 AV <sub>DD</sub> Analog power supply (3 V) — A  32 VRB Reference voltage pin 3  Connect off-chip in common with DV <sub>DD</sub> .  32 VRB Reference voltage pin 3  Connect a 0.1 μF ceramic capacitor between VRB and AV <sub>ss</sub> .  33 VRM Reference voltage pin 1 — A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 16      | ADCLK              | ADC conversion clock input pin                | I   | D                          |

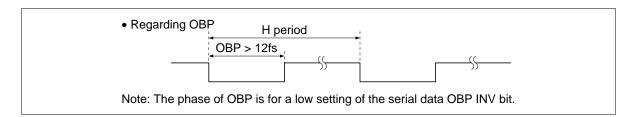

| 19 SPSIG Signal level sampling clock input pin I D 20 AV <sub>ss</sub> Analog ground (0 V) — A 21 AV <sub>oo</sub> Analog power supply (3 V) — A 22 NC No connect off-chip in common with DV <sub>oo</sub> .  23 CLP Clamp voltage pin Connect a 0.22 μF or more capacitor between CLP and AV <sub>ss</sub> .  24 VRM2 Reference voltage pin (for CCD offset cancel) — A 25 AV <sub>ss</sub> Analog ground (0 V) — A 26 AV <sub>oo</sub> Analog power supply (3 V) — A 27 CDSIN CDS input pin I A 28 TESTY Test input pin-Y I A 29 TESTC Test input pin-C I A 30 AV <sub>ss</sub> Analog ground (0 V) — A 31 AV <sub>oo</sub> Analog power supply (3 V) — A 32 VRB Reference voltage pin 3 — A 33 VRM Reference voltage pin 3 — A 34 VRT Reference voltage pin 2 — A 35 VRM Reference voltage pin 2 — A 36 VRT Reference voltage pin 2 — A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 17      | OBP                | Optical black pulse input pin                 | I   | D                          |

| 20 AV <sub>ss</sub> Analog ground (0 V) — A 21 AV <sub>DD</sub> Analog power supply (3 V) Connect off-chip in common with DV <sub>DD</sub> .  22 NC No connection pin — — A 23 CLP Clamp voltage pin Connect a 0.22 μF or more capacitor between CLP and AV <sub>ss</sub> .  24 VRM2 Reference voltage pin (for CCD offset cancel) — A 25 AV <sub>ss</sub> Analog ground (0 V) — A 26 AV <sub>DD</sub> Analog power supply (3 V) Connect off-chip in common with DV <sub>DD</sub> .  27 CDSIN CDS input pin I A 28 TESTY Test input pin-Y I A 29 TESTC Test input pin-C I A 30 AV <sub>ss</sub> Analog ground (0 V) — A 31 AV <sub>DD</sub> Analog power supply (3 V) Connect off-chip in common with DV <sub>DD</sub> .  32 VRB Reference voltage pin 3 Connect off-chip in common with DV <sub>DD</sub> .  33 VRM Reference voltage pin 2 Connect a 0.1 μF ceramic capacitor between VRB and AV <sub>ss</sub> .  34 VRT Reference voltage pin 1  — A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 18      | SPBLK              | Black level sampling clock input pin          | I   | D                          |

| Analog power supply (3 V) Connect off-chip in common with DV Connect a 0.22 μF or more capacitor between CLP and AV Connect a 0.22 μF or more capacitor between CLP and AV Connect a 0.22 μF or more capacitor between CLP and AV Connect a 0.22 μF or more capacitor between CLP and AV Connect a 0.22 μF or more capacitor between CLP and AV Connect a 0.22 μF or more capacitor between CLP and AV Connect a A CDS in AV CDS in Ax CDS in put pin in common with DV CDD CDS input pin in Ax CDS input pin-Y CDS input pin-Y CDS input pin-Y CDS input pin-C CDS input | 19      | SPSIG              | Signal level sampling clock input pin         | I   | D                          |

| Connect off-chip in common with DV <sub>DD</sub> .  22 NC No connection pin — — —  23 CLP Clamp voltage pin Connect a 0.22 μF or more capacitor between CLP and AV <sub>SS</sub> .  24 VRM2 Reference voltage pin (for CCD offset cancel) — A  25 AV <sub>SS</sub> Analog ground (0 V) — A  26 AV <sub>DD</sub> Analog power supply (3 V) — A  27 CDSIN CDS input pin I A  28 TESTY Test input pin-Y I A  29 TESTC Test input pin-C I A  30 AV <sub>SS</sub> Analog ground (0 V) — A  31 AV <sub>DD</sub> Analog power supply (3 V) — A  32 VRB Reference voltage pin 3 — A  33 VRM Reference voltage pin 2 — A  34 VRT Reference voltage pin 1 — A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20      | $AV_{\mathtt{SS}}$ | Analog ground (0 V)                           | _   | A                          |

| CLP Clamp voltage pin Connect a 0.22 μF or more capacitor between CLP and AV <sub>ss</sub> .  24 VRM2 Reference voltage pin (for CCD offset cancel) — A  25 AV <sub>ss</sub> Analog ground (0 V) — A  26 AV <sub>DD</sub> Analog power supply (3 V) — A  27 CDSIN CDS input pin I A  28 TESTY Test input pin-Y I A  29 TESTC Test input pin-C I A  30 AV <sub>ss</sub> Analog ground (0 V) — A  31 AV <sub>DD</sub> Analog ground (0 V) — A  32 VRB Reference voltage pin 3  Connect off-chip in common with DV <sub>DD</sub> .  32 VRB Reference voltage pin 2  Connect a 0.1 μF ceramic capacitor between VRM and AV <sub>ss</sub> .  34 VRT Reference voltage pin 1 — A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21      | $AV_{DD}$          |                                               | _   | Α                          |

| Connect a 0.22 μF or more capacitor between CLP and AV <sub>ss</sub> .  24 VRM2 Reference voltage pin (for CCD offset cancel) — A  25 AV <sub>ss</sub> Analog ground (0 V) — A  26 AV <sub>DD</sub> Analog power supply (3 V) Connect off-chip in common with DV <sub>DD</sub> .  27 CDSIN CDS input pin I A  28 TESTY Test input pin-Y I A  29 TESTC Test input pin-C I A  30 AV <sub>ss</sub> Analog ground (0 V) — A  31 AV <sub>DD</sub> Analog power supply (3 V) Connect off-chip in common with DV <sub>DD</sub> .  32 VRB Reference voltage pin 3 Connect a 0.1 μF ceramic capacitor between VRB and AV <sub>ss</sub> .  33 VRM Reference voltage pin 1  34 VRT Reference voltage pin 1  36 AV <sub>ss</sub> Analog power supply (3 V) Connect a 0.1 μF ceramic capacitor between VRM and AV <sub>ss</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 22      | NC                 | No connection pin                             | _   | _                          |

| 25 AV <sub>ss</sub> Analog ground (0 V) — A 26 AV <sub>DD</sub> Analog power supply (3 V) Connect off-chip in common with DV <sub>DD</sub> .  27 CDSIN CDS input pin I A 28 TESTY Test input pin-Y I A 29 TESTC Test input pin-C I A 30 AV <sub>ss</sub> Analog ground (0 V) — A 31 AV <sub>DD</sub> Analog power supply (3 V) Connect off-chip in common with DV <sub>DD</sub> .  32 VRB Reference voltage pin 3 Connect a 0.1 μF ceramic capacitor between VRB and AV <sub>ss</sub> .  33 VRM Reference voltage pin 2 Connect a 0.1 μF ceramic capacitor between VRM and AV <sub>ss</sub> .  34 VRT Reference voltage pin 1 — A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23      | CLP                |                                               | _   | A                          |

| 26AV<br>DDAnalog power supply (3 V)<br>Connect off-chip in common with DV<br>DD.—A27CDSINCDS input pinIA28TESTYTest input pin-YIA29TESTCTest input pin-CIA30AV<br>ssAnalog ground (0 V)—A31AV<br>DDAnalog power supply (3 V)<br>Connect off-chip in common with DV<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 24      | VRM2               | Reference voltage pin (for CCD offset cancel) | _   | A                          |

| Connect off-chip in common with DV <sub>DD</sub> .  27 CDSIN CDS input pin I A  28 TESTY Test input pin-Y I A  29 TESTC Test input pin-C I A  30 AV <sub>ss</sub> Analog ground (0 V) — A  31 AV <sub>DD</sub> Analog power supply (3 V) Connect off-chip in common with DV <sub>DD</sub> .  32 VRB Reference voltage pin 3 Connect a 0.1 μF ceramic capacitor between VRB and AV <sub>ss</sub> .  33 VRM Reference voltage pin 2 Connect a 0.1 μF ceramic capacitor between VRM and AV <sub>ss</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 25      | AV <sub>SS</sub>   | Analog ground (0 V)                           |     | A                          |

| TESTY Test input pin-Y  1 A  29 TESTC Test input pin-C  1 A  30 AV <sub>ss</sub> Analog ground (0 V) — A  31 AV <sub>DD</sub> Analog power supply (3 V) Connect off-chip in common with DV <sub>DD</sub> .  32 VRB Reference voltage pin 3 Connect a 0.1 μF ceramic capacitor between VRB and AV <sub>ss</sub> .  33 VRM Reference voltage pin 2 Connect a 0.1 μF ceramic capacitor between VRM and AV <sub>ss</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26      | $AV_{DD}$          | •                                             | _   | Α                          |

| TESTC Test input pin-C I A  ANO AV <sub>SS</sub> Analog ground (0 V) — A  Analog power supply (3 V) Connect off-chip in common with DV <sub>DD</sub> .  VRB Reference voltage pin 3 Connect a 0.1 μF ceramic capacitor between VRB and AV <sub>SS</sub> .  VRM Reference voltage pin 2 Connect a 0.1 μF ceramic capacitor between VRM and AV <sub>SS</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27      | CDSIN              | CDS input pin                                 | I   | A                          |

| 30 AV <sub>ss</sub> Analog ground (0 V) — A  31 AV <sub>DD</sub> Analog power supply (3 V) — A  32 VRB Reference voltage pin 3 — A  Connect a 0.1 μF ceramic capacitor between VRB and AV <sub>ss</sub> .  33 VRM Reference voltage pin 2 — A  Connect a 0.1 μF ceramic capacitor between VRM and AV <sub>ss</sub> .  34 VRT Reference voltage pin 1 — A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 28      | TESTY              | Test input pin-Y                              | I   | A                          |

| Analog power supply (3 V) Connect off-chip in common with DV <sub>DD</sub> .  32 VRB Reference voltage pin 3 Connect a 0.1 μF ceramic capacitor between VRB and AV <sub>SS</sub> .  33 VRM Reference voltage pin 2 Connect a 0.1 μF ceramic capacitor between VRM and AV <sub>SS</sub> .  34 VRT Reference voltage pin 1  A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 29      | TESTC              | Test input pin-C                              | I   | A                          |

| Connect off-chip in common with DV <sub>DD</sub> .  32 VRB Reference voltage pin 3 — A Connect a 0.1 μF ceramic capacitor between VRB and AV <sub>SS</sub> .  33 VRM Reference voltage pin 2 — A Connect a 0.1 μF ceramic capacitor between VRM and AV <sub>SS</sub> .  34 VRT Reference voltage pin 1 — A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 30      | $AV_{\mathtt{SS}}$ | Analog ground (0 V)                           | _   | Α                          |

| Connect a 0.1 μF ceramic capacitor between VRB and AV <sub>ss</sub> .  33 VRM Reference voltage pin 2 — A Connect a 0.1 μF ceramic capacitor between VRM and AV <sub>ss</sub> .  34 VRT Reference voltage pin 1 — A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31      | $AV_{DD}$          |                                               | _   | A                          |

| Connect a 0.1 µF ceramic capacitor between VRM and AV <sub>ss</sub> .  34 VRT Reference voltage pin 1 — A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32      | VRB                |                                               | _   | А                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33      | VRM                |                                               | _   | Α                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 34      | VRT                |                                               | _   | Α                          |

## Pin Description (cont)

| Pin No. | Symbol           | Description                                                                               | 1/0 | Analog(A) or<br>Digital(D) |

|---------|------------------|-------------------------------------------------------------------------------------------|-----|----------------------------|

| 35      | BIAS             | Internal bias pin Connect a 24 $k\Omega$ resistor between BIAS and $\text{AV}_\text{SS}.$ | _   | A                          |

| 36      | NC               | No connection pin                                                                         | _   | _                          |

| 37      | AV <sub>SS</sub> | Analog ground (0 V)                                                                       | _   | A                          |

| 38      | $AV_{DD}$        | Analog power supply (3 V) Connect off-chip in common with DV <sub>DD</sub> .              | _   | A                          |

| 39, 40  | NC               | No connection pin                                                                         | _   | _                          |

| 41      | $AV_{DD}$        | Analog power supply (3 V) Connect off-chip in common with DV <sub>DD</sub> .              | _   | A                          |

| 42      | AV <sub>SS</sub> | Analog ground (0 V)                                                                       | _   | A                          |

| 43      | CS               | Serial interface control input pin                                                        | I   | D                          |

| 44      | SCK              | Serial clock input pin                                                                    | I   | D                          |

| 45      | SDATA            | Serial data input pin                                                                     | 1   | D                          |

| 46      | $DV_{DD}$        | Digital power supply (3 V) Connect off-chip in common with AV <sub>DD</sub> .             | _   | D                          |

| 47, 48  | $DV_{SS}$        | Digital ground (0 V)                                                                      | _   | D                          |

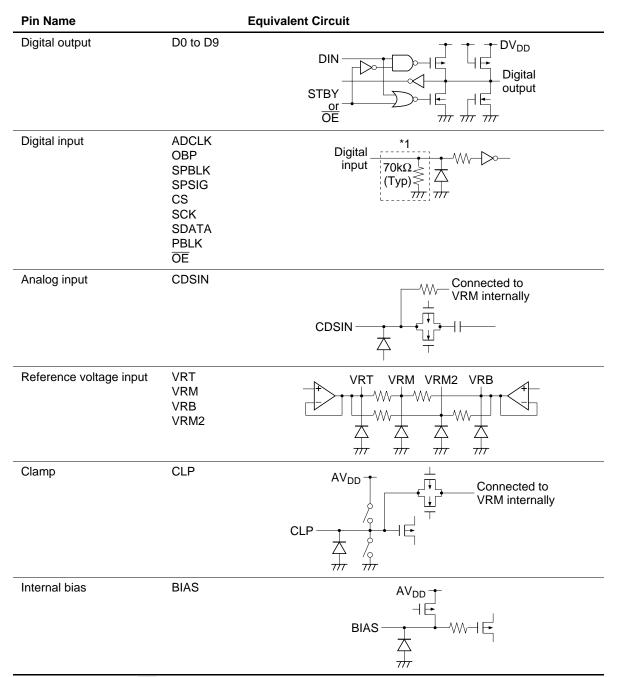

### **Input/Output Equivalent Circuit**

Note: 1. Applies to OE and PBLK.

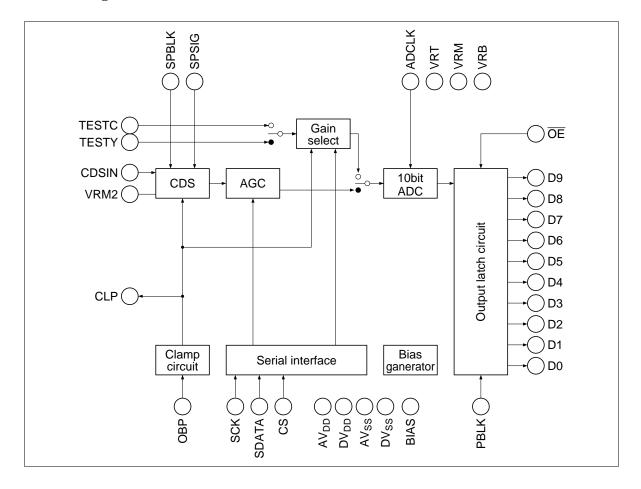

## **Block Diagram**

#### **Internal Functions**

#### **Functional Description**

- CDS (Correlated Double Sampling) circuit

- AGC gain selection (11-bit digital control) \*1

- AGC gain can be set in the range 0 dB to 34.7 dB on the (+) side, and -3.3 dB to 0 dB on the (-) side by means of 11-bit serial data.

- Automatic offset adjustment is possible for the IC's offsets (CDS, AGC, ADC) by means of serial data control at power-on.\*<sup>1</sup>

- Digital output enable function

- Pre-blanking function

- Digital output can be fixed at 32 LSB

- CDS offset cancel function

Note: 1. Serial data control

#### **Operating Description**

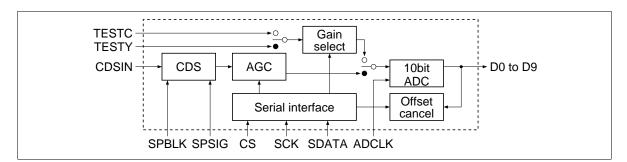

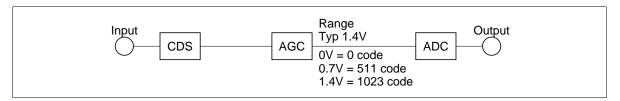

Figure 1 shows CDS/AGC +ADC function block.

Figure 1 CDS/AGC +ADC Function Block

1. CDS (Correlated Double Sampling) Circuit

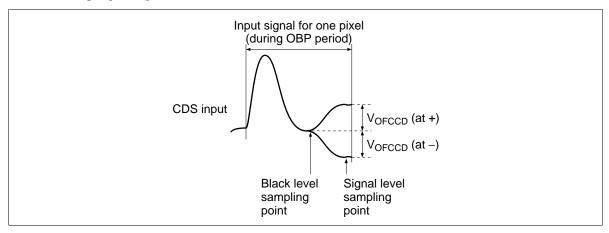

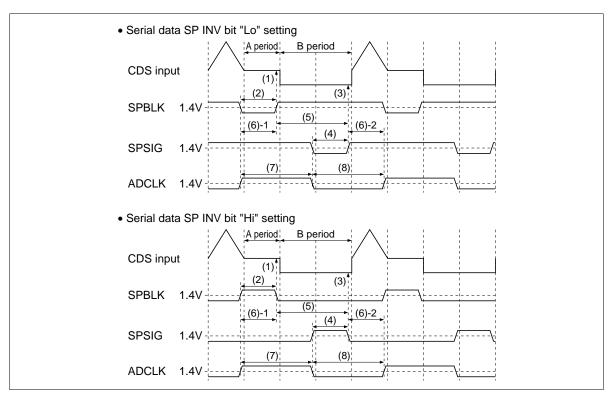

The CCD imaging element alternately outputs a black level (A-period signal) and a signal including the black level (B-period signal). The CDS circuit extracts the differential voltage between the black level and the signal including the black level (see figure 4).

Black level sampling is performed at the rising edge of the SPBLK pulse, and signal level sampling is performed at the rising edge of the SPSIG pulse. This sequence of operations extracts the differential voltage between the black level and the signal including the black level, and supplies this to the next-stage AGC circuit.

2. Feed back clamp function

The clamp level is set by means of 5-bit serial data. The setting range is 32 LSB to 56 LSB, in 1 LSB steps. A serial data value of 0 gives a 32 LSB setting, and a value of 24 gives a 56 LSB setting.

#### 3. AGC Circuit

The AGC gain is set by means of 11-bit serial data. The setting range is –3.3 dB to 34.7 dB. Details of the data are given in the following section.

The (-) side gain setting uses setting codes –81 to 0 in 0.0039-multiple steps, and the (+) side gain setting uses setting codes 0 to 1023 in 0.034 dB steps.

- Detailed specifications of HD49323AF-01 AGC gain setting codes

- (1) To improve S/N, the AD input dynamic range has been extended to 1.4 V from the 1.0 V of the HD49322BF.

- (2) There are two AGC gain ranges: (+) side 0 to 34.7 dB linear gain amp. (0.034 dB/step), and (−) side 0 to −3.3 dB "multiple" linear gain amp. (0.0039 multiple/step).

Considering the case where AGC gain is set so that the ADC output code is 511 when a 150 mV signal is input:

- The HD49322BF AGC gain setting is (code 511)/150 mV multiple = 500 mV/150 mV multiple

- The HD49323AF-01 AGC gain setting is (code 511)/150 mV multiple = 700 mV/150 mV multiple

Table 1 AGC Gain (+) Setting Code Table

| Code | BIN (D10 to D0) | dB    |

|------|-----------------|-------|

| 0    | 000 0000 0000   | 0.000 |

| 1    | 000 0000 0001   | 0.034 |

| 2    | 000 0000 0010   | 0.068 |

| 3    | 000 0000 0011   | 0.102 |

| :    |                 |       |

| 510  | 001 1111 1110   | 17.34 |

| 511  | 001 1111 1111   | 17.37 |

| 512  | 010 0000 0000   | 17.41 |

| 513  | 010 0000 0001   | 17.44 |

| :    |                 |       |

| 1020 | 011 1111 1100   | 34.68 |

| 1021 | 011 1111 1101   | 34.71 |

| 1022 | 011 1111 1110   | 34.75 |

| 1023 | 011 1111 1111   | 34.78 |

Table 2 AGC Gain (-) Setting Code Table

| Code       | BIN (D10 to D0) | Multiple | dB     |

|------------|-----------------|----------|--------|

| 0          | 000 0000 0000   | 1.000    | 0.000  |

| -1         | 111 1111 1111   | 0.996    | -0.034 |

| -2         | 111 1111 1110   | 0.992    | -0.068 |

| -3         | 111 1111 1101   | 0.988    | -0.102 |

| •          |                 |          |        |

| -30        | 111 1110 0010   | 0.883    | -1.083 |

| -31        | 111 1110 0001   | 0.879    | -1.121 |

| -32        | 111 1110 0000   | 0.875    | -1.160 |

| -33        | 111 1101 1111   | 0.871    | -1.199 |

|            |                 |          |        |

| -78        | 111 1011 0010   | 0.695    | -3.156 |

| <b>-79</b> | 111 1011 0001   | 0.691    | -3.205 |

| -80        | 111 1011 0000   | 0.688    | -3.255 |

| -81        | 111 1010 1111   | 0.684    | -3.304 |

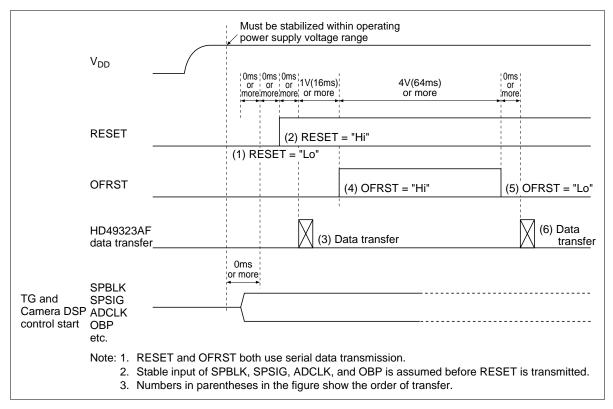

#### 4. Offset cancel circuit

When power is turned on, offset voltages generated by CDS, AGC, ADC, and other circuits by means of serial data control are canceled. (Refer to page 24 (Operating Sequence at Power-On).)

#### 5. Digital output enable function

When the  $\overline{OE}$  pin is driven high, digital output goes to the high-Z state.

| OE Pin             | Digital Output |

|--------------------|----------------|

| High               | High-Z state   |

| Low (or Open, GND) | Output enable  |

#### 6. Pre-blanking function

When the PBLK pin is driven high, digital output is fixed at 32 LSB. However, this is valid only when the  $\overline{OE}$  pin and serial data output mode settings (LINV, MINV, TEST, STBY) are low.

| PBLK Pin           | Digital Output  |

|--------------------|-----------------|

| High               | Fixed at 32 LSB |

| Low (or Open, GND) | Active          |

#### 7. CCD offset cancel function

This function cancels the offset voltage  $(V_{OFCCD})$  during the optical black period of the CCD imaging element. The definition of the CCD offset voltage  $(V_{OFCCD})$  is given below.

The difference between the black level sampling voltage and signal level sampling voltage during the OBP period is designated V<sub>OFCCD</sub>. This value is positive when (signal level sampling voltage) > (black level sampling voltage).

Figure 2 Black Level Signal Level Difference during OBP Period

Table 3

Serial Data Settings

| V <sub>OFCCD</sub> Cancel Function | When Used                                   | When Not Used           |  |  |

|------------------------------------|---------------------------------------------|-------------------------|--|--|

| Serial data settings               | VOFCON bit set to 1<br>VOFD0—3 (4 bits) set | VOFCON bit cleared to 0 |  |  |

- Determining serial set data VOFD0—3

- (1) Provisional setting

Serial data VOFD0—3 settings are made according to the value of  $V_{\text{OFCCD}}$  as shown in table 4.

(2) Actual setting

The set data is adjusted so that the CLP pin (pin 23) voltage is closest to  $1/2~{\rm AV_{DD}}$  when AGC gain is set to the maximum.

The data obtained in (2) is used as the serial set data.

$Table \ 4 \qquad V_{OFCCD} \ Serial \ Setting \ Data \ Correspondence \ Table \ (For \ Reference)$

| V <sub>OFCCD</sub> | Serial Setting Data |       |       |       |  |  |  |  |  |  |

|--------------------|---------------------|-------|-------|-------|--|--|--|--|--|--|

| (mV)               | VOFD3               | VOFD2 | VOFD1 | VOFD0 |  |  |  |  |  |  |

| -110               | 0                   | 0     | 1     | 0     |  |  |  |  |  |  |

| -90                | 0                   | 0     | 1     | 1     |  |  |  |  |  |  |

| <del>-7</del> 0    | 0                   | 1     | 0     | 0     |  |  |  |  |  |  |

| <b>-</b> 50        | 0                   | 1     | 0     | 1     |  |  |  |  |  |  |

| -30                | 0                   | 1     | 1     | 0     |  |  |  |  |  |  |

| <del>-</del> 10    | 0                   | 1     | 1     | 1     |  |  |  |  |  |  |

| +10                | 1                   | 0     | 0     | 0     |  |  |  |  |  |  |

| +30                | 1                   | 0     | 0     | 1     |  |  |  |  |  |  |

| +50                | 1                   | 0     | 1     | 0     |  |  |  |  |  |  |

| +70                | 1                   | 0     | 1     | 1     |  |  |  |  |  |  |

| +90                | 1                   | 1     | 0     | 0     |  |  |  |  |  |  |

| +110               | 1                   | 1     | 0     | 1     |  |  |  |  |  |  |

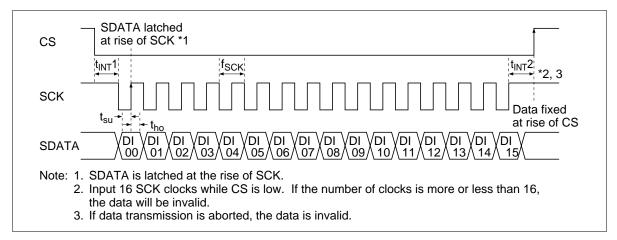

### **Timing Chart**

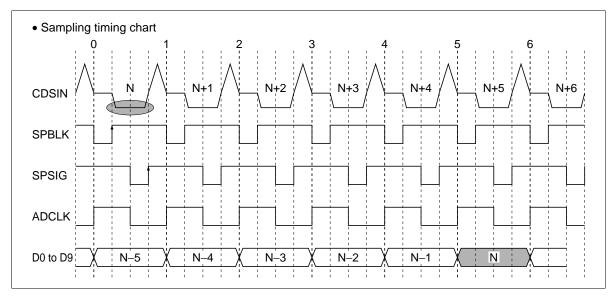

Figure 3 shows the output timing.

Figure 3 Output Timing

- The ADC output signals (D0 to D9) are output at the rising edge of ADCLK.

- The pipeline delay is 5 clocks.

### **Details of Timing Specifications**

#### **Details of Timing Specifications**

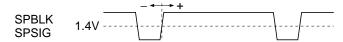

Details of the timing specifications are shown in figure 4, and the timing specifications are summarized in table 5.

**Figure 4 Details of Timing Specifications**

**Table 5** Each Timing Specifications

| No.      | Timing                                          | Symbol              | Min | Тур                   | Max                     | Unit | Note |

|----------|-------------------------------------------------|---------------------|-----|-----------------------|-------------------------|------|------|

| (1)      | Black level signal read-in time                 | t <sub>CDS1</sub>   | 0   | 5                     | 10                      | ns   | 1    |

| (2)      | SPBLK "Lo" period                               | t <sub>CDS2</sub>   | 11  | $1/4f_{ADCLK}$        | Typ $\times$ 1.2        | ns   | 2    |

| (3)      | Signal level read-in time                       | t <sub>CDS3</sub>   | 0   | 5                     | 10                      | ns   | 1    |

| (4)      | SPSIG "Lo" period                               | t <sub>CDS4</sub>   | 11  | 1/4f <sub>ADCLK</sub> | $\text{Typ} \times 1.2$ | ns   | 2    |

| (5)      | SPBLK rise to SPSIG rise                        | t <sub>CDS5</sub>   | 20  | 1/2f <sub>ADCLK</sub> | Typ × 1.15              | ns   | 2    |

| (6)-1    | ADCLK rise to SPBLK rise                        | t <sub>CDS6-1</sub> | 25  | _                     | _                       | ns   | 2    |

| (6)-2    | SPSIG rise to ADCLK rise                        | t <sub>CDS6-2</sub> | 0   |                       |                         | ns   | 2    |

| (7), (8) | ADCLK t <sub>wH</sub> Min / t <sub>wL</sub> Min | t <sub>CDS7,8</sub> | 22  |                       |                         | ns   |      |

Note: 1. Negative when data before the rising edge of SPBLK/SPSIG is sampled, and positive when data after the rising edge is sampled.

2. The polarity of SPBLK and SPSIG is for a low setting of the serial data SP INV bit.

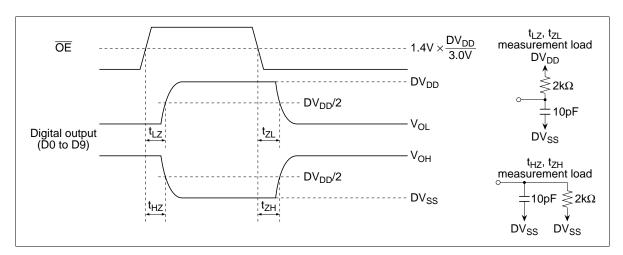

#### **Detailed Timing Specifications for Digital Output Enable Control**

Detailed timing specifications in the case of digital output enable control are shown in figure 5. When the  $\overline{OE}$  pin is high, output disable mode is entered and output goes to the high-Z state.

Figure 5 Detailed Timing Specifications for Digital Output Enable Control

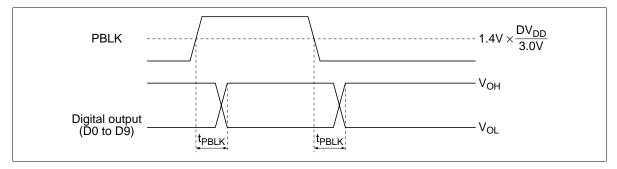

#### **Detailed Timing Specifications for Pre-Blanking**

Detailed timing specifications for pre-blanking are shown in figure 6. When the PBLK pin is high, digital output is fixed at 32 LSB. However, the  $\overline{OE}$  pin and serial data output mode settings (LINV, MINV, TEST, STBY) take precedence.

Figure 6 Detailed Timing Specifications for Pre-Blanking

#### **Output Code Table**

**Table 6** Function Table

|    |      |      |      |      |             | Digital Output                              |                   |

|----|------|------|------|------|-------------|---------------------------------------------|-------------------|

| OE | STBY | TEST | LINV | MINV | <b>PBLK</b> | D9 D8 D7 D6 D5 D4 D3 D2 D1 D0               | Operation Mode    |

| Н  | X    | Χ    | Χ    | Χ    | X           | Hi-Z                                        | Output Hi-Z       |

| L  | Н    | Χ    | Χ    | Χ    | Χ           | Hi-Z                                        | Low power standby |

|    | L    | L    | L    | L    | L           | Table 7 as follows                          | Normal operation  |

|    |      |      | L    | Н    | L           | In the table 7 below, D9 is inverted        |                   |

|    |      |      | Н    | L    | L           | In the table 7 below, D8 to D0 are inverted |                   |

|    |      |      | Н    | Н    | L           | In the table 7 below, D9 to D0 are inverted |                   |

|    |      |      | L    | L    | Н           |                                             | Pre-blanking      |

|    |      | Н    | L    | L    | X           | L                                           | Test mode         |

|    |      |      | L    | Н    | X           | H                                           |                   |

|    |      |      | Н    | L    | Χ           | L L H L H L H L H L H L                     |                   |

|    |      |      | Н    | Н    | Χ           | H                                           |                   |

Note: 1. STBY, TEST, LINV, and MINV mode setting is performed by means of serial data.

- 2.  $\overline{\text{OE}}$  and PBLK mode setting is performed by means of external input pins.

- 3. Pre-blanking mode is enabled when the PBLK pin is high and all other pins are low.

**Table 7 Output Code Table**

| Output Pin |      | D9  | D8 | D7       | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Input Level |

|------------|------|-----|----|----------|----|----|----|----|----|----|----|-------------|

| Output     | Step | 0 L | L  | L        | L  | L  | L  | L  | L  | L  | L  | →0V         |

| code       |      | 1 L | L  | L        | L  | L  | L  | L  | L  | L  | Н  | <b>†</b>    |

|            |      | 2 L | L  | L        | L  | L  | L  | L  | L  | Н  | L  |             |

|            |      | 3 L | L  | L        | L  | L  | L  | L  | L  | Н  | Н  |             |

|            |      | :   | 1  | :        | :  | :  | ÷  | :  | :  | :  | :  | <b>   </b>  |

|            | 51   | 1 L | Н  | Н        | Н  | Н  | Н  | Н  | Н  | Н  | Н  | →0.7V       |

|            | 51   | 2 H | L  | L        | L  | L  | L  | L  | L  | L  | L  | <b>†</b>    |

|            |      | :   | 1  | :        | :  | :  | ÷  | :  | :  | :  | :  |             |

|            | 102  | 0 H | Н  | Н        | Н  | Н  | Н  | Н  | Н  | L  | L  |             |

|            | 102  | 1 H | Н  | Н        | Н  | Н  | Н  | Н  | Н  | L  | Н  |             |

|            | 102  | 2 H | Н  | Н        | Н  | Н  | Н  | Н  | Н  | Н  | L  | <b> </b>    |

|            | 102  | 3 H | Н  | <u> </u> | Н_ | H  | Н  | Н  | H  | Н  | Н  | →1.4V       |

## **Absolute Maximum Ratings** (Ta = 25°C)

| Item                  | Symbol               | Ratings                       | Unit |  |

|-----------------------|----------------------|-------------------------------|------|--|

| Power supply voltage  | $V_{\text{DD(max)}}$ | 6.0                           | V    |  |

| Power dissipation     | P <sub>D(max)</sub>  | 400                           | mW   |  |

| Analog input voltage  | V <sub>IN(max)</sub> | -0.3 to AV <sub>DD</sub> +0.3 | V    |  |

| Digital input voltage | $V_{I(max)}$         | -0.3 to 6.0                   | V    |  |

| Operating temperature | Topr                 | -10 to +85                    | °C   |  |

| Storage temperature   | Tstg                 | -55 to +125                   | °C   |  |

Note: 1.  $V_{DD}$  indicates  $AV_{DD}$  and  $DV_{DD}$ .

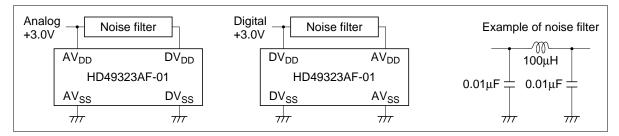

2. Common connection of  $AV_{DD}$  and  $DV_{DD}$  should be made off-chip. If  $AV_{DD}$  and  $DV_{DD}$  are isolated by a noise filter, the phase difference should be 0.3 V or less at power-on and 0.1 V or less during operation.

**Electrical Characteristics** (Unless othewide specified, Ta = 25°C, AV $_{DD}$  = 3.0 V, DV $_{DD}$  = 3.0 V, R $_{EXT}$  = 24 k $\Omega$ )

| Item                            | Symbol               | Min                                            | Тур  | Max                                            | Unit   | <b>Test Conditions</b>     | Remarks                                                  |

|---------------------------------|----------------------|------------------------------------------------|------|------------------------------------------------|--------|----------------------------|----------------------------------------------------------|