### **MOTOROLA SEMICONDUCTOR TECHNICAL DATA**

## Advance Information

# Micro-Power Comparator plus **Voltage Follower CMOS**

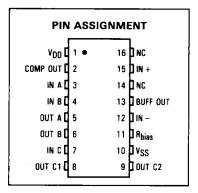

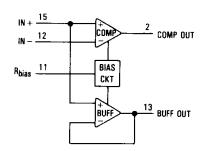

The MC14578 is an analog building block consisting of a very-high input impedance comparator. The voltage follower allows monitoring the noninverting input of the comparator without loading.

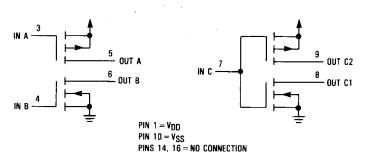

Four enhancement-mode MOSFETs are also included on chip. These FETs can be externally configured as open-drain or totem-pole outputs. The drains have on-chip staticprotecting diodes. Therefore, the output voltage must be maintained between VSS and

The chip requires one external component. A 3.9 M $\Omega\pm$  10% resistor must be connected from the Rbias pin to VDD.

Applications:

Pulse Shapers Threshold Detectors Line-Powered Smoke Detectors

Liquid/Moisture Sensors **Low-Battery Detectors**

• DIP Complies with the UL217 and UL268 Specifications

Operating Voltage Range: 3.5 to 14 V

Operating Temperature Range: -30° to 70°C

Input Current (IN + Pin): ±1 pA @ 25°C (DIP Only)

Quiescent Current: 10 μA @ 25°C

• Electrostatic Discharge (ESD) Protection Circuitry on All Pins

• Chip Complexity: 26 FETs

## MC14578

#### LOGIC DETAIL

This document contains information on a new product. Specifications and information herein are subject to change without notice.

MAXIMUM RATINGS\* (Voltage Referenced to VSS)

| Symbol           | Parameter                                                   | Value                        | Unit |

|------------------|-------------------------------------------------------------|------------------------------|------|

| V <sub>DD</sub>  | DC Supply Voltage                                           | -0.5 to +14.0                | ٧    |

| Vin              | DC Input Voltage                                            | -0.5 to V <sub>DD</sub> +0.5 | ٧    |

| Vout             | DC Output Voltage                                           | -0.5 to V <sub>DD</sub> +0.5 | ٧    |

| lin              | DC Input Current, Except IN+                                | ± 10                         | mA   |

| lin              | DC Input Current, IN+                                       | <u>±</u> 1                   | mA   |

| lout             | DC Output Current, per Pin                                  | ± 25                         | mA   |

| lDD              | DC Supply Current, V <sub>DD</sub> and V <sub>SS</sub> Pins | ± 50                         | mA   |

| PD               | Power Dissipation, per Package                              | 500                          | mW   |

| T <sub>stg</sub> | Storage Temperature                                         | - 65 to + 150                | °C   |

| ΤĹ               | Lead Temperature (10-Second Soldering)                      | 260                          | °C   |

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation,  $V_{in}$  and  $V_{out}$  should be constrained to the range  $V_{SS} \leq (V_{in})$  or  $V_{out}) \leq V_{DD}$ .

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either VSS or VDD). Unused outputs must be left open.

**ELECTRICAL CHARACTERISTICS** (Voltages Referenced to VSS,  $R_{bias} = 3.9 \text{ M}\Omega$  to  $V_{DD}$ ,  $T_{A} = -30^{\circ}$  to  $70^{\circ}$ C Unless Otherwise Indicated)

| Symbol          | Parameter                                                                                                               | Test Condition                                                                                                                                                    | V <sub>DD</sub>   | Guaranteed<br>Limit             | Unit |

|-----------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------|------|

| V <sub>DD</sub> | Power Supply Voltage Range                                                                                              |                                                                                                                                                                   |                   | 3.5 to 14.0                     | V    |

| V <sub>IL</sub> | Maximum Low-Level Input Voltage, MOSFETs Wired as Inverters; i.e., IN A tied to IN B, OUT A to OUT B, OUT C1 to OUT C2  | $V_{out} = 9.0 \text{ V},  I_{out}  < 1 \mu \text{A}$                                                                                                             | 10.0              | 2.0                             | ٧    |

| VIH             | Minimum High-Level Input Voltage, MOSFETs Wired as Inverters; i.e., IN A tied to IN B, OUT A to OUT B, OUT C1 to OUT C2 | $V_{out} = 1.0 \text{ V},  I_{out}  < 1 \mu \text{A}$                                                                                                             | 10.0              | 8.0                             | ٧    |

| V <sub>IO</sub> | Comparator Input Offset Voltage                                                                                         | T <sub>A</sub> = 25°C, Over Common<br>Mode Range                                                                                                                  | 10.0              | ± 50                            | m∨   |

|                 |                                                                                                                         | T <sub>A</sub> = 0° to 50°C, Over Common<br>Mode Range                                                                                                            | 3.5<br>to<br>14.0 | ± 75                            |      |

| Vсм             | Comparator Common Mode Voltage Range                                                                                    |                                                                                                                                                                   | 3.5<br>to<br>14.0 | 0.7 to<br>V <sub>DD</sub> – 1.5 | ٧    |

| VOL             | Maximum Low-Level Comparator Output Voltage                                                                             | $\begin{split} &\text{IN} + :  V_{in} = V_{SS}, \\ &\text{IN} - :  V_{in} = V_{DD}, \\ &\text{I}_{out} = 30  \mu\text{A} \end{split}$                             | 10.0              | 0.5                             | V    |

| VOH             | Minimum High-Level Comparator Output Voltage                                                                            | $\begin{aligned} & \text{IN} + : V_{\text{in}} = V_{DD}, \\ & \text{IN} - : V_{\text{in}} = V_{SS}, \\ & \text{I}_{\text{out}} = -30 \ \mu\text{A} \end{aligned}$ | 10.0              | 9.5                             | V    |

| V <sub>00</sub> | Buffer Amp Output Offset Voltage                                                                                        | $R_{load}$ = 10 M $\Omega$ to V <sub>DD</sub> or V <sub>SS</sub> , Over Common Mode Range                                                                         | -                 | ± 100                           | m۱   |

| VOL             | Maximum Low-Level Output Voltage, MOSFETs Wired as Inverters;                                                           | OUT C1, OUT C2: I <sub>out</sub> = 1.1 mA                                                                                                                         | 10.0              | 0.5                             | V    |

|                 | i.e., IN A tied to IN B, OUT A to OUT B, OUT C1 to OUT C2                                                               | OUT A, OUT B: I <sub>out</sub> = 270 μA                                                                                                                           | 10.0              | 0.5                             |      |

| Voн             |                                                                                                                         | OUT C1, OUT C2: $I_{out} = -1.1 \text{ mA}$                                                                                                                       | 10.0              | 9.5                             | _ v  |

|                 | i.e., IN A tied to IN B, OUT A to OUT B, OUT C1 to OUT C2                                                               | OUT A, OUT B: I <sub>out</sub> = -270 μA                                                                                                                          | 10.0              | 9.5                             |      |

| lin             | Maximum Input Leakage Current IN + (DIP Only)                                                                           | T <sub>A</sub> = 25°C, 40% R.H.,<br>V <sub>in</sub> = V <sub>SS</sub> or V <sub>DD</sub>                                                                          | 10.0              | ±1                              | p/   |

|                 | IN+ (DIP Only)                                                                                                          | T <sub>A</sub> = 50°C,<br>V <sub>in</sub> = V <sub>SS</sub> or V <sub>DD</sub>                                                                                    | 10.0              | ±6                              |      |

|                 | IN+ (SOG), IN A, IN B, IN C, IN-                                                                                        | Vin = VSS or VDD                                                                                                                                                  | 10.0              | ± 40                            | n/   |

| loz             | Maximum Off-State MOSFET Leakage Current                                                                                | IN A, IN C: V <sub>in</sub> = V <sub>DD</sub> , OUT A, OUT C2: V <sub>out</sub> = V <sub>SS</sub> or V <sub>DD</sub>                                              | 10.0              | ± 100                           | n/   |

|                 |                                                                                                                         | IN B, IN C: V <sub>in</sub> =V <sub>SS</sub> , OUT B, OUT C1: V <sub>out</sub> =V <sub>SS</sub> or V <sub>DD</sub>                                                | 10.0              | ± 100                           |      |

| IDD             | Maximum Quiescent Current                                                                                               | $T_A = 25^{\circ}C$ ,<br>IN A, IN B, IN C: $V_{in} = V_{SS}$<br>or $V_{DD}$ ,<br>$ V_{IN} + V_{IN}  = 100 \text{ mV}$ ,<br>$ V_{in}  = 0 \mu A$                   | 10.0              | 10                              | μA   |

| Cin             | Maximum Input Capacitance IN+ Other Inputs                                                                              | f = 1 kHz                                                                                                                                                         | -                 | 5<br>15                         | pl   |

<sup>\*</sup>Maximum Ratings are those values beyond which damage to the device may occur.

## 4

### **APPLICATIONS INFORMATION**

NOTE: IN+ and IN- have very-high input impedance. Interconnect to these pins should be as short as possible.

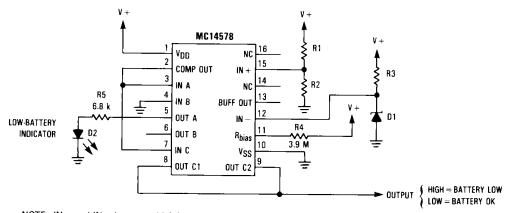

Figure 1. Low-Battery Detector

#### **EXAMPLE VALUES**

D1: 1N4683 Zener Diode (Available From Motorola)

D2: HLMP-D150, HLMP-K150, or HLMP-Q150 Low-Current LED (Hewlett-Packard Part Number or Equivalent)

| R1     | R2     | R3    | Nominal<br>Trip<br>Point |

|--------|--------|-------|--------------------------|

| 470 kΩ | 1.3 MΩ | 20 kΩ | 4.08 V                   |

| 820 kΩ | 1.2 MΩ | 39 kΩ | 5.05 V                   |

| 1.2 MΩ | 1.2 MΩ | 62 kΩ | 6.00 V                   |

Near the switchpoint, the comparator output in the circuit of Figure 1 may chatter or oscillate. This oscillation appears on the signal labelled OUTPUT. In come cases, the oscillation in the transition region will not cause problems. For example, an MPU reading OUTPUT could sample the signal two or three times to ensure a solid level is attained. But, in a low battery detector, this probably is not necessary.

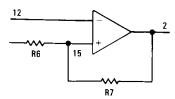

To eliminate comparator chatter, hysteresis can be added as shown in Figure 2. The circuit of Figure 2 requires slightly more operating current than the Figure 1 arrangement.

Figure 2. Adding Hysteresis