## Multi-Link LAPD (MLAPD) Protocol Controller

The Motorola MC68606 Multi-Link LAPD (MLAPD) protocol controller is an integrated circuit implementing the link access procedure (LAPD) protocol. LAPD is the proposed protocol for use at the link layer (ISO-Layer 2) for both signalling and data transfer applications in Integrated Services Digital Network (ISDN) configurations. The LAPD protocol is specified in CCITT Recommendation Q.920/ 0.921.

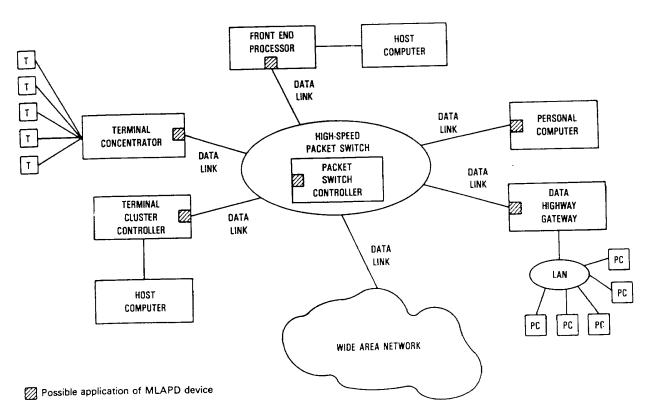

Current product implementations of this link level protocol are accomplished with firmware. This significantly loads the local processor, and presents limitations to both the maximum potential throughput of data and to the number of logical links which may be supported by such packet data interfaces. A generic view of where the MLAPD device can be used to interconnect a diversity of data endpoints in a high speed packet switch network is shown in Figure 1. The data links illustrated could differ functionally and provide data rates in the range of 64 kbps to 2.048 Mbps.

The MLAPD functions as an intelligent peripheral device to a central processing unit (CPU) in a microcomputer system. An on-chip DMA controller transfers data packets to and from a buffer memory. A microcoded buffer management scheme queues packets during transmission and reception. All link management duties are handled by the MLAPD device to maximize the bandwidth available for CPU operation and to increase the throughput for packet data transfer. This VLSI implementation provides a cost effective solution, while encouraging a universal implementation of the LAPD protocol. Key features of the MLAPD device include:

- Full Implementation of CCITT Recommendation Q.920/Q.921 Link Access Procedure (LAPD) with Independent Generation of Commands and Responses for Each Logical Link

- Control of up to 8192 Logical Links Using a Memory-Based Architecture, Wherein the Protocol Controller and the Supervising Microprocessor Communicate Through Shared Memory

- Reliable, Interleaved Data Transfers for Multiple Logical Links with the Following Protocol Actions:

- HDLC framing with zero-bit insertion/deletion for a serial bit stream; or optional parallel assist mode where zero insertion/deletion is disabled and frame delineation is provided by external pins for supporting a parallel interface to the physical level.

- Error control using a 16-bit CRC.

- Flow control to prevent data from accumulating at the receiving end faster than the data can be processed.

- Termination of a Non-Channelized Serial Bit Stream with an Aggregate Rate in Excess of 2.048 Mbps or Optional Memory-to-Memory Operation Allowing the MLAPD to Act as a LAPD Controller Independent of the System's Physical Level Characteristics

## MC68606

Technical Summary

RC SUFFIX PIN GRID ARRAY (84 PIN) CASE 793

## **PIN GRID ARRAY**

| K (   | 0               | 0           | 0        | 0               | 0    | 0               | 0   | O<br>A21 | O<br>GND | O<br>A18 |

|-------|-----------------|-------------|----------|-----------------|------|-----------------|-----|----------|----------|----------|

|       | CLK             | GND         | RxD      | V <sub>DD</sub> | RCLK | A <sup>DD</sup> | A23 | AZI      | ษุพบ     | AIO      |

| J     | 0               | 0           | 0        | 0               | 0    | 0               | 0   | 0        | 0        | 0        |

| i     | v <sub>DO</sub> | GND         | MOTO/    | RTS/<br>TSTART  | TxD  | VDD             | A20 | A19      | A17      | A15      |

| н     | 0               | 0           | O        | O               | 0    | 0               | 0   | 0        | 0        | 0        |

| "     | RESET           | RETRY       | GND      | CTS/            | GND  | TCLK            | A22 | A16      | VDD      | A14      |

|       |                 |             |          | RSTART          |      |                 |     |          |          |          |

| 6     | 0               | 0           | 0        |                 |      |                 |     | 0        | 0        | 0        |

| - 1   | IACK            | BERR        | HALT     |                 |      |                 |     | A13      | A12      | GND      |

| ا ۔ ا | (INTA)          | _           | _        |                 |      |                 |     | _        | 0        | 0        |

| F     | O<br>BG         | 0           | O<br>IRQ |                 |      |                 |     | O<br>49  | A11      | A10      |

|       | (HOLDA)         | BR<br>(HRQ) | (INTR)   |                 |      | TOM             |     | AS       | MII      | KIU      |

| E     | (HOLDK)         | (nnu)       | 0        |                 | VI   | IEW             |     | 0        | 0        | 0        |

|       | R/₩             | GND         | DTACK    |                 | 1    |                 |     | A8       | VDD      | GND      |

|       | (WR)            | -           | (READY)  |                 |      |                 |     |          |          |          |

| D     | 0               | 0           | 0        |                 |      |                 |     | 0        | 0        | 0        |

|       | BGACK           | ogv         | UDS/A0   |                 |      |                 |     | ממע      | A5       | A7       |

|       | (ĀD)            | _           | (AO)     | _               | _    | _               | _   | _        | _        | _        |

| C     | 0               | <u>o</u>    | <u>o</u> | 0               | 0    | 0               | 0   | 0        | O        | 0        |

|       | (DIS            | CS          | ĀŠ       | GND             | VDD  | 010             | D12 | A1       | GND      | A6       |

| 8     | (BHE)           | 0           | 0        | 0               | 0    | 0               | 0   | 0        | 0        | 0        |

| ŭ     | GND             | DO          | D2       | D5              | GND  | D9              | GND | D15      | A2       | A4       |

|       | 0.10            |             | -        | -               |      |                 |     |          |          |          |

| A     | 0               | 0           | 0        | 0               | 0    | 0               | 0   | 0        | 0        | 0        |

|       | 01              | D3          | D4       | D6              | 07   | D8              | D11 | D13      | D14      | A3       |

|       | 1               | 2           | 3        | 4               | 5    | 6               | 7   | 8        | 9        | 10       |

- Supports User Prioritization of I Frame and XID/UI Frame Transmission

- Supports Optional Receive and Transmit of a User-Defined, Non-Standard LAPD Unnumbered (U) Frame

- On-Chip, Content-Addressable Memory (CAM) Provides Address Translation for Up to 16 Logical Links. When Supporting More Than 16 Logical Links, Translation is Provided Via a Translation Table in Shared Memory

- Provides Error/Statistical Counters and Maskable Interrupts to the Level 3 Process

- Supports Optional Non-Protocol Mode on a Per-Logical Link Basis, Which Allows the Host to Receive and Transmit Frames Without Application of the LAPD Procedures by the MLAPD

- Supports Promiscuous Receive Mode in Which the MLAPD Receives All Frames From the Line and Transfers the Entire Frame to Memory

- System Interface Tailored for Different Microprocessor System Implementations:

- Motorola M68000 and Intel iAPX86 Family Bus Interface Options

- 8- and 16-Bit Data Bus Support

- Direct Addressing of 16 Mbytes of System Memory

- Available in 12.5 MHz and 16.67 MHz System Clock Versions

- 84 Lead PGA and PLCC J-Lead Surface Mount Packages

- 1.5 Micron HCMOS Technology

Figure 1. High Speed Data Switching