# 64K x 18 Bit Asynchronous/ Latched Address Fast Static RAM

The MCM67A618 is a 1,179,648 bit latched address static random access memory organized as 65,536 words of 18 bits, fabricated with Motorola's high–performance silicon–gate BiCMOS technology. The device integrates a 64K x 18 SRAM core with advanced peripheral circuitry consisting of address and data input latches, active low chip enable, separate upper and lower byte write strobes, and a fast output enable. This device has increased output drive capability supported by multiple power pins.

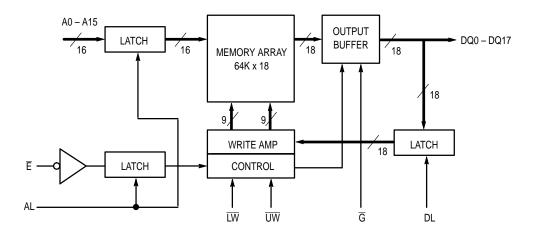

Address, data in, and chip enable latches are provided. When latch enables (AL for address and chip enables and DL for data in) are high, the address, data in, and chip enable latches are in the transparent state. If latch enables are tied high the device can be used as an asynchronous SRAM. When latch enables are low the address, data in, and chip enable latches are in the latched state. This input latch simplifies read and write cycles by guaranteeing address and data—in hold time in a simple fashion.

Dual write enables ( $\overline{LW}$  and  $\overline{UW}$ ) are provided to allow individually writeable bytes.  $\overline{LW}$  controls DQ0 – DQ8 (the lower bits) while  $\overline{UW}$  controls DQ9 – DQ17 (the upper bits).

Six pair of power and ground pins have been utilized and placed on the package for maximum performance.

The MCM67A618 will be available in a 52-pin plastic leaded chip carrier (PLCC).

This device is ideally suited for systems that require wide data bus widths, cache memory, and tag RAMs.

- Single 5 V ± 5% Power Supply

- Fast Access Times: 10/12/15 ns Max

- Byte Writeable via Dual Write Enables

- Separate Data Input Latch for Simplified Write Cycles

- Address and Chip Enable Input Latches

- Common Data Inputs and Data Outputs

- Output Enable Controlled Three–State Outputs

- 3.3 V I/O Compatible

- · High Board Density 52-Lead PLCC Package

# MCM67A618

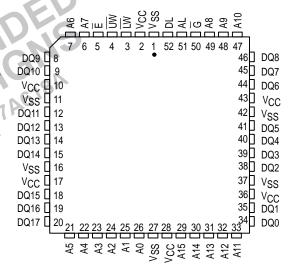

#### **PIN ASSIGNMENT**

| 1 111 10 111120                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0 – A15 Address Inputs AL Address Latch DL Data Latch \overline{\text{LW}} Lower Byte Write Enable \overline{\text{UW}} Higher Byte Write Enable \overline{\text{E}} Chip Enable \overline{\text{G}} Output Enable \overline{\text{DQ0}} - DQ17 Data Input/Output \overline{\text{VCC}} + 5 \ V Power Supply \overline{\text{VS}} Ground |

All power supply and ground pins must be connected for proper operation of the device.

REV 4 5/95

#### **BLOCK DIAGRAM**

#### **TRUTH TABLE**

| Ē | LW | υw | AL* | DL* | G | Mode                                     | Supply<br>Current | I/O<br>Status |

|---|----|----|-----|-----|---|------------------------------------------|-------------------|---------------|

| Н | Х  | Х  | Х   | Х   | Х | Deselected Cycle                         | I <sub>SB</sub>   | High-Z        |

| L | Х  | Х  | L   | Х   | Х | Read or Write Using Latched Addresses    | Icc               | _             |

| L | Х  | Х  | Н   | Х   | Х | Read or Write Using Unlatched Addresses  | Icc               | _             |

| L | Н  | Н  | Х   | Х   | L | Read Cycle                               | Icc               | Data Out      |

| L | Н  | Н  | Х   | Х   | Н | Read Cycle                               | Icc               | High-Z        |

| L | L  | L  | Х   | L   | Х | Write Both Bytes Using Latched Data In   | ICC               | High-Z        |

| L | Ĺ  | L  | Х   | Н   | Х | Write Both Bytes Using Unlatched Data In | Icc               | High–Z        |

| L | L  | Н  | Х   | Х   | Х | Write Cycle, Lower Byte                  | Icc               | High–Z        |

| L | Н  | L  | Х   | Х   | Х | Write Cycle, Lower Byte                  | Icc               | High-Z        |

<sup>\*</sup>E and Addresses satisfy the specified setup and hold times for the falling edge of AL. Data-in satisfies the specified setup and hold times for falling edge of DL.

NOTE: This truth table shows the application of each function. Combinations of these functions are valid.

# **ABSOLUTE MAXIMUM RATINGS** (Voltages Referenced to $V_{SS} = 0$ )

| Rating                                                                    | Symbol                             | Value                          | Unit |

|---------------------------------------------------------------------------|------------------------------------|--------------------------------|------|

| Power Supply Voltage                                                      | Vcc                                | - 0.5 to 7.0                   | V    |

| Voltage Relative to V <sub>SS</sub> for Any<br>Pin Except V <sub>CC</sub> | V <sub>in</sub> , V <sub>out</sub> | - 0.5 to V <sub>CC</sub> + 0.5 | V    |

| Output Current (per I/O)                                                  | l <sub>out</sub>                   | ± 30                           | mA   |

| Power Dissipation                                                         | PD                                 | 1.6                            | W    |

| Temperature Under Bias                                                    | T <sub>bias</sub>                  | - 10 to + 85                   | °C   |

| Operating Temperature                                                     | T <sub>A</sub>                     | 0 to + 70                      | °C   |

| Storage Temperature                                                       | T <sub>stg</sub>                   | - 55 to + 125                  | °C   |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPER-ATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit.

This BiCMOS memory circuit has been designed to meet the dc and ac specifications shown in the tables, after thermal equilibrium has been established.

This device contains circuitry that will ensure the output devices are in High–Z at power up.

## DC OPERATING CONDITIONS AND CHARACTERISTICS

(V<sub>CC</sub> = 5.0 V  $\pm$  5%, T<sub>A</sub> = 0 to + 70°C, Unless Otherwise Noted)

# **RECOMMENDED OPERATING CONDITIONS** (Voltages referenced to $V_{SS} = 0 V$ )

| Parameter                                | Symbol          | Min    | Max                     | Unit |

|------------------------------------------|-----------------|--------|-------------------------|------|

| Supply Voltage (Operating Voltage Range) | Vcc             | 4.75   | 5.25                    | V    |

| Input High Voltage                       | V <sub>IH</sub> | 2.2    | V <sub>CC</sub> + 0.3** | V    |

| Input Low Voltage                        | V <sub>IL</sub> | - 0.5* | 0.8                     | V    |

# DC CHARACTERISTICS

| Parameter                                                                                                                                                                                                                              | Symbol                     | Min | Max               | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----|-------------------|------|

| Input Leakage Current (All Inputs, V <sub>in</sub> = 0 to V <sub>CC</sub> )                                                                                                                                                            | llkg(l)                    | _   | ± 1.0             | μΑ   |

| Output Leakage Current ( $\overline{G} = V_{IH}$ )                                                                                                                                                                                     | llkg(O)                    | _   | ± 1.0             | μΑ   |

| AC Standby Current ( $\overline{G}$ = V <sub>IH</sub> , I <sub>Out</sub> = 0 mA, All Inputs = V <sub>IL</sub> and V <sub>IH</sub> , V <sub>IL</sub> = 0.0 V and V <sub>IH</sub> $\geq$ 3.0 V, Cycle Time $\geq$ t <sub>AVAV</sub> min) | ICCA10<br>ICCA12<br>ICCA15 | _   | 290<br>280<br>265 | mA   |

| AC Standby Current ( $\overline{E}$ = V <sub>IH</sub> , I <sub>Out</sub> = 0 mA, All Inputs = V <sub>IL</sub> and V <sub>IH</sub> , V <sub>IL</sub> = 0.0 V and V <sub>IH</sub> $\geq$ 3.0 V, Cycle Time $\geq$ t <sub>AVAV</sub> min) | I <sub>SB1</sub>           | _   | 95                | mA   |

| CMOS Standby Current $(\overline{E} \ge V_{CC} - 0.2$ , All Inputs $\ge V_{CC} - 0.2$ V or $\le 0.2$ V, f = f <sub>max</sub> )                                                                                                         | I <sub>SB2</sub>           | _   | 20                | mA   |

| Output Low Voltage (I <sub>OL</sub> = + 8.0 mA)                                                                                                                                                                                        | VOL                        | _   | 0.4               | V    |

| Output High Voltage (I <sub>OH</sub> = - 4.0 mA)                                                                                                                                                                                       | Voн                        | 2.4 | 3.3               | V    |

# **CAPACITANCE** (f = 1.0 MHz, dV = 3.0 V, $T_A = 25$ °C, Periodically Sampled Rather Than 100% Tested)

| Characteristic                                 | Symbol           | Тур | Max | Unit |

|------------------------------------------------|------------------|-----|-----|------|

| Input Capacitance (All Pins Except DQ0 – DQ17) | C <sub>in</sub>  | 4   | 5   | pF   |

| Input/Output Capacitance (DQ0 – DQ17)          | C <sub>I/O</sub> | 6   | 8   | pF   |

<sup>\*</sup>  $V_{IL}$  (min) = -0.5 V dc;  $V_{IL}$  (min) = -2.0 V ac (pulse width  $\le 20$  ns) for  $I \le 20.0$  mA.

\*\*  $V_{IH}$  (max) =  $V_{CC}$  + 0.3 V dc;  $V_{IH}$  (max) =  $V_{CC}$  + 2.0 V ac (pulse width  $\le 20$  ns) for  $I \le 20.0$  mA.

## **AC OPERATING CONDITIONS AND CHARACTERISTICS**

(V<sub>CC</sub> =  $5.0 \text{ V} \pm 5\%$ , T<sub>A</sub> =  $0 \text{ to} + 70^{\circ}\text{C}$ , Unless Otherwise Noted)

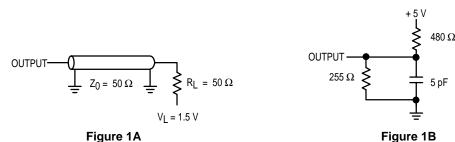

| Input Timing Measurement Reference Level 1.5 V | Output Timing Reference Level               |

|------------------------------------------------|---------------------------------------------|

| Input Pulse Levels 0 to 3.0 V                  | Output Load Figure 1 Unless Otherwise Noted |

| Input Rise/Fall Time                           |                                             |

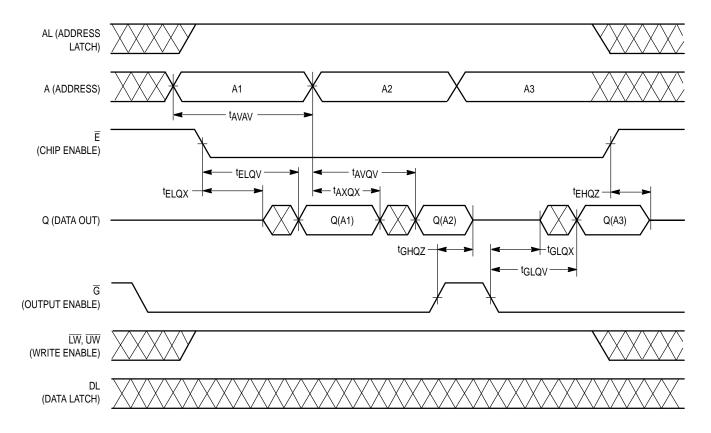

#### ASYNCHRONOUS READ CYCLE TIMING (See Notes 1 and 2)

|                                                                                                                       |                                                                                  | МСМ67            | A618–10        | MCM67            | A618–12        | MCM67            | A618–15          |      |       |

|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------|----------------|------------------|----------------|------------------|------------------|------|-------|

| Parameter                                                                                                             | Symbol                                                                           | Min              | Max            | Min              | Max            | Min              | Max              | Unit | Notes |

| Read Cycle Times                                                                                                      | <sup>t</sup> AVAV                                                                | 10               | _              | 12               | _              | 15               | _                | ns   | 3     |

| Access Times:  Address Valid to Output Valid  E Low to Output Valid Output Enable Low to Output Valid                 | <sup>t</sup> AVQV<br><sup>t</sup> ELQV<br><sup>t</sup> GLQV                      | _<br>_<br>_      | 10<br>10<br>5  | _<br>_<br>_      | 12<br>12<br>6  | _<br>_<br>_      | 15<br>15<br>7    | ns   | 4     |

| Output Hold from Address Change                                                                                       | <sup>t</sup> AXQX                                                                | 4                | _              | 4                | _              | 4                | _                | ns   |       |

| Output Buffer Control:  E Low to Output Active G Low to Output Active E High to Output High–Z G High to Output High–Z | <sup>†</sup> ELQX<br><sup>†</sup> GLQX<br><sup>†</sup> EHQZ<br><sup>†</sup> GHQZ | 3<br>1<br>2<br>2 | <br><br>5<br>5 | 3<br>1<br>2<br>2 | <br><br>6<br>6 | 3<br>1<br>2<br>2 | _<br>_<br>7<br>7 | ns   | 5     |

| Power Up Time                                                                                                         | <sup>t</sup> ELICCA                                                              | 0                | _              | 0                | _              | 0                | _                | ns   |       |

#### NOTES:

- 1. AL and DL are equal to  $V_{\mbox{\scriptsize IH}}$  for all asynchronous cycles.

- 2. Both Write Enable signals  $(\overline{LW}, \overline{UW})$  are equal to  $V_{IH}$  for all read cycles.

- 3. All read cycle timing is referenced from the last valid address to the first transitioning address.

- 4. Addresses valid prior to or coincident with  $\overline{\mathsf{E}}$  going low.

- 5. Transition is measured ± 500 mV from steady–state voltage with output load of Figure 1B. This parameter is sampled and not 100% tested. At any given voltage and temperature, tehoz is less than telox and temperature, tehoz is less than telox and temperature.

#### **AC TEST LOADS**

# **ASYNCHRONOUS READ CYCLES**

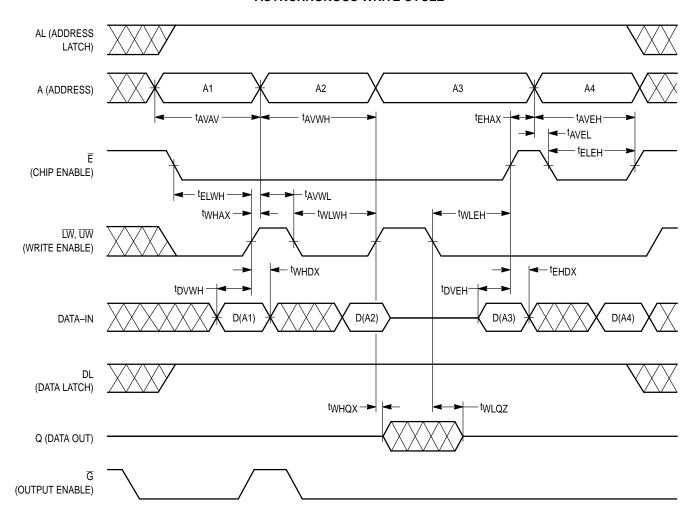

## ASYNCHRONOUS WRITE CYCLE TIMING (See Notes 1, 2, and 3)

|                                                                                                                                                                        |                                           | MCM67                      | CM67A618-10 MCM67A618-12 |                              | MCM67A618-15          |                              |                  |      |                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------|--------------------------|------------------------------|-----------------------|------------------------------|------------------|------|----------------|

| Parameter                                                                                                                                                              | Symbol                                    | Min                        | Max                      | Min                          | Max                   | Min                          | Max              | Unit | Notes          |

| Write Cycle Times                                                                                                                                                      | tAVAV                                     | 10                         | _                        | 12                           | _                     | 15                           | _                | ns   | 4              |

| Setup Times: Address Valid to End of Writ<br>Address Valid to E Hig<br>Address Valid to W Lov<br>Address Valid to E Lov<br>Data Valid to W Hig<br>Data Valid E Hig     | tavel<br>tavel<br>tavel<br>tavel<br>tovel | 9<br>9<br>0<br>0<br>5<br>5 |                          | 10<br>10<br>0<br>0<br>6<br>6 |                       | 13<br>13<br>0<br>0<br>7<br>7 |                  | ns   |                |

| Hold Times: $\overline{W}$ High to Address Invali<br>$\overline{E}$ High to Address Invali<br>$\overline{W}$ High to Data Invali<br>$\overline{E}$ High to Data Invali | d tEHAX                                   | 0<br>0<br>0<br>0           | _<br>_<br>_<br>_         | 0<br>0<br>0<br>0             | _<br>_<br>_<br>_      | 0<br>0<br>0<br>0             | _<br>_<br>_<br>_ | ns   |                |

| Write Pulse Width: Write Pulse Width (G Low<br>Write Pulse Width (G High<br>Write Pulse Width<br>Enable to End of Write<br>Enable to End of Write                      | tWLEH<br>tELWH                            | 9<br>8<br>9<br>9           | _<br>_<br>_<br>_<br>_    | 10<br>9<br>10<br>10          | _<br>_<br>_<br>_<br>_ | 13<br>12<br>13<br>13<br>13   | _<br>_<br>_<br>_ | ns   | 5<br>6<br>5, 6 |

| Output Buffer Control: $\overline{\overline{W}}$ High to Output Activ $\overline{\overline{W}}$ Low to Output High-                                                    |                                           | 3<br>0                     | <u> </u>                 | 3<br>0                       | <u> </u>              | 3<br>0                       | —<br>9           | ns   | 7<br>7, 8      |

#### NOTES:

- 1. W (write) refers to either one or both byte write enables  $\overline{LW}$  and  $\overline{UW}$ .

- 2. AL and DL are equal to VIH for all asynchronous cycles.

- 3. Both Write Enables must be equal to  $V_{\mbox{\scriptsize IH}}$  for all address transitions.

- 4. All write cycle timing is referenced from the last valid address to the first transitioning address.

- 5. If  $\overline{E}$  goes high coincident with or before  $\overline{W}$  goes high the output will remain in a high impedance state.

- 6. If  $\overline{E}$  goes low coincident with or after  $\overline{W}$  goes low the output will remain in a high impedance state.

- 7. Transition is measured ± 500 mV from steady–state voltage with output load of Figure 1B. This parameter is sampled and not 100% tested. At any given voltage and temperature, twLqz is less than twHqx for a given device.

- 8. If  $\overline{G}$  goes low coincident with or after  $\overline{W}$  goes low the output will remain in a high impedance state.

MCM67A618 MOTOROLA FAST SRAM

# **ASYNCHRONOUS WRITE CYCLE**

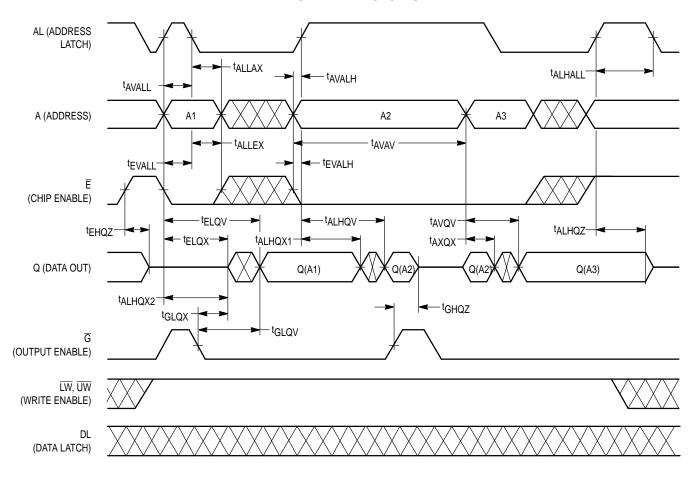

## LATCHED READ CYCLE TIMING (See Notes 1 and 2)

|                                                                                                                                                                         |                                                                                                                               | MCM67A618-10               |                     | MCM67                      | A618–12             | MCM67A618-15               |                       |      |        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------|----------------------------|---------------------|----------------------------|-----------------------|------|--------|

| Parameter                                                                                                                                                               | Symbol                                                                                                                        | Min                        | Max                 | Min                        | Max                 | Min                        | Max                   | Unit | Notes  |

| Read Cycle Times                                                                                                                                                        | t <sub>AVAV</sub>                                                                                                             | 10                         | _                   | 12                         | _                   | 15                         | _                     | ns   | 3      |

| Access Times:  Address Valid to Output Valid  E Low to Output Valid  AL High to Output Valid  Output Enable Low to Output Valid                                         | <sup>t</sup> AVQV<br><sup>t</sup> ELQV<br><sup>t</sup> ALHQV<br><sup>t</sup> GLQV                                             | _<br>_<br>_<br>_           | 10<br>10<br>10<br>5 | _<br>_<br>_<br>_           | 12<br>12<br>12<br>6 | <br>                       | 15<br>15<br>15<br>7   | ns   | 3<br>4 |

| Setup Times:  Address Valid to AL Low  E Valid to AL Low  Address Valid to AL High  E Valid to AL High                                                                  | <sup>†</sup> AVALL<br><sup>†</sup> EVALL<br><sup>†</sup> AVALH<br><sup>†</sup> EVALH                                          | 2<br>2<br>0<br>0           | _<br>_<br>_<br>_    | 2<br>2<br>0<br>0           | _<br>_<br>_<br>_    | 2<br>2<br>0<br>0           | _<br>_<br>_<br>_      | ns   | 4 4    |

| Hold Times:  AL Low to Address Invalid  AL Low to E Invalid                                                                                                             | <sup>†</sup> ALLAX<br><sup>†</sup> ALLEX                                                                                      | 2<br>2                     | _                   | 2<br>2                     | _                   | 3<br>3                     | _                     | ns   | 4      |

| Output Hold:  Address Invalid to Output Invalid  AL High to Output Invalid                                                                                              | <sup>†</sup> AXQX<br><sup>†</sup> ALHQX1                                                                                      | 4<br>4                     | _<br>_              | 4<br>4                     | _<br>_              | 4<br>4                     | _<br>_                | ns   |        |

| Address Latch Pulse Width                                                                                                                                               | <sup>t</sup> ALHALL                                                                                                           | 5                          | _                   | 5                          | _                   | 5                          | _                     | ns   |        |

| Output Buffer Control:  E Low to Output Active G Low to Output Active AL High to Output Active E High to Output High–Z AL High to Output High–Z G High to Output High–Z | <sup>†</sup> ELQX<br><sup>†</sup> GLQX<br><sup>†</sup> ALHQX2<br><sup>†</sup> EHQZ<br><sup>†</sup> ALHQZ<br><sup>†</sup> GHQZ | 3<br>1<br>3<br>2<br>2<br>2 |                     | 3<br>1<br>3<br>2<br>2<br>2 |                     | 3<br>1<br>3<br>2<br>2<br>2 | —<br>—<br>9<br>9<br>7 | ns   | 5      |

#### NOTES:

- 1. Both Write Enable Signals ( $\overline{\text{LW}}, \overline{\text{UW}})$  are equal to VIH for all read cycles.

- 2. All read cycle timing is referenced from the last valid address to the first transitioning address.

- 3. Addresses valid prior to or coincident with  $\overline{\mathsf{E}}$  going low.

- 4. All latched inputs must meet the specified setup and hold times with stable logic levels for ALL falling edges of address latch (AL) and data latch (DL).

- 5. Transition is measured ± 500 mV from steady–state voltage with output load of Figure 1B. This parameter is sampled and not 100% tested. At any given voltage and temperature, tehQZ is less than telQX and telQX is less than telQX and telQX for a given device.

MCM67A618 MOTOROLA FAST SRAM

# **LATCHED READ CYCLES**

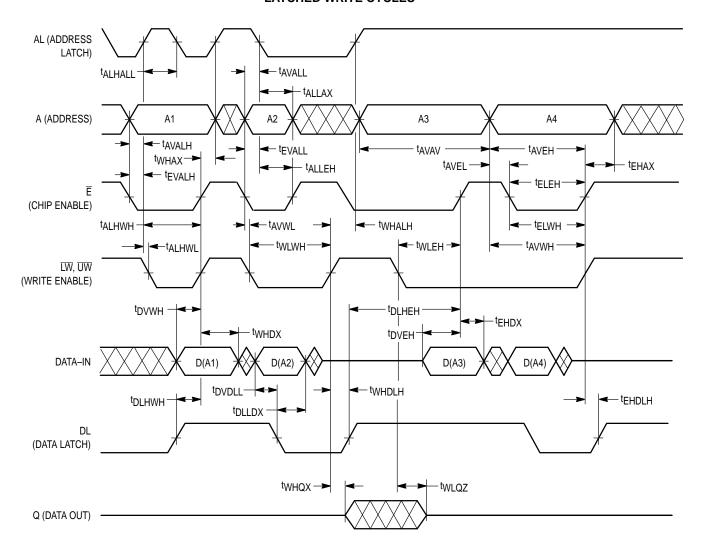

## LATCHED WRITE CYCLE TIMING (See Notes 1, 2, and 3)

|                                               |                     | MCM67 | M67A618-10 MCM67A618-12 |     | MCM67    | A618–15 |        |      |       |

|-----------------------------------------------|---------------------|-------|-------------------------|-----|----------|---------|--------|------|-------|

| Parameter                                     | Symbol              | Min   | Max                     | Min | Max      | Min     | Max    | Unit | Notes |

| Write Cycle Times:                            | t <sub>AVAV</sub>   | 10    | _                       | 12  | _        | 15      | _      | ns   | 4     |

| Address Valid to Address Valid                |                     |       |                         |     |          |         |        |      |       |

| Setup Times:                                  |                     |       |                         |     |          |         |        | ns   |       |

| Address Valid to End of Write                 | <sup>t</sup> AVWH   | 9     | -                       | 10  | _        | 13      | _      |      |       |

| Address Valid to End of Write                 | <sup>t</sup> AVEH   | 9     | -                       | 10  | _        | 13      | _      |      |       |

| E Valid to AL Low                             | <sup>t</sup> EVALL  | 2     | –                       | 2   | _        | 2       | _      |      |       |

| Address Valid to AL Low                       | <sup>t</sup> AVALL  | 2     | -                       | 2   | _        | 2       | _      |      |       |

| E Valid to AL High                            | <sup>t</sup> EVALH  | 0     | -                       | 0   | _        | 0       | _<br>_ |      |       |

| Address Valid to AL High                      | <sup>t</sup> AVALH  | 0     | -                       | 0   | l —      | 0       | _      |      |       |

| AL High to $\overline{\mathbb{W}}$ Low        | tALHWL              | 0     | -                       | 0   | l —      | 0       |        |      |       |

| Address Valid to $\overline{\mathbb{W}}$ Low  | <sup>t</sup> AVWL   | 0     | -                       | 0   | _        | 0       | _      |      |       |

| Address Valid to $\overline{E}$ Low           | <sup>t</sup> AVEL   | 0     | -                       | 0   | _        | 0       | _      | ĺ    |       |

| Data Valid to DL Low                          | <sup>t</sup> DVDLL  | 2     | -                       | 2   | _        | 2       | _      |      |       |

| Data Valid to $\overline{\underline{W}}$ High | <sup>t</sup> DVWH   | 5     | -                       | 6   | _        | 7       | _      |      |       |

| Data Valid to E High                          | <sup>t</sup> DVEH   | 5     | -                       | 6   | _        | 7       | _      |      |       |

| DL High to W High                             | <sup>t</sup> DLHWH  | 5     | -                       | 6   | _        | 7       | _      |      |       |

| DL High to $\overline{E}$ High                | <sup>t</sup> DLHEH  | 5     | -                       | 6   | -        | 7       | _      |      |       |

| Hold Times:                                   |                     |       |                         |     |          |         |        | ns   |       |

| AL Low to $\overline{E}$ High                 | <sup>t</sup> ALLEH  | 2     | l –                     | 2   | _        | 3       | _      |      | 4     |

| AL Low to Address Invalid                     | tALLAX              | 2     | l –                     | 2   | _        | 3       | _      |      | 4     |

| DL Low to Data Invalid                        | tDLLDX              | 2     | l –                     | 2   | _        | 3       | _      |      |       |

| W High to Address Invalid                     | tWHAX               | 0     | -                       | 0   | l –      | 0       | _      |      |       |

| E High to Address Invalid                     | <sup>t</sup> EHAX   | 0     | -                       | 0   | _        | 0       | _      |      |       |

| W High to Data Invalid                        | tWHDX               | 0     | –                       | 0   | _        | 0       | _      |      |       |

| E High to Data Invalid                        | tEHDX               | 0     | -                       | 0   | _        | 0       | _      |      |       |

| W High to DL High                             | tWHDLH              | 0     | -                       | 0   | _        | 0       | _      |      |       |

| E High to DL High                             | <sup>t</sup> EHDLH  | 0     | -                       | 0   | _        | 0       | _      |      |       |

| $\overline{\mathbb{W}}$ High to AL High       | tWHALH              | 0     | -                       | 0   | -        | 0       | _      |      |       |

| Write Pulse Width:                            |                     |       |                         |     |          |         |        | ns   |       |

| AL High to $\overline{W}$ High                | t <sub>ALHWH</sub>  | 9     | l –                     | 10  |          | 13      | _      |      | 5     |

| Write Pulse Width (G Low)                     | tWLWH               | 9     | l –                     | 10  | l —      | 13      | —      | ĺ    |       |

| Write Pulse Width (G High)                    | tWLWH               | 8     | l –                     | 9   | l –      | 12      | _      |      |       |

| Write Pulse Width                             | tWLEH               | 9     | l –                     | 10  | l –      | 13      | -      |      | 6     |

| Enable to End of Write                        | tELWH               | 9     | -                       | 10  | -        | 13      | _      | ĺ    | 7     |

| Enable to End of Write                        | <sup>t</sup> ELEH   | 9     | -                       | 10  | -        | 13      | _      |      | 6, 7  |

| Address Latch Pulse Width                     | <sup>t</sup> ALHALL | 5     | _                       | 5   | <u> </u> | 5       | _      | ns   | 4     |

| Output Buffer Control:                        |                     |       |                         |     |          |         |        | ns   |       |

| W High to Output Active                       | tWHQX               | 3     | l –                     | 3   | l –      | 3       | l —    |      | 8     |

| W Low to Output High-Z                        | tWLQZ               | 0     | 5                       | 0   | 6        | 0       | 9      |      | 8, 9  |

# NOTES:

- 1.  $\overline{W}$  refers to either one or both byte write enables  $\overline{LW}$  and  $\overline{UW}$ .

- 2. A write occurs during the overlap of  $\overline{E}$  low and  $\overline{W}$  low.

- 3. Both Write Enables must be equal to  $V_{\mbox{\scriptsize IH}}$  for all address transitions.

- 4. All write cycle timing is referenced from the last valid address to the first transitioning address.

- 5. All latched inputs must meet the specified setup and hold times with stable logic levels for ALL falling edges of address latch (AL) and data latch (DL).

- 6. If  $\overline{E}$  goes high coincident with or before  $\overline{W}$  goes high the output will remain in a high impedance state.

- 7. If  $\overline{E}$  goes low coincident with or after  $\overline{W}$  goes low the output will remain in a high impedance state.

- 8. Transition is measured  $\pm$  500 mV from steady–state voltage with output load of Figure 1B. This parameter is sampled and not 100% tested. At any given voltage and temperature,  $t_{WLQZ}$  is less than  $t_{WHQX}$  for a given device.

- 9. If  $\overline{G}$  goes low coincident with or after  $\overline{W}$  goes low the output will remain in a high impedance state.

#### **LATCHED WRITE CYCLES**

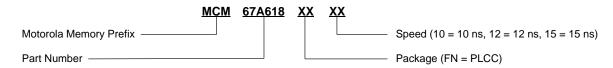

# ORDERING INFORMATION (Order by Full Part Number)

Full Part Numbers — MCM67A618FN10 MCM67A618FN12 MCM67A618FN15

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and "a" are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

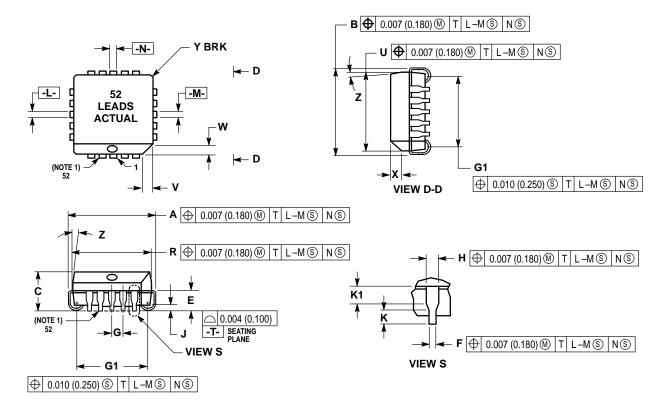

#### PACKAGE DIMENSIONS

**FN PACKAGE** 52-LEAD PLCC **CASE 778-02**

#### NOTES

1982

- DUE TO SPACE LIMITATION, CASE 778-02 SHALL BE REPRESENTED BY A GENERAL (SMALLER) CASE OUTLINE DRAWING RATHER THAN SHOWING ALL 52 LEADS.

DATUMS -L-, -M-, AND -N- DETERMINED WHERE TOP OF

- LEAD SHOULDER EXITS PLASTIC BODY AT MOLD

- PARTING LINE.

DIM 61, TRUE POSITION TO BE MEASURED AT DATUM -T-,

SEATING PLANE.

DIM R AND U DO NOT INCLUDE MOLD FLASH.

- ALLOWABLE MOLD FLASH IS 0.010 (0.250) PER SIDE DIMENSIONING AND TOLERANCING PER ANSI Y14.5M,

- CONTROLLING DIMENSION: INCH.

- THE PACKAGE TOP MAY BE SMALLER THAN THE PACKAGE BOTTOM BY UP TO 0.012 (0.300). DIMENSIONS R AND U ARE DETERMINED AT THE OUTERMOST EXTREMES OF THE PLASTIC BODY EXCLUSIVE OF MOLD FLASH, TIE BAR BURRS, GATE BURRS AND INTERLEAD FLASH, BUT INCLUDING ANY MISMATCH BETWEEN THE

- PLASH, BUT INCLUDING ANY MISMATCH BETWEEN THE TOP AND BOTTOM OF THE PLASTIC BODY.

DIMENSION H DOES NOT INCLUDE DAMBAR PROTRUSION OR INTRUSION. THE DAMBAR PROTRUSION(S) SHALL NOT CAUSE THE H DIMENSION TO BE GREATER THAN 0.037 (0.940). THE DAMBAR INTRUSION(S) SHALL NOT CAUSE THE H DIMENSION TO BE SMALLER THAN 0.025 (0.635).

|     | INC   | HES   | MILLIN | METERS |

|-----|-------|-------|--------|--------|

| DIM | MIN   | MAX   | MIN    | MAX    |

| Α   | 0.785 | 0.795 | 19.94  | 20.19  |

| В   | 0.785 | 0.795 | 19.94  | 20.19  |

| С   | 0.165 | 0.180 | 4.20   | 4.57   |

| Е   | 0.090 | 0.110 | 2.29   | 2.79   |

| F   | 0.013 | 0.019 | 0.33   | 0.48   |

| G   | 0.05  | 0 BSC | 1.27   | BSC    |

| Н   | 0.026 | 0.032 | 0.66   | 0.81   |

| J   | 0.020 | _     | 0.51   | _      |

| K   | 0.025 | _     | 0.64   | _      |

| R   | 0.750 | 0.756 | 19.05  | 19.20  |

| U   | 0.750 | 0.756 | 19.05  | 19.20  |

| ٧   | 0.042 | 0.048 | 1.07   | 1.21   |

| W   | 0.042 | 0.048 | 1.07   | 1.21   |

| Х   | 0.042 | 0.056 | 1.07   | 1.42   |

| Υ   | _     | 0.020 |        | 0.50   |

| Z   | 2°    | 10°   | 2°     | 10°    |

| G1  | 0.710 | 0.730 | 18.04  | 18.54  |

| K1  | 0.040 | _     | 1.02   | _      |

|     |       |       |        |        |

#### **Literature Distribution Centers:**

USA/EUROPE: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141, Japan.

ASIA PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.