# CrystalClear® Audio Codec '97 for Portable Computing

#### Features

- Integrated Asynchronous I<sup>2</sup>S Input Port (ZV Port)

- Integrated High-Performance Microphone Pre-Amplifier

- Integrated Digital Effects Processing for Bass and Treble Response

- Digital Docking Including an I<sup>2</sup>S Output, 3 Synchronous I<sup>2</sup>S Inputs

- Performance Oriented Digital Mixer

- SRS<sup>©</sup> 3D Stereo Enhancement

- On-chip PLL for use with External Clock Sources

- Dedicated Microphone Analog-to-Digital Converter

- Sample Rate Converters

- S/PDIF Digital Audio Output

- ◆ AC '97 2.1 Compliant

- PC Beep Bypass

- 20-bit Stereo Digital-to-Analog Converters

- 18-bit Stereo Analog-to-Digital Converters

- Three Analog Line-level Stereo Inputs for LINE IN, VIDEO, and AUX

- High Quality Pseudo-Differential CD Input

- Extensive Power Management Support

- Meets or Exceeds the Microsoft® PC 99 and PC 2001 Audio Performance Requirements

# Description

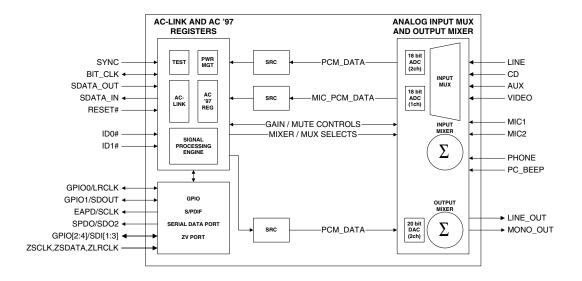

The CS4205 is an AC '97 2.1 compliant stereo audio codec designed for PC multimedia systems. It uses industry leading CrystalClear® delta-sigma and mixed signal technology. The CS405 is the first Cirrus AC '97 audio codec to feature digital centric mixing and digital effects. This advanced technology and these features are designed to help enable the design of PC 99 and PC 2001 compliant high-quality audio systems for desktop, portable, and entertainment PCs.

Coupling the CS4205 with a PCI audio accelerator or core logic supporting the AC '97 interface, implements a cost effective, superior quality audio solution. The CS4205 surpasses PC 99, PC 2001, and AC '97 2.1 audio quality standards.

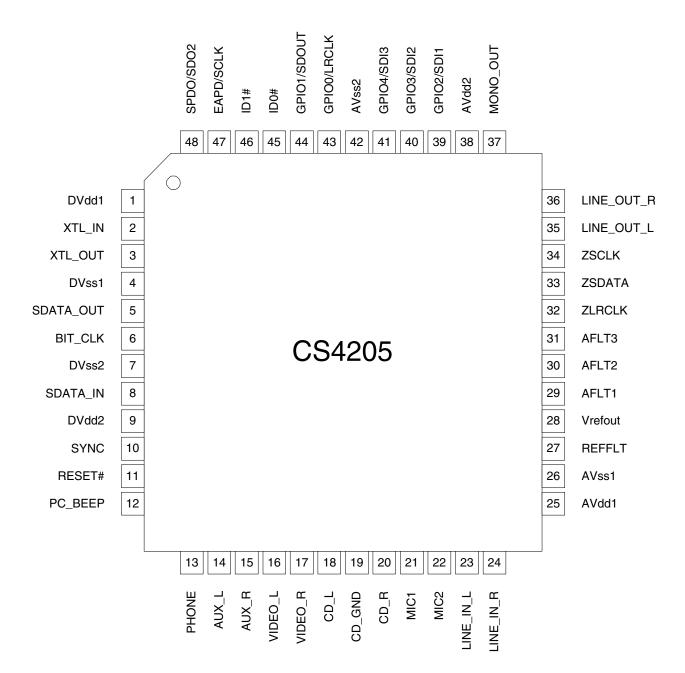

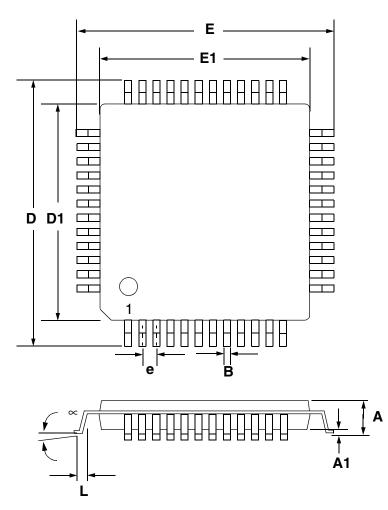

#### **ORDERING INFO**

CS4205-KQ 48-pin TQFP 9x9x1.4 mm

Preliminary Product Information

This document contains information for a new product. Cirrus Logic reserves the right to modify this product without notice.

#### TABLE OF CONTENTS

| 1. | CHARACTERISTICS AND SPECIFICATIONS             | 7  |

|----|------------------------------------------------|----|

|    | Analog Characteristics                         | 7  |

|    | Absolute Maximum Ratings                       | 8  |

|    | Recommended Operating Conditions               |    |

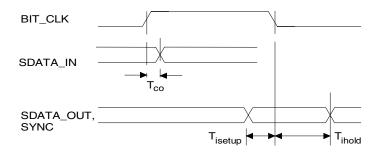

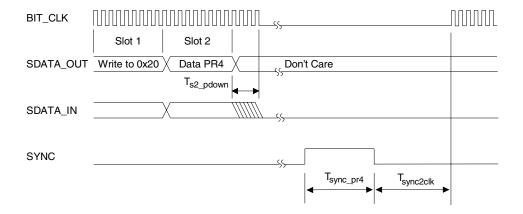

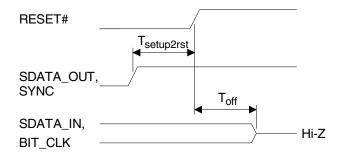

|    | AC '97 Serial Port Timing                      | 10 |

| 2. | GENERAL DESCRIPTION                            | 13 |

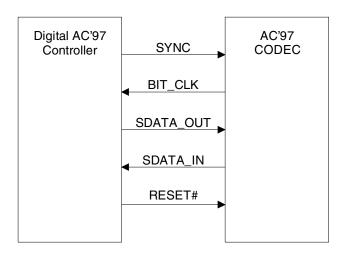

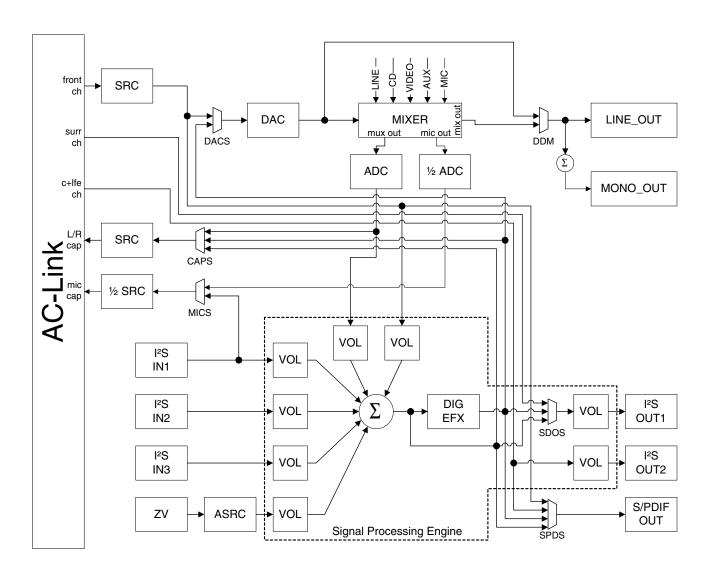

|    | 2.1 AC-Link                                    | 13 |

|    | 2.2 Control Registers                          | 14 |

|    | 2.3 Sample Rate Converters                     | 14 |

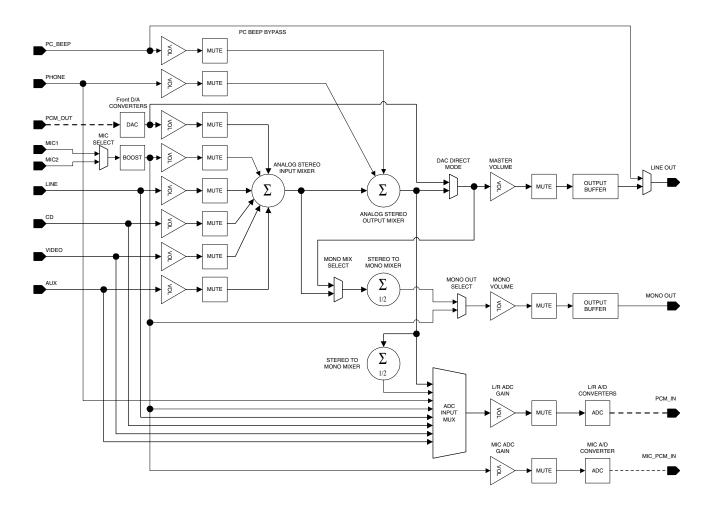

|    | 2.4 Mixers                                     | 14 |

|    | 2.5 Input Mux                                  | 14 |

|    | 2.6 Volume Control                             |    |

|    | 2.7 Dedicated Mic Record Path                  |    |

| 3. | DIGITAL SIGNAL PATHS                           |    |

|    | 3.1 Analog Centric Mode                        |    |

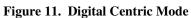

|    | 3.2 Digital Centric Mode                       |    |

|    | 3.3 Host Processing Mode                       |    |

|    | 3.4 Multi-Channel Mode                         |    |

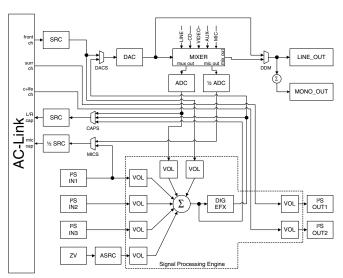

| 4. | AC-LINK FRAME DEFINITION                       | _  |

|    | 4.1 AC-Link Serial Data Output Frame           |    |

|    | 4.1.1 Serial Data Output Slot Tags (Slot 0)    |    |

|    | 4.1.2 Command Address Port (Slot 1)            |    |

|    | 4.1.3 Command Data Port (Slot 2)               |    |

|    | 4.1.4 PCM Playback Data (Slots 3-11)           |    |

|    | 4.1.5 GPIO Pin Control (Slot12)                |    |

|    | 4.2 AC-Link Serial Data Input Frame            |    |

|    | 4.2.1 Serial Data Input Slot Tag Bits (Slot 0) |    |

|    | 4.2.2 Status Address Port (Slot 1)             |    |

|    | 4.2.3 Status Data Port (Slot 2)                |    |

|    | 4.2.4 PCM Capture Data (Slot 3-8)              |    |

|    | 4.2.5 GPIO Pin Status (Slot 12)                |    |

| _  | 4.3 AC-Link Protocol Violation - Loss of SYNC  |    |

| 5. | REGISTER INTERFACE                             |    |

|    | 5.1 Reset Register (Index 00h)                 |    |

|    | 5.2 Master Volume Register (Index 02h)         | 27 |

# **Contacting Cirrus Logic Support**

For a complete listing of Direct Sales, Distributor, and Sales Representative contacts, visit the Cirrus Logic web site at: http://www.cirrus.com/corporate/contacts/sales.cfm

Microsoft is a registered trademark of Microsoft Corporation in the United States and/or other countries. Intel is a registered trademark of Intel Corporation.

CrystalClear is a registered trademark of Cirrus Logic.

Preliminary product information describes products which are in production, but for which full characterization data is not yet available. Advance product information describes products which are in development and subject to development changes. Cirrus Logic, Inc. has made best efforts to ensure that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (express or implied). No responsibility is assumed by Cirrus Logic, Inc. for the use of this information, nor for infringements of patents or other rights of third parties. This document is the property of Cirrus Logic, Inc. and implies no license under patents, copyrights, trademarks, or trade secrets. No part of this publication may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc. Items from any Cirrus Logic website or disk may be printed for use by the user. However, no part of the printout or electronic files may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc. Furthermore, no part of this publication may be used as a basis for manufacture or sale of any items without the prior written consent of Cirrus Logic, Inc. The names of products of Cirrus Logic, Inc. or other vendors and suppliers appearing in this document may be trademarks or service marks of their respective owners which may be registered in some jurisdictions. A list of Cirrus Logic, Inc. trademarks and service marks can be found at http://www.cirrus.com.

| 5.3 Mono Volume Register (Index 06h) 5.4 Master Tone Control Register (Index 08h) 5.5 PC_BEEP Volume Register (Index 0Ch) 5.7 Microphone Volume Register (Index 0Ch) 5.8 Analog Mixer Input Gain Register (Index 10h - 18h) 5.9 Input Mux Select Register (Index 10h - 18h) 5.9 Input Mux Select Register (Index 10h - 18h) 5.10 Record Gain Register (Index 10h) 5.11 Record Gain Mic Register (Index 10h) 5.12 General Purpose Register (Index 20h) 5.13 3D Control Register (Index 22h) 5.14 Powerdown Control/Status Register (Index 28h) 5.15 Extended Audio ID Register (Index 28h) 5.16 Extended Audio Status/Control Register (Index 2Ah) 5.17 Audio Sample Rate Control Registers (Index 2Ch - 34h) 5.18 Extended Modem ID Register (Index 3Ch) 5.19 Extended Modem ID Register (Index 3Ch) 5.20 GPIO Pin Configuration Register (Index 4Ch) 5.21 GPIO Pin Polarity/Type Configuration Register (Index 4Eh) 5.22 GPIO Pin Sticky Register (Index 50h) 5.23 GPIO Pin Status Register (Index 50h) 5.24 GPIO Pin Status Register (Index 50h) 5.25 AC Mode Control Register (Index 55h) 5.26 Misc. Crystal Control Register (Index 56h) 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Port Control Register (Index 66h) 5.29 Special Feature Address Register (Index 6Ch) 5.30 Special Feature Data Register (Index 6Ch) 5.31 Digital Mixer Input Volume Registers (Index 6Ch) 5.32 Serial Data Port Volume Control Registers (Index 6Ch, Address 00h - 05h) 5.33 Signal Processing Engine Control Registers (Index 6Ch, Address 06h) 5.34 Internal Error Condition Control/Status Register (Index 6Ch, Address 06h) 5.35 BIOS-Driver Interface Status Register (Index 6Ch, Address 06h) 5.36 VPort Control/Status Registers (Index 6Ch, Address 06h) 5.37 BIOS-Driver Interface Status Register (Index 6Ch, Address 0Ch - 0Dh) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Ch) 5.30 Vendor ID2 |                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 5.5 PC_BEEP Volume Register (Index Och) 5.6 Phone Volume Register (Index Och) 5.7 Microphone Volume Register (Index Och) 5.8 Analog Mixer Input Gain Registers (Index 10h - 18h) 5.9 Input Mux Select Register (Index 1Ah) 5.10 Record Gain Register (Index 1Ch) 5.11 Record Gain Mic Register (Index 1Ch) 5.12 General Purpose Register (Index 20h) 5.13 3D Control Register (Index 22h) 5.14 Powerdown Control/Status Register (Index 26h) 5.15 Extended Audio ID Register (Index 28h) 5.16 Extended Audio ID Register (Index 28h) 5.17 Audio Sample Rate Control Registers (Index 2Ch - 34h) 5.18 Extended Modem ID Register (Index 3Ch) 5.19 Extended Modem ID Register (Index 3Ch) 5.20 GPIO Pin Configuration Register (Index 4Ch) 5.21 GPIO Pin Polarity/Type Configuration Register (Index 4Eh) 5.22 GPIO Pin Sticky Register (Index 50h) 5.23 GPIO Pin Status Register (Index 54h) 5.24 GPIO Pin Status Register (Index 54h) 5.25 AC Mode Control Register (Index 54h) 5.26 Misc. Crystal Control Register (Index 60h) 5.27 S/PDIF Control Register (Index 66h) 5.28 Serial Port Control Register (Index 66h) 5.29 Special Feature Address Register (Index 66h) 5.30 Special Feature Data Register (Index 66h) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 06h - 07h 5.33 Signal Processing Engine Control Registers (Index 6Eh, Address 06h - 07h 5.34 Event Control Register (Index 6Eh, Address 06h - 07h 5.35 Event Data Port Volume Control Registers (Index 6Eh, Address 06h - 07h 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 06h - 07h 5.37 BIOS-Driver Interface Status Registers (Index 6Eh, Address 06h - 07h 5.38 Vendor ID1 Register (Index 7Eh) 6. SERIAL DATA PORTS 6. SERIAL DATA PORTS 6. 1 Overview 6. 2 Multi-Channel Expansion 6. 3 Digital Docking 6. 4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10. 10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                   | 2930313334353636373838383939                                               |

| 5.6 Phone Volume Register (Index 0Ch) 5.7 Microphone Volume Registers (Index 10h) 5.8 Analog Mixer Input Gain Registers (Index 10h - 18h) 5.9 Input Mux Select Register (Index 1Ah) 5.10 Record Gain Register (Index 1Ch) 5.11 Record Gain Mic Register (Index 1Ch) 5.12 General Purpose Register (Index 20h) 5.13 3D Control Register (Index 22h) 5.14 Powerdown Control/Status Register (Index 26h) 5.15 Extended Audio ID Register (Index 28h) 5.16 Extended Audio Status/Control Register (Index 2Ah) 5.17 Audio Sample Rate Control Registers (Index 2Ch - 34h) 5.18 Extended Modem ID Register (Index 3Ch) 5.19 Extended Modem Batus/Control Register (Index 3Ch) 5.10 GPIO Pin Configuration Register (Index 4Ch) 5.21 GPIO Pin Polarity/Type Configuration Register (Index 4Eh) 5.22 GPIO Pin Status Register (Index 50h) 5.23 GPIO Pin Wakeup Mask Register (Index 52h) 5.24 GPIO Pin Status Register (Index 54h) 5.25 AC Mode Control Register (Index 54h) 5.26 Misc. Crystal Control Register (Index 60h) 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Port Control Register (Index 6Ah) 5.29 Special Feature Address Register (Index 6Ch) 5.30 Special Feature Data Register (Index 6Ch) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 00h - 05h) 5.33 Signal Processing Engine Control Registers (Index 6Eh, Address 00h - 05h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 00h - 05h) 5.35 BIOS-Driver Interface Status Registers (Index 6Eh, Address 0Ch - 07h) 5.36 Vendor ID2 Register (Index 7Eh) 5.37 Port Control/Status Registers (Index 6Eh, Address 0Ch - 07h) 5.38 Vendor ID1 Register (Index 7Eh) 5.39 Vendor ID2 Register (Index 7Eh) 5.30 Vendor ID2 Register (Index 7Eh) 5.31 Digital Docking 6.4 Serial Data Port Volume 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Portes 6.5 Register (Index 7Eh) 6.5 Register (Index 7Eh) 6.5 Register (Index 7Eh) 6.5 Register (Index 7Eh) 6.7 Reset Modes 6.8 DATA PORTS 6.9 LOUSY FUNCTIONS 6.9 L |                                                                            |

| 5.7 Microphone Volume Register (Index 10h - 18h) 5.8 Analog Mixer Input Gain Registers (Index 10h - 18h) 5.9 Input Mux Select Register (Index 11ch) 5.10 Record Gain Mic Register (Index 11ch) 5.11 Record Gain Mic Register (Index 11ch) 5.12 General Purpose Register (Index 20h) 5.13 3D Control Register (Index 22h) 5.14 Powerdown Control/Status Register (Index 26h) 5.15 Extended Audio ID Register (Index 28h) 5.16 Extended Audio ID Register (Index 28h) 5.17 Audio Sample Rate Control Register (Index 2Ch - 34h) 5.18 Extended Modem ID Register (Index 3Ch) 5.19 Extended Modem Batus/Control Register (Index 32h) 5.20 GPIO Pin Configuration Register (Index 4Ch) 5.21 GPIO Pin Polarity/Type Configuration Register (Index 4Eh) 5.22 GPIO Pin Sticky Register (Index 50h) 5.23 GPIO Pin Wakeup Mask Register (Index 52h) 5.24 GPIO Pin Status Register (Index 54h) 5.25 AC Mode Control Register (Index 54h) 5.26 Misc. Crystal Control Register (Index 66h) 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Port Control Register (Index 66h) 5.29 Special Feature Address Register (Index 6Ch) 5.30 Special Feature Data Register (Index 6Ch) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 00h - 05h) 5.33 Signal Processing Engine Control Registers (Index 6Eh, Address 00h - 07h 5.33 Signal Processing Engine Control Registers (Index 6Eh, Address 00h - 07h 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 00h - 07h 5.35 BIOS-Driver Interface Status Registers (Index 6Eh, Address 0Ch - 0Th) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Ch - 0Th) 5.38 Vendor ID1 Register (Index 7Eh) 5.39 Vendor ID2 Register (Index 7Eh) 5.39 Vendor ID1 Register (Index 7Eh) 5.39 Vendor ID2 Register (Index 7Eh) 5.39 Vendor ID2 Register (Index 7Eh) 5.30 Serial Doath PortS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10. 10.1.1 Co | 30<br>31<br>33<br>34<br>35<br>36<br>36<br>37<br>38<br>38<br>38<br>39<br>39 |

| 5.8 Analog Mixer Input Gain Registers (Index 10h - 18h) 5.9 Input Mux Select Register (Index 1Ah) 5.10 Record Gain Register (Index 1Ch) 5.11 Record Gain Mic Register (Index 1Eh) 5.12 General Purpose Register (Index 20h) 5.13 3D Control Register (Index 22h) 5.14 Powerdown Control/Status Register (Index 26h) 5.15 Extended Audio ID Register (Index 28h) 5.16 Extended Audio ID Register (Index 28h) 5.17 Audio Sample Rate Control Registers (Index 2Ch - 34h) 5.18 Extended Modem ID Register (Index 3Ch) 5.19 Extended Modem Bate Control Register (Index 2Ch - 34h) 5.19 Extended Modem Bate Control Register (Index 3Ch) 5.20 GPIO Pin Configuration Register (Index 4Ch) 5.21 GPIO Pin Polarity/Type Configuration Register (Index 4Eh) 5.22 GPIO Pin Sticky Register (Index 50h) 5.23 GPIO Pin Wakeup Mask Register (Index 52h) 5.24 GPIO Pin Status Register (Index 52h) 5.25 AC Mode Control Register (Index 5Eh) 5.26 Misc. Crystal Control Register (Index 5Eh) 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Data Port Control Register (Index 6Bh) 5.29 Special Feature Address Register (Index 6Ch) 5.30 Special Feature Data Register (Index 6Ch, Address 00h - 05h) 5.31 Digital Mixer Input Volume Registers (Index 6Ch, Address 06h - 07h 5.33 Signal Processing Engine Control Registers (Index 6Ch, Address 06h - 07h 5.34 Internal Error Condition Control/Status Registers (Index 6Ch, Address 0Ch - 0Dh) 5.35 EVENIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10. POWER MANAGEMENT 10.1AC '97 Reset Modes 10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                        | 3132333435363637383838393940                                               |

| 5.9 Input Mux Select Register (Index 1Ah) 5.10 Record Gain Register (Index 1Ch) 5.11 Record Gain Mic Register (Index 1Eh) 5.12 General Purpose Register (Index 20h) 5.13 3D Control Register (Index 22h) 5.14 Powerdown Control/Status Register (Index 26h) 5.15 Extended Audio ID Register (Index 28h) 5.16 Extended Audio ID Register (Index 28h) 5.17 Audio Sample Rate Control Register (Index 2Ch - 34h) 5.18 Extended Modem ID Register (Index 3Ch) 5.19 Extended Modem Batus/Control Register (Index 3Ch) 5.19 Extended Modem Status/Control Register (Index 3Ch) 5.19 Extended Modem Status/Control Register (Index 3Ch) 5.19 Extended Modem Status/Control Register (Index 3Ch) 5.20 GPIO Pin Configuration Register (Index 4Ch) 5.21 GPIO Pin Polarity/Type Configuration Register (Index 4Eh) 5.22 GPIO Pin Sticky Register (Index 50h) 5.23 GPIO Pin Wakeup Mask Register (Index 52h) 5.24 GPIO Pin Status Register (Index 54h) 5.25 AC Mode Control Register (Index 56h) 5.26 Misc. Crystal Control Register (Index 68h) 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Port Control Register (Index 68h) 5.29 Special Feature Address Register (Index 6Ch) 5.30 Special Feature Data Register (Index 6Eh) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 07h 5.33 Signal Processing Engine Control Registers (Index 6Eh, Address 06h - 07h 5.33 Signal Processing Engine Control Registers (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 08h - 0.5 and 10 Septimer Interface Control Registers (Index 6Eh, Address 06h - 07h 5.37 BIOS-Driver Interface Status Register (Index 6Eh, Address 0Ch - 0Dh) 5.36 ZV Port Control/Status Register (Index 6Eh, Address 0Ch - 0Dh) 5.37 Vendor ID2 Register (Index 7Ch) 5.39 Vendor ID3 Register (Index 7Ch) 5.30 Ve | 32<br>33<br>34<br>34<br>35<br>36<br>36<br>37<br>38<br>38<br>38<br>39<br>40 |

| 5.10 Record Gain Register (Index 1Ch) 5.11 Record Gain Mic Register (Index 1Eh) 5.12 General Purpose Register (Index 2Dh) 5.13 3D Control Register (Index 2Dh) 5.14 Powerdown Control/Status Register (Index 26h) 5.15 Extended Audio ID Register (Index 28h) 5.16 Extended Audio Status/Control Register (Index 2Ah) 5.17 Audio Sample Rate Control Registers (Index 2Ch - 34h) 5.18 Extended Modem ID Register (Index 3Ch) 5.19 Extended Modem ID Register (Index 3Ch) 5.20 GPIO Pin Configuration Register (Index 4Ch) 5.21 GPIO Pin Polarity/Type Configuration Register (Index 4Eh) 5.22 GPIO Pin Sticky Register (Index 50h) 5.23 GPIO Pin Status Register (Index 50h) 5.24 GPIO Pin Status Register (Index 54h) 5.25 AC Mode Control Register (Index 54h) 5.26 Misc. Crystal Control Register (Index 60h) 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Port Control Register (Index 6Ah) 5.29 Special Feature Address Register (Index 6Ch) 5.30 Special Feature Data Registers (Index 6Ch) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 06h - 07h 5.33 Signal Processing Engine Control Registers (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 06h - 07h 5.35 Surson Interface Control Registers (Index 6Eh, Address 06h - 07h 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 06h - 07h 5.37 BIOS-Driver Interface Status Registers (Index 6Eh, Address 0Ch - 0Dh) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Ch - 0Dh) 5.37 BIOS-Driver Interface Status Registers (Index 6Eh, Address 0Ch - 0Dh) 5.38 Vendor ID2 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Ch) 5.39 Vendor ID3 Register (Index 7Ch) 5.39 Vendor ID4 Register (Index 7Ch) 5.39 Vendor ID5 Register (Index 7Ch) 5.39 Vendor ID6 Register (Index 7Ch) 5.30 Vendor ID7 Register (Index 7Ch) 5.30 Vendor ID7 Register (Index 7Ch) 5.31 Dig1tal Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUN | 33<br>34<br>34<br>35<br>36<br>36<br>37<br>38<br>38<br>38<br>39<br>40       |

| 5.11 Record Gain Mic Register (Index 1Eh) 5.12 General Purpose Register (Index 22h) 5.13 3D Control Register (Index 22h) 5.14 Powerdown Control/Status Register (Index 26h) 5.15 Extended Audio ID Register (Index 28h) 5.16 Extended Audio ID Register (Index 28h) 5.17 Audio Sample Rate Control Registers (Index 2Ch) 5.17 Audio Sample Rate Control Register (Index 2Ch) 5.18 Extended Modem ID Register (Index 3Ch) 5.19 Extended Modem Bate Control Register (Index 3Ch) 5.20 GPIO Pin Configuration Register (Index 4Ch) 5.21 GPIO Pin Polarity/Type Configuration Register (Index 4Eh) 5.22 GPIO Pin Sticky Register (Index 50h) 5.23 GPIO Pin Status Register (Index 50h) 5.24 GPIO Pin Status Register (Index 54h) 5.25 AC Mode Control Register (Index 5Eh) 5.26 Misc. Crystal Control Register (Index 68h) 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Port Control Register (Index 6Ah) 5.29 Special Feature Address Register (Index 6Eh) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 00h - 07h 5.33 Signal Processing Engine Control Registers (Index 6Eh, Address 00h - 07h 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 00h - 07h 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 00h - 07h 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 00h - 07h 5.37 BIOS-Driver Interface Status Registers (Index 6Eh, Address 0Ch - 0Th) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh) 6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10. POWER MANAGEMENT 10.1AC '97 Reset Modes 10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                            |                                                                            |

| 5.12 General Purpose Register (Index 20h) 5.13 3D Control Register (Index 22h) 5.14 Powerdown Control/Status Register (Index 26h) 5.15 Extended Audio ID Register (Index 28h) 5.16 Extended Audio Status/Control Register (Index 2Ah) 5.17 Audio Sample Rate Control Registers (Index 2Ch - 34h) 5.18 Extended Modem ID Register (Index 3Ch) 5.19 Extended Modem ID Register (Index 3Ch) 5.19 Extended Modem Status/Control Register (Index 3Eh) 5.20 GPIO Pin Configuration Register (Index 4Ch) 5.21 GPIO Pin Polarity/Type Configuration Register (Index 4Eh) 5.22 GPIO Pin Sticky Register (Index 50h) 5.23 GPIO Pin Wakeup Mask Register (Index 52h) 5.24 GPIO Pin Status Register (Index 54h) 5.25 AC Mode Control Register (Index 54h) 5.26 Misc. Crystal Control Register (Index 60h) 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Port Control Register (Index 68h) 5.29 Special Feature Address Register (Index 6Ch) 5.30 Special Feature Data Register (Index 6Ch) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 06h - 07h 5.33 Signal Processing Engine Control Registers (Index 6Eh, Address 06h - 07h 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 06h - 07h 5.35 ZV Port Control/Status Registers (Index 6Eh, Address 06h - 07h 5.38 Vendor ID1 Register (Index 7Eh) 5.39 Vendor ID2 Register (Index 7Eh) 6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                        | 34<br>35<br>36<br>36<br>37<br>38<br>38<br>38<br>39<br>40                   |

| 5.13 3D Control Register (Index 22h) 5.14 Powerdown Control/Status Register (Index 26h) 5.15 Extended Audio ID Register (Index 28h) 5.16 Extended Audio Status/Control Register (Index 2Ah) 5.17 Audio Sample Rate Control Registers (Index 2Ch - 34h) 5.18 Extended Modem ID Register (Index 3Ch) 5.19 Extended Modem ID Register (Index 3Ch) 5.20 GPIO Pin Configuration Register (Index 4Ch) 5.21 GPIO Pin Polarity/Type Configuration Register (Index 4Eh) 5.22 GPIO Pin Sticky Register (Index 50h) 5.23 GPIO Pin Sticky Register (Index 50h) 5.24 GPIO Pin Status Register (Index 50h) 5.25 AC Mode Control Register (Index 52h) 5.26 Misc. Crystal Control Register (Index 60h) 5.27 S/PDIF Control Register (Index 60h) 5.28 Serial Port Control Register (Index 6Ah) 5.29 Special Feature Address Register (Index 6Ch) 5.30 Special Feature Data Register (Index 6Eh, Address 00h - 05h) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 00h - 07h 5.33 Signal Processing Engine Control Registers (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 00h - 07h 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 00h - 07h 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 00h - 07h 5.39 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Ch) 5.30 Vendor ID2 Register ( | 34<br>35<br>36<br>36<br>37<br>38<br>38<br>38<br>39<br>40                   |

| 5.14 Powerdown Control/Status Register (Index 26h) 5.15 Extended Audio ID Register (Index 28h) 5.16 Extended Audio Status/Control Register (Index 2Ch - 34h) 5.17 Audio Sample Rate Control Registers (Index 2Ch - 34h) 5.18 Extended Modem ID Register (Index 3Ch) 5.19 Extended Modem Status/Control Register (Index 3Eh) 5.20 GPIO Pin Configuration Register (Index 4Ch) 5.21 GPIO Pin Polarity/Type Configuration Register (Index 4Eh) 5.22 GPIO Pin Sticky Register (Index 50h) 5.23 GPIO Pin Wakeup Mask Register (Index 52h) 5.24 GPIO Pin Status Register (Index 54h) 5.25 AC Mode Control Register (Index 5Eh) 5.26 Misc. Crystal Control Register (Index 60h) 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Port Control Register (Index 68h) 5.29 Special Feature Address Register (Index 6Ch) 5.30 Special Feature Data Register (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 00h - 07h 5.33 Signal Processing Engine Control Registers (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 09h - 0.5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 00h - 0.5.37 BIOS-Driver Interface Status Register (Index 6Eh, Address 0Ch - 0Dh) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Ch) 5.39 Vendor ID3 Register (Index 7Ch) 5.39 Vendor ID4 Register (Index 7Ch) 5.39 Vendor ID5 Register (Index 7Ch) 5.39 Vendor ID4 Register (Index 7Ch) 5.39 Vendor ID5 Register (Index 7Ch) 5.39 Vendor ID7 Register (Index 7Ch) 5.39 Vendor ID8 Register (Index 7Ch)  |                                                                            |

| 5.15 Extended Audio ID Register (Index 28h) 5.16 Extended Audio Status/Control Register (Index 2Ah) 5.17 Audio Sample Rate Control Registers (Index 2Ch - 34h) 5.18 Extended Modem ID Register (Index 3Ch) 5.19 Extended Modem Status/Control Register (Index 3Eh) 5.20 GPIO Pin Configuration Register (Index 4Ch) 5.21 GPIO Pin Polarity/Type Configuration Register (Index 4Eh) 5.22 GPIO Pin Sticky Register (Index 50h) 5.23 GPIO Pin Status Register (Index 50h) 5.24 GPIO Pin Status Register (Index 54h) 5.25 AC Mode Control Register (Index 54h) 5.26 Misc. Crystal Control Register (Index 60h) 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Port Control Register (Index 6Ah) 5.29 Special Feature Address Register (Index 6Ch) 5.30 Special Feature Data Register (Index 6Eh) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 06h - 07h 5.33 Signal Processing Engine Control Registers (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 09h 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 09h 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 00h - 07h) 5.37 BIOS-Driver Interface Status Register (Index 6Eh, Address 00h - 05h) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Ch) 5.39 Vendor ID3 Register (Index 7Ch) 5.39 Vendor ID4 Register (Index 7Ch) 5.39 Vendor ID5 Register (Index 7Ch) 5.39 Vendor ID6 Register (Index 7Ch) 5.39 Vendor ID7 Register (Index 7Ch) 5.39 Vendor ID7 Register (Index 7Ch) 5.39 Vendor ID6 Register (Index 7Ch) 5.39 Vendor ID7 Register (Index 7Ch) 5.39 Vendor ID6 Register (Index 7Ch) 5.39 Vendor ID7 Register (Index 7Ch) 5.39 Vendor ID7 Register (Index 7Ch) 5.39 Vendor ID7 Register (Index 7Ch) 5.30 Register (Index 7Ch) 5. |                                                                            |

| 5.16 Extended Audio Status/Control Register (Index 2Ah) 5.17 Audio Sample Rate Control Registers (Index 2Ch - 34h) 5.18 Extended Modem ID Register (Index 3Ch) 5.19 Extended Modem Status/Control Register (Index 3Eh) 5.20 GPIO Pin Configuration Register (Index 4Ch) 5.21 GPIO Pin Polarity/Type Configuration Register (Index 4Eh) 5.22 GPIO Pin Sticky Register (Index 50h) 5.23 GPIO Pin Wakeup Mask Register (Index 52h) 5.24 GPIO Pin Status Register (Index 54h) 5.25 AC Mode Control Register (Index 5Eh) 5.26 Misc. Crystal Control Register (Index 60h) 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Port Control Register (Index 6Ch) 5.30 Special Feature Address Register (Index 6Ch) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Register (Index 6Eh, Address 06h - 07h 5.33 Signal Processing Engine Control Registers (Index 6Eh, Address 06h - 07h 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 09h 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 0Ch - 0Dh) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Ch - 0Dh) 5.37 BIOS-Driver Interface Status Register (Index 7Ah) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh) 6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                            |

| 5.17 Audio Sample Rate Control Registers (Index 2Ch - 34h) 5.18 Extended Modem ID Register (Index 3Ch) 5.19 Extended Modem Status/Control Register (Index 3Eh) 5.20 GPIO Pin Configuration Register (Index 4Ch) 5.21 GPIO Pin Polarity/Type Configuration Register (Index 4Eh) 5.22 GPIO Pin Sticky Register (Index 50h) 5.23 GPIO Pin Wakeup Mask Register (Index 52h) 5.24 GPIO Pin Status Register (Index 54h) 5.25 AC Mode Control Register (Index 54h) 5.26 Misc. Crystal Control Register (Index 60h) 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Port Control Register (Index 6Ah) 5.29 Special Feature Address Register (Index 6Ch) 5.30 Special Feature Data Register (Index 6Eh, Address 00h - 07h 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 06h - 07h 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 06h - 07h 5.33 Signal Processing Engine Control Registers (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 09h) 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 09h - 07h) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Ch - 0Dh) 5.37 BIOS-Driver Interface Status Registers (Index 6Eh, Address 0Eh - 0Fh) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh) 6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10.1.1 Cold Reset 10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37<br>38<br>38<br>39<br>39<br>40                                           |

| 5.18 Extended Modem ID Register (Index 3Ch) 5.19 Extended Modem Status/Control Register (Index 3Eh) 5.20 GPIO Pin Configuration Register (Index 4Ch) 5.21 GPIO Pin Polarity/Type Configuration Register (Index 4Eh) 5.22 GPIO Pin Sticky Register (Index 50h) 5.23 GPIO Pin Status Register (Index 52h) 5.24 GPIO Pin Status Register (Index 54h) 5.25 AC Mode Control Register (Index 5Eh) 5.26 Misc. Crystal Control Register (Index 60h) 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Port Control Register (Index 6Ah) 5.29 Special Feature Address Register (Index 6Ch) 5.30 Special Feature Data Register (Index 6Eh, Address 00h - 05h) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 06h - 07h 5.33 Signal Processing Engine Control Registers (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 09h - 05h) 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 0Ch - 0Dh) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Ch - 0Dh) 5.37 BIOS-Driver Interface Status Register (Index 7Ah) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh) 6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10.1.1 Cold Reset 10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                            |

| 5.19 Extended Modem Status/Control Register (Index 3Eh) 5.20 GPIO Pin Configuration Register (Index 4Ch) 5.21 GPIO Pin Polarity/Type Configuration Register (Index 4Eh) 5.22 GPIO Pin Sticky Register (Index 50h) 5.23 GPIO Pin Wakeup Mask Register (Index 52h) 5.24 GPIO Pin Status Register (Index 54h) 5.25 AC Mode Control Register (Index 5Eh) 5.26 Misc. Crystal Control Register (Index 60h) 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Port Control Register (Index 68h) 5.29 Special Feature Address Register (Index 6Eh) 5.30 Special Feature Data Register (Index 6Eh) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 07h 5.33 Signal Processing Engine Control Registers (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 09h 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 00h - 0Dh) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Ch - 0Dh) 5.37 BIOS-Driver Interface Status Register (Index 7Ah) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh) 6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10.1.1 Cold Reset 10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38<br>39<br>39<br>40                                                       |

| 5.20 GPIO Pin Configuration Register (Index 4Ch) 5.21 GPIO Pin Polarity/Type Configuration Register (Index 4Eh) 5.22 GPIO Pin Sticky Register (Index 50h) 5.23 GPIO Pin Wakeup Mask Register (Index 52h) 5.24 GPIO Pin Status Register (Index 54h) 5.25 AC Mode Control Register (Index 5Eh) 5.26 Misc. Crystal Control Register (Index 60h) 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Port Control Register (Index 6Ah) 5.29 Special Feature Address Register (Index 6Eh) 5.30 Special Feature Data Register (Index 6Eh) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 00h - 07h 5.33 Signal Processing Engine Control Registers (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 09h 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 00h - 0Dh) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Ch - 0Dh) 5.37 BIOS-Driver Interface Status Register (Index 7Ah) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh) 6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10.1.1 Cold Reset 10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38<br>39<br>40<br>40                                                       |

| 5.21 GPIO Pin Polarity/Type Configuration Register (Index 4Eh) 5.22 GPIO Pin Sticky Register (Index 50h) 5.23 GPIO Pin Wakeup Mask Register (Index 52h) 5.24 GPIO Pin Status Register (Index 54h) 5.25 AC Mode Control Register (Index 55h) 5.26 Misc. Crystal Control Register (Index 60h) 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Port Control Register (Index 6Ah) 5.29 Special Feature Address Register (Index 6Ch) 5.30 Special Feature Data Register (Index 6Eh) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 09h 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 0Ch - 0Dh) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Ch - 0Dh) 5.37 BIOS-Driver Interface Status Register (Index 6Eh, Address 0Ch - 0Dh) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh) 6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10.1AC '97 Reset Modes 10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39<br>40<br>40                                                             |

| 5.22 GPIO Pin Sticky Register (Index 50h) 5.23 GPIO Pin Wakeup Mask Register (Index 52h) 5.24 GPIO Pin Status Register (Index 54h) 5.25 AC Mode Control Register (Index 55h) 5.26 Misc. Crystal Control Register (Index 60h) 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Port Control Register (Index 6Ah) 5.29 Special Feature Address Register (Index 6Ch) 5.30 Special Feature Data Register (Index 6Eh) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 08h) 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 00h - 07h) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Ch - 0Dh) 5.37 BIOS-Driver Interface Status Register (Index 6Eh, Address 0Ch - 0Dh) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh) 6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10.11 Cold Reset 10.1.12 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 39<br>40<br>40                                                             |

| 5.23 GPIO Pin Wakeup Mask Register (Index 52h) 5.24 GPIO Pin Status Register (Index 54h) 5.25 AC Mode Control Register (Index 55h) 5.26 Misc. Crystal Control Register (Index 60h) 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Port Control Register (Index 6Ah) 5.29 Special Feature Address Register (Index 6Ch) 5.30 Special Feature Data Register (Index 6Eh) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 06h - 07h 5.33 Signal Processing Engine Control Register (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 09h 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 0Ch - 0Dh) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Ch - 0Dh) 5.37 BIOS-Driver Interface Status Register (Index 7Ah) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh) 6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10.1AC '97 Reset Modes 10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 40<br>40                                                                   |

| 5.24 GPIO Pin Status Register (Index 54h) 5.25 AC Mode Control Register (Index 5Eh) 5.26 Misc. Crystal Control Register (Index 60h) 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Port Control Register (Index 6Ah) 5.29 Special Feature Address Register (Index 6Ch) 5.30 Special Feature Data Register (Index 6Eh) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 06h - 07h 5.33 Signal Processing Engine Control Registers (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 09h 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 0Ch - 0Dh) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Ch - 0Dh) 5.37 BIOS-Driver Interface Status Register (Index 7Ah) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh) 6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10.1AC '97 Reset Modes 10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40                                                                         |

| 5.25 AC Mode Control Register (Index 5Eh) 5.26 Misc. Crystal Control Register (Index 60h) 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Port Control Register (Index 6Ah) 5.29 Special Feature Address Register (Index 6Ch) 5.30 Special Feature Data Register (Index 6Eh) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 06h - 07h 5.33 Signal Processing Engine Control Registers (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 09h 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 0Ch - 0Dh) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Ch - 0Dh) 5.37 BIOS-Driver Interface Status Register (Index 7Ah) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh) 6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10.1AC '97 Reset Modes 10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                            |

| 5.26 Misc. Crystal Control Register (Index 60h) 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Port Control Register (Index 6Ah) 5.29 Special Feature Address Register (Index 6Ch) 5.30 Special Feature Data Register (Index 6Eh) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 06h - 07h 5.33 Signal Processing Engine Control Registers (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 09h 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 0Ch - 0Dh) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Eh - 0Fh) 5.37 BIOS-Driver Interface Status Register (Index 7Ah) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh)  6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10.1AC '97 Reset Modes 10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 14                                                                         |

| 5.27 S/PDIF Control Register (Index 68h) 5.28 Serial Port Control Register (Index 6Ah) 5.29 Special Feature Address Register (Index 6Ch) 5.30 Special Feature Data Register (Index 6Eh) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 06h - 07h 5.33 Signal Processing Engine Control Register (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 09h 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 0Ch - 0Dh) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Eh - 0Fh) 5.37 BIOS-Driver Interface Status Register (Index 7Ah) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh)  6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10. POWER MANAGEMENT 10.1AC '97 Reset Modes 10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                            |

| 5.28 Serial Port Control Register (Index 6Ah) 5.29 Special Feature Address Register (Index 6Ch) 5.30 Special Feature Data Register (Index 6Eh) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 06h - 07h 5.33 Signal Processing Engine Control Register (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 09h 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 0Ch - 0Dh) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Ch - 0Dh) 5.37 BIOS-Driver Interface Status Register (Index 7Ah) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh) 6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10. POWER MANAGEMENT 10.1AC '97 Reset Modes 10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |

| 5.29 Special Feature Address Register (Index 6Ch) 5.30 Special Feature Data Register (Index 6Eh) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 06h - 07h 5.33 Signal Processing Engine Control Register (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 09h 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 0Ch - 0Dh) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Eh - 0Fh) 5.37 BIOS-Driver Interface Status Register (Index 7Ah) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh)  6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats  7. ZV PORT  8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF)  9. EXCLUSIVE FUNCTIONS  10. POWER MANAGEMENT  10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                            |

| 5.30 Special Feature Data Register (Index 6Eh) 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 06h - 07h 5.33 Signal Processing Engine Control Register (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 09h 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 0Ch - 0Dh) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Eh - 0Fh) 5.37 BIOS-Driver Interface Status Register (Index 7Ah) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh) 6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10. POWER MANAGEMENT 10.1.1 Cold Reset 10.1.1 Cold Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                            |

| 5.31 Digital Mixer Input Volume Registers (Index 6Eh, Address 00h - 05h) 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 06h - 07h 5.33 Signal Processing Engine Control Register (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 09h 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 0Ch - 0Dh) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Eh - 0Ph) 5.37 BIOS-Driver Interface Status Register (Index 7Ah) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh)  6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10. POWER MANAGEMENT 10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

| 5.32 Serial Data Port Volume Control Registers (Index 6Eh, Address 06h - 07h 5.33 Signal Processing Engine Control Register (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 09h 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 0Ch - 0Dh) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Eh - 0Ph) 5.37 BIOS-Driver Interface Status Register (Index 7Ah) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh) 6.1 Overview 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10.1AC '97 Reset Modes 10.1.1 Cold Reset 10.1.2 Warm Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                            |

| 5.33 Signal Processing Engine Control Register (Index 6Eh, Address 08h) 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 09 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 0Ch - 0Dh) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Eh - 0Fh) 5.37 BIOS-Driver Interface Status Register (Index 7Ah) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh)  6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT  8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10. 1AC '97 Reset Modes 10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                            |

| 5.34 Internal Error Condition Control/Status Registers (Index 6Eh, Address 09) 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 0Ch - 0Dh) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Eh - 0Fh) 5.37 BIOS-Driver Interface Status Register (Index 7Ah) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh)  6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats  7. ZV PORT  8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF)  9. EXCLUSIVE FUNCTIONS  10. 10 POWER MANAGEMENT  10.1AC '97 Reset Modes  10.1.1 Cold Reset  10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                            |

| 5.35 BIOS-Driver Interface Control Registers (Index 6Eh, Address 0Ch - 0Dh) 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Eh - 0Fh) 5.37 BIOS-Driver Interface Status Register (Index 7Ah) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh)  6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats  7. ZV PORT  8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF)  9. EXCLUSIVE FUNCTIONS  10.1AC '97 Reset Modes 10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            |

| 5.36 ZV Port Control/Status Registers (Index 6Eh, Address 0Eh - 0Fh) 5.37 BIOS-Driver Interface Status Register (Index 7Ah) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh)  6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats  7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10. POWER MANAGEMENT 10.1AC '97 Reset Modes 10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                            |

| 5.37 BIOS-Driver Interface Status Register (Index 7Ah) 5.38 Vendor ID1 Register (Index 7Ch) 5.39 Vendor ID2 Register (Index 7Eh)  6. SERIAL DATA PORTS 6.1 Overview 6.2 Multi-Channel Expansion 6.3 Digital Docking 6.4 Serial Data Formats 7. ZV PORT 8. SONY/PHILIPS DIGITAL INTERFACE (S/PDIF) 9. EXCLUSIVE FUNCTIONS 10. POWER MANAGEMENT 10.1AC '97 Reset Modes 10.1.1 Cold Reset 10.1.2 Warm Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            |