#### Features

- Integrated synchronous MOSFETs and current mode controller

- 1A continuous output current

- Up to 95% efficiency

- 4.5V to 5.5V input voltage

- Adjustable output from 1V to 3.8V

- Cycle-by-cycle current limit

- Precision reference

- $\pm 0.5\%$  load and line regulation

- Adjustable switching frequency to 1MHz

- Oscillator synchronization

possible

- Internal soft start

- Over temperature protection

- Under voltage lockout

- 16-pin QSOP package

#### Applications

- DSP, CPU Core and IO Supplies

- Logic/Bus Supplies

- Portable Equipment

- DC:DC Converter Modules

- GTL + Bus Power Supply

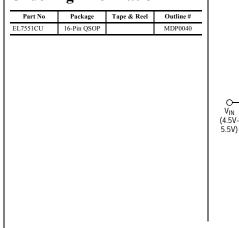

## **Ordering Information**

### **General Description**

The EL7551C is an integrated, synchronous step-down regulator with output voltage adjustable from 1.0V to 3.8V. It is capable of delivering 1A continuous current at up to 95% efficiency. The EL7551C operates at a constant frequency pulse width modulation (PWM) mode, making external synchronization possible. Patented on-chip resistorless current sensing enables current mode control, which provides cycle-by-cycle current limiting, over-current protection, and excellent step load response. The EL7551C is available in a fused-lead 16-pin QSOP package. With proper external components, the whole converter fits into a less than 0.4 in<sup>2</sup> area. The minimal external components and small size make this EL7551C ideal for desktop and portable applications.

The EL7551C is specified for operation over the -40°C to +85°C temperature range.

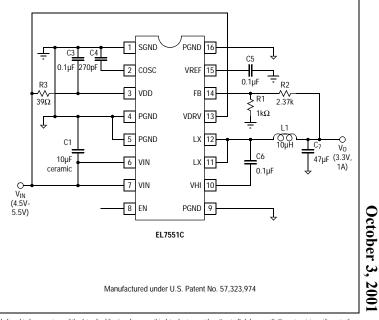

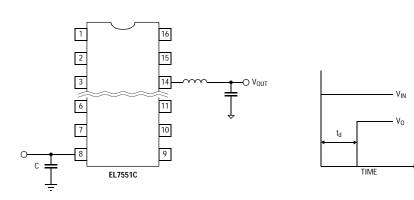

## **Typical Application Diagram**

Note: All information contained in this data sheet has been carefully checked and is believed to be accurate as of the date of publication; however, this data sheet cannot be a "controlled document". Current revisions, if any, to these specifications are maintained at the factory and are available upon your request. We recommend checking the revision level before finalization of your design documentation.

© 2001 Elantec Semiconductor, Inc

# EL7551C - Preliminary

Monolithic 1 Amp DC:DC Step-down Regulator

## Absolute Maximum Ratings (T<sub>A</sub> = 25°C)

| Supply Voltage between $V_{\rm IN}$ or $V_{\rm DD}$ and GND | +6.5V                            | Storage Temperature            | -65°C to +150°C |

|-------------------------------------------------------------|----------------------------------|--------------------------------|-----------------|

| V <sub>LX</sub> Voltage                                     | V <sub>IN</sub> +0.3V            | Operating Ambient Temperature  | -40°C to +85°C  |

| Input Voltage                                               | GND -0.3V, V <sub>DD</sub> +0.3V | Operating Junction Temperature | +135°C          |

| V <sub>HI</sub> Voltage                                     | GND -0.3V, $V_{LX}$ +6V          |                                |                 |

Important Note:

All parameters having Min/Max specifications are guaranteed. Typ values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$ .

#### **DC** Characteristics

$V_{DD} = V_{IN} = 5V$ ,  $T_A = T_J = 25^{\circ}C$ ,  $C_{OSC} = 1.2nF$ , unless otherwise specified.

| Parameter                          | Description                                      | Conditions                                               | Min   | Тур   | Max  | Unit   |

|------------------------------------|--------------------------------------------------|----------------------------------------------------------|-------|-------|------|--------|

| V <sub>REF</sub>                   | Reference Accuracy                               |                                                          | 1.24  | 1.26  | 1.28 | V      |

| VREFTC                             | Reference Temperature Coefficient                |                                                          |       | 50    |      | ppm/°C |

| VREFLOAD                           | Reference Load Regulation                        | $0 < I_{REF} < 50 \mu A$                                 | -1    |       |      | %      |

| V <sub>RAMP</sub>                  | Oscillator Ramp Amplitude                        |                                                          |       | 1.15  |      | V      |

| IOSC_CHG                           | Oscillator Charge Current                        | $0.1V < V_{OSC} < 1.25V$                                 |       | 200   |      | μΑ     |

| IOSC_DIS                           | Oscillator Discharge Current                     | $0.1V < V_{OSC} < 1.25V$                                 |       | 8     |      | mA     |

| I <sub>VDD</sub> +V <sub>DRV</sub> | V <sub>DD</sub> +V <sub>DRV</sub> Supply Current | $V_{EN} = 4V, F_{OSC} = 120kHz$                          |       | 3.5   | 5    | mA     |

| IVDD_OFF                           | V <sub>DD</sub> Standby Current                  | EN = 0                                                   |       | 1     | 1.5  | mA     |

| V <sub>DD_OFF</sub>                | V <sub>DD</sub> for Shutdown                     |                                                          | 3.5   |       | 4    | V      |

| V <sub>DD_ON</sub>                 | V <sub>DD</sub> for Startup                      |                                                          | 3.95  |       | 4.45 | V      |

| T <sub>OT</sub>                    | Over Temperature Threshold                       |                                                          |       | 135   |      | °C     |

| T <sub>HYS</sub>                   | Over Temperature Hysteresis                      |                                                          |       | 20    |      | °C     |

| I <sub>LEAK</sub>                  | Internal FET Leakage Current                     | $EN = 0$ , $L_X = 5V$ (low FET), $L_X = 0V$ (high FET)   |       |       | 10   | μΑ     |

| ILMAX                              | Peak Current Limit                               |                                                          | 2     |       |      | А      |

| R <sub>DSON</sub>                  | FET On Resistance                                | Wafer level test only                                    |       | 45    | 95   | mΩ     |

| RDSONTC                            | R <sub>DSON</sub> Tempco                         |                                                          |       | 0.2   |      | mΩ/°C  |

| V <sub>FB</sub>                    | Output Initial Accuracy                          | $I_{LOAD} = 0A$                                          | 0.960 | 0.975 | 0.99 | V      |

| V <sub>FB_LINE</sub>               | Output Line Regulation                           | $V_{IN} = 5V$ , $\Delta V_{IN} = 10\%$ , $I_{LOAD} = 0A$ |       | 0.5   |      | %      |

| V <sub>FB_LOAD</sub>               | Output Load Regulation                           | 0.1A < I <sub>LOAD</sub> < 1A                            |       | 0.5   |      | %      |

| V <sub>FB_TC</sub>                 | Output Temperature Stability                     | -40°C < $T_A$ < 85°C, $I_{LOAD}$ = 0.5A                  |       | ±1    |      | %      |

| I <sub>FB</sub>                    | Feedback Input Pull Up Current                   | $V_{FB} = 0V$                                            |       | 100   | 200  | nA     |

| V <sub>EN_HI</sub>                 | EN Input High Level                              |                                                          |       | 3.2   | 4    | V      |

| V <sub>EN_LO</sub>                 | EN Input Low Level                               |                                                          | 1     |       |      | V      |

| I <sub>EN</sub>                    | Enable Pull Up Current                           | $V_{\rm EN} = 0$                                         | -4    | -2.5  |      | μΑ     |

## **Closed Loop AC Electrical Characteristics**

| Parameter        | Description                   | Conditions | Min | Тур | Max | Unit |

|------------------|-------------------------------|------------|-----|-----|-----|------|

| FOSC             | Oscillator Initial Accuracy   |            | 105 | 117 | 130 | kHz  |

| tSYNC            | Minimum Oscillator Sync Width |            |     | 25  |     | ns   |

| M <sub>SS</sub>  | Soft Start Slope              |            |     | 0.5 |     | V/ms |

| t <sub>BRM</sub> | FET Break Before Make Delay   |            |     | 15  |     | ns   |

| t <sub>LEB</sub> | High Side FET Minimum On Time |            |     | 150 |     | ns   |

| D <sub>MAX</sub> | Maximum Duty Cycle            |            |     | 95  |     | %    |

| Pin Number | Pin Name | Pin Function                                                                                                                                                       |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | SGND     | Control circuit negative supply.                                                                                                                                   |

| 2          | COSC     | Oscillator timing capacitor. FOSC can be approximated by: FOSC (kHz) = 0.1843/COSC, COSC in µF.                                                                    |

| 3          | VDD      | Control circuit positive supply.                                                                                                                                   |

| 4          | PGND     | Ground return of the regulator. Connected to the source of the low-side synchronous NMOS power FET.                                                                |

| 5          | PGND     | Ground return of the regulator. Connected to the source of the low-side synchronous NMOS power FET.                                                                |

| 6          | VIN      | Power supply input of the regulator. Connected to the drain of the high-side NMOS power FET.                                                                       |

| 7          | VIN      | Power supply input of the regulator. Connected to the drain of the high-side NMOS power FET.                                                                       |

| 8          | EN       | Chip Enable, active high. A 2µA internal pull-up current enables the device if the pin is left open.                                                               |

| 9          | PGND     | Ground return of the regulator.                                                                                                                                    |

| 10         | VHI      | Positive supply of the high-side driver.                                                                                                                           |

| 11         | LX       | Inductor drive pin. High current digital output whose average voltage equals the regulator output voltage.                                                         |

| 12         | LX       | Inductor drive pin. High current digital output whose average voltage equals the regulator output voltage.                                                         |

| 13         | VDRV     | Positive supply of the low-side driver and input voltage for the high-side boot strap.                                                                             |

| 14         | FB       | Voltage feedback input. Connected to an external resistor divider between VOUT and GND. A 125nA pull-up curren forces VOUT to VS in the event that FB is floating. |

| 15         | VREF     | Bandgap reference bypass capacitor. Typically 0.1µF to GND.                                                                                                        |

| 16         | PGND     | Ground return of the regulator.                                                                                                                                    |

EL7551C - Preliminary

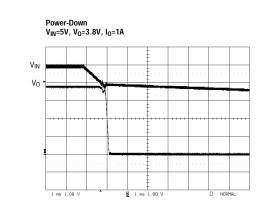

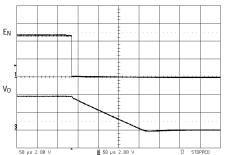

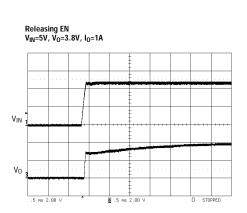

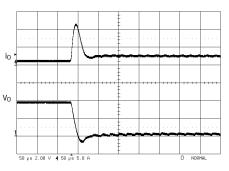

**EL7551C - Preliminary** EL7551C - Preliminary Monolithic 1 Amp DC:DC Step-down Regulator **Typical Performance Curves** Input Current vs Temperature (Enable connected to GND) **Oscillator Frequency vs Temperature** 390 0.96 V<sub>IN</sub>=5.5V 0.94 385 Oscillator Frequency (kHz) 0.92 Input Current (mA) 380 V<sub>IN</sub>=5V V<sub>IN</sub>=4.5V 0.9 0.88 375 0.86 370 0.84 365 0.82 0.8 -40 360 -40 0 40 80 120 10 60 110 160 Temperature (°C) Temperature (°C) Switching Waveforms  $V_{IN}$ =5V,  $V_0$ =3.8V,  $I_0$ =1A Switching Frequency vs Cosc 1400  $\Delta V_{\mathsf{I}}$ 1200  $V_{\text{LX}}$ 1000 Fs (kHz) 800  $\Delta V_{0}$ 600 400 ίL 200 0 2 1 µs 5.0 V 🛿 1 µs 20.0mV 4 1 µs 0.50 A 🗆 STO 1 µs 0 200 400 600 800 1000 C<sub>OSC</sub> (pF) Transient Response V<sub>IN</sub>=5V, V<sub>O</sub>=3.8V, I<sub>O</sub>=0A-1A Power-Up V<sub>IN</sub>=5V, V<sub>O</sub>=3.8V, I<sub>O</sub>=1A VIN i<sub>0</sub>  $\Delta V_{0}$  $V_{\rm O}$ 1.00 A D AUTI 1.00.0 **4** 1 ms 1 ms 1 88 V R I ma

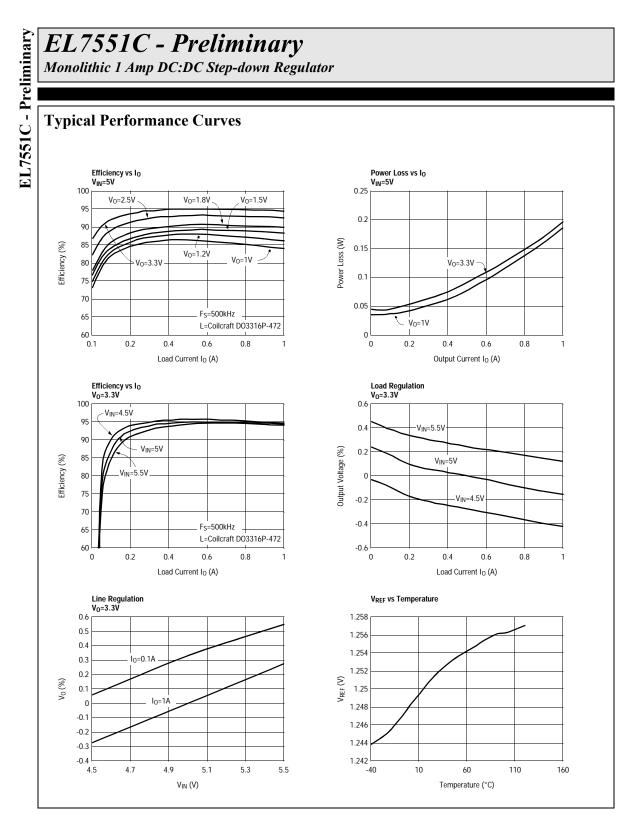

## **Typical Performance Curves**

Short-Circuit Protection V<sub>IN</sub>=5V

**Applications Information**

#### **Circuit Description**

#### General

The EL7551C is a fixed frequency, current mode controlled DC:DC converter with integrated N-channel power MOSFETs and a high precision reference. The device incorporates all the active circuitry required to implement a cost effective, user-programmable 1A synchronous step-down regulator suitable for use in DSP core power supplies.

#### **Theory of Operation**

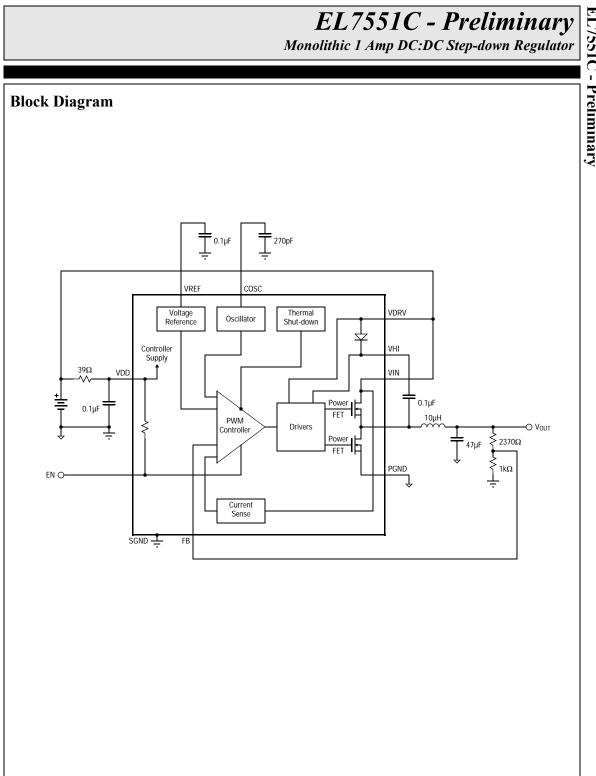

The EL7551C is composed of 5 major blocks:

- 1. PWM Controller

- 2. NMOS Power FETs and Drive Circuitry

- 3. Bandgap Reference

- 4. Oscillator

- 5. Thermal Shut-down

#### **PWM Controller**

The EL7551C regulates output voltage through the use of current-mode controlled pulse width modulation. The three main elements in a PWM controller are the feedback loop and reference, a pulse width modulator whose duty cycle is controlled by the feedback error signal, and a filter which averages the logic level modulator output. In a step-down (buck) converter, the feedback loop forces the time-averaged output of the modulator to equal the desired output voltage. Unlike pure voltagemode control systems, current-mode control utilizes dual feedback loops to provide both output voltage and inductor current information to the controller. The voltage loop minimizes DC and transient errors in the output voltage by adjusting the PWM duty-cycle in response to changes in line or load conditions. Since the output voltage is equal to the time-averaged of the modulator output, the relatively large LC time constant found in power supply applications generally results in low bandwidth and poor transient response. By directly monitoring changes in inductor current via a series sense resistor the controller's response time is not entirely limited by the output LC filter and can react more quickly to changes in line and load conditions. This feed-forward characteristic also simplifies AC loop compensation since it adds a zero to the overall loop response. Through proper selection of the current-feedback to voltage-feedback ratio the overall loop response will approach a onepole system. The resulting system offers several advantages over traditional voltage control systems, including simpler loop compensation, pulse by pulse current limiting, rapid response to line variation and good load step response.

The heart of the controller is an input direct summing comparator which sum voltage feedback, current feedback, slope compensation ramp and power tracking signals together. Slope compensation is required to prevent system instability that occurs in current-mode topologies operating at duty-cycles greater than 50% and is also used to define the open-loop gain of the overall system. The slope compensation is fixed internally and optimized for 500mA inductor ripple current. The power tracking will not contribute any input to the comparator steady-state operation. Current feedback is measured by the patented sensing scheme that senses the inductor current flowing through the high-side switch whenever it is conducting. At the beginning of each oscillator period the high-side NMOS switch is turned on. The comparator inputs are gated off for a minimum period of time of about 150ns (LEB) after the high-side switch is turned on to allow the system to settle. The Leading Edge Blanking (LEB) period prevents the detection of erroneous voltages at the comparator inputs due to switching noise. If the inductor current exceeds the maximum current limit (ILMAX) a secondary overcurrent comparator will terminate the high-side switch on time. If ILMAX has not been reached, the feedback voltage FB derived from the regulator output voltage VOUT is then compared to the internal feedback reference voltage. The resultant error voltage is summed with the current feedback and slope compensation ramp. The high-side switch remains on until all four comparator inputs have summed to zero, at which time the high-side switch is turned off and the low-side switch is turned on. However, the maximum on-duty ratio of the high-side switch is limited to 95%. In order to eliminate cross-con-

duction of the high-side and low-side switches a 15ns break-before-make delay is incorporated in the switch drive circuitry. The output enable (EN) input allows the regulator output to be disabled by an external logic control signal.

#### **Output Voltage Setting**

In general:

$$V_{OUT} = 0.975 V \times \left(1 + \frac{R_2}{R_1}\right)$$

However, due to the relatively low open loop gain of the system, gain errors will occur as the output voltage and loop-gain is changed. This is shown in the performance curves. A 100nA pull-up current from FB to VDD forces VOUT to GND in the event that FB is floating.

#### NMOS Power FETs and Drive Circuitry

The EL7551C integrates low on-resistance ( $60m\Omega$ ) NMOS FETs to achieve high efficiency at 1A. In order to use an NMOS switch for the high-side drive it is necessary to drive the gate voltage above the source voltage (LX). This is accomplished by bootstrapping the VHI pin above the LX voltage with an external capacitor CVHI and internal switch and diode. When the low-side switch is turned on and the LX voltage is close to GND potential, capacitor CVHI is charged through internal switch to VDRV, typically 5V. At the beginning of the next cycle the high-side switch turns on and the LX pins begin to rise from GND to VIN potential. As the LX pin rises the positive plate of capacitor CVHI follows and eventually reaches a value of VDRV+VIN, typically 10V, for VDRV=VIN=5V. This voltage is then level shifted and used to drive the gate of the high-side FET, via the VHI pin. A value of 0.1µF for CVHI is recommended.

#### Reference

A 1.5% temperature compensated bandgap reference is integrated in the EL7551C. The external VREF capacitor acts as the dominant pole of the amplifier and can be increased in size to maximize transient noise rejection. A value of  $0.1\mu$ F is recommended.

#### Oscillator

The system clock is generated by an internal relaxation oscillator with a maximum duty-cycle of approximately 95%. Operating frequency can be adjusted through the COSC pin or can be driven by an external source. If the oscillator is driven by an external source care must be taken in selecting the ramp amplitude. Since CSLOPE value is derived from the COSC ramp, changes to COSC ramp will change the CSLOPE compensation ramp which determine the open-loop gain of the system.

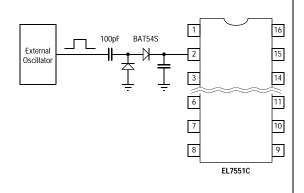

When external synchronization is required, always choose  $C_{OSC}$  such that the free-running frequency is at least 20% lower than that of sync source to accommodate component and temperature variations. Figure 1 shows a typical connection.

#### **Figure 1. Oscillator Synchronization**

#### **Thermal Shut-down**

An internal temperature sensor continuously monitors die temperature. In the event that die temperature exceeds the thermal trip-point, the system is in fault state and will be shut down. The upper and low trip-points are set to 135°C and 115°C respectively.

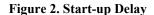

#### Start-up Delay

A capacitor can be added to the EN pin to delay the converter start-up (Figure 2) by utilizing the pull-up current. The delay time is approximately:

$t_d(ms) = 1200 \times C(\mu F)$

#### Layout Considerations

The layout is very important for the converter to function properly. Power Ground ( $\downarrow$ ) and Signal Ground ( $\frac{1}{-}$ ) should be separated to ensure that the high pulse current in the Power Ground never interferes with the sensitive signals connected to Signal Ground. They should only be connected at one point (normally at the negative side of either the input or output capacitor.)

The trace connected to pin 14 (FB) is the most sensitive trace. It needs to be as short as possible and in a "quiet" place, preferably between PGND or SGND traces.

In addition, the bypass capacitor connected to the VDD pin needs to be as close to the pin as possible.

The heat of the chip is mainly dissipated through the PGND pins. Maximizing the copper area around these pins is preferable. In addition, a solid ground plane is always helpful for the EMI performance.

The demo board is a good example of layout based on these principles. Please refer to the EL7551C Application Brief for the layout.

#### **General Disclaimer**

Specifications contained in this data sheet are in effect as of the publication date shown. Elantec, Inc. reserves the right to make changes in the circuitry or specifications contained herein at any time without notice. Elantec, Inc. assumes no responsibility for the use of any circuits described herein and makes no representations that they are free from patent infringement.

Elantec Semiconductor, Inc. 675 Trade Zone Blvd. Milpitas, CA 95035 Telephone: (408) 945-1323 (888) ELANTEC Fax: (408) 945-9305

European Office: +44-118-977-6020 Japan Technical Center: +81-45-682-5820

#### WARNING - Life Support Policy

Elantec, Inc. products are not authorized for and should not be used within Life Support Systems without the specific written consent of Elantec, Inc. Life Support systems are equipment intended to support or sustain life and whose failure to perform when properly used in accordance with instructions provided can be reasonably expected to result in significant personal injury or death. Users contemplating application of Elantec, Inc. Products in Life Support Systems are requested to contact Elantec, Inc. factory headquarters to establish suitable terms & conditions for these applications. Elantec, Inc.'s warranty is limited to replacement of defective components and does not cover injury to persons or property or other consequential damages.

**October 3, 2001**