# LC7574NE, 7574NW

## 1/2 Duty VFD Driver for Frequency Display

CMOS LSI

### **Overview**

The LC7574NE and LC7574NW are 1/2 duty VFD drivers that can be used for electronic tuning frequency display and other applications under the control of a controller. These products can directly drive VFDs with up to 74 segments.

### **Features**

- 74 segment outputs

- Noise reduction circuits are built into the output drivers.

- Serial data input supports CCB\* format communications with the system controller.

- Switching between digital and analog dimmers under serial data control

- High generality since display data is displayed without the intervention of a decoder

- All segments can be turned off with the  $\overline{BLK}$  pin

- CCB is a trademark of SANYO ELECTRIC CO., LTD.

- CCB is SANYO's original bus format and all the bus addresses are controlled by SANYO.

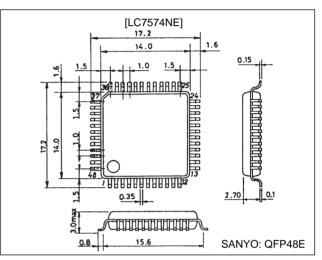

### **Package Dimensions**

unit: mm

3156-QFP48E

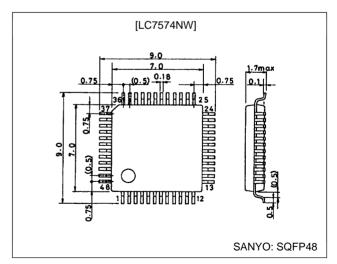

unit: mm

#### 3163A-SQFP48

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

## **Specifications**

## Absolute Maximum Ratings at $Ta=25^{\circ}C,\,V_{SS}$ = 0 V

| Parameter                   | Symbol              | Conditions           | Ratings                       | Unit |

|-----------------------------|---------------------|----------------------|-------------------------------|------|

|                             | V <sub>DD</sub> max | V <sub>DD</sub>      | -0.3 to +6.5                  | V    |

| Maximum supply voltage      | V <sub>FL</sub> max | V <sub>FL</sub>      | -0.3 to +21.0                 | V    |

| Input voltage               | V <sub>IN</sub> 1   | DI, CL, CE, BLK, DIM | -0.3 to +6.5                  | V    |

| Input voltage               | V <sub>IN</sub> 2   | OSC                  | –0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output voltage              | V <sub>OUT</sub> 1  | S1 to S37, G1, G2    | –0.3 to V <sub>FL</sub> + 0.3 | V    |

| Output voltage              | V <sub>OUT</sub> 2  | OSC                  | –0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output current              | I <sub>OUT</sub> 1  | S1 to S37            | 5                             | mA   |

| Output current              | I <sub>OUT</sub> 2  | G1, G2               | 67                            | mA   |

| Allowable power dissipation | Ddmay               | Ta = 85°C (LC7574NE) | 250                           | mW   |

| Allowable power dissipation | Pd max              | Ta = 85°C (LC7574NW) | 150                           | mW   |

| Operating temperature       | Topr                |                      | -40 to +85                    | °C   |

| Storage temperature         | Tstg                |                      | -50 to +125                   | °C   |

## Allowable Operating Ranges at Ta=-40 to $+85^{\circ}C,\,V_{DD}$ = 4.5 to 5.5 V, $V_{SS}$ = 0 V

| Parameter                        | Symbol           | Conditions        | min                 | typ | max                 | Unit |

|----------------------------------|------------------|-------------------|---------------------|-----|---------------------|------|

| Supply voltage                   | V <sub>DD</sub>  | V <sub>DD</sub>   | 4.5                 | 5.0 | 5.5                 | V    |

| Supply voltage                   | V <sub>FL</sub>  | V <sub>FL</sub>   | 8                   | 12  | 18                  | V    |

| Input high level voltage         | VIH              | DI, CL, CE, BLK   | 0.8 V <sub>DD</sub> |     | 5.5                 | V    |

| Input low level voltage          | V <sub>IL</sub>  | DI, CL, CE, BLK   | 0                   |     | 0.2 V <sub>DD</sub> | V    |

| Guaranteed oscillator range      | fosc             | OSC               | 0.4                 | 1.6 | 3.0                 | MHz  |

| Recommended external resistance  | R <sub>OSC</sub> | OSC               |                     | 12  |                     | kΩ   |

| Recommended external capacitance | C <sub>OSC</sub> | OSC               |                     | 50  |                     | pF   |

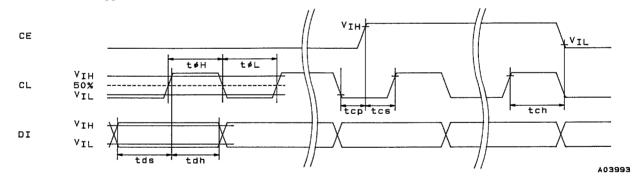

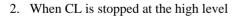

| Low level clock pulse width      | t <sub>øL</sub>  | CL: Figure 1      | 0.5                 |     |                     | μs   |

| High level clock pulse width     | t <sub>øH</sub>  | CL: Figure 1      | 0.5                 |     |                     | μs   |

| Data setup time                  | t <sub>ds</sub>  | DI, CL: Figure 1  | 0.5                 |     |                     | μs   |

| Data hold time                   | t <sub>dh</sub>  | DI, CL: Figure 1  | 0.5                 |     |                     | μs   |

| CE wait time                     | t <sub>cp</sub>  | CE, CL: Figure 1  | 0.5                 |     |                     | μs   |

| CE setup time                    | t <sub>cs</sub>  | CE, CL: Figure 1  | 0.5                 |     |                     | μs   |

| CE hold time                     | t <sub>ch</sub>  | CE, CL: Figure 1  | 0.5                 |     |                     | μs   |

| BLK switching time               | t <sub>c</sub>   | BLK, CE: Figure 3 | 10                  |     |                     | μs   |

| Input voltage range              | V <sub>IN</sub>  | DIM               | 0                   |     | +5.5                | V    |

### **Electrical Characteristics** in the Allowable Operating Ranges

| Parameter                     | Symbol            | Conditions                                                        | min                   | typ  | max  | Unit |

|-------------------------------|-------------------|-------------------------------------------------------------------|-----------------------|------|------|------|

| Input high level current      | I <sub>IH</sub>   | DI, CL, CE, $\overline{\text{BLK}}$ , DIM: V <sub>I</sub> = 5.5 V |                       |      | 5    | μA   |

| Input low level current       | IL                | DI, CL, CE, $\overline{\text{BLK}}$ , DIM: V <sub>I</sub> = 0 V   | -5                    |      |      | μA   |

|                               | V <sub>OH</sub> 1 | S1 to S37: I <sub>O</sub> = 2 mA                                  | V <sub>FL</sub> – 0.6 |      |      | V    |

| Output high level voltage     | V <sub>OH</sub> 2 | G1, G2: I <sub>O</sub> = 25 mA                                    | V <sub>FL</sub> - 0.6 |      |      | V    |

|                               | V <sub>OH</sub> 3 | G1, G2: I <sub>O</sub> = 50 mA                                    | V <sub>FL</sub> – 1.3 |      |      | V    |

| Output low level voltage      | V <sub>OL</sub>   | S1 to S37, G1, G2: I <sub>O</sub> = -5 μA, Ta = 25°C              | 0.125                 | 0.25 | 0.5  | V    |

| Oscillator frequency          | fosc              | $R_{OSC} = 12 \text{ k}\Omega, C_{OSC} = 50 \text{ pF}$           |                       | 1.6  |      | MHz  |

| Hysteresis voltage            | V <sub>H</sub>    | DI, CL, CE, BLK                                                   | 0.5                   |      |      | V    |

| A/D converter linearity error | Err               | DIM                                                               | -1/2                  |      | +1/2 | LSB  |

| Current drain                 | I <sub>DD</sub>   | Outputs open: f <sub>OSC</sub> = 1.6 MHz                          |                       |      | 10   | mA   |

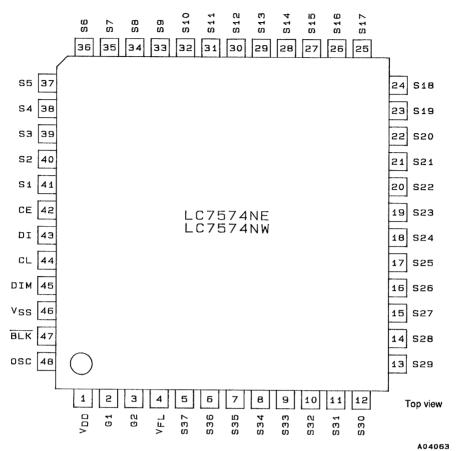

#### **Pin Assignment**

1. When CL is stopped at the low level

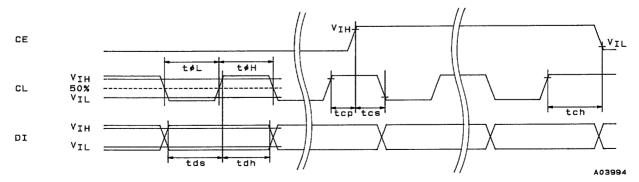

#### **Block Diagram**

#### **Pin Functions**

| Pin No. | Pin             | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  | Handling<br>when unused |                                                                                     |                   |

|---------|-----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------|-------------------|

| 4       | V <sub>FL</sub> | _   | Driver block power supply. A voltage of between 8.0                                                                                                                                                                                                                                                                                                                                                                                                          | Driver block power supply. A voltage of between 8.0 and 18.0 V must be supplied. |                         |                                                                                     |                   |

| 1       | V <sub>DD</sub> | _   | Logic block power supply. A voltage of between 4.5                                                                                                                                                                                                                                                                                                                                                                                                           | and 5.5 V must be supplied.                                                      | —                       |                                                                                     |                   |

| 46      | V <sub>SS</sub> | —   | Ground. Must be connected to the system ground.                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  | —                       |                                                                                     |                   |

| 48      | OSC             | I/O | Dscillator connection. An oscillator circuit is formed by connecting an external resistor and capacitor o this pin                                                                                                                                                                                                                                                                                                                                           |                                                                                  | V <sub>DD</sub>         |                                                                                     |                   |

| 47      | BLK             | I   | <u>Disp</u> lay off control input<br>$\underline{BLK}$ = low (V <sub>SS</sub> ): Display off (G1 and G2 = low)<br>BLK = high (V <sub>DD</sub> ): Display on<br>Note that serial data can be transferred while the display is turned off.                                                                                                                                                                                                                     |                                                                                  | GND                     |                                                                                     |                   |

| 44      | CL              | I   | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Ι                                                                                |                         | CL: synchronization clock                                                           |                   |

| 43      | DI              |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  | I                       | Serial data transfer inputs. These pins must be connected to the system controller. | DI: transfer data |

| 42      | CE              | Ī   |                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CE: chip enable                                                                  |                         |                                                                                     |                   |

| 45      | DIM             | I   | When the analog dimmer is selected, the analog voltage applied to this pin controls the duty of the G1 and G2 digit output pins. Since a 6-bit A/D converter is applied to this analog voltage and that result is input to a decoder that provides a built-in dimmer curve, the relationship between the analog voltage and the duty can be specified as a mask program. Note that $63/96 \cdot V_{DD}$ is the full-scale level for the 6-bit A/D converter. |                                                                                  | GND                     |                                                                                     |                   |

| 2, 3    | G1, G2          | 0   | Digit outputs. The frame frequency f <sub>O</sub> is (f <sub>OSC</sub> /4096) Hz                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  | Open                    |                                                                                     |                   |

| 41 to 5 | S1 to S37       | 0   | Segment outputs for displaying the display data transferred by serial data input.                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  | Open                    |                                                                                     |                   |

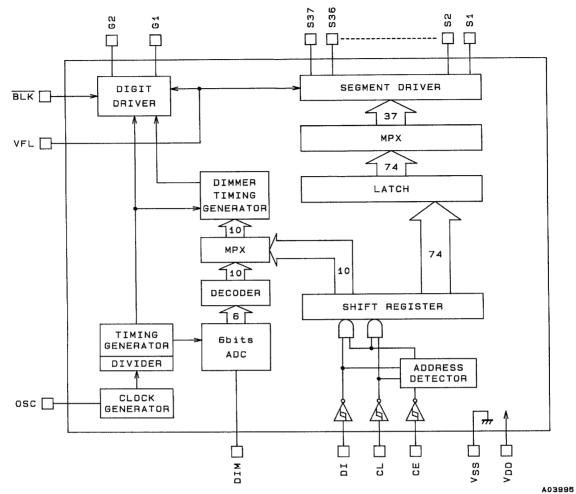

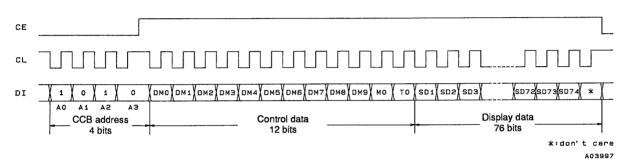

#### Serial Data Transfer Format

1. When CL is stopped at the low level

#### 2. When CL is stopped at the high level

| CCB address: | Transfer $1010_{\rm B}$ , as shown in Figure 2.                                                        |

|--------------|--------------------------------------------------------------------------------------------------------|

| M0:          | Digital/analog dimmer selection data                                                                   |

|              | M0 = 0Digital dimmer                                                                                   |

|              | M0 = 1Analog dimmer                                                                                    |

| DM0 to DM9   | : Dimmer data                                                                                          |

|              | This data controls the duty of the G1 and G2 digit output pins when the digital dimmer is selected.    |

|              | This data consists of 10 bits, of which DM0 is the LSB. Note that display intensity can be adjusted by |

|              | controlling the duty of the G1 and G2 digit output pins. (The DM0 to DM9 dimmer data is ignored        |

|              | when the analog dimmer is selected.)                                                                   |

| SD1 to SD74  | : Display data                                                                                         |

|              | SD1 to SD37Display data for the G1 digit output pin                                                    |

|              | SD38 to SD74Display data for the G2 digit output pin                                                   |

|              | SDn (n = 1 to 74) = 1Display on                                                                        |

|              | SDn (n = 1 to 74) = 0Display off                                                                       |

| T0:          | Test data                                                                                              |

|              | The T0 bit must be set to 0.                                                                           |

|              |                                                                                                        |

#### **Serial Data Format**

### Correspondence between Display Data (SD1 to SD74) and Segment Output Pins

| Segment output pin | G1   | G2   |

|--------------------|------|------|

| S1                 | SD1  | SD38 |

| \$2                | SD2  | SD39 |

| \$3                | SD3  | SD40 |

| S4                 | SD4  | SD41 |

| S5                 | SD5  | SD42 |

| S6                 | SD6  | SD43 |

| S7                 | SD7  | SD44 |

| S8                 | SD8  | SD45 |

| S9                 | SD9  | SD46 |

| S10                | SD10 | SD47 |

| S11                | SD11 | SD48 |

| S12                | SD12 | SD49 |

| S13                | SD13 | SD50 |

| S14                | SD14 | SD51 |

| S15                | SD15 | SD52 |

| S16                | SD16 | SD53 |

| S17                | SD17 | SD54 |

| S18                | SD18 | SD55 |

| S19                | SD19 | SD56 |

| Segment output pin | G1   | G2   |

|--------------------|------|------|

| S20                | SD20 | SD57 |

| S21                | SD21 | SD58 |

| S22                | SD22 | SD59 |

| S23                | SD23 | SD60 |

| S24                | SD24 | SD61 |

| S25                | SD25 | SD62 |

| S26                | SD26 | SD63 |

| S27                | SD27 | SD64 |

| S28                | SD28 | SD65 |

| S29                | SD29 | SD66 |

| S30                | SD30 | SD67 |

| S31                | SD31 | SD68 |

| S32                | SD32 | SD69 |

| S33                | SD33 | SD70 |

| S34                | SD34 | SD71 |

| S35                | SD35 | SD72 |

| S36                | SD36 | SD73 |

| S37                | SD37 | SD74 |

Example: Segment output pin S11 is controlled as follows:

| Display data |      | Segment output pin S11 state                                                |  |

|--------------|------|-----------------------------------------------------------------------------|--|

| SD11         | SD48 | Segment output pin STT state                                                |  |

| 0            | 0    | The segments corresponding to both the G1 and G2 digit output pins are off. |  |

| 0            | 1    | The segment corresponding to the G2 digit output pin is on.                 |  |

| 1            | 0    | The segment corresponding to the G1 digit output pin is on.                 |  |

| 1            | 1    | The segments corresponding to both the G1 and G2 digit output pins are on.  |  |

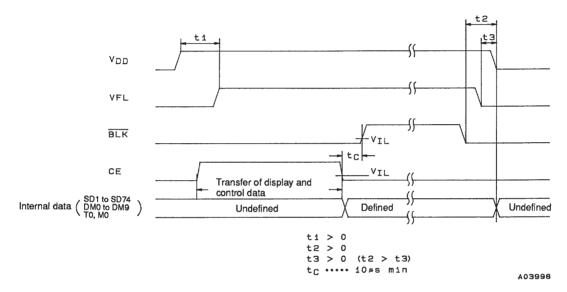

#### **BLK** and the Display Control

Since the LSI internal data (SD1 to SD74 and the control data) is undefined when power is first applied, the display is off (G1 and G2 = low) by setting the  $\overline{BLK}$  pin low at the same time as power is applied. Then, meaningless display at power on can be prevented by transferring all 92 bits of serial data from the controller while the display is off and setting  $\overline{BLK}$  pin high after the transfer completes. (See Figure 3.)

#### **Power Supply Sequence**

The following sequences must be observed when power is turned on and off. (See Figure 3)

- Power on: Logic block power supply (V<sub>DD</sub>) on  $\rightarrow$  Driver block power supply (V<sub>FL</sub>) on

- Power off: Driver block power supply (V<sub>DD</sub>) off  $\rightarrow$  Logic block power supply (V<sub>DD</sub>) off

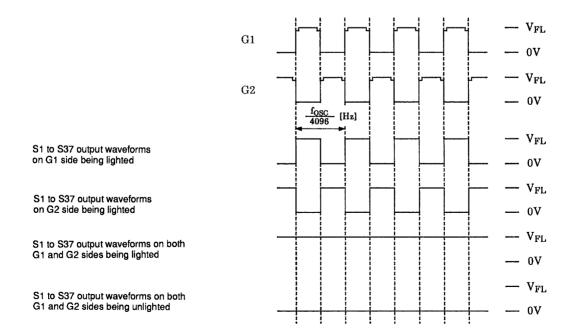

Output Waveforms (S1 to S37)

#### **Relation between Segment and Digit Outputs**

#### Descriptions

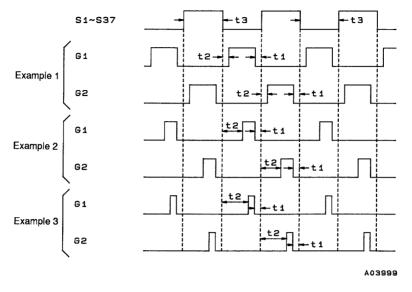

- 1. Consider the examples shown in Figure 4, where data is set up so that the segment outputs S1 to S37 output a low level on the G1 digit output timing and a high level on the G2 digit output timing. (Here, the G2 side being lighted)

- 2. The digit output G1 and G2 waveforms in Example 1 are output when the 10 bits of dimmer data (DM0 to DM9) are set to  $3FE_{\text{H}}$ . The relation between t1 and the oscillator frequency  $f_{\text{OSC}}$  is:

$t1 = 2/f_{OSC}$ .

For example, if  $f_{OSC} = 1.6$  [MHz], then

t1 = 2/1.6 [MHz] = 1.25 [µs].

Note that t1 and t2 are the same period in Example 1.

3. The digit output G1 and G2 waveforms in Example 2 are those when the dimmer data (DM0 to DM9) are set to a smaller value. Although the time t1, which is from the point where digit output falls to segment output changes, does not change, the time t2, which is from the point where segment output changes to the time the digit output rises, becomes longer. When the dimmer data (DM0 to DM9) are set to 0FF<sub>H</sub> and f<sub>OSC</sub> is 1.6 [MHz], then the frame frequency f<sub>O</sub> is:

```

\begin{split} f_{O} &= 1/(t3\times2) \\ &= f_{OSC}/4096 \\ &= 391 \text{ [Hz],} \\ \text{and,} \\ t3 &= 1.28 \text{ [ms].} \end{split}

```

Therefore,

$t2 = \frac{(1.28 \text{ [ms]} - 1.25 \text{ [}\mu\text{s}\text{]} \times 2) \times (3\text{FF}_{\text{H}} - 0\text{FF}_{\text{H}})}{1023} = 0.96 \text{ [ms]}.$

4. When the dimmer data (DM0 to DM9) are set to an even smaller value, the time t2, which is from the point where segment output changes to the time the digit output rises, becomes even longer, as in Example 3. Note that t1 does not change here, either.

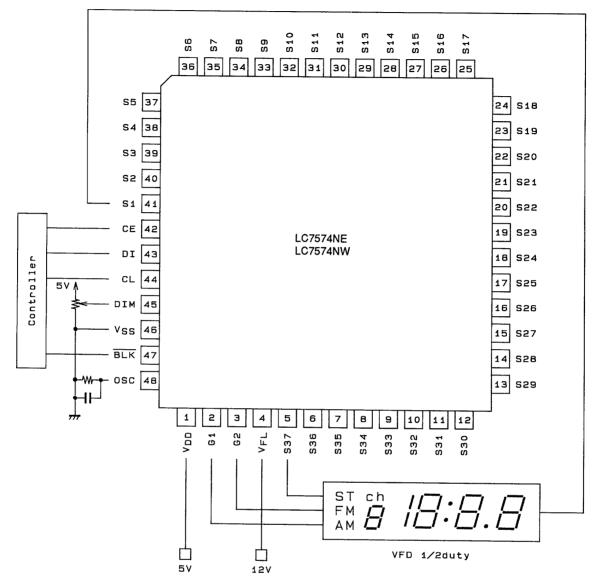

#### **Sample Application Circuit**

#### **Usage Notes**

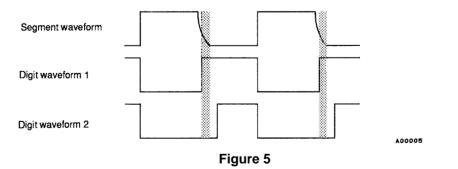

1. Notes on the segment and digit waveforms

The segment waveform is distorted by the VFD panel used and the wiring, and furthermore, in the case of being used with essentially no dimming as in the digit waveform 1, as shown in Figure 5, the VFD panel glow dimly. By carefully considering the segment waveform, it can be seen that this problem can be resolved by applying an adequate amount of dimming, as shown in Digit waveform 2. When  $f_{OSC}$  is 1.6 [MHz], we recommend using 10 bits of dimmer data in the range  $000_{\rm H}$  to  $3E0_{\rm H}$ .

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of October, 1995. Specifications and information herein are subject to change without notice.

No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.