# Pre-Amplifier and Servo IC for Quadruple-Speed CD-ROM

# HITACHI

ADE-207-183(Z)

1st. Edition October 1995

### Description

The typical values of built-in capacitances in this IC are reduced 10% compared with those in IC HA12188F. The values of Electrical Characteristics of this IC are same as those of IC HA12188F.

### Functions

- RF amplifier

- Focus error amplifier

- Tracking error amplifier

- FOK detector

- Mirror detector

- Defect detector

- APC amplifier

- Focus, tracking, and sled servo control

- Inner/outer direction detector

#### Features

- Built-in variable resistors for adjusting tracking error EF balance, tracking gain, and focus gain

- Single power supply

- Supports double and quadruple speeds

- Few external components

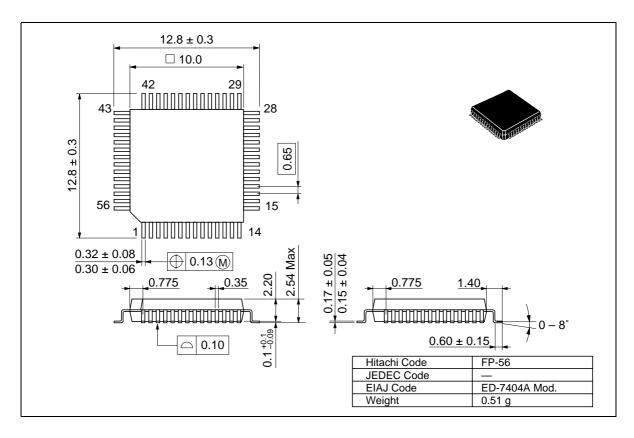

- FP-56 package

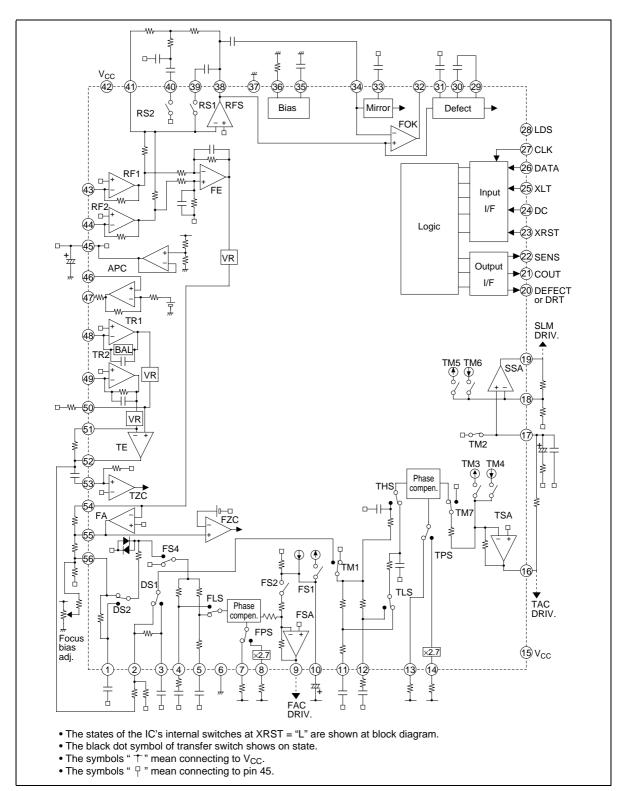

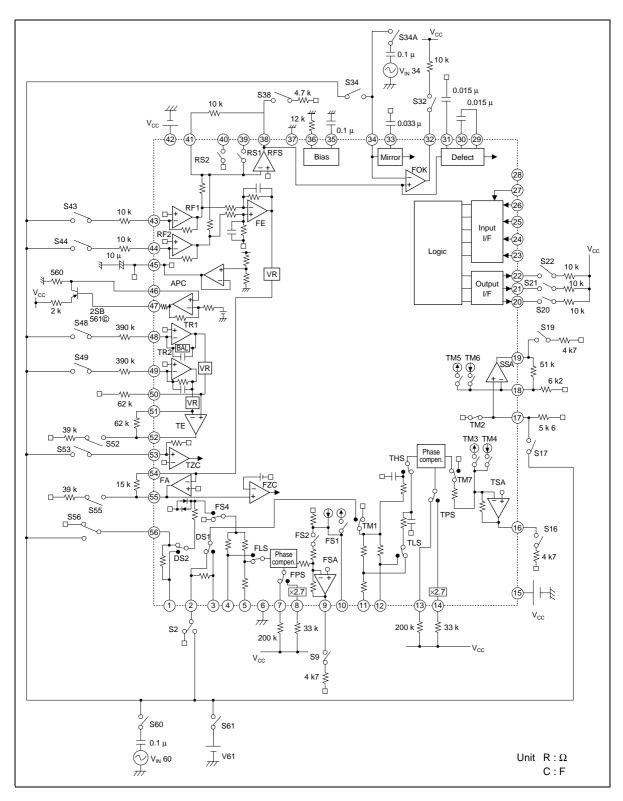

### **Block Diagram**

| Pin No. | Symbol | Equivalent Circuit | Function                                                                           |

|---------|--------|--------------------|------------------------------------------------------------------------------------|

| 1       | FH     | 470 k              | Focus error hold signal output                                                     |

| 3       | TH     | -                  | Tracking error hold signal output                                                  |

| 2       | TSI    | 0                  | Tracking servo input                                                               |

| 56      | FSI    | -                  | Focus servo input                                                                  |

| 4       | FLS    | 90 k               | Focus-servo low-frequency filter<br>resistor & capacitor connection<br>(FLS on)    |

| 5       | FLS    | 30 k<br>           | Focus-servo low-frequency filter capacitor connection (FLS off)                    |

| 6       | SGND   |                    | Servo ground                                                                       |

| 7       | FPS    |                    | Resistor connection for programming<br>focus-servo phase compensation<br>(FPS off) |

| 8       | FPS    | -                  | Resistor connection for programming focus-servo phase compensation (FPS on)        |

| 9       | FSA    |                    | Focus servo output                                                                 |

| 10      | FS1    | 20 k               | FS1 voltage output                                                                 |

| 11      | TLS    | 33 k<br>           | Tracking servo low-frequency filter capacitor connection (TLS off)                 |

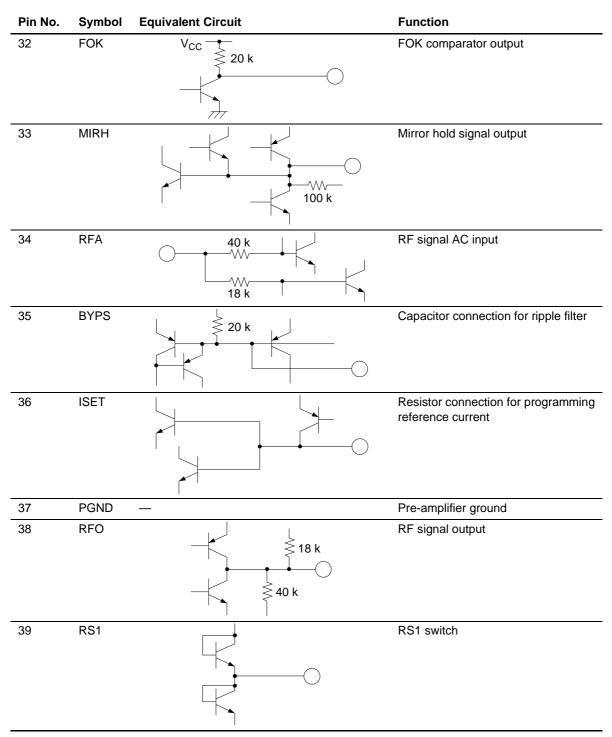

### Pin Descriptions and Equivalent Circuits

| Pin No. | Symbol                      | Equivalent Circuit | Function                                                                              |

|---------|-----------------------------|--------------------|---------------------------------------------------------------------------------------|

| 12      | TLS                         | 100 k              | Tracking servo low-frequency filter<br>resistor & capacitor connection<br>(TLS on)    |

| 13      | TPS                         |                    | Resistor connection for programming<br>tracking servo phase compensation<br>(TPS off) |

| 14      | TPS                         | -                  | Resistor connection for programming<br>tracking servo phase compensation<br>(TPS on)  |

| 15      | $\mathrm{SV}_{\mathrm{cc}}$ | _                  | Servo power supply                                                                    |

| 16      | TSA                         |                    | Tracking servo output                                                                 |

| 17      | TM2                         |                    | Sled servo input                                                                      |

| 18      | SSM                         |                    | SSA amplifier inverting input                                                         |

| 19      | SSA                         |                    | Sled servo output                                                                     |

### Pin Descriptions and Equivalent Circuits (cont)

#### Pin No. Symbol **Equivalent Circuit** Function V<sub>CC</sub> 20 DRT Defect signal output or inner/outer direction signal output 10 k 21 COUT COUT output SENS output 22 SENS 23 XRST Reset input DC DC input 24 25 XLT XLT input 26 DATA Data input 27 CLK Clock input LDS Laser switch input 28 50 k Ŵ 50 k DFIN 29 Defect comparator input ≶ 43 k 30 DFO Defect envelope signal output 31 DFH Defect hold signal output

### Pin Descriptions and Equivalent Circuits (cont)

### Pin Descriptions and Equivalent Circuits (cont)

| 40       RS2       RS2 switch         41       RFM       RFS amplifier inverting input         41       RFM       RFS amplifier inverting input         42 $PV_{\infty}$ -       Pre-amplifier power supply         43       RF1       Image: Constraint of the system o                                                                                                                                                                                                                                                    | Pin No. | Symbol         | Equivalent Circuit  | Function                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------|---------------------|-------------------------------|

| $42  PV_{cc}  - \qquad Pre-amplifier power supply$ $43  RF1 \qquad \qquad$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40      | RS2            |                     | RS2 switch                    |

| 43       RF1       RF1 amplifier input         44       RF2       RF2 amplifier input         44       RF2       RF2 amplifier input         45 $V_c$ Voltage reference output         46       MD       APC amplifier input         47       LD       APC amplifier output         48       TR1       Model of the state of                                                                                                                                                                                                                                                                                                                                        | 41      | RFM            |                     | RFS amplifier inverting input |

| 43       RF1       RF1 amplifier input         44       RF2       RF2 amplifier input         44       RF2       RF2 amplifier input         45 $V_c$ Voltage reference output         46       MD       APC amplifier input         47       LD       APC amplifier output         48       TR1       Model of the state of                                                                                                                                                                                                                                                                                                                                        | 42      | $PV_{cc}$      |                     | Pre-amplifier power supply    |

| 44       RF2       RF2 amplifier input         45 $V_c$ Voltage reference output         46       MD       APC amplifier input         47       LD $1 k$ 48       TR1 $80 k \leq 3.6 p$ TR1 amplifier input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 43      |                |                     | RF1 amplifier input           |

| 46 MD<br>47 LD<br>48 TR1<br>48 TR1<br>20  k<br>10  k                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 44      | RF2            | -                   | RF2 amplifier input           |

| 47 LD<br>47 LD<br>48 TR1<br>1 k<br>1 k<br>2 k<br>2 k<br>2 k<br>1 k<br>1 k<br>1 k<br>1 k<br>2 k<br>1 k<br>2 k<br>1 k<br>2 k<br>1 k<br>2 k<br>1 k<br>2 k<br>1 k<br>2 k<br>1 k<br>2 k | 45      | V <sub>c</sub> |                     | Voltage reference output      |

| 47 LD<br>150  k $1  k$ $1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 46      | MD             |                     | APC amplifier input           |

| 48 TR1<br>$80 k \leq 3.6 p$<br>$20 k \leq 16 k \leq 32 k$<br>TR1 amplifier input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47      | LD             |                     | APC amplifier output          |

| 49 TR2 TR2 amplifier input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 48      | TR1            | 80 k ≥ 3.6 p → 32 k | TR1 amplifier input           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49      | TR2            | -                   | TR2 amplifier input           |

### Pin Descriptions and Equivalent Circuits (cont)

| Pin No. | Symbol | Equivalent Circuit | Function                         |

|---------|--------|--------------------|----------------------------------|

| 50      | TEP    | 22.6 k             | TE amplifier non-inverting input |

| 51      | TEM    | -                  | TE amplifier inverting input     |

| 52      | TEO    |                    | TE amplifier output              |

| 53      | TZC    |                    | TZC comparator input             |

| 54      | FAM    | ○ 5.5 k            | FA amplifier inverting input     |

| 55      | FAO    |                    | FA amplifier output              |

### Pin Descriptions and Equivalent Circuits (cont)

### Operation

#### 1. Microprocessor Control

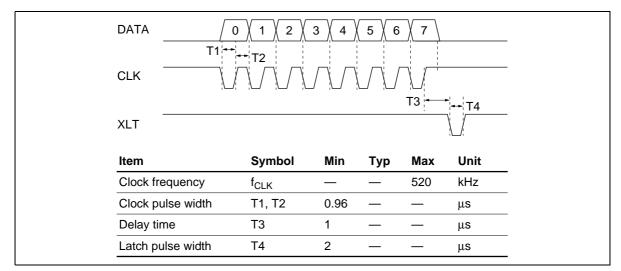

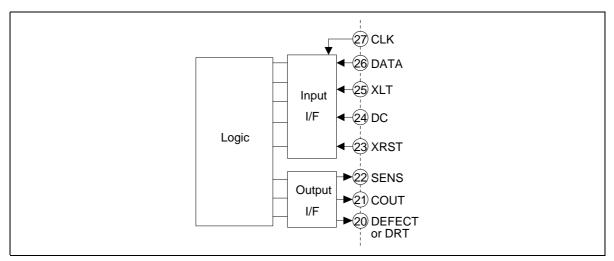

The IC's internal switches can be operated by sending control data from a microprocessor. The signal timing is shown in figure 1, and the control commands are listed in table 1.

Figure 1 Timing Diagram for Microprocessor Control

Signals from the microprocessor are input at pins 23 to 27. A low input at the XRST pin resets the IC. Normally this pin should be kept high. (See figure 2.)

Figure 2 Microprocessor Interface

| Table 1Microprocessor ( | <b>Control Commands</b> |

|-------------------------|-------------------------|

|-------------------------|-------------------------|

|                                      |    | DATA <sup>*1</sup> |     |    |                                                                                                                          |                                            |                                               |                                             |      |  |

|--------------------------------------|----|--------------------|-----|----|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------|---------------------------------------------|------|--|

|                                      | D7 | D6                 | D5  | D4 | D3                                                                                                                       | D2                                         | D1                                            | D0                                          | SENS |  |

| Focus mode                           | 0  | 0                  | 0   | 0  | (FS4)                                                                                                                    | OFF                                        |                                               | (FS1)                                       | FZC  |  |

| Tracking mode and FS1<br>DRT setting | 0  | 0                  | 0   | 1  | DRT <sup>*3</sup><br>0: Defect<br>1: Direction                                                                           | 0: Defect (TM7) <sup>4</sup>               |                                               | THS                                         | Н    |  |

| Access control mode                  | 0  | 0                  | 1   | 0  |                                                                                                                          | See t                                      | able 2                                        |                                             | TZC  |  |

|                                      |    |                    |     |    |                                                                                                                          | 4 current *6                               | 6 current *6                                  |                                             |      |  |

| Pulse setting mode                   | 0  | 0                  | 1   | 1  | D3         D2         Cu           0         0         1           1         0         1           1         1         1 | rrent value<br>32μA<br>16μA<br>24μA<br>8μA | D1 D0 Cu<br>0 0<br>1<br>1 0<br>1 1            | irrent value<br>32μΑ<br>16μΑ<br>24μΑ<br>8μΑ | н    |  |

| Speed setting mode                   | 0  | 1                  | 0   | 0  | D3         D2           0         0           0         1                                                                | Mode<br>Normal<br>Double<br>Quadruple      | Focus<br>tracking<br>(FLS)(FPS)<br>(TLS)(TPS) | RF<br>(RS1)(RS2)                            | н    |  |

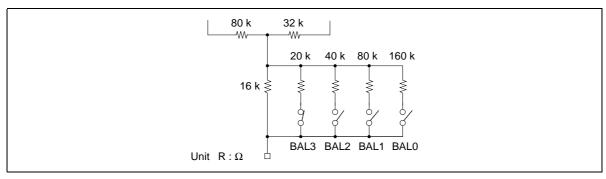

| EF balance adjustment                | 0  | 1                  | 0   | 1  | BAL3                                                                                                                     | BAL2                                       | (BAL1)                                        | BALO                                        | н    |  |

| Tracking gain and focus              | 0  | 1                  | . 1 | 0  | 0 ; Focus<br>gain                                                                                                        | GF2                                        | GF1                                           | GF0                                         | Н    |  |

| gain adjustment                      |    |                    |     |    | 1 ; Tracking<br>gain                                                                                                     | GT2                                        | GT1                                           | GT0                                         | Н    |  |

- Notes: 1. The switch name surrounded by circle means that the switch turns on when the corresponding bit is "1". The switch name with bar surrounded by circle means that the switch turns on when the corresponding bit is "0".

- "DEFECT OFF" means that switches DS1 and DS2 don't turn on when the corresponding bit is "1". Though the "DEFECT OFF" bit is set, the output at pin 20 is defect signal (in defect signal output mode).

- 3. DRT (pin 20) outputs defect signal when the corresponding bit is "0", and outputs direction signal when the corresponding bit is "1".

- 4. TM7 can turn on only when COUT is high.

- 5. The value of two current sources over switch FS1 are 18  $\mu$ A(source) 36  $\mu$ A(sink) when the corresponding bit is "1", and are 9  $\mu$ A(source) 18  $\mu$ A(sink) when the corresponding bit is "0".

- 6. The current values through switches TM3, TM4, TM5 and TM6 can be selected in four steps.

- 7. The speed of Mirror circuit can be selected in three steps. Don't use D3 = "1", D2 = "0" mode.

|      |    | DA | TA |    |     |            | S          | T1         |            |            |            |            | S          | Г2         |            |     |            |     | S   | Т3  |            |     |

|------|----|----|----|----|-----|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|-----|------------|-----|-----|-----|------------|-----|

|      | D3 | D2 | D1 | D0 | TM6 | TM5        | TM4        | тмз        | TM2        | TM1        | TM6        | TM5        | TM4        | тм3        | TM2        | TM1 | TM6        | TM5 | TM4 | TM3 | TM2        | TM1 |

| \$20 | 0  | 0  | 0  | 0  |     |            |            |            | 0          |            |            |            | $\bigcirc$ |            | $\bigcirc$ |     |            |     |     |     |            | 0   |

| \$21 | 0  | 0  | 0  | 1  |     |            |            |            |            |            |            |            | $\bigcirc$ |            |            |     |            |     |     |     |            | 0   |

| \$22 | 0  | 0  | 1  | 0  |     | 0          |            |            | 0          |            |            | 0          | 0          |            | 0          |     | 0          |     |     |     | 0          | 0   |

| \$23 | 0  | 0  | 1  | 1  | 0   |            |            |            | 0          |            | $\bigcirc$ |            | 0          |            | 0          |     | 0          |     |     |     | $\bigcirc$ | 0   |

| \$24 | 0  | 1  | 0  | 0  |     |            |            |            | 0          | $\bigcirc$ |            |            |            | $\bigcirc$ | 0          |     |            |     |     |     |            | 0   |

| \$25 | 0  | 1  | 0  | 1  |     |            |            |            |            | $\bigcirc$ |            |            |            | $\bigcirc$ |            |     |            |     |     |     |            | 0   |

| \$26 | 0  | 1  | 1  | 0  |     | 0          |            |            | $\bigcirc$ | $\bigcirc$ |            | 0          |            | $\bigcirc$ | 0          |     | 0          |     |     |     | 0          | 0   |

| \$27 | 0  | 1  | 1  | 1  | 0   |            |            |            | 0          | $\bigcirc$ | 0          |            |            | $\bigcirc$ | 0          |     | 0          |     |     |     | 0          | 0   |

| \$28 | 1  | 0  | 0  | 0  |     |            |            | $\bigcirc$ | $\bigcirc$ |            |            |            | $\bigcirc$ |            | 0          |     |            |     |     |     |            | 0   |

| \$29 | 1  | 0  | 0  | 1  |     |            |            | 0          |            |            |            |            | 0          |            |            |     |            |     |     |     |            | 0   |

| \$2A | 1  | 0  | 1  | 0  |     | $\bigcirc$ |            | $\bigcirc$ | $\bigcirc$ |            |            | $\bigcirc$ | $\bigcirc$ |            | 0          |     | $\bigcirc$ |     |     |     | $\bigcirc$ | 0   |

| \$2B | 1  | 0  | 1  | 1  | 0   |            |            | 0          | 0          |            | 0          |            | 0          |            | 0          |     | $\bigcirc$ |     |     |     | 0          | 0   |

| \$2C | 1  | 1  | 0  | 0  |     |            | $\bigcirc$ |            | $\bigcirc$ |            |            |            |            | $\bigcirc$ | 0          |     |            |     |     |     |            | 0   |

| \$2D | 1  | 1  | 0  | 1  |     |            | $\bigcirc$ |            |            |            |            |            |            | $\bigcirc$ |            |     |            |     |     |     |            | 0   |

| \$2E | 1  | 1  | 1  | 0  |     | 0          | 0          |            | 0          |            |            | 0          |            | 0          | 0          |     | 0          |     |     |     | 0          | 0   |

| \$2F | 1  | 1  | 1  | 1  | 0   |            | 0          |            | $\bigcirc$ |            | 0          |            |            | 0          | 0          |     | 0          |     |     |     | 0          | 0   |

#### Table 2Access Control Mode

A circle means that the switch is ON.

Note: After the microprocessor sends serial data, TM1 to TM6 can be switched among the states listed under ST1 to ST3 by input at the DC pin. First, if the microprocessor sends serial data when DC is high, TM1 to TM6 are placed in the state listed under ST1. When DC is brought low, the states change to the states listed under ST2. Then if DC is brought high again, the states change to the states listed under ST3.

#### Table 2-A Access Control Mode Appendix

1) Tracking servo

| DATA |    | Tracking servo movement              |

|------|----|--------------------------------------|

| D3   | D2 | at DC = H (ST1)                      |

| 0    | 0  | Servo loop off                       |

| 0    | 1  | Servo loop on                        |

| 1    | 0  | Servo loop off jump to outside track |

| 1    | 1  | Servo loop off jump to inside track  |

#### 2) Sled servo

| DATA |    | Sled servo movement                  |

|------|----|--------------------------------------|

| D1   | D0 | at DC = H (ST1)                      |

| 0    | 0  | Servo loop off                       |

| 0    | 1  | Servo loop on                        |

| 1    | 0  | Servo loop off move to outside track |

| 1    | 1  | Servo loop off move to inside track  |

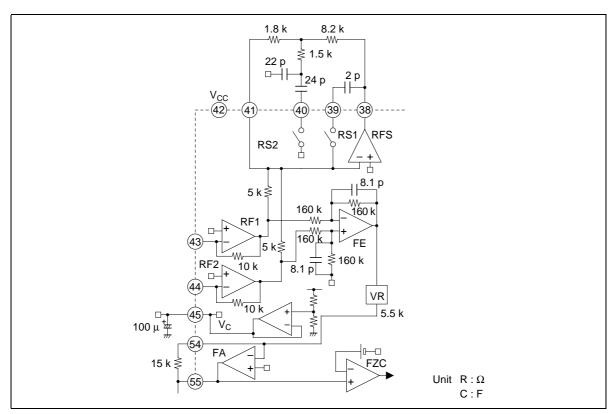

#### 2. RF and Focus Error Pre-Amplifiers

The main beam output signals from the photodiode IC are led in through resistors at pins 43 and 44. The outputs of amplifiers RF1 and RF2 are summed by amplifier RFS to generate the EFM RF signal. (\*1)

External resintances of pins 43 and 44 and amplifier RFS should be set according to the pick-up so that the RF signal at pin 38 is about 1.5  $V_{OP}$  (the difference between the peak level of 11T signal component and the voltage at no signal).

Switches RS1 and RS2 operate together under microprocessor control. For example they are on for normal or double speed, and off for quadruple speed. ON resistance of RS1 is  $1.1k\Omega$  typ and on resistance of RS2 is  $530\Omega$  typ.

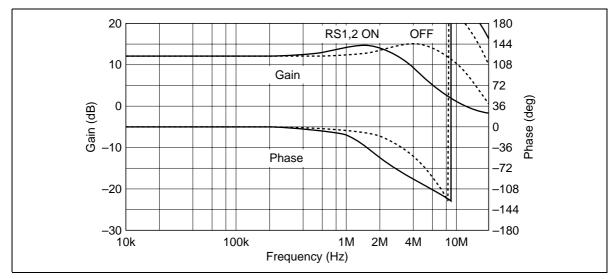

Figure 3-A shows the frequency characteristic at pin 38 in the condition of figure 3.(Input resistances of pins 43 and 44 are  $10k\Omega$ .)

External resistances and capacitances should be fitted according to the pick-up. Stray capacitances of board print patterns have influence on this frequency characteristic. Therefore external resistances and capacitances should be set considering stray capacitances.

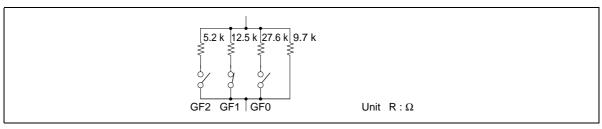

Amplifier FE subtracts the output of amplifier RF2 from the output of amplifier RF1 to generate the focus error signal. The gain is 0dB. The focus error signal is output as the output of amplifier FA at pin 55, with a gain set by variable resistor VR and the external resistance values. With the external resistors in figure 3, the gain of amplifier FA is 8.7dB (initial value after reset).

Variable resistor VR is controlled by 3-bit data. The gain can be varied from -5dB to +7dB with respect to the reset value.

The focus error signal is binarized by comparator FZC, with a Vth equal to  $V_c + 0.38V$ .

A reference voltage of 1/2  $V_{cc}$  is output at pin 45. The IC's internal reference voltage is connected internally.

The feedback resistance of amplifier FA should be set according to the pick-up so that the focus S-curve at pin 55 is about 3V peak-to-peak.

Note: 1 The sink current of amplifier RFS is about 1mA. When load capacitance of pin 38 is big because of wiring with CD DSP LSI etc, please use buffer amplifier. (for example emitter follower transistor)

Figure 3 RF and Focus Error Pre-Amplifiers

Figure 3-A Frequency characteristic example of RF preamplifiers

Figure 4 Focus VR

| Table 5 | Tocus VIX and Gam |    |      |        |  |

|---------|-------------------|----|------|--------|--|

| D2      | D1                | D0 | VR   | Gain   |  |

| 0       | 1                 | 0  | 9.7k | -4.8dB |  |

| 0       | 1                 | 1  | 7.2k | -2.2dB |  |

| 0       | 0                 | 0  | 5.5k | ±0dB   |  |

| 0       | 0                 | 1  | 4.6k | +1.6dB |  |

| 1       | 1                 | 0  | 3.4k | +3.8dB |  |

| 1       | 1                 | 1  | 3k   | +4.9dB |  |

| 1       | 0                 | 0  | 2.7k | +6.0dB |  |

| 1       | 0                 | 1  | 2.4k | +6.8dB |  |

#### Table 3Focus VR and Gain

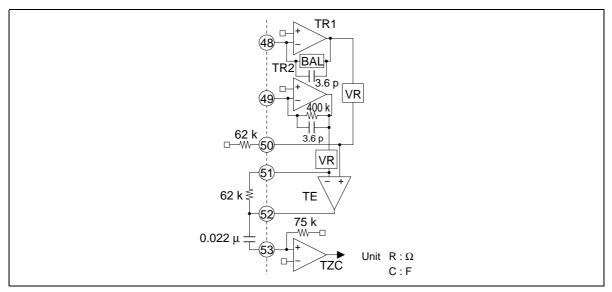

#### 3. Tracking Pre-Amplifiers

The sub-beam outputs from the photodiode IC are led in through resistors at pins 48 and 49.

External resistances of pins 48 and 49 and amplifier TE should be set according to the pick-up so that the traverse signal at pin 52 is about 2  $V_{PP}$ .

After a reset, the initial value of the feedback resistance BAL from amplifier TR1 to pin 48 is  $400k\Omega$ , the same as the feedback resistance from amplifier TR2 to pin 49.

BAL has a variable resistance value that is controlled by 4-bit data. The variable range is from -32% to +28% of the reset value. This resistance can be varied to adjust the EF balance of the tracking error.

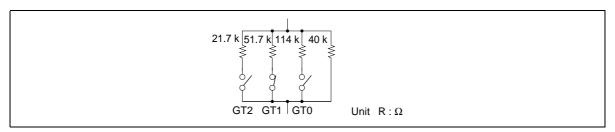

Amplifier TE generates the tracking error signal. Its input signals are received from the preceding stage through variable resistors VR. With the external resistor values in figure 5, after a reset, the initial value of the gain is 8.8dB.

The variable VR resistance is controlled by 3-bit data. The gain can be varied from -5dB to +7dB with respect to the reset value.

The tracking error signal is coupled through a capacitor to input pin 53 and binarized by comparator TZC, with a Vth equal to  $V_{c}$  (\*1)

Note: 1 At normal speed the output of amplifier TE contains much EFM signal components. Therefore the output of amplifier TE had better be led in through LPF for reduction of EFM signal components at pin 53.

Figure 5 Tracking Pre-Amplifiers

| D2 | D1 | D0 | VR    | Gain   |

|----|----|----|-------|--------|

| 0  | 1  | 0  | 40k   | -4.9dB |

| 0  | 1  | 1  | 29.6k | -2.3dB |

| 0  | 0  | 0  | 22.6k | ±0dB   |

| 0  | 0  | 1  | 18.8k | +1.6dB |

| 1  | 1  | 0  | 14.1k | +3.9dB |

| 1  | 1  | 1  | 12.5k | +4.9dB |

| 1  | 0  | 0  | 11.1k | +6.1dB |

| 1  | 0  | 1  | 10.1k | +6.9dB |

| Table 4 | Tracking | VR | Values | and Gain |  |

|---------|----------|----|--------|----------|--|

|---------|----------|----|--------|----------|--|

Table 5BAL Values

| D3 | D2 | D1 | D0 | BAL  | Ratio |

|----|----|----|----|------|-------|

| 1  | 0  | 0  | 0  | 272k | -32%  |

| 1  | 0  | 0  | 1  | 288k | -28%  |

| 1  | 0  | 1  | 0  | 304k | -24%  |

| 1  | 0  | 1  | 1  | 320k | -20%  |

| 1  | 1  | 0  | 0  | 336k | -16%  |

| 1  | 1  | 0  | 1  | 352k | -12%  |

| 1  | 1  | 1  | 0  | 368k | -8%   |

| 1  | 1  | 1  | 1  | 384k | -4%   |

| 0  | 0  | 0  | 0  | 400k | ±0%   |

| 0  | 0  | 0  | 1  | 416k | +4%   |

| 0  | 0  | 1  | 0  | 432k | +8%   |

| 0  | 0  | 1  | 1  | 448k | +12%  |

| 0  | 1  | 0  | 0  | 464k | +16%  |

| 0  | 1  | 0  | 1  | 480k | +20%  |

| 0  | 1  | 1  | 0  | 496k | +24%  |

| 0  | 1  | 1  | 1  | 512k | +28%  |

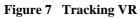

#### 4. FOK Detector

This detector is a comparator that generates the FOK signal. FOK is one of the signals that determines when to activate the focus servo. When the voltage at pin 38 exceeds the voltage at pin 34 by approximately 0.4V, pin 32 goes high.

Figure 8 Mirror, FOK, and Defect Detectors

#### 5. Defect Detector

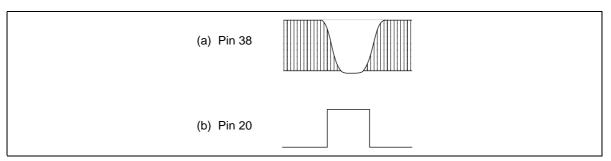

When a scratched disc is played, the EFM RF signal has the shape shown in figure 9 (a). The defect detector detects the drop-out area of this signal. Scratches with dimensions of about 100 $\mu$ m or greater are detected.

Figure 9 Defect Detector Waveforms

#### 6. Mirror Detector

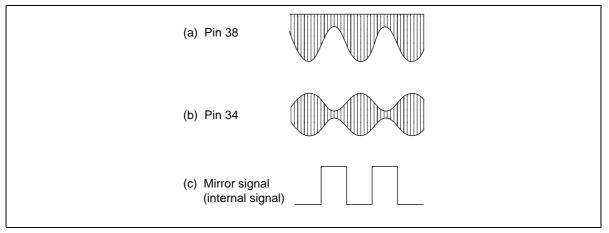

As the pick-up travels across tracks, the EFM RF signal varies as in figure 10 (a). At pin 34, the signal varies as in figure 10 (b). The mirror detector detects the mirror areas. The external capacitor on pin 33 integrates the track-crossing frequency component.

The internal time constant of the mirror detector can be set for normal, double, or quadruple speed by microprocessor commands, to raise the trackable range of track-crossing frequencies.

Figure 10 Mirror Detector Waveforms

#### 7. Bias

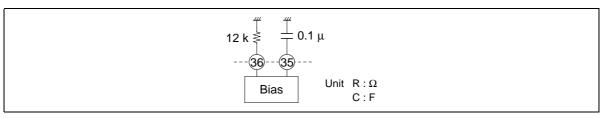

The 12-k $\Omega$  external resistor on pin 36 sets the reference value of the IC's internal bias current. Use only this resistance value. The IC will not operate correctly with other resistance values.

Pin 35 is for a bypass capacitor to eliminate noise from the IC's internal bias circuits.

Figure 11 Bias

#### 8. APC

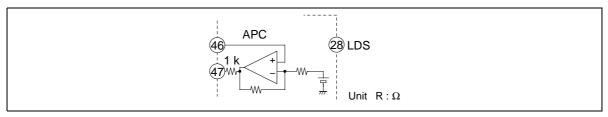

This circuit is for the Psub laser diode. The APC circuit is switched off when pin 28 is high.

Figure 12 APC

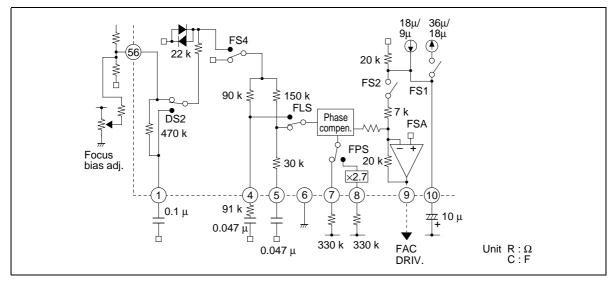

#### 9. Focus Servo System

The focus error signal is led in through a gain-control resistor to pin 56. Focus bias is adjusted at pin 56.

When a defect is detected, switch DS2 propagates the focus error signal, which is integrated by an internal resistor and external capacitor. Switch DS2 also inverts the phase of the propagated signal.

Switch FS4 is the focus servo loop switch.

Switch FLS switches low frequency filter, thereby switching the AC gain of the servo.

Switch FPS switches the peak phase-compensation frequency. This switch is linked with switch FLS and tracking servo switches TLS and TPS. For example this switch is off at normal, double speed and is on at quadruple speed.

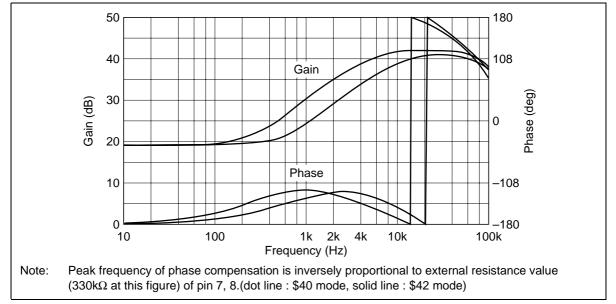

The DC gain from input at pin 56 to output at pin 9 is 19dB. Figure 14 shows the frequency characteristic when pin 4, 5 are open.

#### Rev.1, Oct. 1995, page 20 of 35

Switch FS1 switches a current source to generate the focus search voltage. When switch FS2 is switched on, focus is acquired by switching switch FS1 on and off.

The current through switch FS1 can be switched in two stages:  $36\mu A \sin k/18\mu A$  source, and  $18\mu A \sin k/9\mu A$  source.

Figure 13 Focus Servo

Figure 14 Focus Servo Frequency Characteristic (pin 4, 5 are open)

The transform function of phase compen block at figure 13 is as follows.

$$\frac{\text{VOUT}}{\text{VIN}} \approx \frac{8.95}{1+j\omega(2.7\times10^{-6})} \frac{1+j\omega\left(\frac{7.9\times10^{-9}}{I}\right)}{1+j\omega\left(\frac{5.6\times10^{-10}}{I}\right)}$$

$$\emptyset \approx \tan^{-1}\omega\left(\frac{7.9\times10^{-9}}{I}\right) - \tan^{-1}\omega\left(\frac{5.6\times10^{-10}}{I}\right) - \tan^{-1}\omega(2.7\times10^{-6})$$

at FPS OFF I = I<sub>7</sub> at FPS ON I = 2.7 I<sub>8</sub>

I<sub>7</sub> or I<sub>8</sub>  $\approx \frac{V_{CC} - 0.71V}{\text{External resistance value of pin 7 or 8}}$

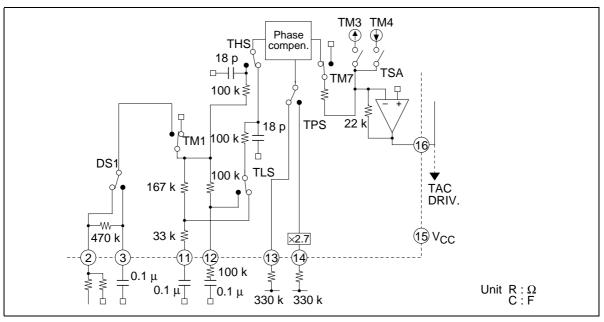

#### 10. Tracking Servo System

The tracking error signal is led in through a gain-control resistor to pin 2.

When a defect is detected, switch DS1 propagates the tracking error signal, which is integrated by an internal resistor and external capacitor. Switch DS1 also inverts the phase of the propagated signal. Switch TM1 is the tracking servo loop switch.

Switch TLS switches low frequency filter, thereby switching the AC gain of the servo.

The purpose of switch THS is to raise the high-frequency gain.

Switch TPS switches the peak phase-compensation frequency. This switch is linked with switch TLS and focus servo switches FLS and FPS. For example this switch is off at normal, double speed and is on at quadruple speed.

Switch TM7 is turned on by taking the logical AND of COUT and microprocessor data, to improve the performance of the pick-up. COUT is a signal generated by latching Mirror with both edges of TZC.

Figure 15 Tracking Servo

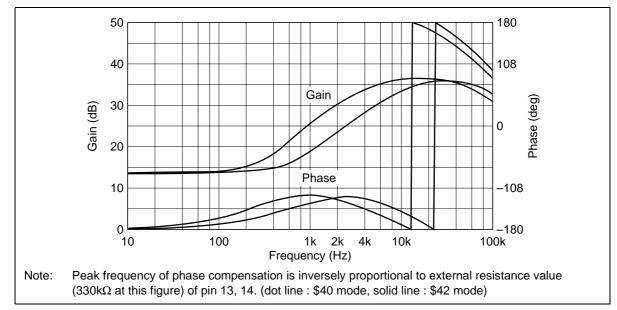

The transform function of phase compen block at figure 15 is as follows.

$$\begin{split} \frac{\text{VOUT}}{\text{VIN}} &\approx 4.47 \quad \frac{1+\text{j}\omega\left(\frac{7.9\times10^{-9}}{\text{I}}\right)}{1+\text{j}\omega\left(\frac{5.6\times10^{-10}}{\text{I}}\right)}\\ \text{$\emptyset \approx \tan^{-1}\omega\left(\frac{7.9\times10^{-9}}{\text{I}}\right) - \tan^{-1}\omega\left(\frac{5.6\times10^{-10}}{\text{I}}\right)$\\ \text{at TPS OFF} \quad I = I_{13} \quad \text{at TPS ON} \quad I = 2.7 \ I_{14}\\ I_{13} \text{ or } I_{14} &\approx \frac{V_{CC} - 0.71V}{\text{External resistance value of pin 13 or 14}} \end{split}$$

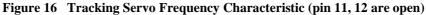

Figure 17 shows the phase relationships of Mirror, the tracking error, TZC, and COUT. TM7 operates to prevent the moving direction component of the tracking error signal from reaching the actuator.

The purpose of switches TM3 and TM4 is to generate the track jump voltage. A positive voltage appears at pin 16 when TM3 is switched on. A negative voltage appears at pin 16 when TM4 is switched on.

The current values through switches TM3 and TM4 can be selected in four steps:  $8\mu$ A,  $16\mu$ A,  $24\mu$ A, and  $32\mu$ A. The DC gain from input at pin 2 to output at pin 16 is 13dB. Figure 16 shows the frequency characteristic when pin 11, 12 are open.

Figure 17 Phase Relationships of Mirror and Other Signals

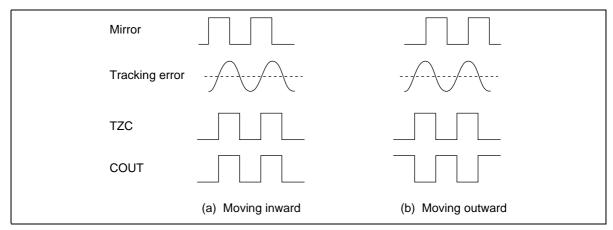

#### 11. DRT

DRT is an output signal that indicates the inward or outward direction. In the example in figure 18, DRT is low during motion from outer toward inner tracks, and high for motion in the reverse direction. This signal is output from pin 20 on command from the microprocessor.

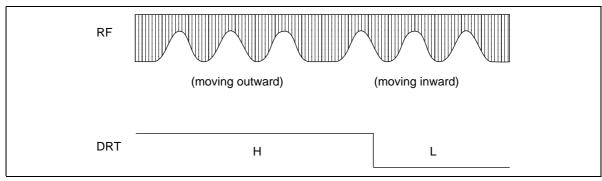

#### 12. Sled Servo

The signal output at pin 16 is passed through a low-pass filter and input at pin 17. TM2 is the loop switch of the sled servo.

TM5 and TM6 are current switches that generate voltages for large movements of the sled. A positive voltage appears at pin 19 when TM5 is switched on. A negative voltage appears at pin 19 when TM6 is switched on.

The current values through switches TM5 and TM6 can be selected in four steps:  $8\mu A$ ,  $16\mu A$ ,  $24\mu A$ , and  $32\mu A$ .

Figure 19 Sled Servo

#### 13. Direct Control

The switches in the tracking control and sled servo control blocks can be switched on and off by microprocessor commands. TM1 to TM6 can also be controlled directly by the DC pin after input of serial data from the microprocessor.

When the microprocessor sends a command from \$20 to \$2F as serial data with DC high, TM1 to TM6 are placed in the states indicated under ST1 in table 2. Next, when DC is driven low, the states change to ST2. When DC is brought high again, the states change to ST3.

Example of using the DC terminal for 1 track jump is as follows.

For inside track jump, after sending the 2C at DC = H, when the TZC's rising edge is detected set DC = L and set DC = H after a setting time.

For outside track jump, after sending the \$28 at DC = "H", when the TZC's falling edge is detected, set DC = "L" and set DC = "H" after a setting time.

#### Rev.1, Oct. 1995, page 25 of 35

### **Test Circuit Diagram**

### **Absolute Maximum Ratings**

| ltem                  | Symbol          | Value       | Unit |

|-----------------------|-----------------|-------------|------|

| Power supply voltage  | V <sub>cc</sub> | 7           | V    |

| Power dissipation     | Ρ,              | 550         | mW   |

| Operating temperature | Topr            | -20 to +75  | °C   |

| Storage temperature   | Tstg            | -55 to +125 | °C   |

Note: Recommended operating power supply voltage range:  $5 \pm 0.5V$ .

## **Electrical Characteristics** (Ta = $25^{\circ}$ C, V<sub>cc</sub> = 5V)

| Item                   |                            | Symbol                            | Min  | Тур  | Max  | Unit | Test Conditions                              | Pins   |

|------------------------|----------------------------|-----------------------------------|------|------|------|------|----------------------------------------------|--------|

| 1.Current di           | issipation                 | I <sub>cc</sub>                   |      | 36   | 52   | mA   | No signal                                    | 15, 42 |

| 2.Reference voltage    |                            | V <sub>c</sub>                    | 2.3  | 2.5  | 2.7  | V    | 145 = ±5mA                                   | 45     |

| RF amp.                | 3.Offset voltage           | $V_{RF}$                          | -65  | 0    | 65   | mV   |                                              | 38     |

|                        | 4.Max. output level H      | $V_{rfh}$                         | 4.2  | —    | _    | V    | S38,S43,S44,S61<br>V61 = 4.0V                | 38     |

|                        | 5.Max. output level L      | $V_{rfl}$                         | _    | _    | 2.1  | V    | S38,S43,S44,S61<br>V61 = 1.0V                | 38     |

|                        | 6.Voltage gain             | $\boldsymbol{G}_{\text{vrf}}$     | 10.0 | 12.0 | 14.0 | dB   | S43, S44, S60<br>V38/V <sub>№</sub> 60       | 38     |

| Focus<br>error amp.    | 7.Offset voltage           | $V_{FA}$                          | -65  | 0    | 65   | mV   |                                              | 55     |

|                        | 8.Max. output level H      | $V_{fah}$                         | 4.0  | 4.5  | _    | V    | S44, S55, S61<br>V61 = 4.0V                  | 55     |

|                        | 9.Max. output level L      | $V_{fal}$                         | _    | 0.5  | 1.0  | V    | S43, S55, S61<br>V61 = 4.0V                  | 55     |

|                        | 10.Voltage gain 1          | $\boldsymbol{G}_{\text{vfai}}$    | 6.7  | 8.7  | 10.7 | dB   | S43, S60<br>V55/V <sub>№</sub> 60            | 55     |

|                        | 11.Voltage gain 2          | $\boldsymbol{G}_{\text{VFA2}}$    | 6.7  | 8.7  | 10.7 | dB   | S44, S60<br>V55/V <sub>№</sub> 60            | 55     |

| Tracking<br>error amp. | 12.Offset voltage          | $V_{\text{te}}$                   | -50  | 0    | 50   | mV   |                                              | 52     |

|                        | 13.Max. output level H     | $V_{teh}$                         | 4.0  | 4.5  | _    | V    | S49, S52, S61<br>V61 = 4.0V                  | 52     |

|                        | 14.Max. output level L     | $V_{tel}$                         | _    | 0.5  | 1.0  | V    | S48, S52, S61<br>V61 = 4.0V                  | 52     |

|                        | 15.Voltage gain 1          | $\boldsymbol{G}_{_{VTE1}}$        | 7.0  | 9.0  | 11.0 | dB   | S49, S60<br>V52/V <sub>№</sub> 60            | 52     |

|                        | 16.Voltage gain 2          | $\boldsymbol{G}_{_{\text{VTE2}}}$ | 7.0  | 9.0  | 11.0 | dB   | S48, S60<br>V52/V <sub>№</sub> 60            | 52     |

| FOK                    | 17.FOK Vth                 | V <sub>fok</sub>                  | 0.25 | 0.38 | 0.50 | V    | S34, S61<br>when V32 ≥ 4V<br>Min (V38 – V34) | 32     |

|                        | 18."H" output voltage      | V <sub>FKH</sub>                  | 4.7  | —    | _    | V    | S34, S61                                     | 32     |

|                        | 19."L" output voltage      | V <sub>FKL</sub>                  | _    | _    | 0.4  | V    | S32, S34, S61                                | 32     |

| Defect                 | 20.Max operation frequency | F <sub>DH</sub>                   | 2    | _    | _    | kHz  | S43, S44, S60                                | 20     |

|                        | 21.Min operation frequency | F <sub>DL</sub>                   | —    | —    | 1    | kHz  | S43, S44, S60                                | 20     |

|                        | 22."H" output voltage      | $V_{\text{dfh}}$                  | 4.7  | _    | _    | V    |                                              | 20     |

|                        | 23."L" output voltage      | V                                 | _    | _    | 0.4  | V    | S20                                          | 20     |

Note: All offset voltages are values referring to  $V_c$  (pin 45)at XRST = "L".

### **Electrical Characteristics** (Ta = 25°C, $V_{cc}$ = 5V) (cont)

| ltem                              |                              | Symbol           | Min   | Тур   | Мах   | Unit | Test Conditions                                      | Pins        |

|-----------------------------------|------------------------------|------------------|-------|-------|-------|------|------------------------------------------------------|-------------|

| Defect                            | 24.Operation min input level | $V_{\text{DF1}}$ | 0.75  | _     | _     | VPP  | S43, S44, S60                                        | 20          |

| -                                 | 25.operation max input level | $V_{\rm dF2}$    | _     | _     | 2.5   | VPP  | S43, S44, S60                                        | 20          |

| COUT                              | 26.Max operation frequency   | $F_{co}$         | 100   | _     | _     | kHz  | S34A, S53, S60 *1<br>Mirror Qudruple<br>mode         | 21          |

| -                                 | 27."H" output voltage        | V <sub>COH</sub> | 4.7   | —     | —     | V    |                                                      | 21          |

| -                                 | 28."L" output voltage        | V <sub>COL</sub> | —     | —     | 0.4   | V    | S21                                                  | 21          |

| CLK,<br>DATA,<br>XLT, DC,<br>XRST | 29."H" input level           | V <sub>MH</sub>  | 4.0   | _     | _     | V    |                                                      | 23 to<br>27 |

| -                                 | 30."L" input level           | $V_{\rm ML}$     | —     | —     | 1.0   | V    |                                                      | 23 to<br>27 |

| APC                               | 31.APC voltage               | V                | 0.09  | 0.16  | 0.23  | V    |                                                      | 46          |

| 32.TZC Vth                        |                              | $V_{\text{tzc}}$ | -40   | 0     | 40    | mV   | S53, S61<br>Refer to V53                             | 53          |

| 33.FZC Vth                        |                              | $V_{_{FZC}}$     | 0.25  | 0.38  | 0.50  | V    | S43, S61                                             | 55          |

| Focus<br>servo<br>amp.            | 34.Offset voltage            | $V_{\rm FO}$     | -100  | 0     | 100   | mV   |                                                      | 9           |

| -                                 | 35.Max output level H        | $V_{FOH}$        | 4.0   | 4.5   | —     | V    | S9, S56, S61<br>FS4 on, V61 = 1.0V                   | 9           |

| -                                 | 36.Max output level L        | $V_{FOL}$        | _     | 0.8   | 1.0   | V    | S9, S56, S61<br>FS4 on, V61 = 4.0V                   | 9           |

| -                                 | 37.Voltage gain              | $G_{vfo}$        | 16.9  | 18.9  | 20.9  | dB   | S56, S60<br>V9/V <sub>⊪</sub> 60<br>FS4, FLS, FPS on | 9           |

| -                                 | 38.Search voltage 1          | $V_{s_1}$        | -0.70 | -0.51 | -0.32 | V    | FS2 on<br>V9 – $V_{FO} - V_{C}$                      | 9           |

|                                   | 39.Search voltage 2          | $V_{s_2}$        | 0.32  | 0.51  | 0.70  | V    | FS2, FS1 on V9 – $V_{FO}$ – $V_{C}$                  | 9           |

| Tracking<br>servo<br>amp.         | 40.Offset voltage            | V <sub>to</sub>  | -120  | 0     | 120   | mV   |                                                      | 16          |

| -                                 | 41.Max output level H        | $V_{\text{TOH}}$ | 4.0   | 4.5   | —     | V    | S2, S16, S61<br>TM1 on, V61 = 1.0V                   | 16          |

| -                                 | 42.Max output level L        | $V_{\text{tol}}$ | _     | 0.8   | 1.0   | V    | S2, S16, S61<br>TM1 on, V61 = 4.0V                   | 16          |

Note: 90deg phase differnce between  $V_{_{\rm IN}}$  34 and  $V_{_{\rm IN}}$  60.

# **Electrical Characteristics** (Ta = 25°C, $V_{cc}$ = 5V) (cont)

| Item                   |                       | Symbol                                     | Min   | Тур   | Max   | Unit | Test Conditions                                               | Pins |

|------------------------|-----------------------|--------------------------------------------|-------|-------|-------|------|---------------------------------------------------------------|------|

| Tracking<br>servo amp. | 43.Voltage gain       | G <sub>vro</sub>                           | 11.4  | 13.4  | 15.4  | dB   | S2, S60<br>TLS, TPS, TM1 on<br>V16/V <sub>IN</sub> 60         | 16   |

|                        | 44.TM3 voltage        | $V_{\text{TM3}}$                           | 0.51  | 0.71  | 0.89  | V    | TM3 on<br>V16 – V <sub>to</sub> – V <sub>c</sub>              | 16   |

|                        | 45.TM4 voltage        | $V_{\rm TM4}$                              | -0.89 | -0.71 | -0.51 | V    | TM4 on<br>V16 – V <sub>to</sub> – V <sub>c</sub>              | 16   |

| Sled servo<br>amp.     | 46.Offset voltage     | $V_{so}$                                   | -66   | 0     | 66    | mV   |                                                               | 19   |

|                        | 47.Max output level H | $V_{\rm SOH}$                              | 4.0   | 4.5   | —     | V    | S17, S19, S61<br>TM2 on V61 = 4.0V                            | 19   |

|                        | 48.Max output level L | $V_{SOL}$                                  | _     | 0.8   | 1.0   | V    | S17, S19, S61<br>TM2 on, V61 = 1.0V                           | 19   |

|                        | 49.Voltage gain       | $G_{vs}$                                   | 17.3  | 19.3  | 21.3  | dB   | S17, S60<br>TM2 on, V19/V <sub>⊪</sub> 60                     | 19   |

|                        | 50.TM5 voltage        | $V_{\text{TM5}}$                           | 0.55  | 0.85  | 1.10  | V    | 16μA mode<br>TM5 on<br>V19 – V <sub>so</sub> – V <sub>c</sub> | 19   |

|                        | 51.TM6 voltage        | $V_{\text{TM6}}$                           | -1.10 | -0.85 | -0.55 | V    | 16μA mode<br>TM6 on<br>V19 – V <sub>so</sub> – V <sub>c</sub> | 19   |

| SENS                   | 52."H" output voltage | $V_{\text{SEH}}$                           | 4.7   | _     | _     | V    |                                                               | 22   |

|                        | 53."L" output voltage | V                                          | —     | —     | 0.4   | V    | S22                                                           | 22   |

| LDS                    | 54."H" input voltage  | $V_{LDH}$                                  | 3.5   | _     | _     | V    |                                                               | 28   |

|                        | 55."L" input voltage  | $V_{\text{LDL}}$                           | _     | —     | 0.5   | V    |                                                               | 28   |

| Focus VR               | 56.VR gain 1          | $\boldsymbol{G}_{_{FVR1}}$                 | -5.8  | -4.8  | -3.8  | dB   | S43, S60<br>V55 / V <sub>IN</sub> 60 – G <sub>VFA1</sub>      | 55   |

|                        | 57.VR gain 2          | $\boldsymbol{G}_{\text{fvr2}}$             | -3.2  | -2.2  | -1.2  | dB   | S43, S60<br>V55 / V <sub>IN</sub> 60 – G <sub>VFA1</sub>      | 55   |

|                        | 58.VR gain 3          | $\boldsymbol{G}_{\text{fvr3}}$             | 2.8   | 3.8   | 4.8   | dB   | S43, S60<br>V55 / V <sub>IN</sub> 60 – G <sub>VFA1</sub>      | 55   |

|                        | 59.VR gain 4          | $\boldsymbol{G}_{_{FVR4}}$                 | 5.8   | 6.8   | 7.8   | dB   | S43, S60<br>V55 / V <sub>IN</sub> 60 – G <sub>VFA1</sub>      | 55   |

| Tracking<br>VR         | 60.VR gain 1          | $\boldsymbol{G}_{\scriptscriptstyle TVR1}$ | -5.9  | -4.9  | -3.9  | dB   | S48, S60<br>V52 / V <sub>IN</sub> 60 – G <sub>VTE2</sub>      | 52   |

|                        | 61.VR gain 2          | $\boldsymbol{G}_{\scriptscriptstyle TVR2}$ | -3.3  | -2.3  | -1.3  | dB   | S48, S60<br>V52 / V <sub>IN</sub> 60 – G <sub>VTE2</sub>      | 52   |

|                        | 62.VR gain 3          | ${\sf G}_{\rm tyr3}$                       | 2.9   | 3.9   | 4.9   | dB   | S48, S60<br>V52 / V <sub>IN</sub> 60 – G <sub>VTE2</sub>      | 52   |

|                        | 63.VR gain 4          | $\boldsymbol{G}_{\scriptscriptstyle TVR4}$ | 5.9   | 6.9   | 7.9   | dB   | S48, S60<br>V52 / V <sub>IN</sub> 60 – G <sub>VTE2</sub>      | 52   |

| Item   |                              | Symbol                                     | Min  | Тур  | Мах  | Unit        | Test Conditions                                        | Pins |

|--------|------------------------------|--------------------------------------------|------|------|------|-------------|--------------------------------------------------------|------|

| BAL    | 64.BAL gain 1                | ${\sf G}_{\scriptscriptstyle \sf BA1}$     | -4.2 | -3.2 | -2.2 | dB          | S48, S60<br>V52/V <sub>IN</sub> 60 – G <sub>VTE2</sub> | 52   |

|        | 65.BAL gain 2                | $G_{_{BA2}}$                               | -3.7 | -2.7 | -1.7 | dB          | S48, S60<br>V52/V <sub>IN</sub> 60 – G <sub>VTE2</sub> | 52   |

|        | 66.BAL gain 3                | $G_{_{\text{BA3}}}$                        | -3.2 | -2.2 | -1.2 | dB          | S48, S60<br>V52/V <sub>№</sub> 60 – G <sub>VTE2</sub>  | 52   |

|        | 67.BAL gain 4                | $G_{\scriptscriptstyleBA4}$                | -2.4 | -1.4 | -0.4 | dB          | S48, S60<br>V52/V <sub>IN</sub> 60 – G <sub>VTE2</sub> | 52   |

|        | 68.BAL gain 5                | ${\sf G}_{{\scriptscriptstyle {\sf BA5}}}$ | 1.1  | 2.1  | 3.1  | dB          | S48, S60<br>V52/V <sub>IN</sub> 60 – G <sub>VTE2</sub> | 52   |

| Mirror | 69.Operation min input level | V <sub>MI1</sub>                           | 0.25 | _    | _    | $V_{_{PP}}$ | S34A, S53, S60<br>Quadraple mode                       | 21   |

|        | 70.Operation max input level | $V_{\rm MI2}$                              | —    | —    | 2.5  | $V_{PP}$    | S34A, S53, S60<br>Quadraple mode                       | 21   |

# **Electrical Characteristics** (Ta = 25°C, $V_{cc} = 5V$ ) (cont)

### **Test Method Notes**

| Item No. | Notes |

|----------|-------|

|----------|-------|

| item No. | notes                                                                                                                                                                    |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | I15 (I15 means "current at pin 15". Following expressions are same as this expression.)+ I42                                                                             |

| 2        | V45 (V45 means "voltage at pin 45". Following expressions are same as this expression.<br>These symbols mean DC voltage at DC measuring and AC voltage at AC measuring.) |

| 3        | V38 – V <sub>c</sub>                                                                                                                                                     |

| 4, 5     | V38                                                                                                                                                                      |

| 6        | 20log (V38 / $V_{IN}60$ ) $V_{IN}60 = 500$ kHz, 0.2 $V_{PP}$                                                                                                             |

| 7        | $V55 - V_c$                                                                                                                                                              |

| 8, 9     | V55                                                                                                                                                                      |

| 10, 11   | 20log (V55 / V <sub>IN</sub> 60) V <sub>IN</sub> 60 = 4kHz, 0.5 V <sub>PP</sub>                                                                                          |

| 12       | $V52 - V_c$                                                                                                                                                              |

| 13, 14   | V52                                                                                                                                                                      |

| 15, 16   | 20log (V52 / $V_{IN}60$ ) $V_{IN}60 = 4$ kHz, 0.5 $V_{PP}$                                                                                                               |

| 17       | (V38 – V34) at the point that V32 exceeds 4V when V61 is lowered from 2.5V.                                                                                              |

| 18, 19   | V32                                                                                                                                                                      |

| 20       | The maximum frequency for VIN60 such that the pin 20 signal is still a square wave. $V_{IN}60 = 0.25 V_{PP} + V_{C} + 95 mV_{DC}$                                        |

| 21       | The minimum frequency for VIN60 such that the pin 20 signal is still a square wave.<br>$V_{IN}60 = 0.25 V_{PP} + V_{C} + 95mV_{DC}$                                      |

| 22, 23   | V20                                                                                                                                                                      |

### Test Method Notes (cont)

| Item No. | Notes                                                                                                                                                                                                   |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24       | The minimum voltage for V38 such that the pin 20 signal is still a square wave.<br>$V_{IN}60 = 1 \text{kHz} + V_c + 95 \text{mV}_{DC}$                                                                  |

| 25       | The maximum voltage for V38 such that the pin 20 signal is still a square wave. $V_{IN}60 = 1 \text{kHz} + V_c + 95 \text{ mV}_{DC}$                                                                    |

| 26       | $V_{IN}60$ , $V_{IN}34$ 90deg phase difference input signal $V_{IN}60 = V_{IN}34 = 1 V_{PP}$<br>The maximum frequency for $V_{IN}60$ ( $V_{IN}34$ ) such that the pin 21 signal is still a square wave. |

| 27, 28   | V21                                                                                                                                                                                                     |

| 29       | H input voltage of pin 23 to 27                                                                                                                                                                         |

| 30       | L input voltage of pin 23 to 27                                                                                                                                                                         |

| 31       | V46                                                                                                                                                                                                     |

| 32       | (V61 – V53) such that V22 exceeds 4V when V61 is upped from 2.4V. (SENS = TZC mode)                                                                                                                     |

| 33       | $(V55 - V_c)$ such that V22 exceeds 4V when V61 is upped from 2.5V. (SENS = FZC mode)                                                                                                                   |

| 34       | V9 – V <sub>c</sub>                                                                                                                                                                                     |

| 35, 36   | V9                                                                                                                                                                                                      |

| 37       | 20log (V9 / $V_{IN}60$ ) $V_{IN}60 = 1$ kHz, 0.15 $V_{PP}$                                                                                                                                              |

| 38, 39   | V9 – VFO – V <sub>c</sub>                                                                                                                                                                               |

| 40       | V16 – V <sub>c</sub>                                                                                                                                                                                    |

| 41, 42   | V16                                                                                                                                                                                                     |

| 43       | 20log (V16 / $V_{IN}60$ ) $V_{IN}60 = 1$ kHz, 0.3 $V_{PP}$                                                                                                                                              |

| 44, 45   | $V9 - VTO - V_c$                                                                                                                                                                                        |

| 46       | V19 – V <sub>c</sub>                                                                                                                                                                                    |

| 47, 48   | V19                                                                                                                                                                                                     |

| 49       | 20log (V19 / $V_{IN}60$ ) $V_{IN}60 = 4$ kHz, 0.15 $V_{PP}$                                                                                                                                             |

| 50, 51   | $V19 - VSO - V_{c}$                                                                                                                                                                                     |

| 52, 53   | V22                                                                                                                                                                                                     |

| 54       | Input voltage of pin 28 such that APC is off.                                                                                                                                                           |

| 55       | Input voltage of pin 28 such that APC is on.                                                                                                                                                            |

| 56       | $GF2 = 0, \overline{GF1} = 1, GF0 = 0$ 20log (V55 / $V_{IN}60$ ) – $G_{VFA1}$ $V_{IN}60 = 4kHz, 0.5 V_{PP}$                                                                                             |

| 57       | $GF2 = 0, \overline{GF1} = 1, GF0 = 1$ 20log (V55 / V <sub>IN</sub> 60) - G <sub>VFA1</sub> V <sub>IN</sub> 60 = 4kHz, 0.5 V <sub>PP</sub>                                                              |

| 58       | $GF2 = 1, \overline{GF1} = 1, GF0 = 0$ 20log (V55 / V <sub>IN</sub> 60) - G <sub>VFA1</sub> V <sub>IN</sub> 60 = 4kHz, 0.5 V <sub>PP</sub>                                                              |

| 59       | $GF2 = 1, \overline{GF1} = 0, GF0 = 1$ 20log (V55 / V <sub>IN</sub> 60) - G <sub>VEA1</sub> V <sub>IN</sub> 60 = 4kHz, 0.5 V <sub>PP</sub>                                                              |

| 60       | $GT2 = 0, \overline{GT}1 = 1, GT0 = 0$ 20log (V52 / V <sub>IN</sub> 60) - G <sub>VTE2</sub> V <sub>IN</sub> 60 = 4kHz, 0.5 V <sub>PP</sub>                                                              |

| 61       | $GT2 = 0, \overline{GT}1 = 1, GT0 = 1$ 20log (V52 / V <sub>IN</sub> 60) - G <sub>VTE2</sub> V <sub>IN</sub> 60 = 4kHz, 0.5 V <sub>PP</sub>                                                              |

| 62       | $GT2 = 1, \overline{GT}1 = 1, GT0 = 0$ 20log (V52 / V <sub>IN</sub> 60) - G <sub>VTE2</sub> V <sub>IN</sub> 60 = 4kHz, 0.5 V <sub>PP</sub>                                                              |

| 63       | $GT2 = 1, \overline{GT}1 = 0, GT0 = 1$ 20log (V52 / V <sub>IN</sub> 60) - G <sub>VTE2</sub> V <sub>IN</sub> 60 = 4kHz, 0.5 V <sub>PP</sub>                                                              |

### Test Method Notes (cont)

| Item No. | Notes |

|----------|-------|

|----------|-------|

| 64 | $\overline{\text{BAL}3}$ = 1, $\text{BAL}2$ = 0, $\text{BAL}1$ = 0, $\text{BAL}0$ = 0 20log (V52 / V <sub>IN</sub> 60) - G <sub>VTE2</sub> V <sub>IN</sub> 60 = 4kHz, 0.5V <sub>PP</sub>    |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 65 | $\overline{\text{BAL}3}$ = 1, $\text{BAL}2$ = 0, $\text{BAL}1$ = 0, $\text{BAL}0$ = 1 20log (V52 / V <sub>IN</sub> 60) - G <sub>VTE2</sub> V <sub>IN</sub> 60 = 4kHz, 0.5V <sub>PP</sub>    |

| 66 | $\overline{\text{BAL}3}$ = 1, $\text{BAL}2$ = 0, $\text{BAL}1$ = 1, $\text{BAL}0$ = 0 20log (V52 / V <sub>IN</sub> 60) - G <sub>VTE2</sub> V <sub>IN</sub> 60 = 4kHz, 0.5V <sub>PP</sub>    |

| 67 | $\overline{\text{BAL}3}$ = 1, $\text{BAL}2$ = 1, $\text{BAL}1$ = 0, $\text{BAL}0$ = 0 20log (V52 / V <sub>IN</sub> 60) - G <sub>VTE2</sub> V <sub>IN</sub> 60 = 4kHz, 0.5V <sub>PP</sub>    |

| 68 | $\overline{\text{BAL}3} = 0$ , $\text{BAL}2 = 1$ , $\text{BAL}1 = 1$ , $\text{BAL}0 = 1$ 20log (V52 / V <sub>IN</sub> 60) - G <sub>VTE2</sub> V <sub>IN</sub> 60 = 4kHz, 0.5V <sub>PP</sub> |

| 69 | The minimum input voltage for VIN34 such that the pin 21 signal is still a square wave. $V_{IN}60 = 1$ MHz, 1 $V_{PP}$ $V_{IN}34 = 100$ kHz                                                 |

| 70 | The maximum input voltage for VIN34 such that the pin 21 signal is still a square wave.<br>$V_{IN}60 = 1$ MHz, 1 $V_{PP}$ $V_{IN}34 = 100$ kHz                                              |

### **Package Dimensions**

Unit: mm

#### Disclaimer

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

#### **Sales Offices**

### HITACHI Hitachi, Ltd.

Semiconductor & Integrated Circuits. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109

| URL                               | NorthAmerica | : http://semiconductor.hitachi.com/      |  |  |  |

|-----------------------------------|--------------|------------------------------------------|--|--|--|

|                                   | Europe       | : http://www.hitachi-eu.com/hel/ecg      |  |  |  |

|                                   | Asia         | : http://sicapac.hitachi-asia.com        |  |  |  |

|                                   | Japan        | : http://www.hitachi.co.jp/Sicd/indx.htm |  |  |  |

| For further information write to: |              |                                          |  |  |  |

#### For further information write to: Hitachi Semiconductor Hitachi Europe GmbH

Hitachi Semiconductor (America) Inc. 179 East Tasman Drive, San Jose,CA 95134 Tel: <1> (408) 433-1990 Fax: <1>(408) 433-0223