# 3.3V Phase-Lock Loop Clock Driver

### **General Description**

**The ICS2509C** is a high performance, low skew, low jitter clock driver. It uses a phase lock loop (PLL) technology to align, in both phase and frequency, the CLKIN signal with the CLKOUT signal. It is specifically designed for use with synchronous SDRAMs. The **ICS2509C** operates at 3.3V VCC and drives up to nine clock loads.

One bank of five outputs and one bank of four outputs provide nine low-skew, low-jitter copies of CLKIN. Output signal duty cycles are adjusted to 50 percent, independent of the duty cycle at CLKIN. Each bank of outputs can be enabled or disabled separately via control (OEA and OEB) inputs. When the OE inputs are high, the outputs align in phase and frequency with CLKIN; when the OE inputs are low, the outputs are disabled to the logic low state.

The ICS2509C does not require external RC filter components. The loop filter for the PLL is included on-chip, minimizing component count, board space, and cost. The buffer mode shuts off the PLL and connects the input directly to the output buffer. This buffer mode, the ICS2509C can be use as low skew fanout clock buffer device. The ICS2509C comes in 24 pin 173mil Thin Shrink Small-Outline package (TSSOP) package.

#### **Features**

- Meets or exceeds PC133 registered DIMM specification 1.1

- Spread Spectrum Clock Compatible

- Distributes one clock input to one bank of five and one bank of four outputs

- Separate output enable(OEA,OEB) for each output bank

- Operating frequency 25 MHz to 175 Mhz

- External feedback input (FBIN) terminal is used to synchrionize the outputs to the clock input

- No external RC network required

- Operates at 3.3V Vcc

- Plastic 24-pin 173mil TSSOP package

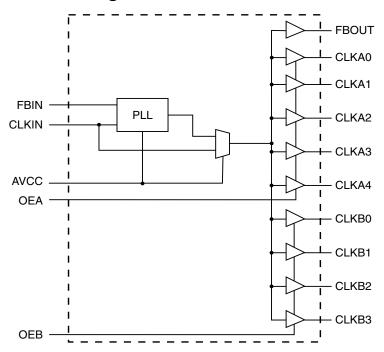

# **Block Diagram**

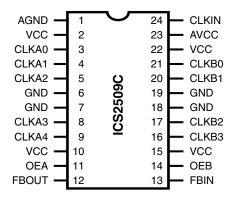

# **Pin Configuration**

24 Pin TSSOP 4.40 mm. Body, 0.65 mm. pitch

# ICS2509C

# **Pin Descriptions**

| PIN NUMBER   | PIN NAME         | TYPE | DESCRIPTION                                                                                                                         |

|--------------|------------------|------|-------------------------------------------------------------------------------------------------------------------------------------|

| 1            | AGND             | PWR  | Analog Ground                                                                                                                       |

| 2, 10, 15    | VCC              | PWR  | Power Supply (3.3V)                                                                                                                 |

| 3            | CLKA0            | OUT  | Buffered clock output, Bank A                                                                                                       |

| 4            | CLKA1            | OUT  | Buffered clock output, Bank A                                                                                                       |

| 5            | CLKA2            | OUT  | Buffered clock output, Bank A                                                                                                       |

| 6, 7, 18, 19 | GND              | PWR  | Ground                                                                                                                              |

| 8            | CLKA3            | OUT  | Buffered clock output, Bank A                                                                                                       |

| 9            | CLKA4            | OUT  | Buffered clock output, Bank A                                                                                                       |

| 11           | OEA <sup>1</sup> | IN   | Output enable (has internal pull_up). When high, normal operation. When low bank A clock outputs are disabled to a logic low state. |

| 12           | FBOUT            | OUT  | Feedback output                                                                                                                     |

| 13           | FBIN             | IN   | Feedback input                                                                                                                      |

| 14           | OEB <sup>1</sup> | IN   | Output enable (has internal pull_up). When high, normal operation. When low bank B clock outputs are disabled to a logic low state. |

| 16           | CLKB3            | OUT  | Buffered clock output. Bank B                                                                                                       |

| 17           | CLKB2            | OUT  | Buffered clock output. Bank B                                                                                                       |

| 20           | CLKB1            | OUT  | Buffered clock output. Bank B                                                                                                       |

| 21           | CLKB0            | OUT  | Buffered clock output. Bank B                                                                                                       |

| 22           | VCC              | PWR  | Power Supply (3.3V) digital supply.                                                                                                 |

| 23           | AVCC             | IN   | Analog power supply (3.3V). When input is ground PLL is off and bypassed.                                                           |

| 24           | CLKIN            | IN   | Clock input                                                                                                                         |

#### Note:

1. Weak pull-ups on these inputs

# **Functionality**

|     | INPUTS OUTPUTS |      |        |        | PLL    |        |          |  |

|-----|----------------|------|--------|--------|--------|--------|----------|--|

| OEA | OEB            | AVCC | (0:4)  | (0:3)  | FBOUT  | Source | Shutdown |  |

| 0   | 0              | 3.33 | 0      | 0      | Driven | PLL    | N        |  |

| 0   | 1              | 3.33 | 0      | Driven | Driven | PLL    | N        |  |

| 1   | 0              | 3.33 | Driven | 0      | Driven | PLL    | N        |  |

| 1   | 1              | 3.33 | Driven | Driven | Driven | PLL    | N        |  |

|     | Buffer Mode    |      |        |        |        |        |          |  |

| 0   | 0              | 0    | 0      | 0      | Driven | CLKIN  | Y        |  |

| 0   | 1              | 0    | 0      | Driven | Driven | CLKIN  | Y        |  |

| 1   | 0              | 0    | Driven | 0      | Driven | CLKIN  | Y        |  |

| 1   | 1              | 0    | Driven | Driven | Driven | CLKIN  | Y        |  |

Test mode:

When AVCC is 0, shuts off the PLL and connects the input directly to the output buffers

### **Absolute Maximum Ratings**

Supply Voltage (AVCC) . . . . . . . . . . AVCC < ( $V_{cc}$  + 0.7V)

Supply Voltage (VCC) ..... 4.3 V

Logic Inputs ...... GND -0.5 V to  $V_{cc} +0.5 \text{ V}$

Ambient Operating Temperature . . . . . .  $0^{\circ}$ C to  $+70^{\circ}$ C Storage Temperature . . . . .  $-65^{\circ}$ C to  $+150^{\circ}$ C

Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

### **Electrical Characteristics - OUTPUT**

$T_A = 0 - 70C$ ;  $V_{DD} = V_{DDL} = 3.3 \text{ V} + /-10\%$ ;  $C_L = 20 - 30 \text{ pF}$ ;  $R_L = 470 \text{ Ohms}$  (unless otherwise stated)

| PARAMETER                          | SYMBOL              | CONDITIONS                                       | MIN  | TYP  | MAX   | UNITS |

|------------------------------------|---------------------|--------------------------------------------------|------|------|-------|-------|

| Output Impedance                   | $R_{DSP}$           | $V_O = V_{DD}^*(0.5)$                            |      | 36   |       | Ω     |

| Output Impedance                   | $R_{DSN}$           | $V_{\rm O} = V_{\rm DD}^*(0.5)$                  |      | 32   |       | Ω     |

| Output High Voltage                | $V_{OH}$            | $I_{OH} = -8 \text{ mA}$                         | 2.4  | 2.9  |       | V     |

| Output Low Voltage                 | $V_{OL}$            | $I_{OL} = 8 \text{ mA}$                          |      | 0.25 | 0.4   | V     |

| Output High Current                | $I_{OH}$            | $V_{OH} = 2.4 \text{ V}$                         |      | -26  | -13.6 | mA    |

| Output Tingin Current              | +OH                 | $V_{OH} = 2.0 \text{ V}$                         |      | -37  | -22   |       |

| Output Low Current                 | $I_{OL}$            | $V_{OL} = 0.8 \text{ V}$                         | 19   | 25   |       | mA    |

| Output Low Current                 | <sup>1</sup> OL     | $V_{OL} = 0.55 \text{ V}$                        | 13   | 17   |       | ] """ |

| Rise Time <sup>1</sup>             | $T_{\rm r}$         | $V_{OL} = 0.8 \text{ V}, V_{OH} = 2.0 \text{ V}$ | 0.5  | 1.4  | 2.1   | ns    |

| Fall Time <sup>1</sup>             | $T_{\rm f}$         | $V_{OH} = 2.0 \text{ V}, V_{OL} = 0.8 \text{ V}$ | 0.5  | 1.5  | 2.7   | ns    |

| Duty Cycle <sup>1</sup>            | $D_{t}$             | $V_T = 1.5 \text{ V;} C_L = 30 \text{ pF}$       | 45   | 50   | 55    | %     |

| Cycle to Cycle jitter <sup>1</sup> | Tcyc-cyc            | at 66-100 MHz ; loaded outputs                   |      | 52   | 100   | ps    |

|                                    |                     | at 133 MHz; loaded outputs                       |      | 39   | 75    | PS    |

| Absolute Jitter <sup>1</sup>       | Tjabs               | 10000 cycles; $C_L = 30 \text{ pF}$              |      | 57   |       | ps    |

| Skew <sup>1</sup>                  | $T_{sk}$            | $V_T = 1.5 \text{ V (Window)}$ Output to Output  |      | 80   | 150   | ps    |

| Phase error <sup>1</sup>           | $T_{pe}$            | $V_T = Vdd/2$ ; CLKIN-FBIN                       | -150 | 40   | 150   | ps    |

| Phase error Jitter <sup>1</sup>    | $T_{pe}^{-3}$       | $V_T = Vdd/2$ ; CLKIN-FBIN; Delay Jitter         | -50  | 35   | 50    | ps    |

| Delay Input-Output                 | $\overline{D}_{R1}$ | $V_{\rm T} = 1.5 \text{ V}; \text{ PLL\_EN} = 0$ |      | 3.3  | 3.7   | ns    |

Guaranteed by design, not 100% tested in production.

# **ICS2509C**

# Electrical Characteristics - Input & Supply $T_A$ = 0 - 70C; Supply Voltage $V_{\rm DD}$ = 3.3 V +/-10% (unless otherwise stated)

| PARAMETER          | SYMBOL        | CONDITIONS                          | MIN           | TYP | MAX           | UNITS |

|--------------------|---------------|-------------------------------------|---------------|-----|---------------|-------|

| Input High Voltage | $ m V_{IH}$   |                                     | 2             |     | $V_{DD}$ +0.3 | V     |

| Input Low Voltage  | $V_{ m IL}$   |                                     | $V_{SS}$ -0.3 |     | 0.8           | V     |

| Input High Current | $I_{IH}$      | $V_{IN} = V_{DD}$                   |               | 0.1 | 100           | uA    |

| Input Low Current  | $I_{IL}$      | $V_{IN} = 0 V;$                     |               | 19  | 50            | uA    |

| Operating current  | $I_{DD1}$     | $C_L = 0 \text{ pF; } F_{IN} @ 66M$ |               | 140 | 170           | mA    |

| Input Capacitance  | $C_{IN}^{-1}$ | Logic Inputs                        |               | 4   |               | pF    |

| Output Capacitance | $C_{O}^{-1}$  | Logic Outputs                       |               | 8   |               | pF    |

<sup>&</sup>lt;sup>1</sup>Guarenteed by design, not 100% tested in production.

### liming requirements over recommended ranges of supply voltage and operating free-air temperature

| Symbol | Parameter                        | Test Conditions | Min. | Max. | Unit |

|--------|----------------------------------|-----------------|------|------|------|

| Fclk   | Input clock frequency            |                 | 25   | 175  | MHz  |

|        | Input clock frequency duty cycle |                 | 40   | 60   | %    |

|        | Stabilization time               | After power up  |      | 1    | ms   |

Note: Time required for the PLL circuit to obtain phase lock of its feedback signal to its reference In order for phase lock to be obtained, a fixed-frequency, fixed-phase reference signal must be Until phase lock is obtained, the specifications for parameters given in the switching characteristics table are not

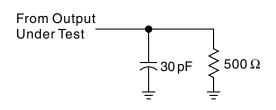

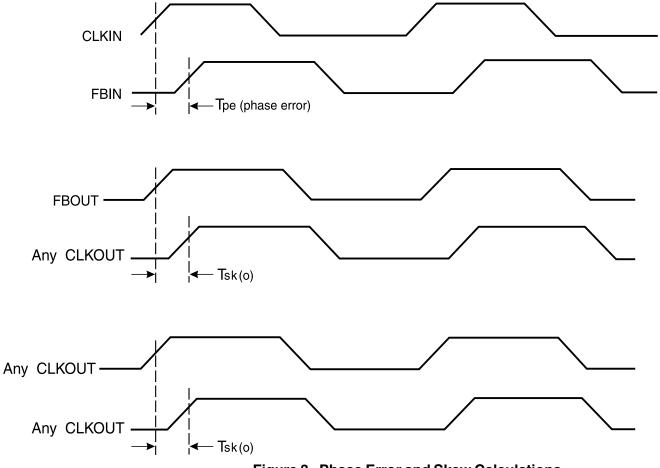

### PARAMETER MEASUREMENT INFORMATION

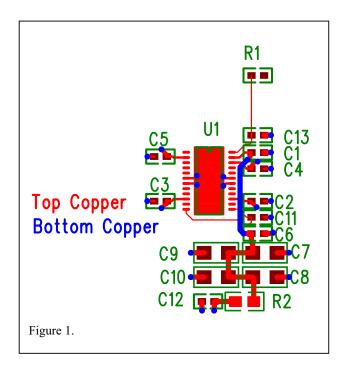

Figure 1. Load Circuit for Outputs

#### Notes:

- 1. C<sub>L</sub> includes probe and jig capacitance.

- 2. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  133MHz,  $Z_0 = 50 \Omega$ ,  $T_r \leq$ 1.2ns,  $T_f \leq$ 1.2ns.

- 3. The outputs are measured one at a time with one transition per measurement.

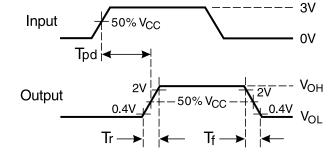

Figure 3. Phase Error and Skew Calculations

# ICS2509C

#### **General Layout Precautions:**

An ICS2509C is used as an example. It is similar to the ICS2510C. The same rules and methods apply.

- 1) Use copper flooded ground on the top signal layer under the clock buffer The area under U1 in figure 1 on the right is an example.

- Use power vias for power and ground. Vias 20 mil or larger in diameter have lower high frequency impedance. Vias for signals may be minimum drill size.

- 3) Make all power and ground traces are as wide as the via pad for lower inductance.

- 4) VAA for pin 23 has a low pass RC filter to decouple the digital and analog supplies. C9-11 may be replaced with a single low ESR (0.8 ohm or less) device with the same total capacitance.

- 5) Notice that ground vias are never shared.

- 6) All VCC pins have a decoupling capacitor. Power is always routed from the plane connection via to the capacitor pad to the VCC pin on the clock buffer.

- 7) Component R1 is located at the clock source.

#### Component Values:

C1= As necessary for delay adjust C[7:2]=.01uF

C8,C13=0.1uF C[11:9]=4.7Uf

R1=10 ohm. Locate at driver

R2=10 ohm.

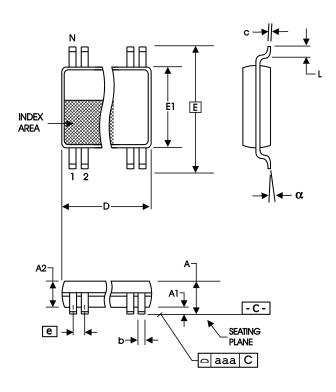

| 4.40 mm. Bo | dy, 0.65 mm. pitch TSSOP |

|-------------|--------------------------|

| (173 mil)   | (0.0256 Inch)            |

| SYMBOL | In Millimeters COMMON DIMENSIONS |       | In Inches COMMON DIMENSIONS |          |  |

|--------|----------------------------------|-------|-----------------------------|----------|--|

|        | MIN                              | MAX   | MIN                         | MAX      |  |

| Α      |                                  | 1.20  |                             | .047     |  |

| A1     | 0.05                             | 0.15  | .002                        | .006     |  |

| A2     | 0.80                             | 1.05  | .032                        | .041     |  |

| b      | 0.19                             | 0.30  | .007                        | .012     |  |

| С      | 0.09                             | 0.20  | .0035                       | .008     |  |

| D      | SEE VARIATIONS                   |       | SEE VARIATIONS              |          |  |

| E      | 6.40 I                           | BASIC | 0.252 BASIC                 |          |  |

| E1     | 4.30                             | 4.50  | .169                        | .177     |  |

| е      | 0.65 BASIC                       |       | 0.0256                      | BASIC    |  |

| L      | 0.45                             | 0.75  | .018                        | .030     |  |

| N      | SEE VARIATIONS                   |       | SEE VAF                     | RIATIONS |  |

| α      | 0°                               | 8°    | 0°                          | 8°       |  |

| aaa    |                                  | 0.10  |                             | .004     |  |

#### **VARIATIONS**

| N  | Dr   | nm.  | D (inch) |      |  |

|----|------|------|----------|------|--|

|    | MIN  | MAX  | MIN      | MAX  |  |

| 24 | 7.70 | 7.90 | .303     | .311 |  |

Reference Doc.: JEDEC Publication 95, MO-153

10-0035

# **Ordering Information**

ICS2509CyG-T