# mos integrated circuit $\mu PD75237$

## 4-BIT SINGLE-CHIP MICROCOMPUTER

#### **DESCRIPTION**

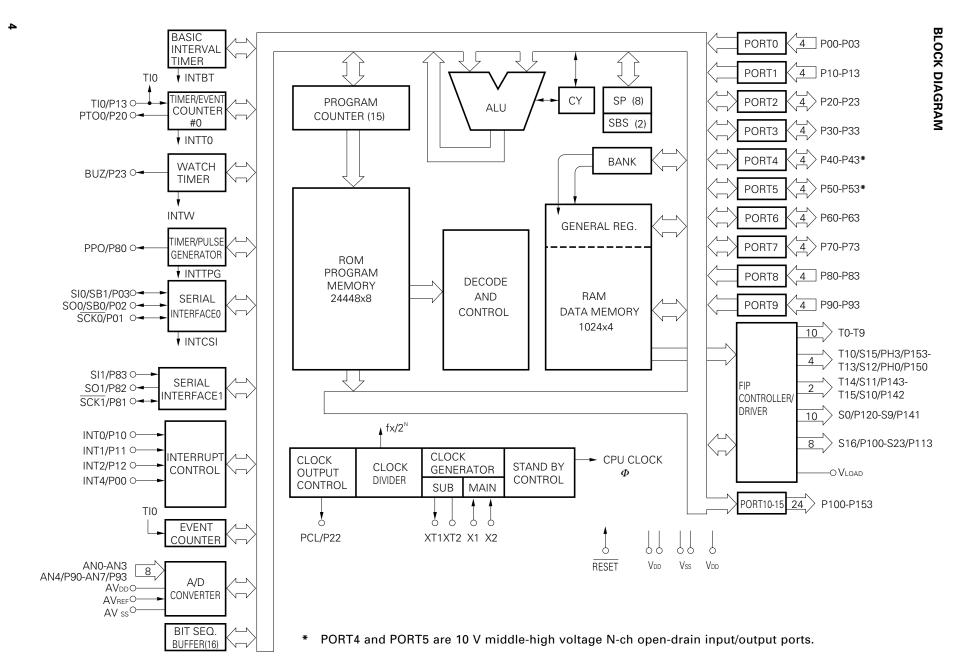

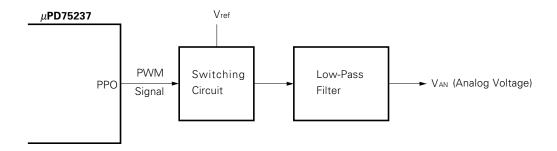

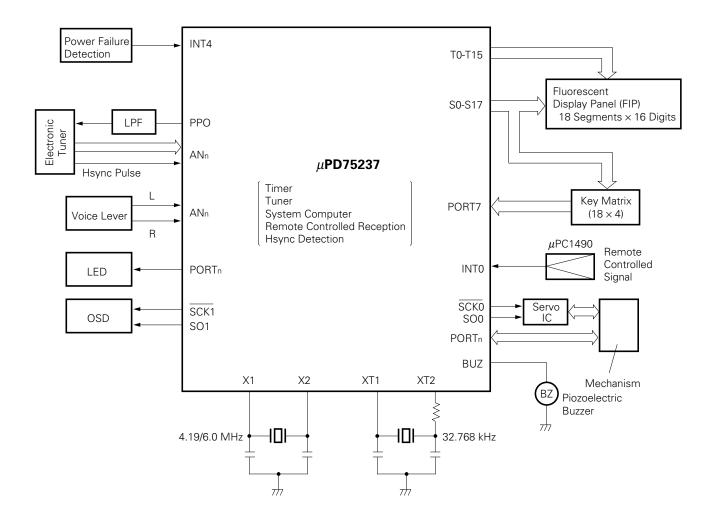

The  $\mu$ PD75237 is a microcomputer with a CPU capable of 1-, 4-, and 8-bit-wise data processing, a ROM, a RAM, I/O ports, a fluorescent display tube (FIP <sup>®</sup>) controller/driver, A/D converters, a watch timer, a timer/pulse generator capable of outputting 14-bit PWM, a serial interface and a vectored interrupt function integrated on a single-chip.

The  $\mu$ PD75237 has the more improved peripheral functions including the RAM capacity, FIP controller/driver display capabilities, I/O ports, A/D converter and serial interface than those of the  $\mu$ PD75217.

The  $\mu$ PD75237 is most suited for advanced and popular VCR timer and tuner applications, single-chip configurations of system computers, advanced CD players and advanced microwave ovens.

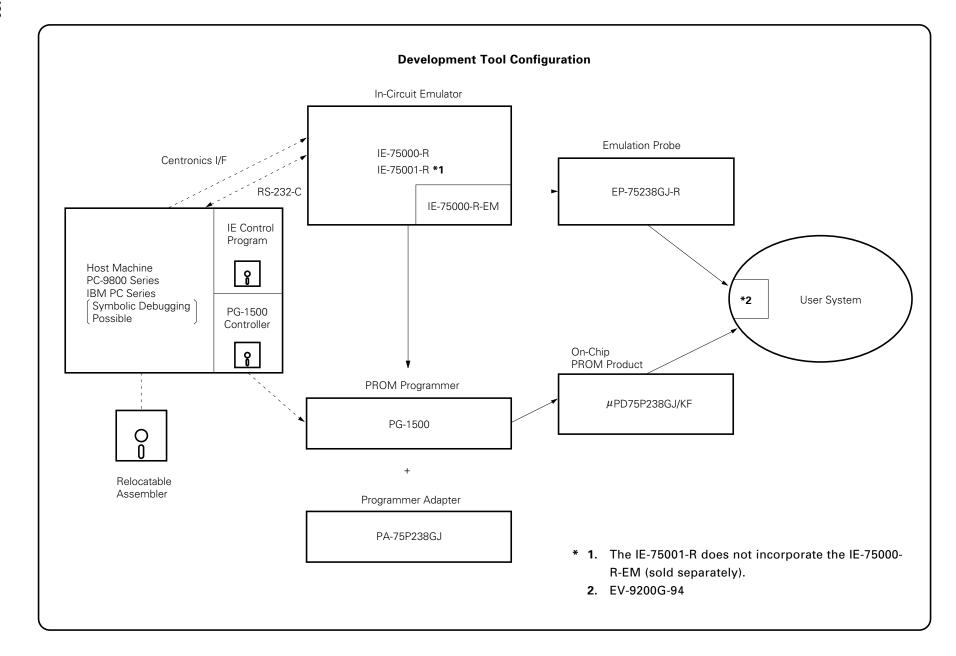

The  $\mu$ PD75P238 PROM product and various types of development tools (IE-75001-R, assemblers and others) are available for evaluation in system development or small-volume production.

#### **FEATURES**

- Built-in, large-capacity ROM and RAM

- Program memory (ROM): 24K × 8

- Data memory (RAM): 1K × 4

- I/O port: 64 ports (except FIP dedicated pins)

- Minimum instruction execution time: 0.67  $\mu s$  (when operated at 6.0 MHz)

- Instruction execution time varying function to achieve a wide range of power supply voltages

- Built-in programmable FIP controller/driver

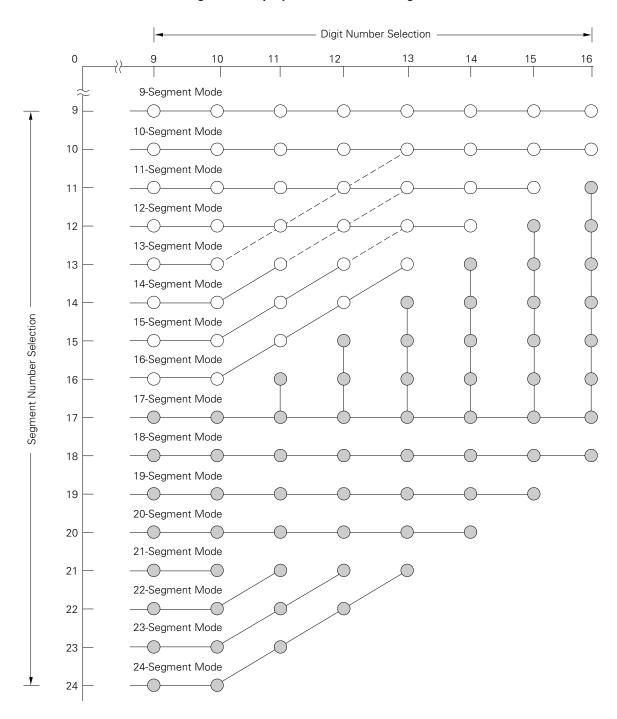

- Number of segments: 9 to 24

Number of digital 0 to 16

- Number of digits: 9 to 16

- 8-bit A/D converter: 8 channels

- Powerful timer/counter function: 5 channels

- 8-bit serial interface: 2 channels

- Interrupt function with importance attached to applications

- Product with built-in PROM: μPD75P238

## ORDERING INFORMATION

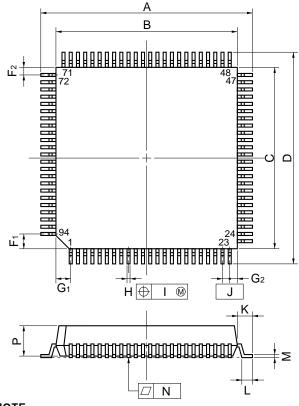

| Ordering Code      | Package                                | Quality Grade |

|--------------------|----------------------------------------|---------------|

| μPD75237GJ-×××-5BG | 94-pin plastic QFP (20 $\times$ 20 mm) | Standard      |

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

The information in this document is subject to change without notice.

# LIST OF $\mu$ PD75237 FUNCTIONS

| Item                                                   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Built-in memory capacity                               | ROM: 24448 × 8 bits, RAM: 1024 × 4bits                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| I/O line<br>(except FIP<br>dedicated pins)             | 64 lines   O Input pin : 16  Input/output pin : 24  O Output pin : 24                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

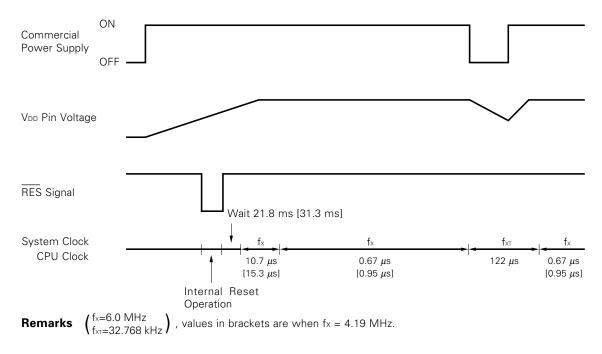

| Instruction cycle                                      | $\circ$ 0.67 μs/1.33 μs/2.67 μs/10.7 μs (when operated at 6.0 MHz) $\circ$ 0.95 μs/1.91 μs/3.82 μs/15.3 μs (when operated at 4.19 MHz) $\circ$ 122 μs (when operated at 32.768 kHz)                                                                                                                                                                                                                                                                                              |  |  |  |

| Fluorescent display<br>tube (FIP)<br>controller/driver | <ul> <li>Number of segments: 9 to 24</li> <li>Number of digits: 9 to 16</li> <li>Dimmer function: 8 levels</li> <li>Pull-down resistor mask option</li> <li>Key scan interrupt generation enabled</li> </ul>                                                                                                                                                                                                                                                                     |  |  |  |

| Timer/counter                                          | Basic interval timer : Watchdog timer applicable     Timer/event counter     Watch timer : Buzzer output enabled     Timer/pulse generator : 14-bit PWM output enabled     Event counter                                                                                                                                                                                                                                                                                         |  |  |  |

| Serial interface                                       | 2 channels SBI/3-wire type  3-wire type                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Interrupt                                              | <ul> <li>Multi-interrupt enabled by hardware</li> <li>External interrupt: 3 interrupts</li> <li>Detected edge programmable (with noise remove function)</li> <li>Detected edge programmable</li> <li>External test input: 1 input</li> <li>Rising edge detection</li> <li>Timer/pulse generator</li> <li>Timer/event counter</li> <li>Basic interval timer</li> <li>Serial interface #0</li> <li>Key scan interrupt</li> <li>Clock timer</li> <li>Serial interface #1</li> </ul> |  |  |  |

| System clock oscillator                                | Main system clock : 6.0 MHz, 4.19 MHz     Subsystem clock : 32.768 kHz standard                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Mask option                                            | <ul> <li>High withstand voltage port : Pull-down resistor or open-drain output</li> <li>Ports 4 and 5 : Pull-up resistors</li> <li>Port 7 : Pull-down resistor</li> </ul>                                                                                                                                                                                                                                                                                                        |  |  |  |

| Operating temperature range                            | −40 to +85 °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| Operating voltage                                      | 2.7 to 6.0 V (standby data hold: 2.0 to 6.0 V)                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Package                                                | 94-pin plastic QFP (20 × 20 mm)                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

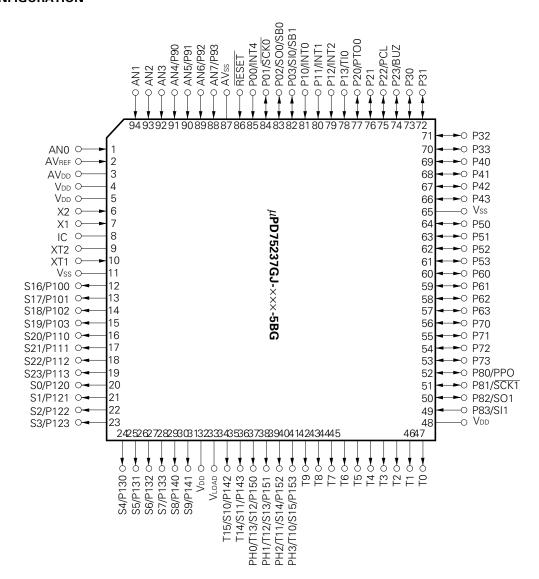

#### **PIN CONFIGURATION**

Note Be sure to supply power to AVDD, VDD, Vss and AVss pins (pin Nos. 3, 4, 5, 11, 30, 48, 65 and 87).

Remarks Connect the IC (Internally Connected) pin to GND.

# **CONTENTS**

| 1. | PIN      | FUNCTIONS                                               | 7     |

|----|----------|---------------------------------------------------------|-------|

|    | 1.1      | PORT PINS                                               | 7     |

|    | 1.2      | NON-PORT PINS                                           | g     |

|    | 1.3      | PIN INPUT/OUPUT CIRCUIT LIST                            | 11    |

|    | 1.4      | RECOMMENDED CONNECTIONS OF $\mu$ PD75237 UNUSED PINS    | 15    |

| 2. | $\mu$ PD | 75237 ARCHITECTURE AND MEMORY MAP                       | . 16  |

|    | 2.1      | DATA MEMORY BANK CONFIGURATION AND ADDRESSING MODE      | 16    |

|    | 2.2      | GENERAL REGISTER BANK CONFIGURATION                     | 19    |

|    | 2.3      | MEMORY MAPPED I/O                                       | 22    |

| 3. | INTE     | ERNAL CPU FUNCTIONS                                     | 28    |

|    | 3.1      | PROGRAM COUNTER (PC): 15 BITS                           | 28    |

|    | 3.2      | PROGRAM MEMORY (ROM): 24448 WORDS × 8 BITS              | 28    |

|    | 3.3      | DATA MEMORY                                             | 30    |

|    | 3.4      | GENERAL REGISTER: 8 × 4 BITS × 4 BANKS                  | 32    |

|    | 3.5      | ACCUMULATOR                                             | 33    |

|    | 3.6      | STACK POINTER (SP) AND STACK BANK SELECT REGISTER (SBS) | 33    |

|    | 3.7      | PROGRAM STATUS WORD (PSW): 8 BITS                       | 36    |

|    | 3.8      | BANK SELECT REGISTER (BS)                               | 40    |

| 4. | PER      | IPHERAL HARDWARE FUNCTIONS                              | . 41  |

|    | 4.1      | DIGITAL INPUT/OUTPUT PORTS                              | 41    |

|    | 4.2      | CLOCK GENERATOR                                         | 50    |

|    | 4.3      | CLOCK OUTPUT CIRCUIT                                    | 58    |

|    | 4.4      | BASIC INTERVAL TIMER                                    | 61    |

|    | 4.5      | TIMER/EVENT COUNTER                                     | 63    |

|    | 4.6      | WATCH TIMER                                             | 69    |

|    | 4.7      | TIMER/PULSE GENERATOR                                   | 71    |

|    | 4.8      | EVENT COUNTER                                           | 77    |

|    | 4.9      | SERIAL INTERFACE                                        | 79    |

|    | 4.10     | A/D CONVERTER                                           | . 113 |

|    | 4.11     | BIT SEQUENTIAL BUFFER: 16 BITS                          | . 119 |

|    | 4.12     | FIP CONTROLLER/DRIVER                                   |       |

| 5. | INTE     | ERRUPT FUNCTIONS                                        |       |

|    | 5.1      | INTERRUPT CONTROL CIRCUIT CONFIGURATION                 | . 131 |

|    | 5.2      | INTERRUPT CONTROL CIRCUIT HARDWARE DEVICES              | 133   |

|    | 5.3      | INTERRUPT SEQUENCE                                      | 138   |

|    | 5.4      | MULTI-INTERRUPT SERVICE CONTROL                         | 139   |

|    | 5.5      | VECTOR ADDRESS SHARING INTERRUPT SERVICING              | . 141 |

| 6. | STA      | NDBY FUNCTIONS                                          | 142   |

|    | 6.1      | STANDBY MODE SETTING AND OPERATING STATE                | 142   |

|    | 6.2      | STANDBY MODE RELEASE                                    | 144   |

|    | 6.3      | OPERATION AFTER STANDBY MODE RELEASE                    | 146   |

|    |          |                                                         |       |

|   | 7.  | RESET FUNCTIONS                                          | 147   |

|---|-----|----------------------------------------------------------|-------|

|   | 8.  | INSTRUCTION SET                                          | . 150 |

|   | 9.  | MASK OPTION SELECTION                                    | 168   |

|   | 10. | APPLICATION BLOCK DIAGRAM                                | 169   |

|   | 11. | ELECTRICAL SPECIFICATIONS                                | 170   |

| τ | 12. | CHARACTERISTIC CURVES (REFERENCE VALUES)                 | 183   |

|   | 13. | PACKAGE INFORMATION                                      | 185   |

|   | 14. | RECOMMEDED SOLDERING CONDITIONS                          | 186   |

|   | API | PENDIX A. LIST OF $\mu$ PD75238 SERIES PRODUCT FUNCTIONS | 187   |

|   | ΔΡΙ | PENDLY B DEVELOPMENT TOOLS                               | 199   |

# 1. PIN FUNCTIONS

# 1.1 PORT PINS (1/2)

| Pin Name                 | I/O                   | Dual-<br>Function Pin | Function                                                                                                                                                                                                                                                                                                                  |                      | 8-Bit<br>I/O                                                                             | After Reset                                                                              | Input / Output<br>Circuit Type *1 |

|--------------------------|-----------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------|

| P00                      |                       | INT4                  |                                                                                                                                                                                                                                                                                                                           |                      | 1,0                                                                                      |                                                                                          | В                                 |

| P01                      |                       | SCK0                  | 4-bit input port (PORT0).                                                                                                                                                                                                                                                                                                 |                      |                                                                                          | Input                                                                                    | (F) – A                           |

| P02                      | Input                 | SO0/SB0               | Built-in pull-up resistor can be                                                                                                                                                                                                                                                                                          | •                    | ×                                                                                        |                                                                                          | F) – B                            |

| P03                      |                       | SI0/SB1               | units by software for P01 to P                                                                                                                                                                                                                                                                                            | 03.                  |                                                                                          |                                                                                          | M – C                             |

| P10                      |                       | INT0                  |                                                                                                                                                                                                                                                                                                                           | Noise removing       |                                                                                          |                                                                                          | 0                                 |

| P11                      |                       | INT1                  |                                                                                                                                                                                                                                                                                                                           | function available   |                                                                                          |                                                                                          |                                   |

| P12                      | Input                 | INT2                  | 4-bit input port (PORT1).  Built-in pull-up resistor can b                                                                                                                                                                                                                                                                | e specified in 4-hit | ×                                                                                        | Input                                                                                    | B – C                             |

| P13                      |                       | TIO                   | units by software.                                                                                                                                                                                                                                                                                                        | o opcomed in 1 bit   |                                                                                          |                                                                                          |                                   |

| P20                      |                       | PTO0                  |                                                                                                                                                                                                                                                                                                                           |                      |                                                                                          |                                                                                          |                                   |

| P21                      | Input/                | _                     | 4-bit input/ output port (PORT2                                                                                                                                                                                                                                                                                           |                      |                                                                                          |                                                                                          |                                   |

| P22                      | output                | PCL                   | Built-in pull-up resistor can be specified in 4-bit units by software.                                                                                                                                                                                                                                                    | ×                    | Input                                                                                    | E – B                                                                                    |                                   |

| P23                      |                       | BUZ                   | ante by contrare.                                                                                                                                                                                                                                                                                                         |                      |                                                                                          |                                                                                          |                                   |

| P30 *2                   |                       | _                     |                                                                                                                                                                                                                                                                                                                           |                      |                                                                                          |                                                                                          |                                   |

| P31 * <b>2</b>           | Input/                | _                     | Programmable 4-bit input/ output port (PORT3). Input/ output specifiable in 1-bit units. Built-in pull-up resistor can be specified in 4-bit units by software.                                                                                                                                                           |                      |                                                                                          | Input                                                                                    | E – C                             |

| P32 *2                   | output                | _                     |                                                                                                                                                                                                                                                                                                                           |                      | ×                                                                                        |                                                                                          |                                   |

| P33 *2                   |                       | _                     |                                                                                                                                                                                                                                                                                                                           |                      |                                                                                          |                                                                                          |                                   |

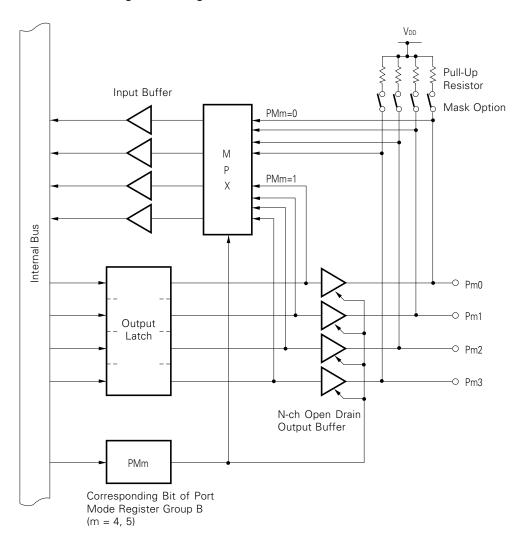

| *2<br>P40 to P43         | Input/<br>output      | _                     | N-ch open-drain 4-bit input/output port (PORT4). Pull-up resistor can be incorporated in 1-bit units (mask option). 10 V withstand voltage with open drain.  N-ch open-drain 4-bit input/ output port (PORT5). Pull-up resistor can be incorporated in 1-bit units (mask option). 10 V withstand voltage with open drain. |                      | High level<br>(when a pull-<br>up resistor is<br>incorporated)<br>or high im-<br>pedance | М                                                                                        |                                   |

| * <b>2</b><br>P50 to P53 | Input/<br>output      | _                     |                                                                                                                                                                                                                                                                                                                           |                      | 0                                                                                        | High level<br>(when a pull-<br>up resistor is<br>incorporated)<br>or high im-<br>pedance | M                                 |

| P60                      |                       |                       | Programmable 4-bit input/out                                                                                                                                                                                                                                                                                              | put port (PORT6).    |                                                                                          |                                                                                          |                                   |

| P61                      | Input/                | _                     | Input/output specifiable in 1-b                                                                                                                                                                                                                                                                                           |                      |                                                                                          | Input                                                                                    | F 6                               |

| P62                      | output                | _                     | Built -in pull-up resistor can bunits by software.                                                                                                                                                                                                                                                                        | e specified in 4-bit |                                                                                          | прис                                                                                     | E – C                             |

| P63                      |                       | _                     | units by software.                                                                                                                                                                                                                                                                                                        |                      |                                                                                          |                                                                                          |                                   |

| P70                      |                       | _                     |                                                                                                                                                                                                                                                                                                                           |                      | ]                                                                                        | Vss level                                                                                |                                   |

| P71                      | P71 Input/ P72 output |                       | 4-bit input/output port (PORT7).  Built-in pull-down resistor can be incorporated in                                                                                                                                                                                                                                      |                      |                                                                                          | (when a pull-<br>down resistor                                                           | V                                 |

| P72                      |                       |                       | 1-bit units (mask option).                                                                                                                                                                                                                                                                                                | 20 moorporated m     |                                                                                          | is incorpo-<br>rated) or high                                                            | , v                               |

| P73                      |                       | _                     |                                                                                                                                                                                                                                                                                                                           |                      |                                                                                          | impedance                                                                                |                                   |

- \* 1. Schmitt trigger inputs are circled.

- 2. Can drive LED directly.

## 1.1 PORT PINS (2/2)

| Pin Name | I/O              | Dual-<br>Function Pin | Function                                                                                         | 8-Bit<br>I/O | After Reset                                                                                                                                                                              | Input / Output<br>Circuit Type * |

|----------|------------------|-----------------------|--------------------------------------------------------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| P80      | Input/<br>output | PPO                   |                                                                                                  |              |                                                                                                                                                                                          | А                                |

| P81      | Input/<br>output | SCK1                  | 4-bit input port (PORT8).                                                                        | ×            | Input                                                                                                                                                                                    | F                                |

| P82      | Input/<br>output | SO1                   |                                                                                                  |              |                                                                                                                                                                                          | E                                |

| P83      | Input            | SI1                   |                                                                                                  |              |                                                                                                                                                                                          | B                                |

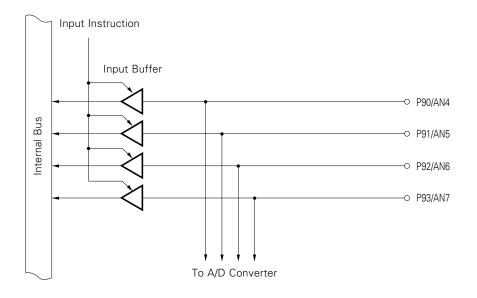

| P90      |                  | AN4                   |                                                                                                  |              |                                                                                                                                                                                          |                                  |

| P91      | Innut            | AN5                   | ALVI (DODTO)                                                                                     |              |                                                                                                                                                                                          | \ \ \ \ \ \                      |

| P92      | Input            | AN6                   | 4-bit input port (PORT9).                                                                        | ×            | Input                                                                                                                                                                                    | Y – A                            |

| P93      |                  | AN7                   |                                                                                                  |              |                                                                                                                                                                                          |                                  |

| P100     |                  | S16                   |                                                                                                  |              |                                                                                                                                                                                          |                                  |

| P101     | 1                | S17                   | P-ch open-drain 4-bit high-voltage output port.                                                  |              | VLOAD level<br>(when a pull-<br>down resistor<br>to VLOAD is in-<br>corporated),<br>Vss level<br>(when a pull-<br>down resistor<br>to Vssis incor-<br>porated) or<br>high imped-<br>ance |                                  |

| P102     | Output           | S18                   | Pull-down resistor can be incorporated (mask op-                                                 |              |                                                                                                                                                                                          |                                  |

| P103     | 1                | S19                   | tion).                                                                                           |              |                                                                                                                                                                                          |                                  |

| P110     |                  | S20                   |                                                                                                  |              |                                                                                                                                                                                          | I – F                            |

| P111     |                  | S21                   | P-ch open-drain 4-bit high-voltage output port.                                                  |              |                                                                                                                                                                                          |                                  |

| P112     | Output           | S22                   | Pull-down resistor can be incorporated (mask option).                                            |              |                                                                                                                                                                                          |                                  |

| P113     | 1                | S23                   |                                                                                                  |              |                                                                                                                                                                                          |                                  |

| P120     |                  | S0                    |                                                                                                  |              |                                                                                                                                                                                          |                                  |

| P121     |                  | S1                    | P-ch open-drain 4-bit high-voltage output port.                                                  |              |                                                                                                                                                                                          |                                  |

| P122     | Output           | S2                    | Pull-down resistor can be incorporated (mask option).                                            |              |                                                                                                                                                                                          |                                  |

| P123     | -                | S3                    | tion).                                                                                           |              |                                                                                                                                                                                          |                                  |

| P130     |                  | S4                    |                                                                                                  |              |                                                                                                                                                                                          |                                  |

| P131     |                  | S5                    | P-ch open-drain 4-bit high-voltage output port.                                                  |              |                                                                                                                                                                                          |                                  |

| P132     | Output           | S6                    | Pull-down resistor can be incorporated (mask option).                                            |              |                                                                                                                                                                                          |                                  |

| P133     | 1                | S7                    |                                                                                                  |              |                                                                                                                                                                                          |                                  |

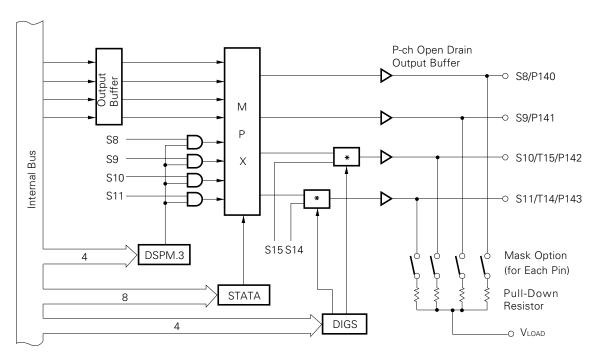

| P140     |                  | S8                    |                                                                                                  |              | VLOAD level<br>(when a pull-                                                                                                                                                             |                                  |

| P141     | 1                | S9                    | P-ch open-drain 4-bit high-voltage output port. Pull-down resistor can be incorporated (mask op- |              | down resistor<br>to VLOAD is in-                                                                                                                                                         | I – C                            |

| P142     | Output           | S10/T15               | tion).                                                                                           |              | corporated) or high imped-<br>ance                                                                                                                                                       |                                  |

| P143     | 1                | S11/T14               | P142 and P143 can drive LED directly.                                                            |              | ance                                                                                                                                                                                     |                                  |

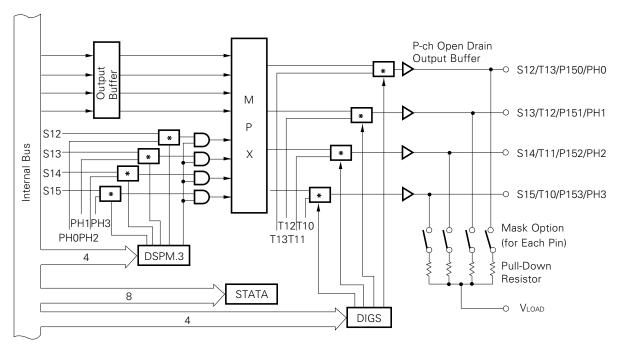

| P150     |                  | S12/T13/PH0           | P-ch open-drain 4-bit high-voltage output port.                                                  |              |                                                                                                                                                                                          |                                  |

| P151     | 1                | S13/T12/PH1           | Pull-down resistor can be incorporated (mask op-                                                 |              |                                                                                                                                                                                          |                                  |

| P152     | Output           | S14/T11/PH2           | tion).                                                                                           |              |                                                                                                                                                                                          |                                  |

| P153     |                  | S15/T10/PH3           | These ports can drive LED directly.                                                              |              |                                                                                                                                                                                          |                                  |

| PH0      |                  | S12/T13/P150          |                                                                                                  |              |                                                                                                                                                                                          |                                  |

| PH1      | 1_               | S13/T12/P151          | P-ch open-drain 4-bit high-voltage output port.                                                  |              |                                                                                                                                                                                          |                                  |

| PH2      | Output           | S14/T11/P152          | Pull-down resistor can be incorporated (mask option).                                            | ×            |                                                                                                                                                                                          |                                  |

| PH3      | 1                | S15/T10/P153          | don,                                                                                             |              |                                                                                                                                                                                          |                                  |

<sup>\*</sup> Schmitt trigger inputs are circled.

## 1.2 NON-PORT PINS (1/2)

| Pin Name              | I/O              | Dual-<br>Function Pin   |                                                                                                                                                                                                                | Function                                                                                                                                                        | After Reset                                                                                      | Input / Output<br>Circuit Type *                                                                 |  |

|-----------------------|------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|

| T0 to T9              |                  | _                       |                                                                                                                                                                                                                | Digit output high-voltage high-<br>current output pins.                                                                                                         |                                                                                                  |                                                                                                  |  |

| T10/S15 to<br>T13/S12 |                  | PH3/P153 to<br>PH0/P150 |                                                                                                                                                                                                                | Digit/segment output dual-function high-voltage high-current output pins. Extra pins can be used as PORTH. These pins can be used as PORT15 in the static mode. | V <sub>LOAD</sub> level<br>(when a                                                               |                                                                                                  |  |

| T14/S11               |                  | P143                    |                                                                                                                                                                                                                | Digit/segment output dual-function high-voltage high-current                                                                                                    | pull-down<br>resistor to<br>VLOAD is in-                                                         | I – C                                                                                            |  |

| T15/S10               |                  | P142                    |                                                                                                                                                                                                                | output pins. These pins can be used as POTR14 in the static mode.                                                                                               | corpo-<br>rated) or<br>high im-<br>pedance.                                                      | . 9                                                                                              |  |

| S0 to S3              |                  | P120 to<br>P123         | FIP controller/driver out-<br>put pins.<br>Pull-down resistor can                                                                                                                                              | Segment high-voltage output pins.                                                                                                                               |                                                                                                  |                                                                                                  |  |

| S4 to S7              | Output           | P130 to<br>P133         | be incorporated in bit units (mask option).  These pins can be used as PORT12 to PORT14 in the static mode.  Segment high-voltage output pins. These pins can be used as PORT10 and PORT11 in the static mode. | These pins can be used as                                                                                                                                       |                                                                                                  |                                                                                                  |  |

| S8                    |                  | P140                    |                                                                                                                                                                                                                |                                                                                                                                                                 | İ                                                                                                |                                                                                                  |  |

| S9                    |                  | P141                    |                                                                                                                                                                                                                |                                                                                                                                                                 |                                                                                                  |                                                                                                  |  |

| S16 to S19            |                  | P100 to<br>P103         |                                                                                                                                                                                                                | Segment high-voltage out                                                                                                                                        |                                                                                                  | VLOAD level<br>(when a<br>pull-down<br>resistor to<br>VLOAD is in-<br>c o r p o -<br>rated), Vss |  |

| S20 to S23            |                  | P110 to<br>P113         |                                                                                                                                                                                                                | PORT10 and PORT11 in the static                                                                                                                                 | level (when<br>a pull-down<br>resistor to<br>Vss is incor-<br>porated) or<br>high im-<br>pedance | I – F                                                                                            |  |

| TIO                   | Input            | P13                     | External event pulse inp event counter #1.                                                                                                                                                                     | ut to timer/event counter #0 and                                                                                                                                | _                                                                                                | <b>B</b> – C                                                                                     |  |

| PTO0                  | Output           | P20                     | Timer/event counter output.                                                                                                                                                                                    |                                                                                                                                                                 | Input                                                                                            | E – B                                                                                            |  |

| PCL                   | Output           | P22                     | Clock output.                                                                                                                                                                                                  |                                                                                                                                                                 | Input                                                                                            | E – B                                                                                            |  |

| BUZ                   | Output           | P23                     | Fixed frequency output (for buzzer or system clock trimming).                                                                                                                                                  |                                                                                                                                                                 | Input                                                                                            | E – B                                                                                            |  |

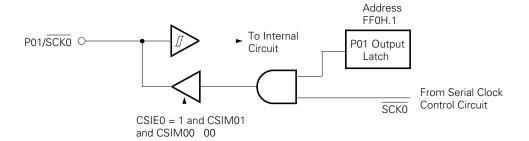

| SCK0                  | Input/<br>output | P01                     | Serial clock input/output.                                                                                                                                                                                     |                                                                                                                                                                 | Input                                                                                            | (F) – A                                                                                          |  |

| SO0/SB0               | Input/<br>output | P02                     | Serial data output. Serial bus input/output.                                                                                                                                                                   |                                                                                                                                                                 | Input                                                                                            | (F) – B                                                                                          |  |

| SI0/SB1               | Input/<br>output | P03                     | Serial data input. Serial bus input/output.                                                                                                                                                                    |                                                                                                                                                                 | Input                                                                                            | M – C                                                                                            |  |

<sup>\*</sup> Schmitt trigger inputs are circled.

## 1.2 NON-PORT PINS (2/2)

| Pin Name                  | I/O              | Dual-<br>Function Pin | Function                                                                                                                          |                            | After Reset | Input / Output<br>Circuit Type * |

|---------------------------|------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------|----------------------------------|

| INT4                      | Input            | P00                   | Edge-detected vectored interrupt inpution of rising and falling edges).                                                           | t (valid for detec-        | _           | B                                |

| INT0                      | Input            | P10                   | Edge-detected vectored interrupt in-                                                                                              | Clocked                    |             | (B) – C                          |

| INT1                      | mput             | P11                   | put (detected edge selection possible).                                                                                           | Asynchronous               |             | <u> </u>                         |

| INT2                      | Input            | P12                   | Edge-detected testable input (rising edge detection).                                                                             | Asynchronous               | _           | B – C                            |

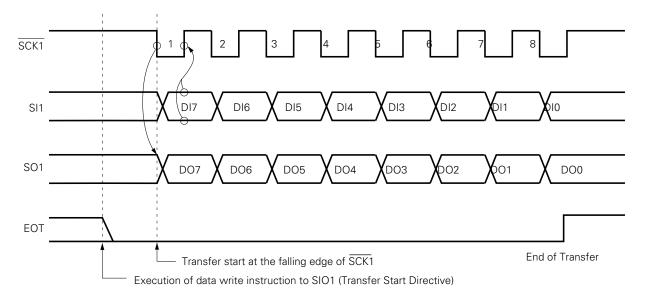

| SCK1                      | Input/<br>output | P81                   | Serial clock input/output.                                                                                                        | Serial clock input/output. |             | Ē                                |

| SO1                       | Output           | P82                   | Serial data output.                                                                                                               |                            | Input       | E                                |

| SI1                       | Input            | P83                   | Serial data input.                                                                                                                |                            | Input       | B                                |

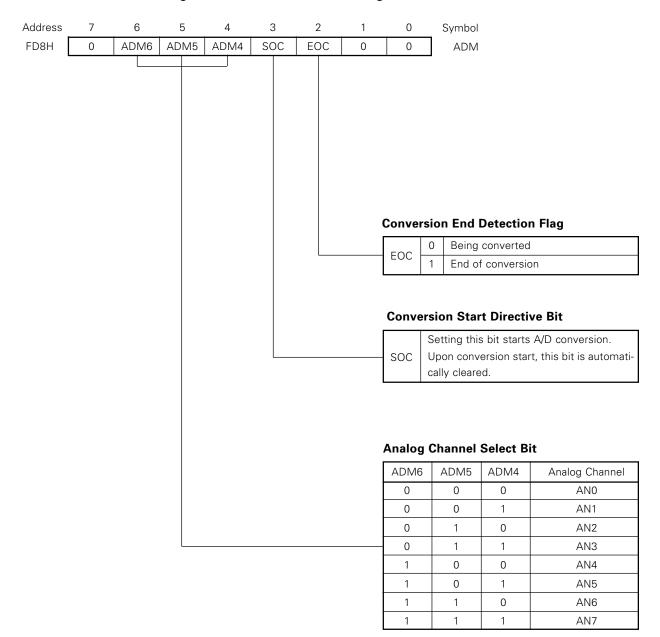

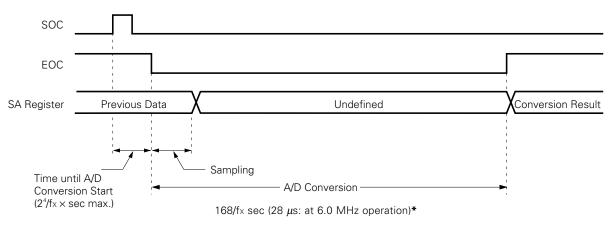

| AN0 to AN3                |                  | _                     | Analog input to A/D converter.                                                                                                    |                            |             | Y                                |

| AN4 to AN7                | Input            | P90 to P93            |                                                                                                                                   |                            | _           | Y – A                            |

| AV <sub>DD</sub>          | _                | _                     | A/D converter power supply.                                                                                                       |                            | _           | _                                |

| AVref                     | Input            | _                     | A/D converter reference voltage input.                                                                                            |                            | _           | Z                                |

| AVss                      | _                | _                     | A/D converter reference GND potential                                                                                             |                            | _           | _                                |

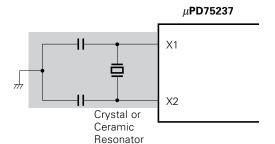

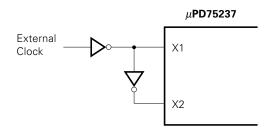

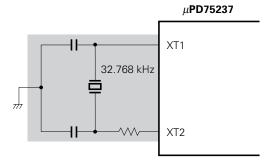

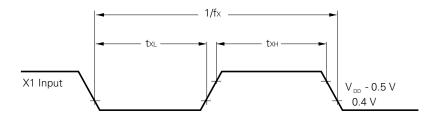

| X1, X2                    | Input            | _                     | Main system clock oscillation crystal/ceramic connection. An external clock is input to X1 and an antiphase clock is input to X2. |                            | _           | _                                |

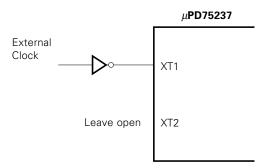

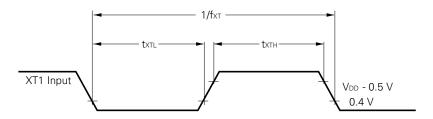

| XT1                       | Input            |                       | Subsystem clock oscillation crystal conr                                                                                          | nection. An exter-         |             |                                  |

| XT2                       |                  |                       | nal clock is input to XT1 and XT2 is made open.                                                                                   |                            |             |                                  |

| RESET                     | Input            |                       | System reset input.                                                                                                               |                            | _           | B                                |

| PPO                       | Output           | P80                   | Timer/pulse generator pulse output.                                                                                               |                            | Input       | _                                |

| V <sub>DD</sub> (3 – Pin) | _                |                       | Positive power supply.                                                                                                            |                            |             |                                  |

| Vss (2 – Pin)             | _                | _                     | GND potential.                                                                                                                    |                            | _           | _                                |

| VLOAD                     | _                | _                     | FIP controller/driver pull-down resistor connect/power supply.                                                                    |                            | _           | _                                |

<sup>\*</sup> Schmitt trigger inputs are circled.

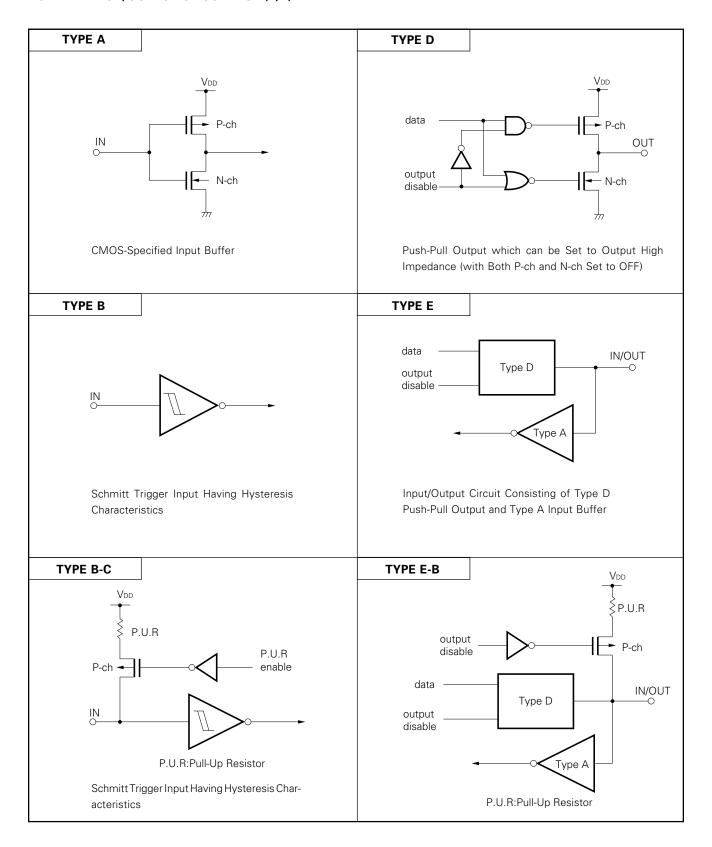

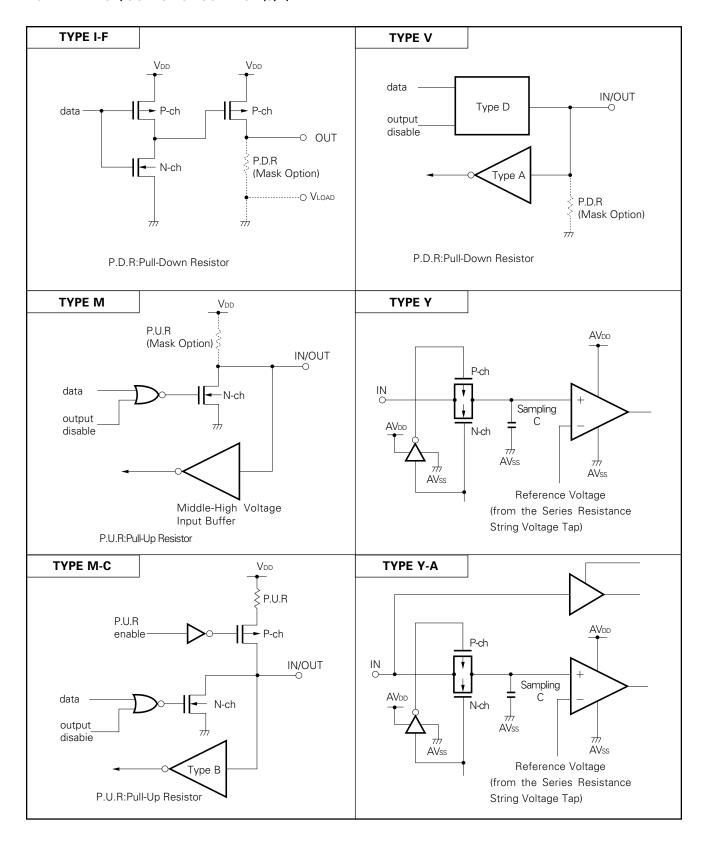

## 1.3 PIN INPUT/OUTPUT CIRCUIT LIST (1/4)

## 1.3 PIN INPUT/OUTPUT CIRCUIT LIST (2/4)

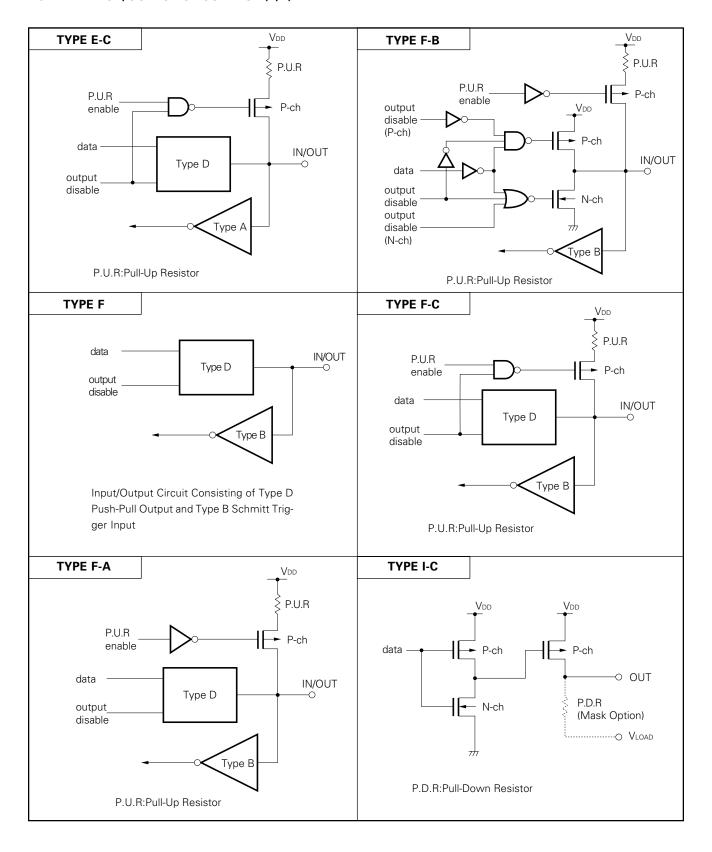

## 1.3 PIN INPUT/OUTPUT CIRCUIT LIST (3/4)

# 1.3 PIN INPUT/OUTPUT CIRCUIT LIST (4/4)

# 1.4 RECOMMENDED CONNECTIONS OF $\mu$ PD75237 UNUSED PINS

| Pin                  | Recommended Connection              |  |

|----------------------|-------------------------------------|--|

| P00/INT4             | Connect to Vss                      |  |

| P01/SCK0             |                                     |  |

| P02/SO0/SB0          | Connect to Vss or VDD               |  |

| P03/SI1/SB1          |                                     |  |

| P10/INT0 to P12/INT2 | Commontate V                        |  |

| P13/TI0              | Connect to Vss                      |  |

| P20/PTO0             |                                     |  |

| P21                  |                                     |  |

| P22/PCL              |                                     |  |

| P23/BUZ              | Input state : Connect to Vss or VDD |  |

| P30 to P33           |                                     |  |

| P40 to P43           | Ouput state : Leave open            |  |

| P50 to P53           |                                     |  |

| P60 to P63           |                                     |  |

| P70 to P73           |                                     |  |

| P80/PPO              |                                     |  |

| P81/SCK1             |                                     |  |

| P82/SO1              | Connect to Vss                      |  |

| P83/SI1              |                                     |  |

| P90/AN4 to P93/AN7   |                                     |  |

| P100/S16 to P103/S19 |                                     |  |

| P110/S20 to P113/S23 |                                     |  |

| P120 to P123         | Leave open                          |  |

| P130 to P133         | Leave open                          |  |

| P140 to P143         |                                     |  |

| P150 to P153         |                                     |  |

| AN0 to AN3           | Connect to Vss                      |  |

| AVREF                |                                     |  |

| AV <sub>DD</sub>     | Connect to VDD                      |  |

| AVss                 | Connect to Vss                      |  |

| XT1                  | Connect to Vss or VDD               |  |

| XT2                  | Leave open                          |  |

| VLOAD                | Connect to Vss                      |  |

## 2. $\mu$ PD75237 ARCHITECTURE AND MEMORY MAP

The  $\mu$ PD75237 has the following three architectural features.

- (a) Data memory bank configuration

- (b) General register bank configuration

- (c) Memory mapped I/O

Each feature is outlined below.

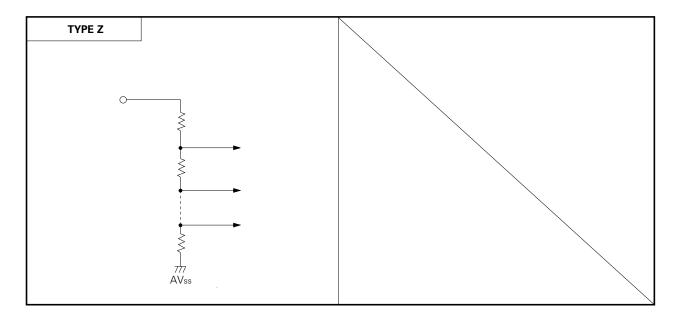

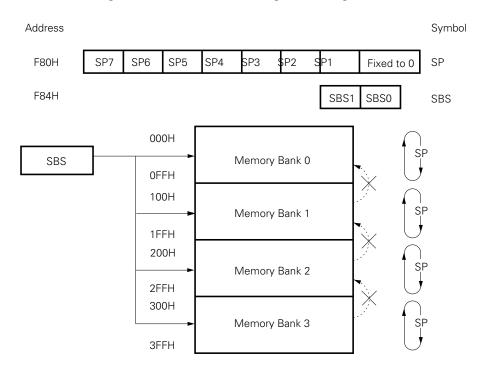

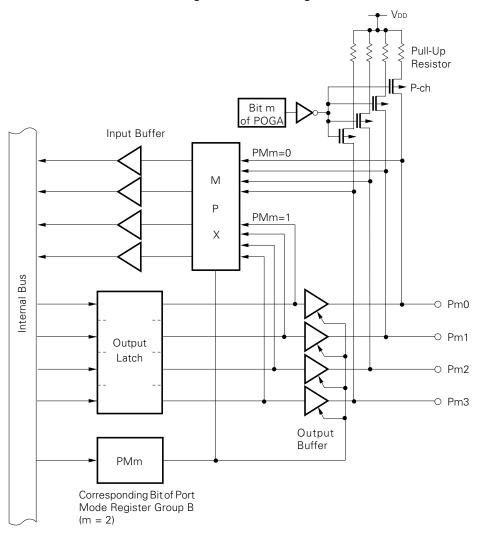

#### 2.1 DATA MEMORY BANK CONFIGURATION AND ADDRESSING MODE

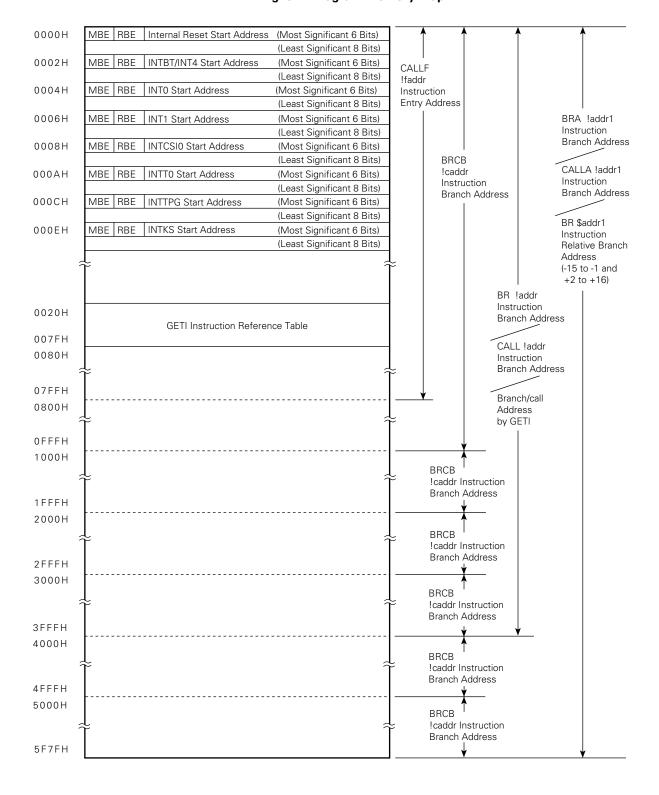

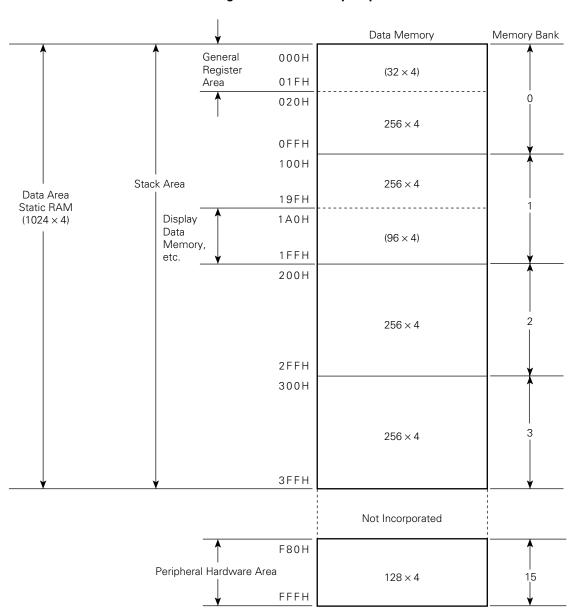

As shown in Fig. 2-1, the  $\mu$ PD75237 incorporates a static RAM (928 words  $\times$  4 bits) at addresses 000H to 19FH and 200H to 3FFH in the data memory space and a display data memory (96 words  $\times$  4 bits) at addresses 1A0H to 1FFH and peripheral hardware (input/output ports, timers, etc.) at addresses F80H to FFFH. For addressing of this 12-bit address data memory space, the memory bank has a configuration wherein the lower 8 bits are directly or indirectly specified by an instruction and the higher 4-bit address is specified by a memory bank (MB).

A memory bank enable flag (MBE) and a memory bank select register (MBS) are incorporated to specify the memory bank (MB) and addressing operations shown in Fig. 2-1 and Table 2-1 can be carried out. (MBS is a register to select the memory bank and can set 0, 1, 2, 3 and 15. MBE is a flag to determine whether the memory bank selected by MBS should be validated or not. Since MBE is automatically saved/reset for interrupt or subroutine processing, it can be freely set for either processing.)

For data memory space addressing, set MBE = 1 normally and manipulate the memory bank static RAM specified by MBS. Efficient programming is possible by using the MBE = 0 or MBE = 1 mode for each program processing.

|              | Applicable Program Processing                                                                                                                                    |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MBE = 0 mode | <ul> <li>Interrupt service</li> <li>Processing of repeating built-in hardware manipulation and static RAM manipulation</li> <li>Subroutine processing</li> </ul> |  |  |

| MBE = 1 mode | Normal program processing                                                                                                                                        |  |  |

Fig. 2-1 Date Memory Configuration and Addressing Range in Each Addressing Mode

Remarks — : Don't care

**Table 2-1 Addressing Modes**

| Addressing Mode                    | Identifier   | Address Specified                                                                                                                                                                                                                 |  |  |

|------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1-bit direct addressing            | mem.bit      | Bit indicated by bit of address indicated by MB and mem, where: $ MBE = 0 \qquad \begin{cases}  When \ mem = 00H \ to \ 7FH, \ MB = 0 \\  When \ mem = 80H \ to \ FFH, \ MB = 15 \\  MBE = 1 \end{cases} $ $ MBE = 1 \qquad MBS $ |  |  |

| 4-bit direct addressing            | mem          | Address indicated by MB and mem, where : $MBE = 0 \qquad \begin{cases} When \ mem = 00H \ to \ 7FH, \ MB = 0 \\ When \ mem = 80H \ to \ FFH, \ MB = 15 \\ MBE = 1 \end{cases}$ $MBE = 1 \qquad MB = MBS$                          |  |  |

| 8-bit direct addressing            | e            | Address indicated by MB and mem (mem is an even address), where: $ MBE = 0 \qquad \begin{cases} When \ mem = 00H \ to \ 7FH, \ MB = 0 \\ When \ mem = 80H \ to \ FFH, \ MB = 15 \\ MBE = 1 \end{cases} $ $ MBE = 1 \qquad MBS $   |  |  |

|                                    | @HL          | Address indicated by MB and HL, where : MB = MBE• MBS                                                                                                                                                                             |  |  |

| 4-bit register indirect            | @HL+ @HL-    | Address indicated by MB and HL, where: MB = MBE• MBS HL+ automatically increments L register after addressing. HL- automatically decrements L register after addressing.                                                          |  |  |

|                                    | @DE          | Address indicated by DE of memory bank 0                                                                                                                                                                                          |  |  |

|                                    | @DL          | Address indicated by DL of memory bank 0                                                                                                                                                                                          |  |  |

| 8-bit register indirect addressing | @HL          | Address indicated by MB and HL, where: MB = MBE• MBS Bit 0 of L register is ignored.                                                                                                                                              |  |  |

|                                    | fmem.bit     | Bit indicated by bit of address indicated by fmem, where:  fmem =   FB0H to FBFH (interrupt-related hardware)  FF0H to FFFH (I/O port)                                                                                            |  |  |

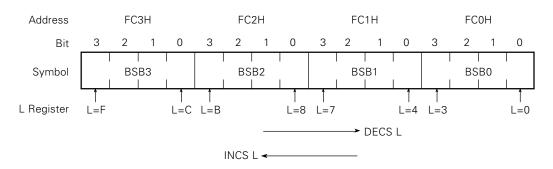

| Bit manipulation addressing        | pmem.@L      | Bit indicated by the lower 2 bits of L register of the address indicated by the higher 10 bits of pmem and the higher 2 bits of L register, where:  pmem = FC0H to FFFH                                                           |  |  |

|                                    | @H + mem.bit | Bit indicated by bit of the address indicated by MB, H and the lower 4 bits of mem, where: MB = MBE• MBS                                                                                                                          |  |  |

| Stack addressing                   |              | Address indicated by SP of memory banks 0, 1, 2 and 3 selected by SBS                                                                                                                                                             |  |  |

As described in Table 2-1, direct and indirect addressing is possible for each of 1-bit, 4-bit and 8-bit data in  $\mu$ PD75237 data memory manipulation. Thus, easy-to-understand programs can be created very efficiently.

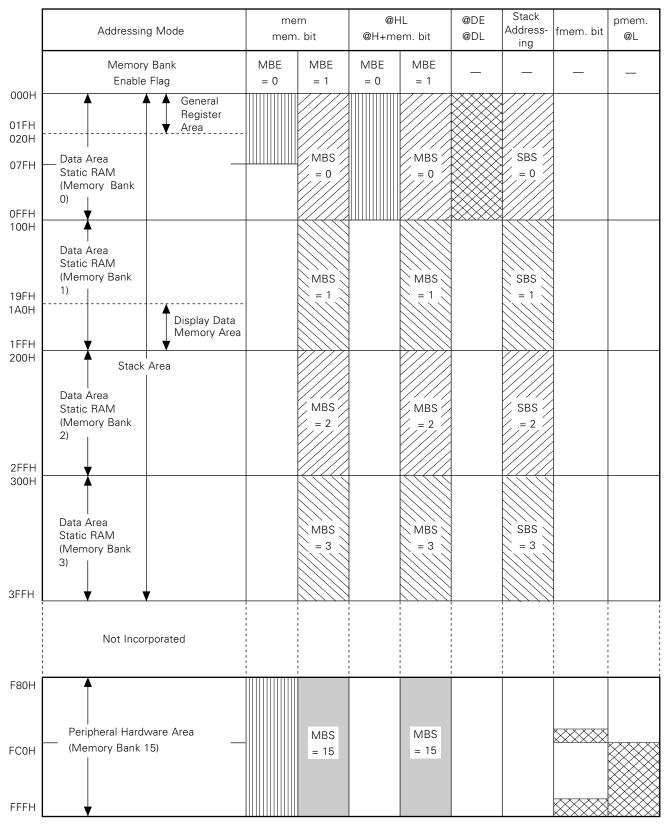

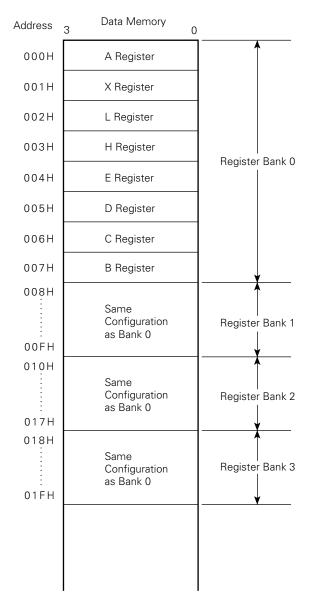

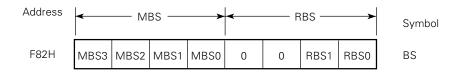

#### 2.2 GENERAL REGISTER BANK CONFIGURATION

The  $\mu$ PD75237 incorporates four register banks, each bank consisting of eight general registers, X, A, B, C, D, E, H and L. This general register area is mapped at addresses 00H to 1FH of the memory bank 0 of the data memory (refer to **Fig. 2-2 General Register Configuration (4-Bit Processing)**). A register bank enable flag (RBE) and a register bank select register (RBS) are incorporated to specify the above general register banks. RBS is a register to select a register bank and RBE is a flag to determine whether the register bank selected by RBS should be validated or not. The register bank (RB) which is validated for instruction execution is given as

RB = RBE• RBS.

As described above, with the  $\mu$ PD75237 having four register banks, programs can be created very efficiently by using different register banks for normal processing and interrupt service as described in Table 2-2. (RBE is automatically saved and set for interrupt service and automatically reset upon termination of the interrupt service.)

Table 2-2 Recommended Use of Register Banks in Normal and Interrupt Routines

| Normal processing                | Use register banks 2 and 3 with RBE = 1.                               |

|----------------------------------|------------------------------------------------------------------------|

| Single interrupt service         | Use register bank 0 with RBE = 0.                                      |

| Double interrupt service         | Use register bank 1 with RBE = 1. (It is necessary to save/reset RBS.) |

| Triple or more interrupt service | Save/reset registers by PUSH and POP.                                  |

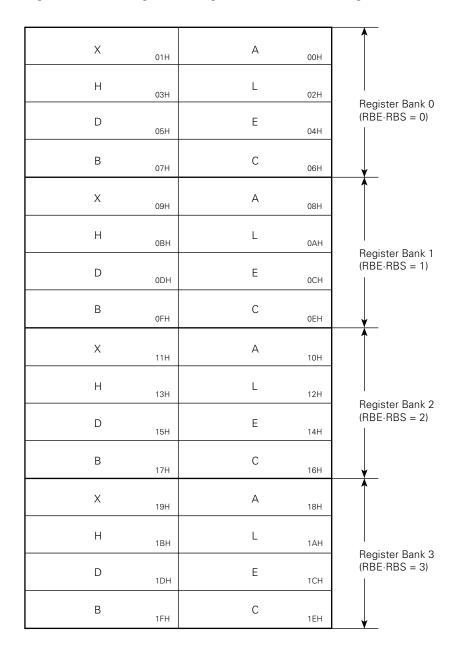

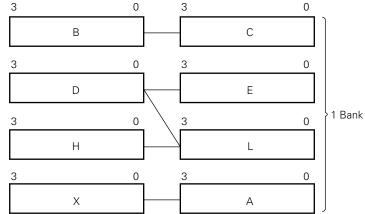

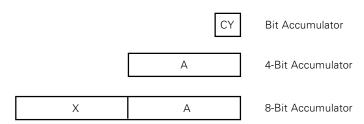

Not only in 4-bit units, a register pair of XA, HL, DE or BC can transfer, compare, operate, increment or decrement data in 8-bit units. In this case, register pairs with the reversed bit 0 of the register bank specified by RBE•RBS can be specified as XA', HL', DE' and BC'. Thus, the  $\mu$ PD75237 has eight 8-bit registers (refer to **Fig. 2-3 General Register Configuration (8-Bit Processing)**).

Fig. 2-2 General Register Configuration (4-Bit Processing)

XA XΑ' 00H 00H HL'  $\mathsf{HL}$ 02H 02H DE DE' 04H 04H ВС BC' 06H 06H When RBE⋅RBS = 0 When  $RBE \cdot RBS = 1$ XA' XA08H 08H HL'  $\mathsf{HL}$ 0AH 0AH DE' DE 0CH 0CH BC' ВС 0EH 0EH XΑ XΑ' 10H 10H HLHL' 12H 12H DE DE' 14H 14H ВС BC' 16H 16H When RBE·RBS = 2 When RBE·RBS = 3 XA'  $\mathsf{X}\mathsf{A}$ 18H 18H HL'  $\mathsf{HL}$ 1AH 1AH DE' DE 1CH 1CH BC' ВС 1EH 1EH

Fig. 2-3 General Register Configuration (8-Bit Processing)

#### 2.3 MEMORY MAPPED I/O

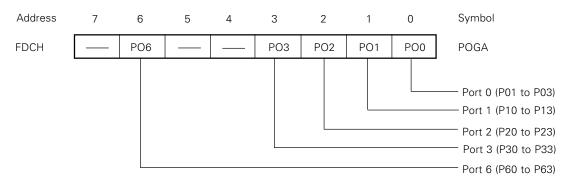

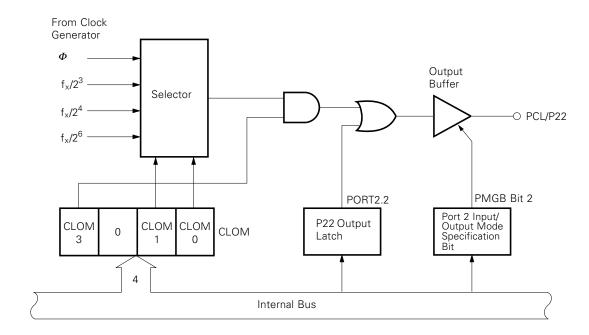

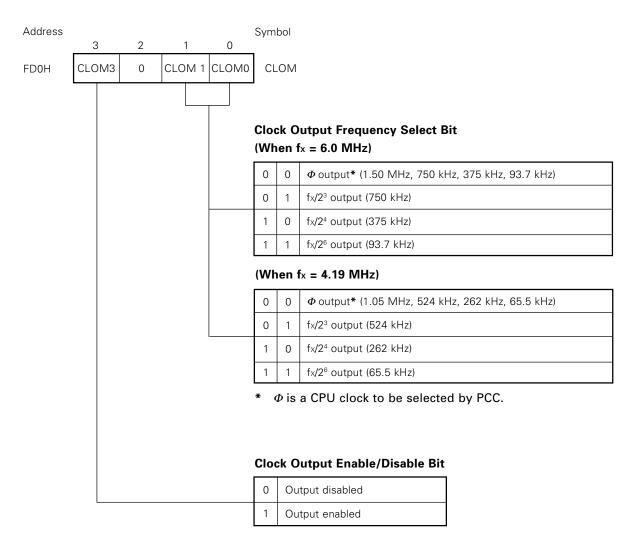

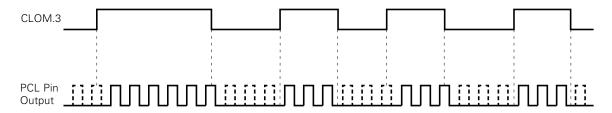

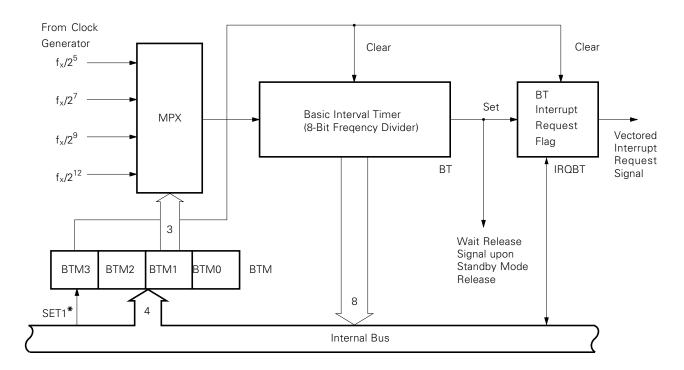

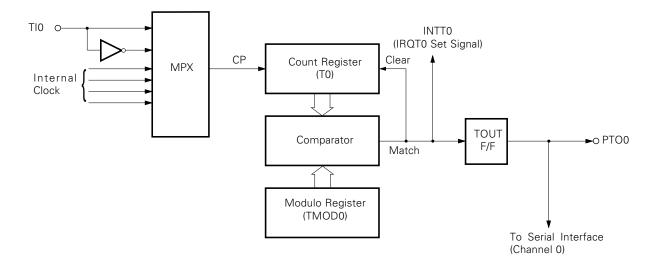

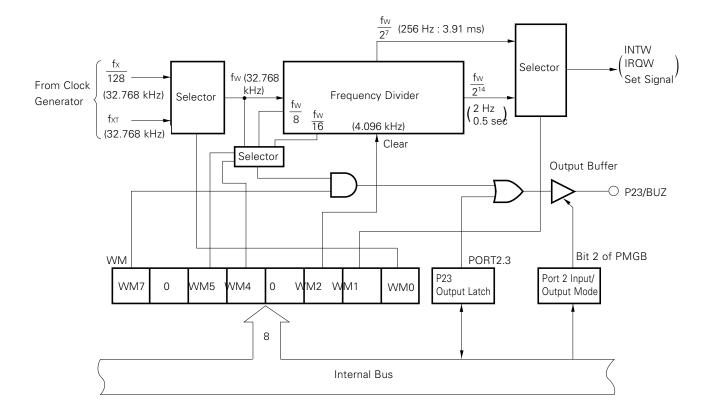

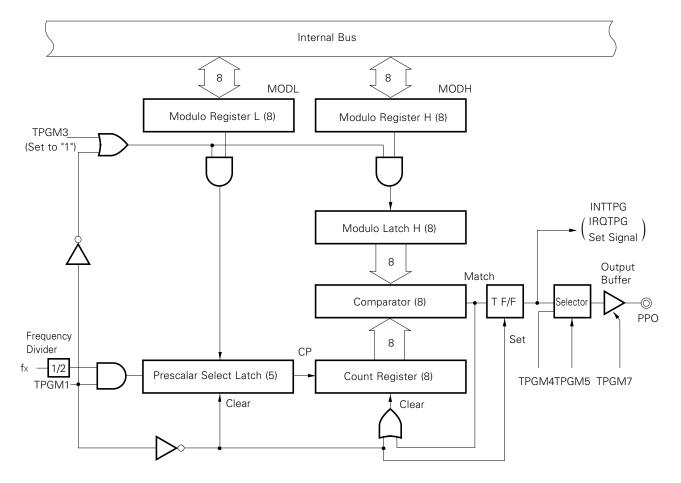

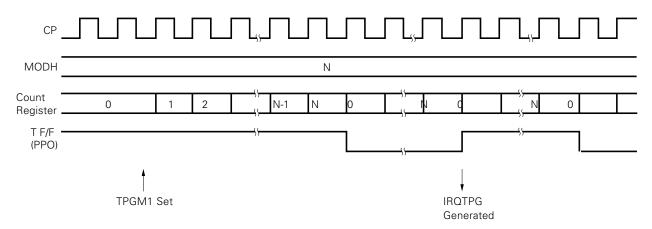

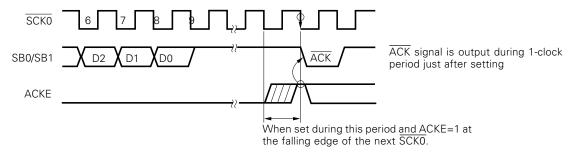

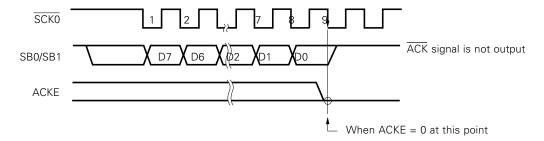

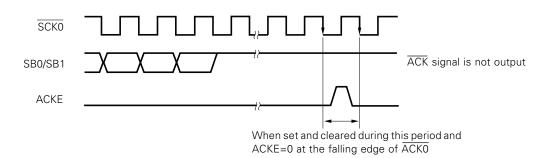

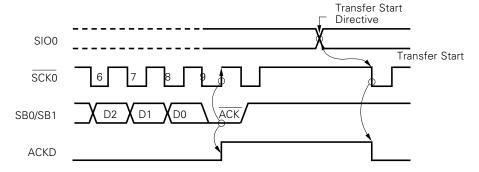

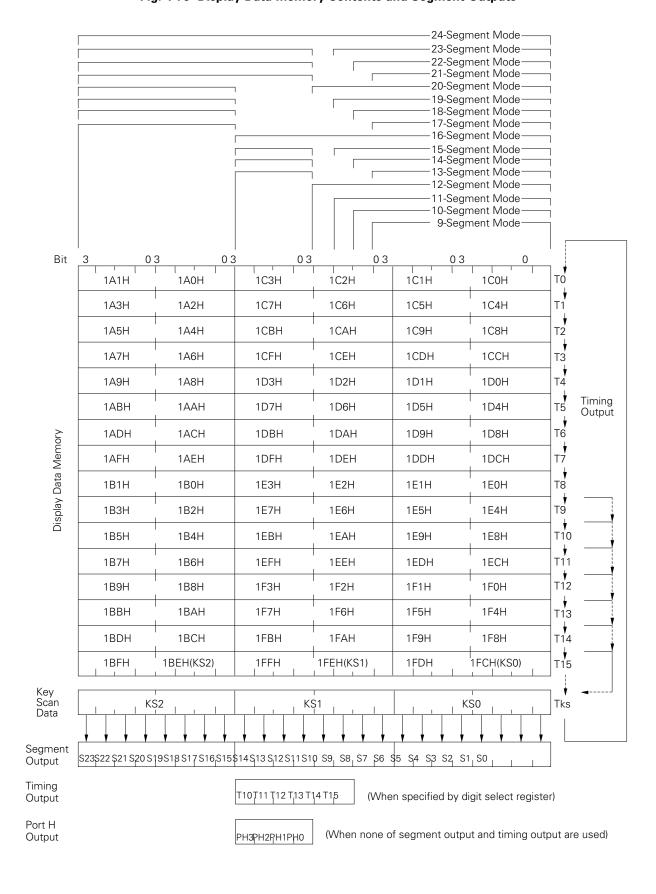

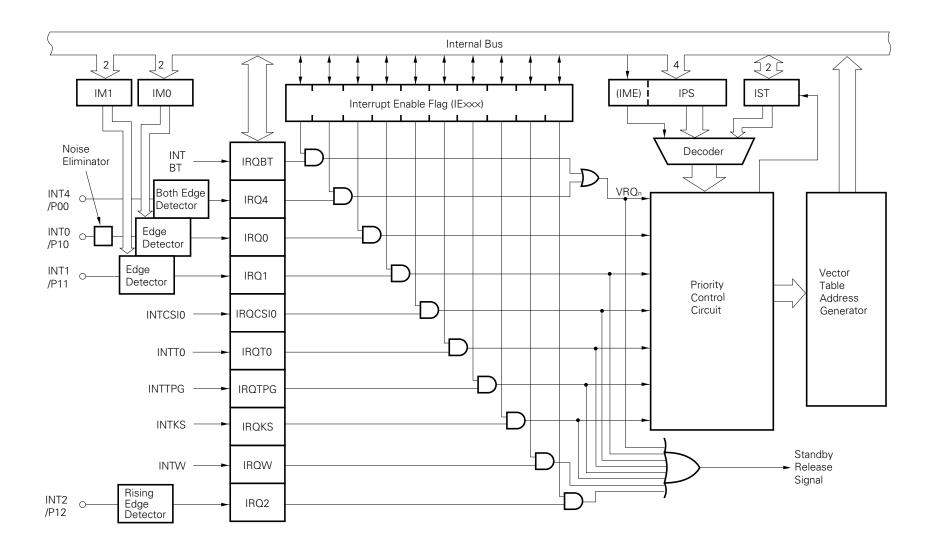

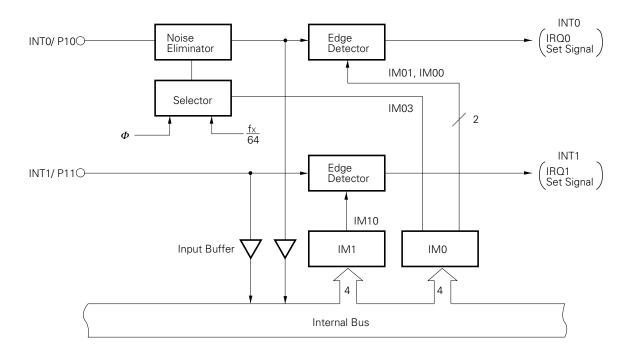

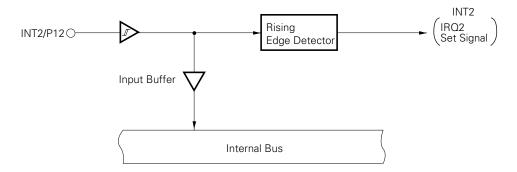

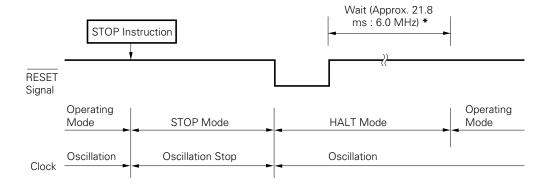

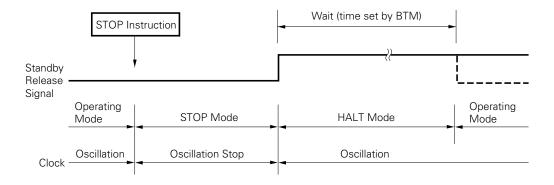

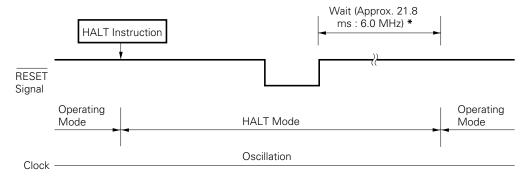

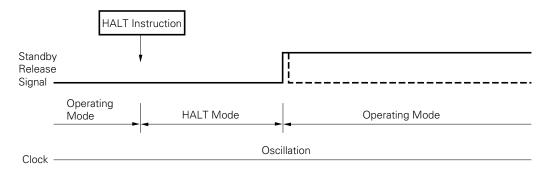

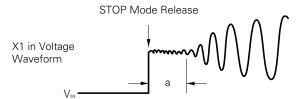

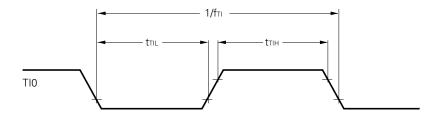

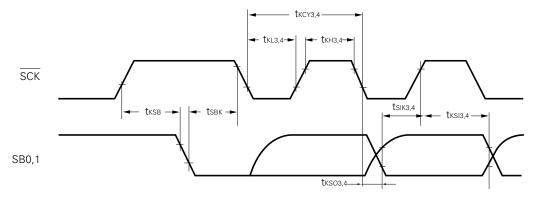

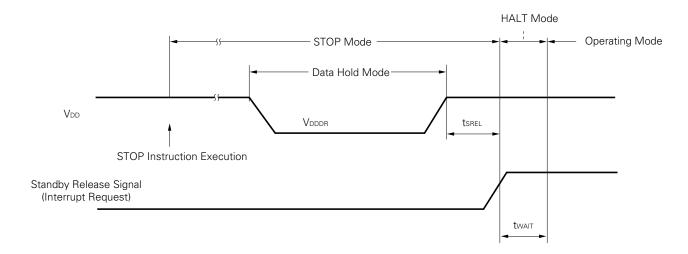

As shown in Fig. 2-1, the  $\mu$ PD75237 employs the memory mapped I/O with the peripheral hardware including input/output ports and timers mapped at addresses F80H to FFFH in the data memory space. Thus, there are no special instructions to control the peripheral hardware and all operations are controlled by memory manipulation instructions. (Some hardware control mnemonics are available to make the program easy to understand.)