# A3965

### DMOS Dual Full-Bridge PWM Motor Driver

| is device ine device | are in production but have been determined to be<br>NEW DESIGN. This classification indicates that sale of<br>is currently restricted to existing customer applications.<br>should not be purchased for new design applications<br>colescence in the near future is probable. Samples are no<br>able. |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ate of state         | us change: November 1, 2004                                                                                                                                                                                                                                                                           |

|                      | ended Substitutions:                                                                                                                                                                                                                                                                                  |

| tting niche          | is a fairly unique device within Allegro's portfolio, typically<br>low-voltage, battery-driven stepper motor applications.<br>recommended alternatives are:                                                                                                                                           |

| • For cust           | tomers looking for a stepper motor driver for battery-driven ions, we recommend the <u>A3977</u> , A3982, A3983, or A3984.                                                                                                                                                                            |

|                      |                                                                                                                                                                                                                                                                                                       |

NOTE: For detailed information on purchasing options, contact your local Allegro field applications engineer or sales representative.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, revisions to the anticipated product life cycle plan for a product to accommodate changes in production capabilities, alternative product availabilities, or market demand. The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

# 3965

PRELIMINARY DATASHEET - 12/4/2002 (Subject to change without notice)

| ABSOLUTE MAXIMUM RATINGS<br>at T <sub>A</sub> = +25°C     |

|-----------------------------------------------------------|

| Load Supply Voltage, VBB                                  |

| Output Current, I <sub>OUT</sub> ±500 mA*                 |

| Logic Supply Voltage, V <sub>DD</sub> <b>7.0</b> V        |

| Logic Input Voltage Range,                                |

| $V_{IN}$                                                  |

| $(t_w < 30 ns)$ 1.0V to $V_{DD}$ +1V                      |

| Sense Voltage, V <sub>SENSE</sub> <b>0.5</b> V            |

| Reference Voltage, $V_{REF}$                              |

| Package Power Dissipation ( $T_A = +25^{\circ}C$ ), $P_D$ |

| A3965SLB <b>50°C/W**</b>                                  |

Operating Temperature Range,

| T <sub>A</sub>                       | -20°C to +85°C |

|--------------------------------------|----------------|

| Junction Temperature, T <sub>J</sub> |                |

| Storage Temperature Range,           |                |

| Т                                    | 55°C to +150°C |

\* Output current rating may be limited by duty cycle, ambient temperature, and heat sinking. Under any set of conditions, do not exceed the specified current rating or a junction temperature of 150°C.

\*Measured with 062" thick FR4, two sided PCB with 1 sq inch copper area.

### DMOS DUAL FULL-BRIDGE PWM MOTOR DRIVER

Designed for Pulse Width Modulated (PWM) current control of low voltage stepper motors, the A3965S is capable of output currents to  $\pm$  500 mA and operating voltages to 20 V.

The A3965 is particularly attractive for low power or battery operated motors where minimal power consumption is desired. A SLEEP mode disables all circuitry and typically draws less than  $1\mu$ A supply current from motor and logic supply. During operation the fixed frequency ON pulses of each H-bridge are 180 degrees out of phase to minimize the peak demand required of the motor supply allowing savings in size and cost of external power supply components.

PHASE and ENABLE input terminals are provided for use in controlling the speed and direction of a stepper motor with externally applied PWM control signals.

Internal circuit protection includes thermal shutdown with hysteresis, undervoltage monitoring of  $V_{DD}$  and charge pump, and crossover current protection. Special power up sequencing is not required.

The A3965 is supplied in a 24-lead plastic SOIC with a copper batwing tab (suffix 'LB').

#### FEATURES

- ±500 mA, 20 V Output Rating

- 2.85 to 5.5V Logic Supply Operation

- Sleep Mode for Minimum Power Consumption

- Fixed Frequency PWM

- Offset On Pulses to Minimize Peak Supply Transient Currents

- Internal UVLO and Thermal Shutdown Circuitry

- Crossover-Current Protection

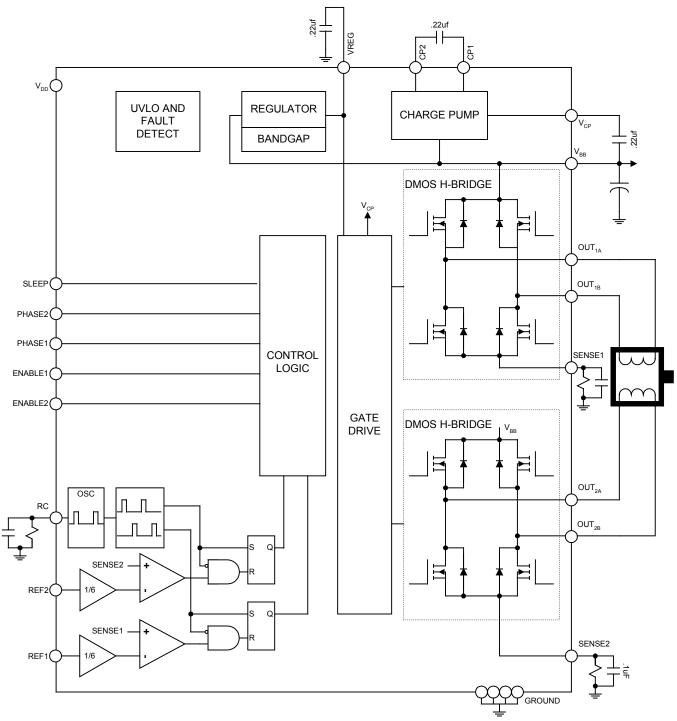

#### **Functional Block Diagram**

### ELECTRICAL CHARACTERISTICS at $T_A = +25^{\circ}$ C, $V_{BB} = 20$ V, $V_{DD} = 3.0$ V, $V_{SENSE} = 0.5$ V, $f_{PWM} < 50$ KHz (unless noted otherwise)

|                            |                                      |                                                   |      | nits  |                  |       |

|----------------------------|--------------------------------------|---------------------------------------------------|------|-------|------------------|-------|

| Characteristics            | aracteristics Symbol Test Conditions |                                                   | Min. | Тур.  | Max.             | Units |

| Output Drivers             |                                      |                                                   |      |       |                  |       |

| Load Supply Voltage Range  | VBB                                  | Operating, $I_{OUT}$ = ±500 mA                    | 6    | _     | 20               | V     |

|                            |                                      | During Sleep Mode                                 | 0    |       | 20               | V     |

| Output Leakage Current     | I <sub>DSS</sub>                     | V <sub>OUT</sub> = V <sub>BB</sub>                | _    | <1.0  | 20               | μA    |

|                            |                                      | V <sub>OUT</sub> = 0 V                            | _    | <-1.0 | -20              | μA    |

| Output On Resistance       | R <sub>DSON</sub>                    | Source Driver, I <sub>OUT</sub> = -500 mA         | _    | 1.2   | 1.35             | Ω     |

|                            |                                      | Sink Driver, I <sub>OUT</sub> = 500 mA            | _    | .75   | .9               | Ω     |

|                            |                                      | Source Driver, I <sub>OUT</sub> = -500 mA; VBB=6V |      | 1.3   | 1.5              | Ω     |

|                            |                                      | Sink Driver, I <sub>OUT</sub> = 500 mA, VBB=6V    |      | .85   | 1.0              | Ω     |

| Body Diode Forward Voltage | V <sub>F</sub>                       | Source Diode, $I_F$ = -500 mA                     | _    | 1     | -                | V     |

|                            |                                      | Sink Diode, $I_F = 500 \text{mA}$                 | _    | 1     | -                | V     |

| Motor Supply Current       | I <sub>BB</sub>                      | f <sub>PWM</sub> < 50 kHz                         | _    | 3.5   | 7                | mA    |

|                            |                                      | Charge Pump On, Outputs Disabled                  | _    | 1.5   | 3                | mA    |

|                            |                                      | Sleep Mode                                        | _    | _     | 10               | uA    |

| Logic Supply Current       | I <sub>DD</sub>                      | f <sub>PWM</sub> < 50 kHz                         |      |       | <mark>4.5</mark> | mA    |

|                            |                                      | Outputs Off                                       |      |       | 3.6              | mA    |

|                            |                                      | Sleep Mode (Inputs below .5V)                     |      | <1    | 10               | μA    |

#### **Control Logic**

| Logic Supply Voltage Range | V <sub>DD</sub>    | Operating             | 2.85                |      | 5.5                 | V  |

|----------------------------|--------------------|-----------------------|---------------------|------|---------------------|----|

| Logic Input Voltage        | V <sub>IN(1)</sub> |                       | V <sub>DD</sub> *.7 | _    |                     | V  |

|                            | V <sub>IN(0)</sub> |                       |                     | -    | V <sub>DD</sub> *.3 | V  |

| Logic Input Current        | I <sub>IN(1)</sub> | $V_{IN} = V_{DD}^*.7$ | -20                 | <1.0 | 20                  | μA |

|                            | I <sub>IN(0)</sub> | $V_{IN} = V_{DD}^*.3$ | -20                 | <1.0 | 20                  | μA |

#### ELECTRICAL CHARACTERISTICS at $T_A = +25^{\circ}$ C, $V_{BB} = 20$ V, $V_{DD} = 3.0$ V, $V_{SENSE} = 0.5$ V (unless noted otherwise)

|                             |                    |                          |                  | Limits            |                   |       |  |

|-----------------------------|--------------------|--------------------------|------------------|-------------------|-------------------|-------|--|

| Characteristics             | Symbol             | Test Conditions          | Min.             | Тур.              | Max.              | Units |  |

| Control Logic               |                    |                          |                  |                   |                   |       |  |

| Reference Input Current     | I <sub>REF</sub>   | $V_{REF} = V_{DD}$       | -1               | 0                 | 1                 | μA    |  |

| VREF input voltage range    | $V_{REF}$          |                          | 0                |                   | V <sub>DD</sub> 1 |       |  |

| Reference Divider Ratio     | $V_{REF}/V_{S}$    |                          |                  | 6                 |                   |       |  |

| G <sub>M</sub> Error        | V <sub>ERR</sub>   | V <sub>REF</sub> = 1.5V  | -5               |                   | 5                 | %     |  |

|                             | (Note 3)           | V <sub>REF</sub> = .5V   | -10              |                   | 10                | %     |  |

| Propagation Delay           | t <sub>PD</sub>    | PWM CHANGE TO SOURCE OFF | -                | <mark>150</mark>  | -                 | ns    |  |

|                             |                    | PWM CHANGE TO SINK OFF   | -                | <mark>150</mark>  | -                 | ns    |  |

|                             |                    | PWM CHANGE TO SOURCE ON  | -                | <mark>1000</mark> | -                 | ns    |  |

|                             |                    | PWM CHANGE TO SINK ON    | -                | <mark>1000</mark> | -                 | ns    |  |

|                             |                    | DISABLE TO SOURCE ON     | -                | <mark>200</mark>  | _                 | ns    |  |

|                             |                    | DISABLE TO SINK ON       | -                | <mark>200</mark>  | _                 | ns    |  |

|                             | t <sub>COD</sub>   |                          | <mark>300</mark> | <mark>850</mark>  | <mark>1200</mark> | ns    |  |

| PWM RC Frequency            | f <sub>osc</sub>   | R = 1000pf, C = 20K      |                  | 47.4              |                   | Khz   |  |

| Blank Time                  | t <sub>BLANK</sub> | R = 1000pf, C = 20K      | .8               | 1.21              | 1.6               | μs    |  |

| Thermal Shutdown Temp.      | TJ                 |                          | _                | 165               |                   | °C    |  |

| Thermal Shutdown Hysteresis | $\Delta T_{J}$     |                          | _                | 15                | _                 | °C    |  |

| UVLO Enable Threshold       |                    | Rising V <sub>DD</sub>   |                  | 2.5               | 2.8               | V     |  |

| UVLO Hysteresis             |                    |                          | 0.05             | 0.10              | _                 | V     |  |

NOTES: 1. Typical Data is for design information only.

2. Negative current is defined as coming out of (sourcing) the specified device pin.

3.  $V_{\text{ERR}} = ((V_{\text{REF}}/6) - V_{\text{SENSE}})/(V_{\text{REF}}/6)$

#### **Functional Description**

**Sleep Mode.** The input pin SLEEP is dedicated to put the device into a minimum current draw mode. All circuits are disabled including the VDD undervoltage monitor.

**Shutdown.** In the event of a fault due to excessive junction temperature, or low voltage on  $V_{CP}$  or  $V_{REG}$ , the outputs of the device are disabled until the fault condition is removed. At power up, and in the event of low  $V_{DD}$ , the UVLO circuit disables the drivers

**Current Regulation.** Load current is regulated by a fixed frequency PWM control circuit. When the outputs of the DMOS H-bridge are turned on, current increases in the motor winding until it reaches a value given by:

$I_{TRIP} = V_{REF} / (6*R_{SENSE})$

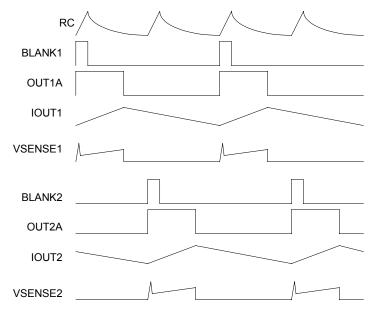

At the trip point, the sense comparator resets the source enable latch, turning off the source. At this point, load inductance causes the current to recirculate until the end fixed frequency cycle. (see timing diagram)

**VREF.** The  $V_{REF}$  voltage is divided down by 6 and compared to the voltage across the sense resistor to set the value of bridge current that will trip the PWM comparator. The  $V_{REF}$  input is a high impedance input and can be connected to  $V_{DD}$ , if desired, as well as via resistor divider. Note: When connected to  $V_{DD}$ , the  $V_{BB}$  voltage must be 1.8V greater than  $V_{DD}$  to allow proper headroom for the buffer output.

**Fixed Frequency PWM.** Selection of an external RC sets the oscillator frequency as follows:

$f_{OSC} = 1/(\frac{850ns}{t_{BLANK}} + R_T C_T))$

**Blank Time.** When a source driver turns on, a current spike occurs due to the reverse recovery currents of the clamp diodes and/or switching transients related to distributed capacitance in the load. To prevent this current spike from erroneously resetting the source enable latch, the sense comparator is blanked. The blank duration is determined by the time it takes to charge the external RC  $.38*V_{DD}$  volts with a 1mA current source.

$t_{BLANK} = C_T^*.38^*V_{DD} / (1mA - (.41^*V_{DD}/R_T))$

**VREG.** This supply voltage is used to run the sink side DMOS outputs. VREG is internally monitored and in the case of a fault condition, the outputs of the device are disabled. The VREG pin should be decoupled with a 0.22  $\mu$ F capacitor to ground.

**Charge Pump.** The Charge Pump is used to generate a supply above VBB to drive the source side DMOS gates. A 0.22 uF ceramic monolithic capacitor should be connected between  $CP_1$  and  $CP_2$  for pumping purposes. A 0.22 uF ceramic monolithic capacitor should be connected between  $V_{CP}$  and VBB to act as a reservoir to run the high side DMOS devices. The  $V_{CP}$  Voltage is internally monitored and in the case of a fault condition the outputs of the device are disabled.

**Thermal protection**. Circuitry turns OFF all drivers when the junction temperature reaches 165°C typically. It is intended only to protect the device from failures due to excessive junction temperatures and should not imply that output short circuits are permitted. Thermal shutdown has a hysteresis of approximately 15°C.

#### **Control Logic**

| Phase | Enable | Sleep | Chopping<br>(Vs>V <sub>REF</sub> /6) | OUT <sub>A</sub> |     | Function        |

|-------|--------|-------|--------------------------------------|------------------|-----|-----------------|

| Х     | Х      | 0     | Х                                    | Off              | Off | Sleep           |

| Х     | 1      | 1     | Х                                    | Off              | Off | Fast Decay      |

| 0     | 0      | 1     | 0                                    | L                | Н   | Forward         |

| 0     | 0      | 1     | 1                                    | L                | L   | Slow Decay Chop |

| 1     | 0      | 1     | 0                                    | Н                | L   | Reverse         |

| 1     | 0      | 1     | 1                                    | L                | L   | Slow Decay Chop |

Typical PWM Waveforms (Phase = 1)

#### **Terminal List**

| Pin Name | Pin Description                                 | SOIC 24 |

|----------|-------------------------------------------------|---------|

| VREG     | Regulator decoupling Terminal                   | 1       |

| RC       | Analog Input for fixed frequency                | 2       |

| SLEEP    | Logic input for SLEEP mode                      | 3       |

| VDD      | Logic Supply Voltage                            | 4       |

| OUT1B    | DMOS H – Bridge 1 Output B                      | 5       |

| GND      | Ground                                          | 6,7     |

| SENSE1   | Sense Resistor Terminal for Bridge 2            | 8       |

| OUT1A    | DMOS H – Bridge 1 Output A                      | 9       |

| ENABLE1  | Logic Input for Bridge 1 Enable Control         | 10      |

| PHASE1   | Logic Input for Bridge 1 PHASE Control          | 11      |

| REF1     | G <sub>m</sub> Reference Input Voltage Bridge 2 | 12      |

| REF2     | G <sub>m</sub> Reference Input Voltage Bridge 1 | 13      |

| PHASE2   | Logic Input for Bridge 2 PHASE Control          | 14      |

| ENABLE2  | Logic Input for Bridge 2 Enable Control         | 15      |

| OUT2B    | DMOS H – Bridge 2 Output B                      | 16      |

| SENSE2   | Sense Resistor Terminal for Bridge 1            | 17      |

| GND      | Ground                                          | 18,19   |

| OUT2A    | DMOS H – Bridge 2 Output A                      | 20      |

| VCP      | Reservoir Capacitor Terminal                    | 21      |

| CP2      | Charge Pump Capacitor Terminal                  | 22      |

| CP1      | Charge Pump Capacitor Terminal                  | 23      |

| VBB      | Load Supply                                     | 24      |

<u>eoro</u>