# 40 ns Prop. Delay, SO-8 Optocoupler

## Preliminary Technical Data

#### HCPL-0710

#### **Features**

- +5 V CMOS Compatibility

- 8 ns Pulse Width Distortion

- High Speed: 12 Mbd

- 10 kV/µs Minimum Common Mode Rejection

- Industrial Temperature Range: 0°C to 85°C

- Safety and Regulatory Approvals

UL Recognized 2500 V rms for 1 min. per UL 1577 CSA Component Acceptance Notice #5

#### **Applications**

- Digital Fieldbus Isolation: DeviceNet, SDS, PROFIBUS

- Multiplexed Data Transmission

- Computer Peripheral Interface

- Microprocessor System Interface

#### **Description**

Available in the SO-8 package style, the HCPL-0710 optocoupler utilizes the latest CMOS IC technology to achieve outstanding performance with very low power consumption. The HCPL-0710 requires only two bypass capacitors for complete CMOS compatibility.

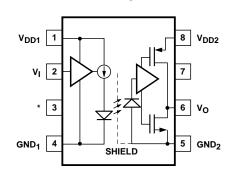

Basic building blocks of the HCPL-0710 are a CMOS LED driver IC and a CMOS detector IC. A CMOS logic input signal controls the LED driver IC which supplies current to the LED. The detector IC incorporates an integrated photodiode, a high-speed transimpedance amplifier, and a voltage comparator with an output driver.

#### **Functional Diagram**

| TRUTH TABLE            |                         |  |  |  |  |

|------------------------|-------------------------|--|--|--|--|

| V <sub>I</sub> , INPUT | V <sub>I</sub> , OUTPUT |  |  |  |  |

| Н                      | Н                       |  |  |  |  |

| L                      | L                       |  |  |  |  |

\*Pin 3 is the anode of the internal LED and must be left unconnected for guaranteed data sheet performance. Pin 7 is not connected internally. External connections to pin 7 are not recommended.

\*\*A 0.1 µF bypass capacitor must be connected between pins 1 and 4, and 5 and 8.

**CAUTION:** It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD.

This data sheet represents the latest information at the time of publication of this catalog. All specifications subject to change. Samples available Fall 1996.

### **Electrical Specifications**

Unless otherwise noted, all specifications are guaranteed across recommended operating conditions. All Typical specifications are at  $T_A = +25\,^{\circ}\text{C}$ ,  $V_{DD1} = V_{DD2} = +5\,\text{V}$ . Test conditions that are not specified can be anywhere within the recommended operating range.

| Parameter                                                         | Symbol             | Min.                   | Typ.               | Max. | Units | <b>Test Conditions</b>                                               |

|-------------------------------------------------------------------|--------------------|------------------------|--------------------|------|-------|----------------------------------------------------------------------|

| DC Specifications                                                 |                    |                        |                    |      |       |                                                                      |

| Logic Low Input Supply Current                                    | $I_{ m DDIL}$      |                        | 1.5                | 3.0  | mA    | $V_{DD1} = 5.5 \text{ V}, V_{I} = 0 \text{ V}$                       |

| Logic High Input Supply Current                                   | $I_{ m DDIH}$      |                        | 6.0                | 10.0 | mA    | $V_{DD1} = 5.5 \text{ V}, V_{I} = V_{DDI}$                           |

| Input Supply Current                                              | $I_{\mathrm{DDI}}$ |                        |                    | 13.0 | mA    | $V_{DD1} = 5.5 \text{ V}$                                            |

| Output Supply Current                                             | $I_{\mathrm{DD2}}$ |                        | 5.5                | 10.0 | mA    | $V_{\rm DD2} = 5.5 \text{ V}$                                        |

| Input Current                                                     | $I_{I}$            | -10                    |                    | 10   | μA    |                                                                      |

| Logic High Output Voltage                                         | V <sub>OH</sub>    | V <sub>DD2</sub> - 0.1 | $V_{\mathrm{DD2}}$ |      | V     | $I_{\rm O} = -20  \mu A,  V_{\rm I} = V_{\rm IH}$                    |

|                                                                   |                    | 0.8 *V <sub>DD2</sub>  | 4.5                |      |       | $I_{\rm O}$ = -4 mA, $V_{\rm I}$ = $V_{\rm IH}$                      |

| Logic Low Output Voltage                                          | $V_{ m OL}$        |                        | 0                  | 0.1  | V     | $I_{\rm O} = 20  \mu A,  V_{\rm I} = V_{\rm IL}$                     |

|                                                                   |                    |                        | 0.2                | 0.8  |       | $I_O = 4 \text{ mA}, V_I = V_{IL}$                                   |

| Switching Specifications                                          |                    |                        |                    |      |       |                                                                      |

| Propagation Delay Time to                                         | $ m t_{PHL}$       |                        | 20                 | 40   | ns    | $C_L = 15 \text{ pF}$                                                |

| Logic Low Output                                                  |                    |                        |                    |      |       | CMOS Signal Levels                                                   |

| Propagation Delay Time to                                         | $t_{ m PLH}$       |                        | 23                 | 40   |       |                                                                      |

| Logic High Output                                                 | DXX                | 00                     |                    |      |       |                                                                      |

| Pulse Width                                                       | PW                 | 80                     |                    | 10.5 | MD I  |                                                                      |

| Data Rate                                                         | DIVID              |                        | 9                  | 12.5 | MBd   | O 15 F                                                               |

| Pulse Width Distortion                                            | PWD                |                        | 3                  | 8    | ns    | $C_L = 15 \text{ pF}$<br>CMOS Signal Levels                          |

| t <sub>PHL</sub> - t <sub>PLH</sub>  <br>  Propagation Delay Skew | t                  |                        |                    | 20   |       | OWOS Signal Levels                                                   |

| Output Rise Time                                                  | t <sub>PSK</sub>   |                        | 13                 | 20   |       | $C_L = 15 \text{ pF}$                                                |

| (10 - 90%)                                                        | $t_{ m R}$         |                        | 10                 |      |       | CMOS Signal Levels                                                   |

| Output Fall Time                                                  | $t_{ m F}$         |                        | 5                  |      |       | onion algini zovola                                                  |

| (90 - 10%)                                                        | -r                 |                        |                    |      |       |                                                                      |

| Common Mode Transient                                             | CM <sub>H</sub>    | 10                     | 20                 |      | kV/μs | $V_{\rm I} = V_{\rm DDI}, V_{\rm O} >$                               |

| Immunity at Logic High Output                                     | '                  |                        |                    |      |       | $0.8 \text{ V}_{\text{DDI}}, \text{ V}_{\text{CM}} = 1000 \text{ V}$ |

| Common Mode Transient                                             | $ \mathrm{CM_L} $  | 10                     | 20                 |      |       | $V_{\rm I} = 0 \text{ V}, V_{\rm O} > 0.8 \text{ V},$                |

| Immunity at Logic Low Output                                      |                    |                        |                    |      |       | $V_{CM} = 1000 \text{ V}$                                            |

| Input Dynamic Power                                               | $C_{PD1}$          |                        | 60                 |      | pF    |                                                                      |

| Dissipation Capacitance                                           |                    |                        |                    |      |       |                                                                      |

| Output Dynamic Power                                              | $C_{PD2}$          |                        | 10                 |      |       |                                                                      |

| Dissipation Capacitance                                           |                    |                        |                    |      |       |                                                                      |