# μPD8155/56 2048-BIT STATIC MOS RAM WITH I/O PORTS AND TIMER

### **Description**

The  $\mu$ PD8155 and  $\mu$ PD8156 are  $\mu$ PD8085A family components having 256  $\times$  8-bit static RAM, 3 programmable I/O ports, and a programmable timer. They directly interface to the multiplexed  $\mu$ PD8085A bus with no external logic. The  $\mu$ PD8155 has an active low chip enable while the  $\mu$ PD8156 is active high.

The  $\mu$ PD8155 and  $\mu$ PD8156 contain 2048 bits (256  $\times$  8) of static RAM. The 256 words of memory may be selected anywhere within the system's 64K memory space by coding the upper 8 bits of address from the  $\mu$ PD8085A as a chip select.

The two general purpose 8-bit ports (PA and PB) may be programmed for input or output either in interrupt or status mode. The single 6-bit port (PC) may be used as a control for PA and PB or as a general purpose I/O port. The  $\mu$ PD8155 and  $\mu$ PD8156 are programmed for their system personalities by writing into their command/status (C/S) registers upon system initialization.

The timer is a single 14-bit down counter which is programmable for 4 modes of output operation; see table 3.

#### **Features**

- ☐ 256 × 8-bit static RAM

- ☐ Two programmable 8-bit I/O ports

- One programmable 6-bit I/O port

- ☐ Single +5 V ± 10% power supply

- Directly interfaces to the μPD8085A and μPD8085A-2

- ☐ Programmable 14-bit binary counter/timer

#### **Ordering Information**

| Part<br>Number      | Package Type       | Max Frequency<br>of Operation |

|---------------------|--------------------|-------------------------------|

| μPD8155C / 55HC     | 40-pin plastic DIP | 3 MHz                         |

| μPD8155C-2 / 55HC-2 | 40-pin plastic DIP | 5 MHz                         |

| μPD8156C / 56HC     | 40-pin plastic DIP | 3 MHz                         |

| μPD8156C-2 / 56HC-2 | 40-pin plastic DIP | 5 MHz                         |

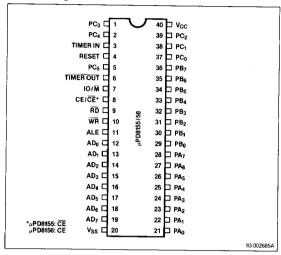

### **Pin Configuration**

#### Pin Identification

| No.            | Symbol                           | Function                          |

|----------------|----------------------------------|-----------------------------------|

| 1. 2. 5. 37-39 | PC <sub>0</sub> -PC <sub>5</sub> | 6-bit I / O port or control lines |

| 3              | TIMER IN                         | Timer clack input                 |

| 4              | RESET                            | Reset input                       |

| 6              | TIMER OUT                        | Timer counter output              |

| 7              | 10 / <b>M</b>                    | I / 0 or memory select input      |

| 8              | CE / CE                          | Chip enable input                 |

| 9              | RD                               | Read strobe input                 |

| 10             | WR                               | Write strobe input                |

| 11             | ALE                              | Address low enable input          |

| 12-19          | AD <sub>0</sub> -AD <sub>7</sub> | Low address / data bus I / 0      |

| 20             | V <sub>SS</sub>                  | Ground                            |

| 21-28          | PA <sub>0</sub> -PA <sub>7</sub> | 8-bit I / 0 port A                |

| 29-36          | PB <sub>0</sub> -PB <sub>7</sub> | 8-bit I / O port B                |

| 40             | V <sub>CC</sub>                  | +5 V power supply                 |

#### **Pin Functions**

### AD0-AD7 (Low Address/Data Bus)

Three-state address/data (AD) lines that interface with the CPU lower 8-bit address/data bus. The 8-bit address is loaded into the internal address latch on the falling edge of ALE. The 8-bit data is then written to or read from the chip, based on WR and RD strobe inputs.

### PA<sub>0</sub>-PA<sub>7</sub> (Port A)

8-bit general purpose I/O port. Data direction is selected by programming the command status register.

### PB<sub>0</sub>-PB<sub>7</sub> (Port B)

8-bit general purpose I/O port. Data direction is selected by programming the command status register.

### PC<sub>0</sub>-PC<sub>5</sub> (Port C)

6-bit general purpose I/O port or control signals for PA and PB. Port C function is selected by programming the command status register.

#### **ALE (Address Low Enable)**

This input control signal latches the address on the AD<sub>0</sub>-AD<sub>7</sub> lines and the states of CE/CE and IO/M into the chip on the falling edge of ALE.

# CE/CE (Chip Enable)

The chip enable input is active low for  $\mu$ PD8155 and active high for  $\mu$ PD8156.

## IO/M (I/O or Memory Select)

This input selects either internal RAM memory if low or I/O and command status registers if high.

#### RESET (Reset)

The reset input from  $\mu$ PD8085A initializes ports A, B, and C to the input mode.

### **TIMER IN (Timer Clock in)**

Clock input to the 14-bit binary down counter.

## **TIMER OUT (Timer Counter Output)**

The timer output is programmable for 4 output waveform modes. The selected output waveform can be a single pulse or a continuous pulse train, or it can be a single square wave or a continuous square wave.

## RD (Read Strobe)

The  $\overline{RD}$  input will strobe the addressed RAM data onto the AD bus if the IO/ $\overline{M}$  pin is low; otherwise the content of the selected I/O port or command status registers will be strobed onto the AD bus.

## WR (Write Strobe)

The WR input will strobe the available data on the AD bus into addressed RAM location or I/O ports and command status registers depending on IO/M.

### V<sub>CC</sub> (Power Supply)

+5 V power supply input.

### Vss (Ground)

Ground.

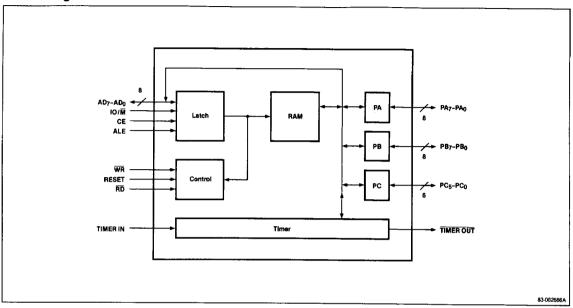

## **Block Diagram**

## **Absolute Maximum Ratings**

$T_A = 25$  °C

| Power supply voltage, V <sub>CC</sub>   | -0.5 V to +7 V  |

|-----------------------------------------|-----------------|

| Operating temperature, T <sub>OPT</sub> | 0°C to +70°C    |

| Storage temperature, T <sub>STG</sub>   | -65°C to +150°C |

| Power dissipation, P <sub>D</sub>       | 1.5 W           |

Comment: Exposing the device to stresses above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of the specification. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **DC Characteristics**

$T_A = 0$ °C to +70°C,  $V_{CC} = +5 V \pm 10$ %

|                                            |                      |      | Limit | 3                    |      | Test                                        |

|--------------------------------------------|----------------------|------|-------|----------------------|------|---------------------------------------------|

| Parameter                                  | Symbol               | Min  | Тур   | Max                  | Unit | Conditions                                  |

| Input voltage<br>low                       | V <sub>IL</sub>      | -0.5 |       | 8.0                  | ٧    |                                             |

| Input voltage<br>high                      | V <sub>IH</sub>      | 2.0  | _,    | V <sub>CC</sub> +0.5 | ٧    |                                             |

| Output voltage iow                         | V <sub>OL</sub>      |      |       | 0.45                 | ٧    | $I_{OL} = 2.0  \text{mA}$                   |

| Output voltage<br>high                     | V <sub>0H</sub>      | 2.4  |       |                      | ٧    | $l_{0H} = 400 \mu\text{A}$                  |

| Input leakage<br>current                   | l <sub>L</sub>       |      |       | ±10                  | μА   | V <sub>I</sub> =V <sub>CC</sub> to 0 V      |

| Output leakage<br>current                  | lro                  |      |       | ±10                  | μΑ   | 0.45 V ≤ V <sub>OUT</sub> ≤ V <sub>CC</sub> |

| Power supply<br>current (V <sub>CC</sub> ) | lcc                  |      |       | 180                  | mA   | 8155/56,<br>8155-2/56-2                     |

|                                            |                      |      |       | 125                  | mA   | 8155H/56H,<br>8155H-2/56H-2                 |

| Chip μPD8155                               | I <sub>IL</sub> (CE) |      |       | +100                 | μΑ   | $V_1 = V_{CC}$ to 0 V                       |

| enable µPD8156<br>leakage                  |                      |      |       | - 100                | μΑ   | $V_1 = V_{CC}$ to 0 V                       |

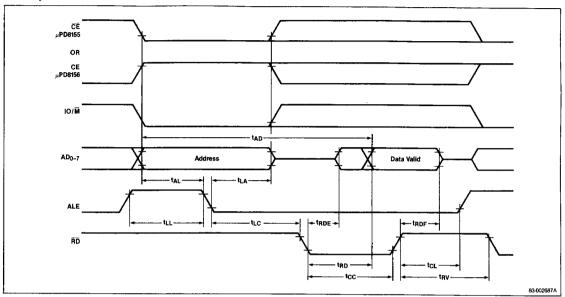

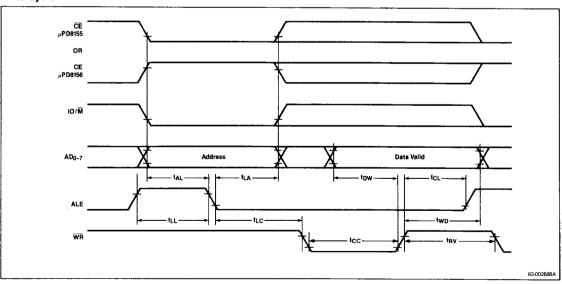

### **AC Characteristics**

$T_A = 0$ °C to +70°C,  $V_{CC} = 5$  V ± 10%

|                                        |                                 |           |           | imits         |               |      |               |

|----------------------------------------|---------------------------------|-----------|-----------|---------------|---------------|------|---------------|

|                                        | _                               | μPD8155/5 | 6/55H/56H | μPD8155-2/56- | 2/55H-2/56H-2 |      | Test          |

| Parameter                              | Symbol                          | Min       | Max       | Min           | Max           | Unit | Conditions(1) |

| Address to latch setup time            | t <sub>AL</sub>                 | 50        |           | 30            |               | ns   |               |

| Address hold time after latch          | t <sub>LA</sub>                 | 80        |           | 30            |               | ns   |               |

| Latch to READ / WRITE control          | t <sub>LC</sub>                 | 100       |           | 40            |               | ns   |               |

| Valid data out delay from READ control | t <sub>RD</sub>                 |           | 170       |               | 140           | ns   |               |

| Address stable to data out valid       | t <sub>AD</sub>                 |           | 400       |               | 330           | ns   |               |

| atch enable width                      | t <sub>LL</sub>                 | 100       |           | 70            |               | ns   |               |

| Data bus float after READ              | t <sub>RDF</sub>                | 0         | 100       | 0             | 80            | ns   |               |

| READ / WRITE control to latch enable   | t <sub>CL</sub>                 | 20        |           | 10            |               | ns   |               |

| READ / WRITE control width             | t <sub>CC</sub>                 | 250       |           | 200           |               | ns   |               |

| Data in to WRITE setup time            | t <sub>DW</sub>                 | 150       |           | 100           |               | ns   |               |

| Data in hold time after WRITE          | t <sub>WD</sub>                 | 0         |           | 0             |               | ns   |               |

| Recovery time between controls         | t <sub>RV</sub>                 | 300       |           | 200           |               | ns   |               |

| WRITE to port output                   | t <sub>WP</sub>                 |           | 400       |               | 300           | ns   |               |

| Port input setup time                  | tpR                             | 70        |           | 50            |               | ns   |               |

| Port input hold time                   | t <sub>RP</sub>                 | 50        |           | 10            |               | กร   |               |

| Strobe to buffer full                  | t <sub>SBF</sub>                |           | 400       |               | 300           | ns   |               |

| Strobe width                           | tss                             | 200       |           | 150           |               | ns   |               |

| READ to buffer empty                   | t <sub>RBE</sub>                |           | 400       |               | 300           | ns   |               |

| Strobe to INTR on                      | t <sub>SI</sub>                 |           | 400       |               | 300           | ns   |               |

| READ to INTR off                       | t <sub>RDI</sub>                |           | 400       |               | 300           | ns   |               |

| Port setup time to strobe              | tpss                            | 50        |           | 0             |               | ns   |               |

| Port hold time after strobe            | t <sub>PHS</sub>                | 120       |           | 100           |               | ns   |               |

| Strobe to buffer empty                 | t <sub>SBE</sub>                |           | 400       |               | 300           | ns   |               |

| WRITE to buffer full                   | twbe                            |           | 400       |               | 300           | ns   |               |

| WRITE to INTR off                      | twi                             |           | 400       |               | 300           | ns   |               |

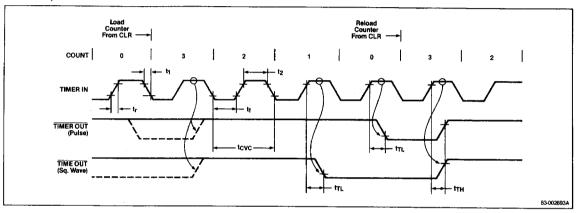

| TIMER IN to TIMER OUT low              | t <sub>TL</sub>                 |           | 400       |               | 300           | ns   |               |

| TIMER IN to TIMER OUT high             | t <sub>TH</sub>                 |           | 400       |               | 300           | ns   |               |

| Data bus enable from READ control      | t <sub>RDE</sub>                | 10        |           | 10            |               | ns   |               |

| Clock TIMER IN                         | tcyc                            | 320       |           | 200           |               | ns   |               |

| CLK rise and fall time                 | t <sub>r</sub> . t <sub>f</sub> |           | 30        |               | 30            | ns   |               |

| CLK pulse width                        | t <sub>1</sub>                  | 80        |           | 40            |               | ns   |               |

| •                                      | t <sub>2</sub>                  | 120       |           | 70            |               | ns   |               |

Note:

(1) 150 pF load

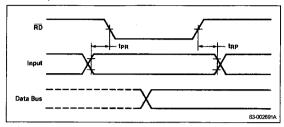

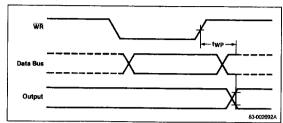

# **Timing Waveforms**

## Read Cycle

## Write Cycle

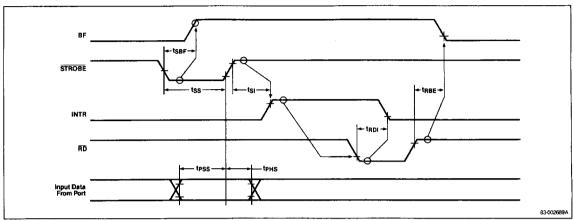

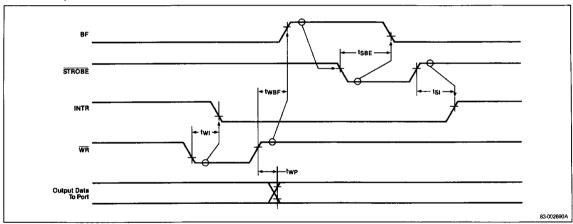

# **Timing Waveforms (cont)**

## Strobed Input Mode

## **Strobed Output Mode**

#### **Basic Input Mode**

#### **Basic Output Mode**

#### **Time Output**

### **Functional Description**

#### **Command Status Register**

The command status register is an 8-bit register which must be programmed before the  $\mu$ PD8155/56 can perform any useful functions. Its purpose is to define the mode of operation of the three ports and the timer. Programming of the device may be accomplished by writing to I/O address XXXXX000 (X = don't care) with a specific bit pattern. Reading of the command status register can be accomplished by performing an I/O read operation at address XXXXX000. The pattern returned will be a 7-bit status report of PA, PB and the timer. The bit patterns for the command status register read and write are shown in tables 1 and 2.

Table 1. Command Status Write

| TM2 TM1 | IEB | IEA | PC <sub>2</sub> | PC <sub>1</sub> | PB | PA |

|---------|-----|-----|-----------------|-----------------|----|----|

|---------|-----|-----|-----------------|-----------------|----|----|

where:

TM2-TM1 = Define timer mode

IEB = Enable port B interrupt

IEA = Enable port A interrupt

PC2-PC1 = Define port C mode

PB/PA = Define port B/A as in or out(1)

The timer mode of operation is programmed as follows during command status write:

| TM2 | TM1 | Timer Mode                   |

|-----|-----|------------------------------|

| 0   | 0   | Don't affect timer operation |

| 0   | 1   | Stop timer counting          |

| 1   | 0   | Stop counting after TC       |

| 1   | 1   | Start timer operation        |

Interrupt enable status is programmed as follows:

| IEB/IEA | Interrupt Enable Port B/A |

|---------|---------------------------|

| 0       | No                        |

| 1       | Yes                       |

Port C may be placed in four possible (Alt) modes of operation as outlined below. The modes are selected during command status write as follows:

| PC <sub>2</sub> | PC <sub>1</sub> | Port C Mode |

|-----------------|-----------------|-------------|

| 0               | 0               | Alt 1       |

| 0               | 1               | Alt 3       |

| 1               | 0               | Alt 4       |

| 1               | 1               | Alt 2       |

The function of each pin of port C in the four possible modes is outlined as follows:

| Pin             | Alt 1 | Alt 2 | Alt 3(2) | Alt 4(2) |

|-----------------|-------|-------|----------|----------|

| PC <sub>0</sub> | In    | Out   | A INTR   | A INTR   |

| PC <sub>1</sub> | In    | Out   | A BF     | A BF     |

| PC <sub>2</sub> | ln    | Out   | A STB    | A STB    |

| PC <sub>3</sub> | In    | Out   | Out      | B INTR   |

| PC <sub>4</sub> | In    | Out   | Out      | B BF     |

| PC <sub>5</sub> | In    | Out   | Out      | B STB    |

#### Note:

(1) PB/PA sets port B/A mode: 0 = input; 1 = output

(2) In Alt 3 and Alt 4 modes, the control signals are initialized as follows:

Control Input Output

STB (Input strobe) Input control Output control

INTR (Interrupt request) Low High

BF (Buffer full) Low Low

Table 2. Command Status Read

| TI | INTE | B  | INTR | INTE | A  | INTR |

|----|------|----|------|------|----|------|

|    | B    | BF | B    | A    | BF | A    |

where:

TI

= Indicates a timer interrupt. This bit is set when terminal count is reached. It is reset when starting a new count, or a hardware reset occurs, or after reading the CS register.

INTE B/A B/A BF = Port B/A interrupt. High = active.

= Indicates whether port B/A is full if in input mode or empty if in output mode. High = active.

INTR B/A = Port B/A interrupt request. High = active.

The programming address summary for the status, ports, and timer are as follows:

| I/O Address | Number of Bits | Function       |  |

|-------------|----------------|----------------|--|

| XXXXX000    | 8              | Command status |  |

| XXXXX001    | 8              | PA             |  |

| XXXXX010    | 8              | PB             |  |

| XXXXX011    | 6              | PC             |  |

| XXXXX100    | 8              | Timer low      |  |

| XXXXX101    | 8              | Timer high     |  |

#### **Timer Operation**

The internal timer is a 14-bit binary down counter capable of operating in 4 output modes which are programmable at any time during operation. Any TTL clock meeting timer in requirements (see AC Characteristics) may be used as a time base and fed to the timer input. The timer output may be looped around and cause an interrupt or may be used as I/O control. The output modes are defined in table 3 and programmed as the two MSBs of the higher order byte of the timer count register.

Table 3. Timer Output Modes

| M <sub>2</sub> | M <sub>1</sub> | Operation                                             |  |  |  |  |  |

|----------------|----------------|-------------------------------------------------------|--|--|--|--|--|

| 0              | 0              | Single square wave cycle from start to terminal count |  |  |  |  |  |

| 0              | 1              | Continuous square wave (period = count length)        |  |  |  |  |  |

| 1              | 0              | Single pulse at terminal count                        |  |  |  |  |  |

| 1              | 1              | Continuous single pulse occurring at terminal count   |  |  |  |  |  |

Programming the timer requries two words to be written to the  $\mu$ PD8155/56 at I/O address XXXXX100 and XXXXX101 for the low and high order bytes, respectively. Valid count length must be between 0002H and 3FFFH. The bit assignments for the high and low programming words of the timer count register are as follows:

| Word      | Timer Count Register |                |                 |                 |                 |                 |                |                | I/O Address |

|-----------|----------------------|----------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|-------------|

| High byte | M <sub>2</sub>       | M <sub>1</sub> | T <sub>13</sub> | T <sub>12</sub> | T <sub>11</sub> | T <sub>10</sub> | Tg             | T <sub>8</sub> | XXXXX101    |

| Low byte  | T <sub>7</sub>       | T <sub>6</sub> | T <sub>5</sub>  |                 | T <sub>3</sub>  | T <sub>2</sub>  | T <sub>1</sub> | T <sub>0</sub> | XXXXX100    |

The control of the timer is performed by TM2 and TM1 of the command status word.

Note that counting will be stopped by a hardware reset. A start command must be issued via the command status register to begin counting. A new mode and/or count length can be loaded while the counter is counting, but will not be used until a start command is issued.

When an external nonsynchronous event is used as the timer input, the signal must first be synchronized to the system clock. A D-type flip-flop can be used for this purpose.