# 82C556/82C557/82C558N Viper Notebook Chipset Data Book

Revision: 1.0 912-3000-032 May 25, 1995

#### Copyright

Copyright © 1995, OPTi Inc. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written permission of OPTi Incorporated, 2525 Walsh Avenue, Santa Clara, CA 95051.

#### Disclaimer

OPTi Inc. makes no representations or warranties with respect to the design and documentation herein described and especially disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, OPTi Inc. reserves the right to revise the design and associated documentation and to make changes from time to time in the content without obligation of OPTi Inc. to notify any person of such revisions or changes.

#### **Trademarks**

OPTi and OPTi Inc. are registered trademarks of OPTi Inc. All other trademarks and copyrights are the property of their respective holders.

#### **OPTi Inc.**

2525 Walsh Avenue Santa Clara, CA 95051 Tel: (408) 980-8178 Fax: (408) 980-8860

BBS: (408) 980-9774

# **Table of Contents**

| 1.0 | ) Features |            |            |                                 | 1  |  |

|-----|------------|------------|------------|---------------------------------|----|--|

| 2.0 | Overview   |            |            |                                 |    |  |

|     | 2.1        | 82C556     | Data Buff  | er Controller (DBC)             | 3  |  |

|     | 2.2        |            |            | controller (SYSC)               |    |  |

|     | 2.3        |            | -          | ed Peripherals Controller (IPC) |    |  |

| 3.0 | Sign       | al Definit | ions       |                                 | 6  |  |

|     | 3.1        | Termin     | ology/Non  | nenclature Conventions          | 6  |  |

|     | 3.2        |            |            | escriptions                     |    |  |

|     |            | 3.2.1      | _          | Interface Signals               |    |  |

|     |            | 3.2.2      |            | nterface Signals                |    |  |

|     |            | 3.2.3      |            | terface Signals                 |    |  |

|     |            | 3.2.4      |            | round, and NC Pins              |    |  |

|     | 3.3        |            |            | escriptions                     |    |  |

|     |            | 3.3.1      | _          | d Clock Signals                 |    |  |

|     |            | 3.3.2      | CPU Bus    | Interface Signals               | 21 |  |

|     |            | 3.3.3      | Cache Co   | ontrol Interface Signals        | 24 |  |

|     |            | 3.3.4      |            | terface Signals                 |    |  |

|     |            | 3.3.5      | Local Bus  | Interface Signals               | 27 |  |

|     |            | 3.3.6      |            | 2C558N Interface Signals        |    |  |

|     |            | 3.3.7      |            | nterface Signals                |    |  |

|     |            | 3.3.8      |            | d Ground Pins                   |    |  |

|     | 3.4        | 82C557     | Suspend    | Mode Support                    | 32 |  |

|     | 3.5        | 82C558     | N Signal [ | Descriptions                    | 38 |  |

|     |            | 3.5.1      | Reset and  | d Clock Signals                 | 38 |  |

|     |            | 3.5.2      | 82C557 a   | and 82C556 Interface Signals    | 38 |  |

|     |            | 3.5.3      | PCI Bus I  | nterface Signals                | 39 |  |

|     |            | 3.5.4      | PMU Inte   | rface Signals                   | 41 |  |

|     |            | 3.5.5      | ISA Bus I  | nterface Signals                | 42 |  |

|     |            | 3.5.6      | ISA DMA    | Arbiter Signals                 | 45 |  |

|     |            | 3.5.7      | Interrupt  | Control Signals                 | 48 |  |

|     |            |            | 3.5.7.1    | RTC and Timer Signals           |    |  |

|     |            |            | 3.5.7.2    | Miscellaneous Signals           |    |  |

|     |            |            | 3.5.7.3    | Power and Ground Signals        |    |  |

|     | 3.6        |            | • .        | nmable Pin Information          |    |  |

|     | 3.7        | 82C558     | N Suspen   | d Mode Support                  | 58 |  |

912-3000-032

Revision: 1.0

Page iii

**-** 9004196 0001150 845 🖛

## **Table of Contents (cont.)**

| 1.0 | Fund | tional D      | Pescription                                                       | 57 |  |  |

|-----|------|---------------|-------------------------------------------------------------------|----|--|--|

|     | 4.1  | 1 Reset Logic |                                                                   |    |  |  |

|     | 4.2  | System        | m Clocks                                                          | 57 |  |  |

|     |      | 4.2.1         | CPU and 82C557 Clocks                                             | 57 |  |  |

|     |      | 4.2.2         | PCI and VL Bus Clocks                                             | 58 |  |  |

|     |      | 4.2.3         | ISA Bus Clocks                                                    | 58 |  |  |

|     | 4.3  | Cache         | Subsystem                                                         |    |  |  |

|     |      | 4.3.1         | CPU Burst Mode Control                                            | 59 |  |  |

|     |      |               | 4.3.1.1 Cyrix Linear Burst Mode Support                           | 59 |  |  |

|     |      | 4.3.2         | Cache Cycle Types                                                 | 60 |  |  |

|     |      | 4.3.3         | Single and Double Bank Support                                    | 60 |  |  |

|     |      | 4.3.4         | Cache Operation                                                   | 61 |  |  |

|     |      |               | 4.3.4.1 L2 Cache Read Hit                                         | 61 |  |  |

|     |      |               | 4.3.4.2 L2 Cache Write Hit Cycle                                  | 65 |  |  |

|     |      |               | 4.3.4.3 L2 Cache Read Miss                                        | 68 |  |  |

|     |      |               | 4.3.4.4 L2 Cache Write Miss                                       |    |  |  |

|     |      |               | 4.3.4.5 Adaptive Write-Back Policy                                |    |  |  |

|     |      |               | 4.3.4.5.1 Write-Through on Page Hit and RAS# Active (AWB Mode 1)  |    |  |  |

|     |      |               | 4.3.4.5.2 Write-Through on Page Hit (AWB Mode 2)                  |    |  |  |

|     |      |               | 4.3.4.6 Tag Compare Table                                         |    |  |  |

|     |      |               | 4.3.4.7 1 Separate Tag/Dirty RAM Implementation                   |    |  |  |

|     |      |               | 4.3.4.7.2 Combined Tag/Dirty RAM Implementation                   |    |  |  |

|     |      |               | 4.3.4.8 Cache Initialization                                      |    |  |  |

|     |      |               | 4.3.4.9 Write Back Cache with DMA/ISA Master/PCI Master Operation |    |  |  |

|     |      | 4.3.5         | Shadow ROM and BIOS Cacheability                                  |    |  |  |

|     |      |               | 4.3.5.1 Cacheability and Write Protection                         |    |  |  |

|     |      | 4.3.6         | Synchronous SRAM Support                                          |    |  |  |

|     |      |               | 4.3.6.1 Pipelined Synchronous SRAM support                        |    |  |  |

|     |      |               | 4.3.6.2 SONY SONIC-2WP (Cache Module) Support                     | 91 |  |  |

|     |      | 4.3.7         | SRAM Requirements                                                 | 92 |  |  |

|     |      | 4.3.8         | Skew Control                                                      | 93 |  |  |

|     | 4.4  | DRAM          | Controller                                                        | 94 |  |  |

|     |      | 4.4.1         | DRAM Configuration                                                | 94 |  |  |

|     |      | 4.4.2         | Programming the DRAM Parameters                                   | 94 |  |  |

|     |      |               | 4.4.2.1 Number of DRAM banks                                      | 94 |  |  |

|     |      |               | 4.4.2.2 DRAM Size and Type                                        | 95 |  |  |

|     |      |               | 4.4.2.3 DRAM Address Muxing                                       |    |  |  |

|     |      |               | 4.4.2.4 Timing Parameters                                         |    |  |  |

|     |      |               | 4.4.2.5 Drive Strengths                                           | 97 |  |  |

Page iv Revision: 1.0

912-3000-032

**-** 9004196 0001151 781 **-**

## Table of Contents (cont.)

|      | 4.4.3  | DRAM Cycles                                    | 97  |

|------|--------|------------------------------------------------|-----|

|      |        | 4.4.3.1 DRAM Read Cycle                        | 97  |

|      |        | 4.4.3.2 DRAM Write Cycle                       |     |

|      |        | 4.4.3.3 DRAM Parity Generation/Detection Logic | 102 |

|      |        | 4.4.3.4 DRAM Refresh Logic                     | 102 |

|      | 4.4.4  | DRAM DMA/Master Cycles                         | 103 |

|      | 4.4.5  | DRAM Hole Control                              | 104 |

|      | 4.4.6  | Lookup Table DRAM Configuration Mode           | 105 |

| 4.5  | PCI Bu | ıs Interface                                   | 106 |

|      | 4.5.1  | PCI Master Cycles                              | 106 |

|      |        | 4.5.1.1 System Memory Access                   | 106 |

|      |        | 4.5.1.2 Non-Local Memory Access                | 107 |

|      |        | 4.5.1.3 PCI Master Pre-Snoop                   | 107 |

|      | 4.5.2  | PCI Slave Cycles                               | 108 |

|      |        | 4.5.2.1 CPU Master Cycles                      | 108 |

|      |        | 4.5.2.2 PCI Byte/Word Merge                    | 108 |

|      |        | 4.5.2.3 ISA Master Cycles                      | 108 |

| 4.6  | VL Bus | s Interface                                    | 109 |

| 4.7  | ISA Bu | ıs Interface                                   | 120 |

| 4.8  | XD Bus | s Interface                                    | 120 |

| 4.9  | Bus Aı | rbitration Logic                               | 120 |

| 4.10 | Data B | us Conversion/Data Path Control Logic          | 121 |

| 4.11 | Specia | ıl Cycles                                      | 121 |

|      | 4.11.1 | •                                              |     |

|      | 4.11.2 | •                                              |     |

| 4.12 |        | al Integrated Peripherals Controller           |     |

|      | 4.12.1 | Hardware Considerations                        |     |

|      | 4.12.2 | IPC Configuration Programming                  |     |

|      | 4.12.3 | IPC Register Programming                       |     |

|      | 4.12.0 | 4.12.3.1 Initialization Command Words          |     |

|      |        | 4.12.3.2 Operational Command Words             |     |

|      |        | 4.12.3.3 Interrupt Controller Shadow Registers |     |

|      | 4.12.4 | DMA Controller Programming Registers           |     |

|      | 4.12.5 | Timer Programming Registers                    |     |

|      |        | 4.12.5.1 Shadow Registers To Support Timer     |     |

|      | 4.12.6 | Writing/Reading I/O Port 070h                  |     |

|      |        | 4.12.6.1 RTC Index Shadow Register             |     |

|      | 4.12.7 | IRQ8 Polarity                                  |     |

|      | 4.12.8 | Fast GATEA20 and Reset Emulation               |     |

|      | 7.12.0 | 1 ast On LAZV and Neset Linuation              |     |

912-3000-032

Revision: 1.0

Page v

**9004196 0001152 618**

# Table of Contents (cont.)

| 4.13 | Integra | ted Local I | Bus Enhan   | ced IDE Interface                                  | 132 |

|------|---------|-------------|-------------|----------------------------------------------------|-----|

|      | 4.13.1  | Hardware    | Considerat  | tions                                              | 132 |

|      | 4.13.2  | Performar   | nce and Po  | wer                                                | 132 |

|      | 4.13.3  |             |             |                                                    |     |

|      | 4.13.4  | •           |             |                                                    |     |

|      |         | _           | _           | ogramming Method (Enhanced)                        |     |

|      |         |             |             | Timing 0 and Timing 1                              |     |

|      |         |             |             | Subset Registers for Timing 0 and 1                |     |

|      |         |             |             | Step-by-Step Programming Procedure                 |     |

|      |         |             |             | Enabling Access to 611 Register Set                |     |

|      |         |             | 4.13.4.1.5  | Setting Up Enhanced 611 Timing                     | 136 |

|      |         |             | 4.13.4.1.6  | Associating Timing with Each Drive                 | 136 |

|      |         |             | 4.13.4.1.7  | Enabling IDE Operation and Hiding 611 Register Set | 136 |

| 4.14 | Power   | Manageme    | ent         | ***************************************            | 137 |

|      | 4.14.1  | Power Ma    | anagement   | Unit (PMU)                                         | 137 |

|      |         | 4.14.1.1    | Activity Mo | nitoring                                           | 138 |

|      |         |             | 4.14.1.1.1  | Timers                                             | 138 |

|      |         |             | 4.14.1.1.2  | Events                                             | 138 |

|      |         |             | 4.14.1.1.3  | Timer Clock Sources                                | 138 |

|      |         |             |             | Time-Out Count and Time-Out SMI                    |     |

|      |         |             | 4.14.1.1.5  | ACCESS Events                                      | 141 |

|      |         |             |             | Serial (COMx) and Parallel Port (LPT) Access       |     |

|      |         |             | 4.14.1.1.7  | ISA Bus Floppy and Hard Drive Access               | 142 |

|      |         |             | •           | Controller Hard Drive Access                       |     |

|      |         |             |             | Keyboard Access                                    |     |

|      |         |             |             | LCD Controller Access                              |     |

|      |         |             |             | t Generation (GPCS) Access                         |     |

|      |         |             |             | General Purpose (GNR) Access                       |     |

|      |         |             |             | Memory Watchdog Feature                            |     |

|      |         |             | -           | cking Registers                                    |     |

|      |         |             | _           | DLE_TIMER                                          |     |

|      |         |             |             | MI Events                                          |     |

|      |         |             |             | EPMI Programming                                   |     |

|      |         |             |             | agement Event Status                               |     |

|      | 4.14.2  | •           |             | ol                                                 |     |

|      |         |             |             | Mechanism to Control CPU Power Dissipation         |     |

|      |         |             |             | Programming                                        |     |

|      |         |             |             |                                                    |     |

|      |         |             |             | Presetting Events to Reset Doze Mode               |     |

|      |         |             |             | Automatic (Hardware) Doze Mode                     |     |

|      |         | •           | 4.14.2.2.3  | APM (Software) Doze Mode                           | 153 |

Page vi Revision: 1.0 912-3000-032

**■ 9004196 0001153 554 ■**

## Table of Contents (cont.)

|      |        | 4.14.2.2.4              | Start Doze Bit                        | 155 |

|------|--------|-------------------------|---------------------------------------|-----|

|      |        | 4.14.2.2.5 U            | Jsing Doze Time-out to Trigger an SMI | 155 |

|      |        | 4.14.2.3 DEVSEL# Do     | oze Reset                             | 155 |

|      | 4.14.3 | CPU Thermal Manager     | ment Unit                             | 156 |

|      |        | 4.14.3.1 Prediction of  | Overtemp Activity                     | 156 |

|      |        | 4.14.3.2 Operating Te   | mperature Ranges                      | 156 |

|      |        | 4.14.3.3 Accounting for | or CPU Activity                       | 156 |

|      |        | 4.14.3.4 Operating Te   | mperature Range Determination         | 157 |

|      |        | 4.14.3.4.1 E            | Example                               | 158 |

|      |        | 4.14.3.4.2 F            | Programming                           | 158 |

|      |        | 4.14.3.4.3              | SMI Generation                        | 158 |

|      |        | 4.14.3.5 Emergency C    | Overtemp Sense                        | 158 |

|      |        | 4.14.3.5.1 F            | Programming                           | 159 |

|      | 4.14.4 | Suspend and Resume      |                                       | 160 |

|      |        | 4.14.4.1 Suspend Mod    | de                                    | 160 |

|      |        |                         | Suspend Mode Power Savings            |     |

|      |        | 4.14.4.1.2              | Suspend Mode Refresh                  | 160 |

|      |        |                         | Multiplexed Inputs Scan Rate          |     |

|      |        | 4.14.4.1.4              | Suspend Mode HOLD Control             | 160 |

|      | 4.14.5 | Resume Event            |                                       | 162 |

|      |        | 4.14.5.1 EPMI/IRQ Ev    | vents                                 | 162 |

|      |        | 4.14.5.2 SUS/RES# a     | nd RINGI Events                       | 162 |

|      | 4.14.6 | Chip-Level Power Cons   | servation Features                    | 164 |

|      |        | 4.14.6.1 Automatic Ke   | eper Resistors                        | 164 |

|      |        |                         | U Suspend                             |     |

|      |        | 4.14.6.3 Stopping IPC   | Clock When Not In Use                 | 164 |

|      | 4.14.7 |                         |                                       |     |

|      |        | 4.14.7.1 Hardware Co    | nsiderations                          | 166 |

|      |        | 4.14.7.2 Programming    | ]                                     | 166 |

|      |        | 4.14.7.3 Resume Rec     | overy Time                            | 167 |

|      |        | 4.14.7.4 PPWR[1:0] S    | Suspend Auto Toggle Feature           | 167 |

|      | 4.14.8 | Programmable Chip Se    | elect Feature                         | 167 |

| 4.15 | System | Management Interrup     | t (SMI)                               | 169 |

|      | 4.15.1 | SMI Operation and Initi | ialization                            | 170 |

|      |        | 4.15.1.1 Loading Initia | al SMM Code and Data                  | 170 |

|      |        | 4.15.1.2 Run-Time SN    | /II Address Relocation                | 172 |

|      | 4.15.2 | SMI Event Generation    |                                       | 172 |

|      |        | 4.15.2.1 Time-out Eve   | ent Generation of SMI                 | 172 |

|      |        | 4.15.2.2 Access Even    | t Generation of SMI                   | 173 |

|      |        | 4.15.2.3 Interrupt Eve  | nt Generation of SMI                  | 174 |

|      |        |                         |                                       |     |

912-3000-032

Revision: 1.0

Page vii

## **Table of Contents (cont.)**

|     |                         | 4.15.2.4 DRQ Event Generation of SMI                             | 174 |  |  |  |

|-----|-------------------------|------------------------------------------------------------------|-----|--|--|--|

|     |                         | 4.15.3 Enabling of Events to Generate SMI                        | 175 |  |  |  |

|     |                         | 4.15.3.1 PMI #25 Triggers                                        | 175 |  |  |  |

|     |                         | 4.15.4 Servicing an SMI                                          | 177 |  |  |  |

|     |                         | 4.15.4.1 PMI Source Register Details                             | 178 |  |  |  |

|     |                         | 4.15.4.2 EPMI Pin PMI Sources                                    | 178 |  |  |  |

|     |                         | 4.15.5 I/O SMI Trap Indication                                   | 178 |  |  |  |

|     | 4.16                    | Utility Registers                                                | 179 |  |  |  |

|     | 4.17                    | ISA Bus Hot Docking Feature                                      | 180 |  |  |  |

| 5.0 | Regi                    | ster Descriptions                                                | 184 |  |  |  |

|     | 5.1                     | 82C557 Register Space                                            | 185 |  |  |  |

|     |                         | 5.1.1 82C557 PCI Configuration Registers                         | 185 |  |  |  |

|     |                         | 5.1.2 82C557 System Control Registers                            | 187 |  |  |  |

|     | 5.2                     | 82C558N Register Space                                           | 194 |  |  |  |

|     |                         | 5.2.1 82C558N PCI Configuration Register Space                   | 194 |  |  |  |

|     |                         | 5.2.2 82C558N Power Management Register Descriptions             | 200 |  |  |  |

|     | 5.3                     | Miscellaneous System Control Registers                           | 216 |  |  |  |

| 6.0 | Maxi                    | mum Ratings                                                      | 219 |  |  |  |

|     | 6.1                     | Absolute Maximum Ratings                                         | 219 |  |  |  |

|     | 6.2                     | DC Characteristics: 5.0 Volt (VCC = 5.0V ±5%, TA = 0°C to +70°C) | 219 |  |  |  |

|     | 6.3                     | DC Characteristics: 3.3 Volt (VDD = 3.3V ±5%, TA = 0°C to +70°C) | 219 |  |  |  |

|     | 6.4                     | 82C556 AC Characteristics (66MHz - Preliminary)                  | 220 |  |  |  |

|     | 6.5                     | 82C557 AC Characteristics (66MHz - Preliminary)                  | 221 |  |  |  |

|     | 6.6                     | 82C558N AC Characteristics (66MHz - Preliminary)                 | 223 |  |  |  |

|     | 6.7                     | AC Timing Diagrams                                               | 224 |  |  |  |

| 7.0 | Test Mode Information22 |                                                                  |     |  |  |  |

|     | 7.1                     | 82C556 Testability                                               | 227 |  |  |  |

|     |                         | 7.1.1 82C556 NAND Tree Test (Test Mode 1)                        | 227 |  |  |  |

|     | 7.2                     | 82C557 Testability                                               | 227 |  |  |  |

|     |                         | 7.2.1 82C557 NAND Tree Test (Test Mode 1)                        |     |  |  |  |

|     | 7.3                     | 82C558N Testability                                              |     |  |  |  |

|     |                         | 7.3.1 82C558N NAND Tree Test (Test Mode 1)                       |     |  |  |  |

|     |                         | 7.3.2 Drive High/Drive Low Test (Test Modes 2 and 3)             | 231 |  |  |  |

| 8.0 | Meci                    | nanical Package Outlines                                         | 233 |  |  |  |

Page viii

Revision: 1.0

912-3000-032

**=** 9004196 0001155 327 **=**

## **Table of Contents (cont.)**

| ٩.٥ | Acce       | Accessing the BBS |                             |     |  |  |  |

|-----|------------|-------------------|-----------------------------|-----|--|--|--|

|     | <b>A.1</b> | Paging            | g the SYSOP                 | 237 |  |  |  |

|     | <b>A.2</b> | Syster            | m Requirements              | 237 |  |  |  |

|     | <b>A.3</b> | Calling           | g In/Hours of Operation     | 237 |  |  |  |

|     | <b>A.4</b> | Loggir            | ng On for the First Time    | 237 |  |  |  |

|     | <b>A.5</b> |                   |                             | 237 |  |  |  |

|     | <b>A.6</b> | Using             | the BBS                     | 237 |  |  |  |

|     |            | A.6.1             | Reading Bulletins           | 237 |  |  |  |

|     |            | A.6.2             | Sending/Receiving Messages  | 238 |  |  |  |

|     |            | A.6.3             | Finding Information         | 238 |  |  |  |

|     |            | A.6.4             | Downloading Files From OPTi | 238 |  |  |  |

|     |            | A.6.5             | Uploading Files To OPTi     | 238 |  |  |  |

|     |            | A.6.6             | Logging Off                 | 238 |  |  |  |

|     |            | A.6.7             | Logging Back on Again       | 238 |  |  |  |

|     | <b>A.7</b> | The M             | lenus                       | 238 |  |  |  |

|     |            | A.7.1             | Menu Selections             | 239 |  |  |  |

912-3000-032

Revision: 1.0

Page ix

9004196 0001156 263

# **List of Figures**

| Figure 1-1  | Viper-N System Block Diagram                                                    | 1  |

|-------------|---------------------------------------------------------------------------------|----|

| Figure 2-1  | 82C556 Block Diagram                                                            | 3  |

| Figure 2-2  | 82C557 Block Diagram                                                            | 4  |

| Figure 2-3  | 82C558N Block Diagram                                                           | 5  |

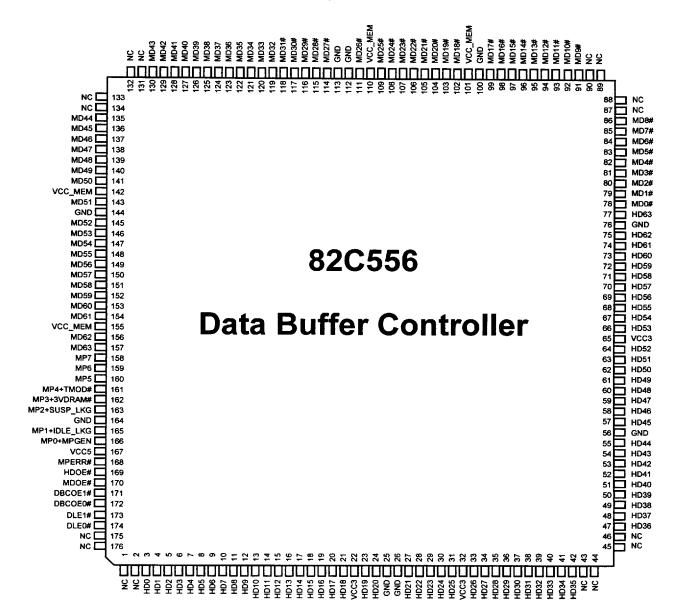

| Figure 3-1  | 82C556 Pin Diagram (176-Pin TQFP)                                               | 7  |

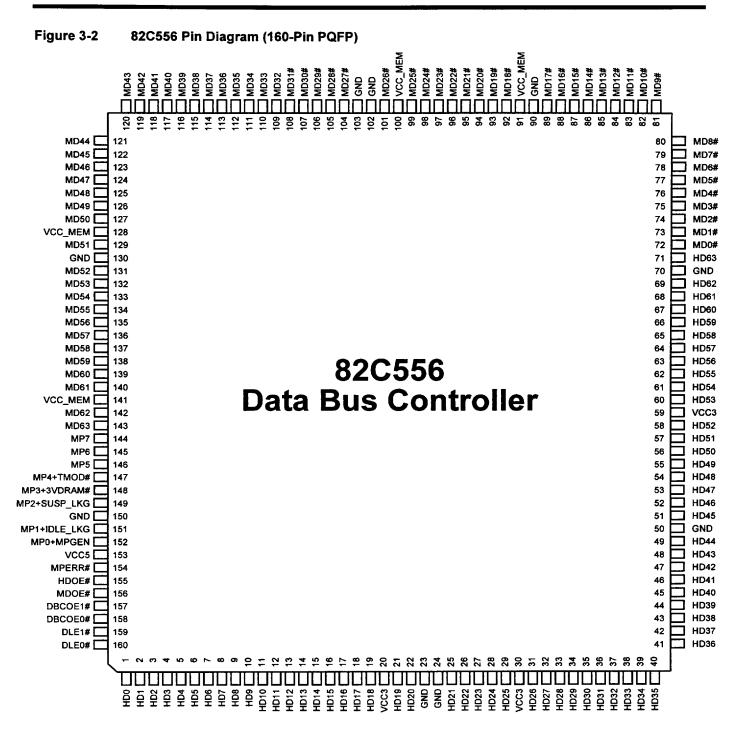

| Figure 3-2  | 82C556 Pin Diagram (160-Pin PQFP)                                               | 10 |

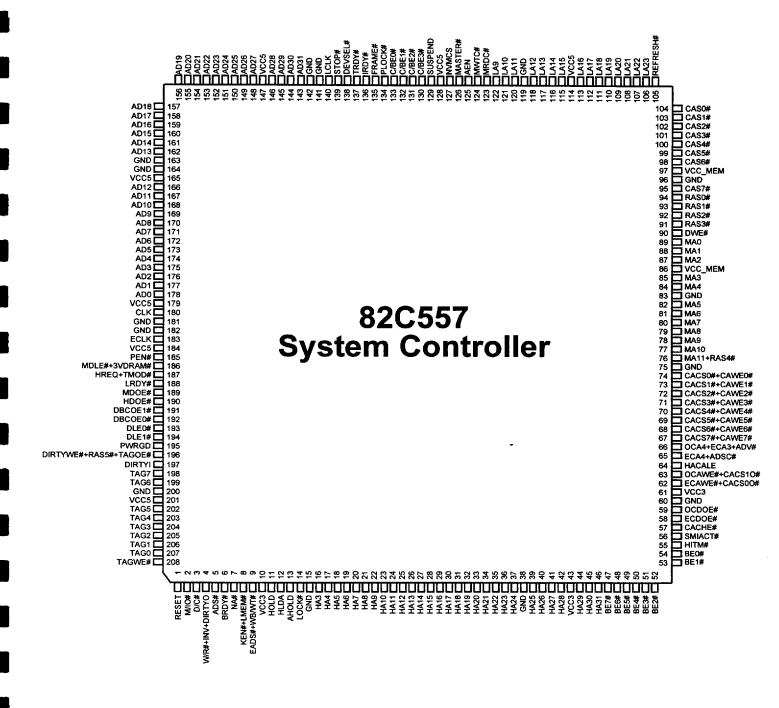

| Figure 3-3  | 82C557 Pin Diagram                                                              | 17 |

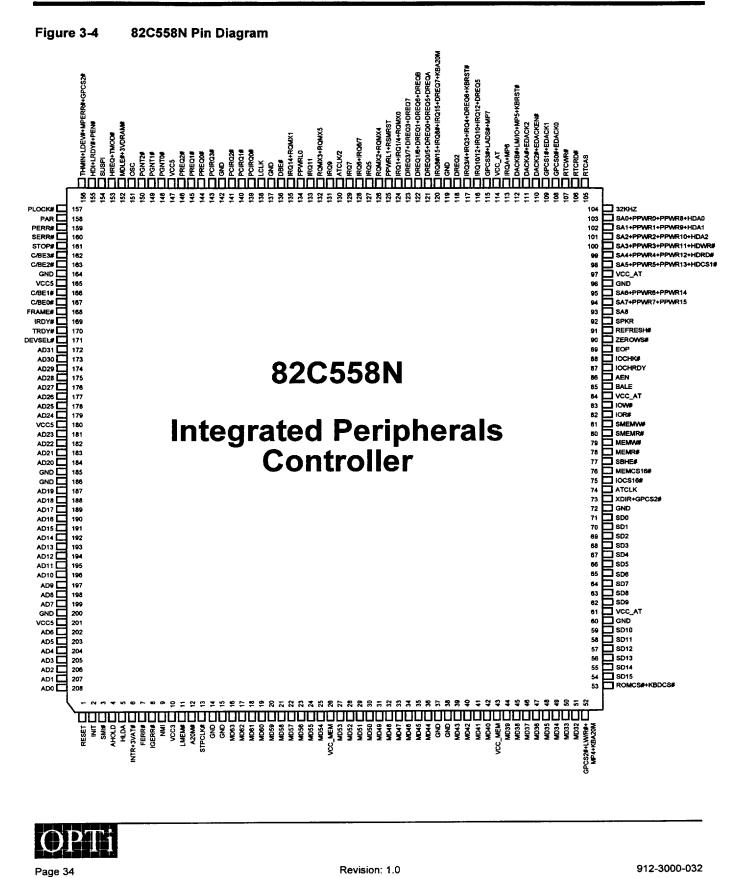

| Figure 3-4  | 82C558N Pin Diagram                                                             | 34 |

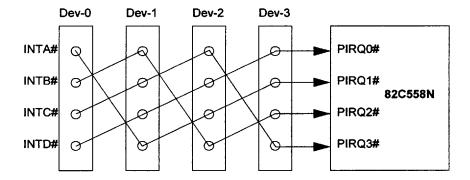

| Figure 3-5  | PCI Interrupts Mapping Matrix                                                   | 52 |

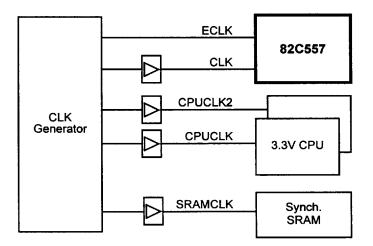

| Figure 4-1  | CPU and 82C557 Clock Distribution                                               | 57 |

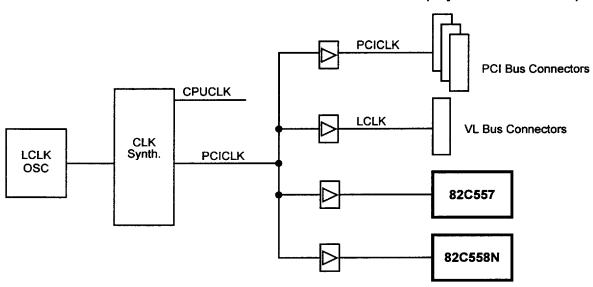

| Figure 4-2  | Clock Distribution Method for VL Bus and PCI Connectors (Async. PCI and VL Bus) | 58 |

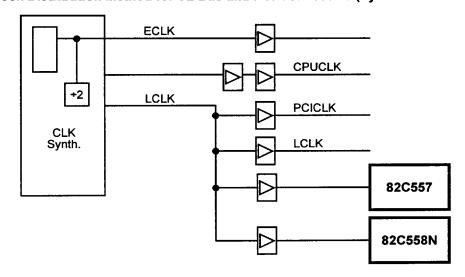

| Figure 4-3  | Clock Distribution Method for VL Bus and PCI Connectors (Sync. PCI and VL Bus)  | 58 |

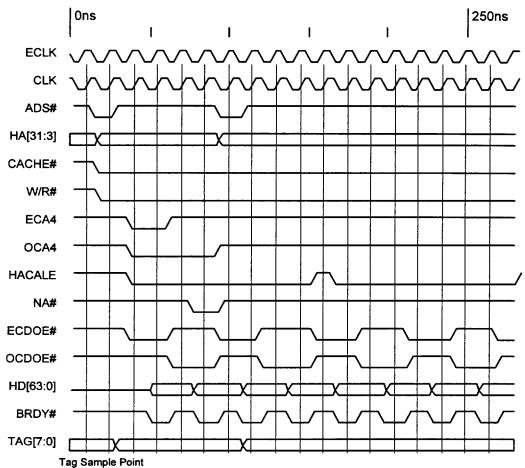

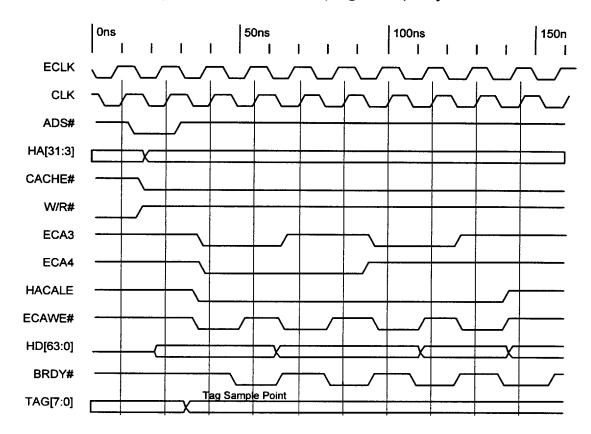

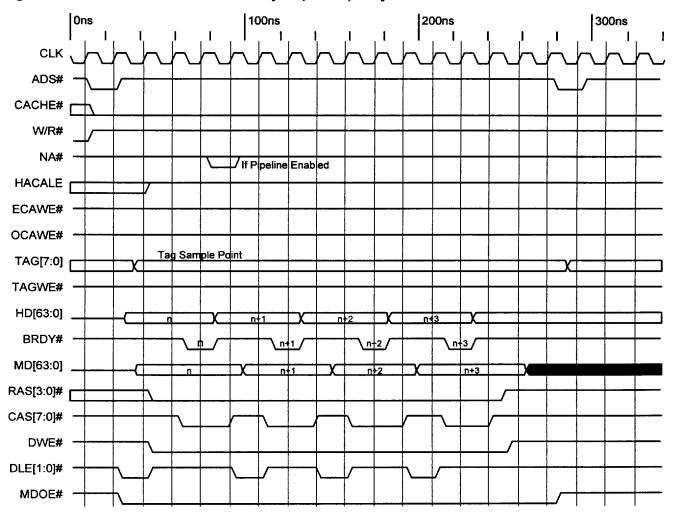

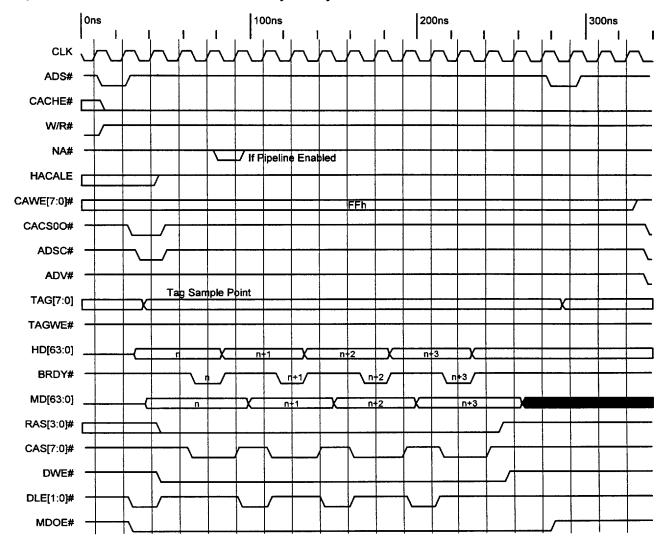

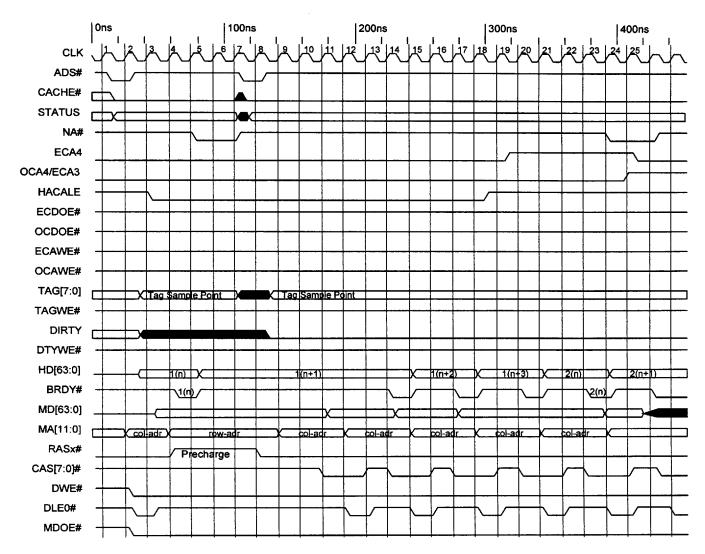

| Figure 4-4  | L2 Cache Read Hit Cycle - Async. SRAMs (Double Bank)                            | 62 |

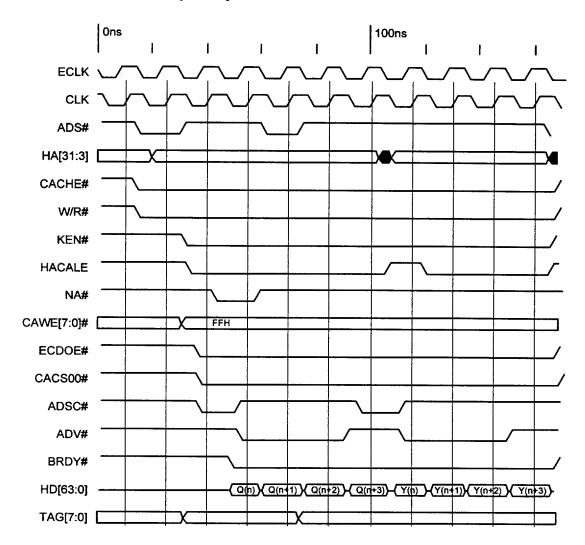

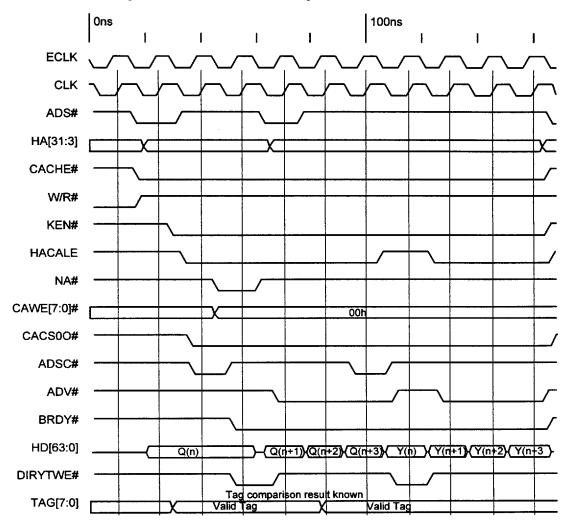

| Figure 4-5  | L2 Cache Read Hit Cycle - Sync. SRAMs                                           | 63 |

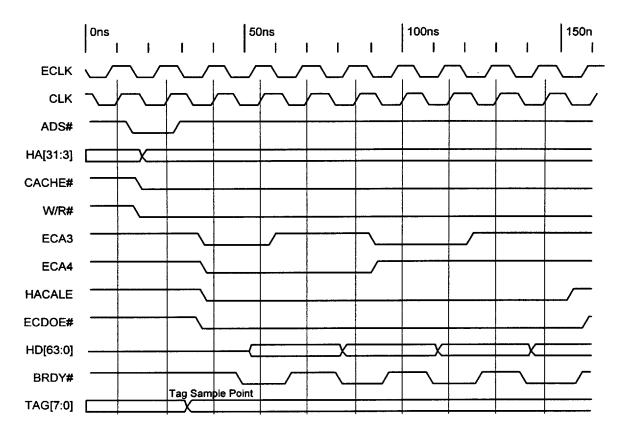

| Figure 4-6  | L2 Cache Read Hit Cycle Async. SRAMs (Single Bank)                              | 64 |

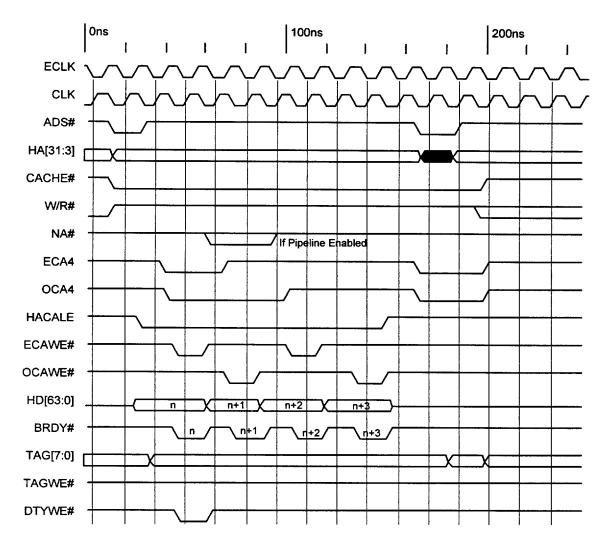

| Figure 4-7  | Write Hit Burst Cycle for Write-Back Mode - Async. SRAM (Double Bank)           | 65 |

| Figure 4-8  | Write Hit Burst Cycle for Write-Back Mode (Single Bank) - Async. SRAM           | 66 |

| Figure 4-9  | Write Hit Burst Cycle for Write-Back Mode - Sync. SRAM                          | 67 |

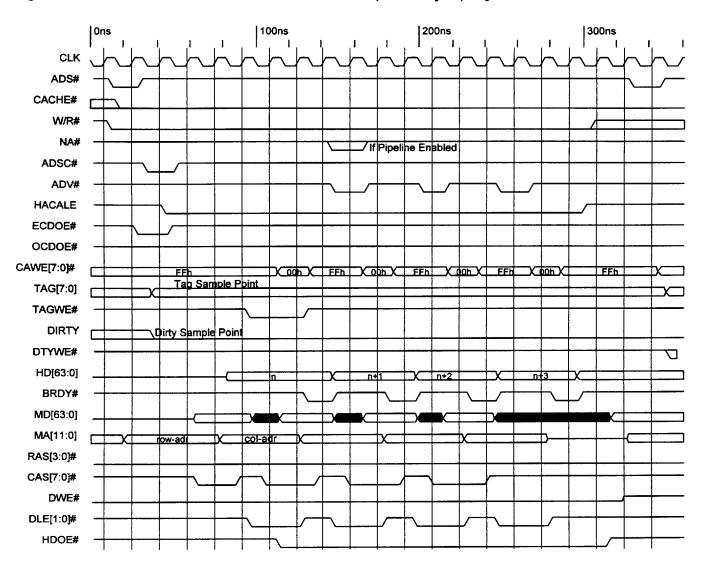

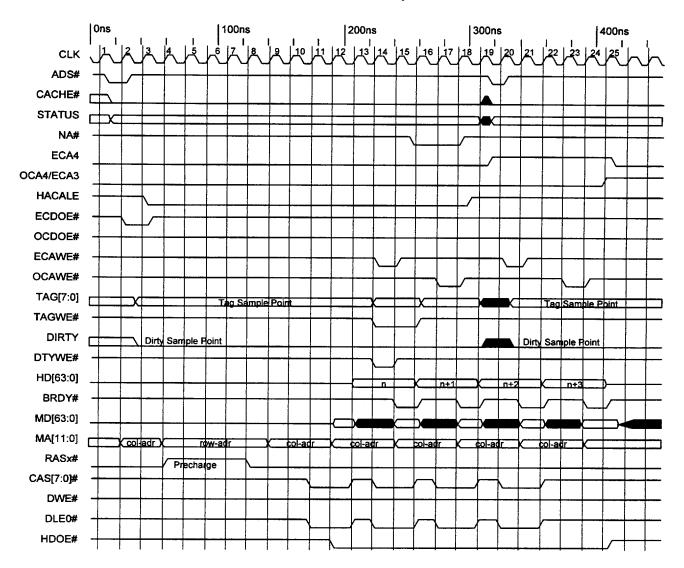

| Figure 4-10 | L2 Cache Read Miss Clean Burst of 8-3-3-3 (Linefill Cycle) - Async. SRAMs       | 69 |

| Figure 4-11 | L2 Cache Read Miss Clean Burst of 8-3-3-3 (Linefill Cycle) - Sync. SRAMs        | 70 |

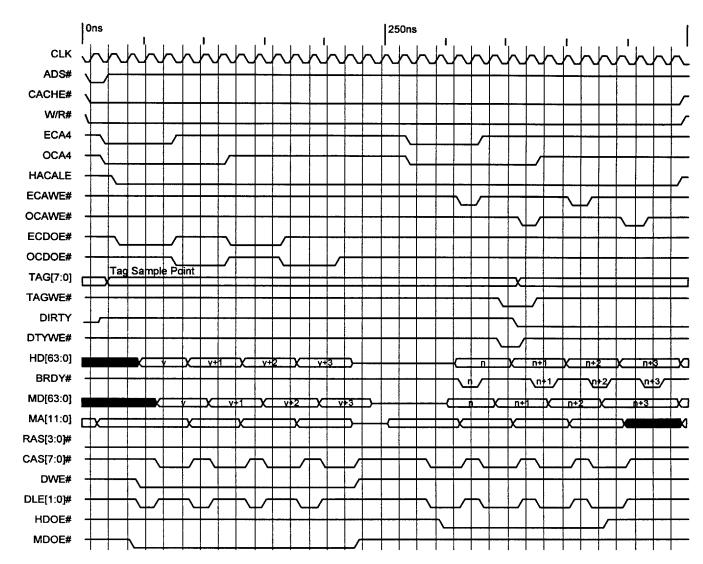

| Figure 4-12 | L2 Cache Read Miss Dirty Cycle - Async. SRAMs                                   | 71 |

| Figure 4-13 | L2 Cache Write Miss Burst Cycle (4-3-3-3) - Async. SRAMs                        | 72 |

| Figure 4-14 | L2 Cache Write Miss Burst Cycle - Sync. SRAMs                                   | 73 |

| Figure 4-15 | 82C557 Internal Tag Comparator Block Diagram                                    | 75 |

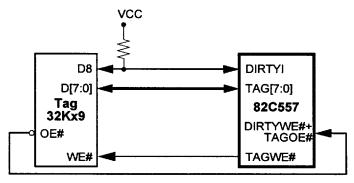

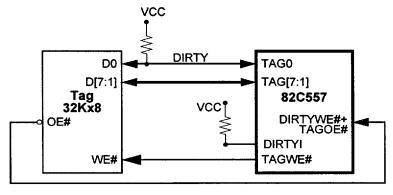

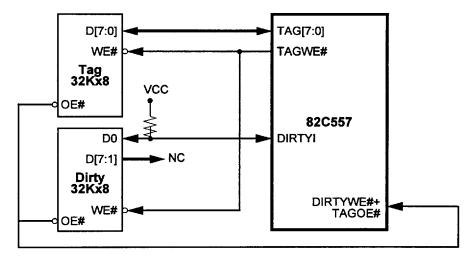

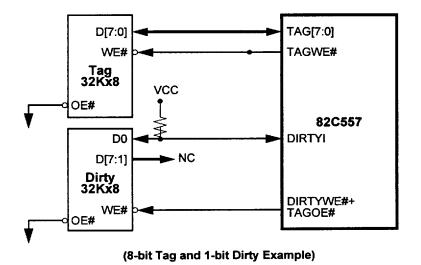

| Figure 4-16 | 32Kx8 and 32Kx1 Split Tag/Dirty RAM Implementation                              | 77 |

| Figure 4-17 | 32Kx9 Combined Tag/Dirty RAM Implementation                                     | 77 |

| Figure 4-18 | 32Kx8 Combined Tag/Dirty RAM Implementation                                     | 77 |

| Figure 4-19 | 32Kx8 and 32Kx8 Combined Tag/Dirty RAM Implementation                           | 78 |

| Figure 4-20 | 32Kx8 and 32Kx8 Combined Tag/Dirty RAM Implementation (Separate Devices)        | 78 |

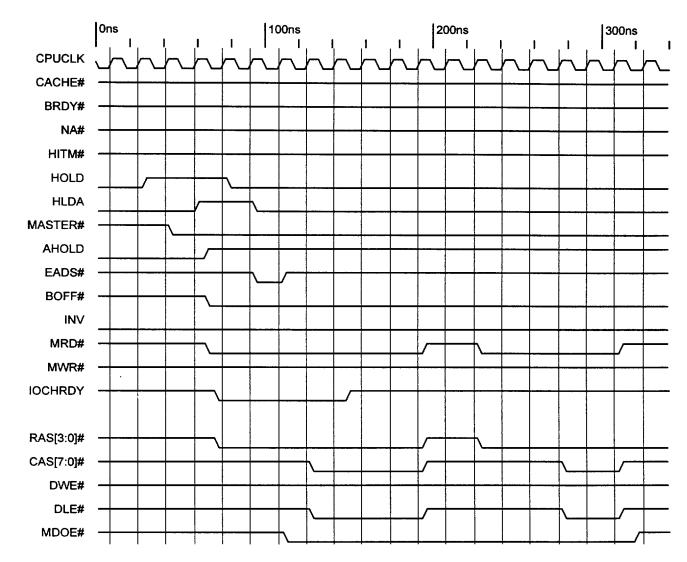

| Figure 4-21 | ISA DMA/Master Read (L1 cache with non-modified line)                           | 81 |

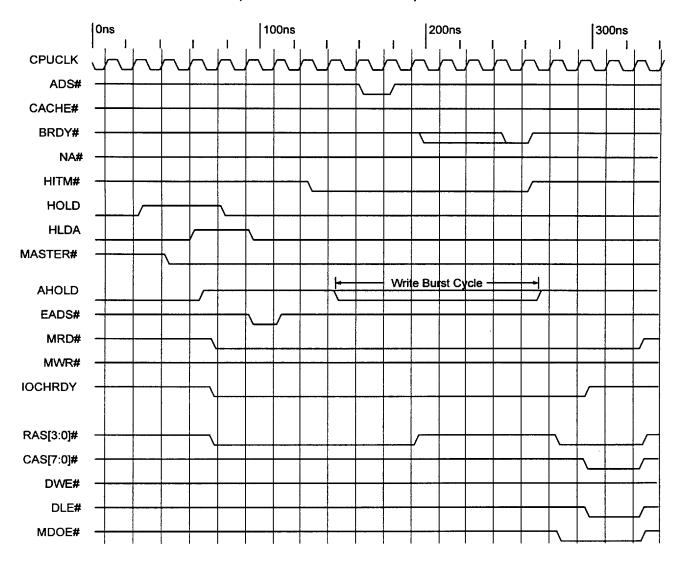

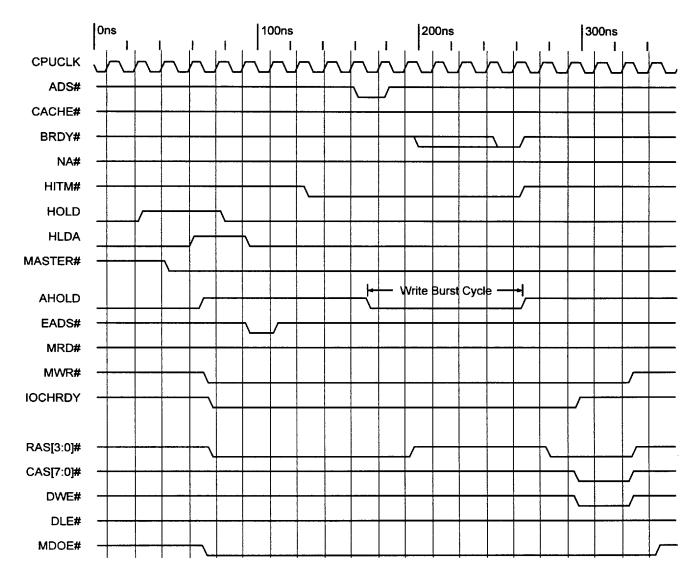

| Figure 4-22 | ISA DMA/Master Read (L1 cache with modified line)                               | 82 |

| Figure 4-23 | ISA DMA/Master Write (L1 cache with modified line)                              | 83 |

|             |                                                                                 |    |

912-3000-032 Revision: 1.0 Page xi

■ 9004196 0001157 1TT ■

## **List of Figures (cont.)**

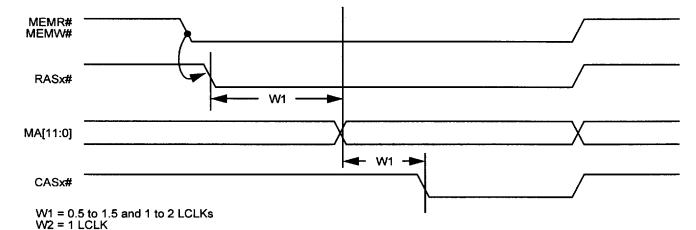

| Figure 4-24 | DRAM Read Page Miss with RAS Active Read Cycle                              | 100 |

|-------------|-----------------------------------------------------------------------------|-----|

| Figure 4-25 | DRAM Page Miss with RAS Active Write Cycle                                  | 101 |

| Figure 4-26 | ISA Master Synchronization                                                  | 103 |

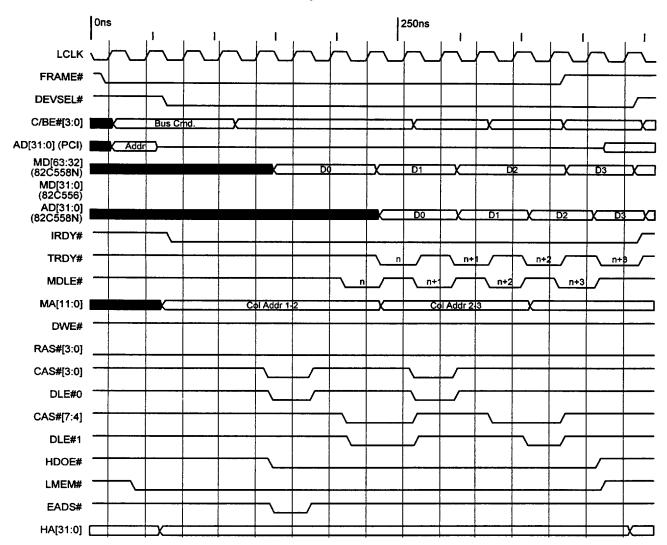

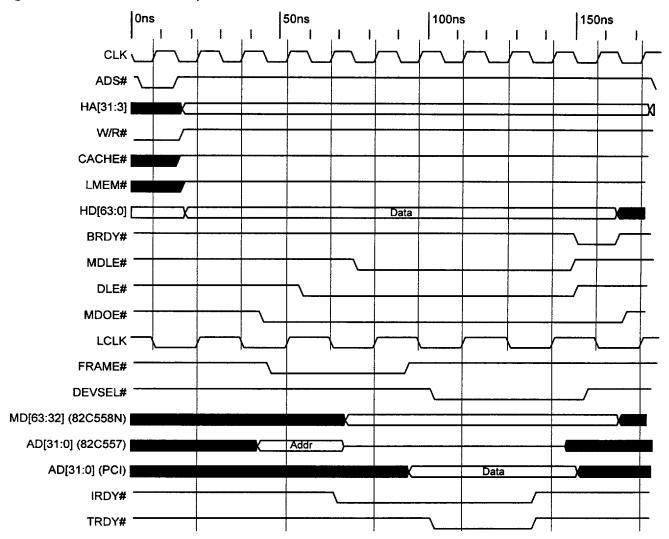

| Figure 4-27 | PCI Master Read from Local Memory                                           | 110 |

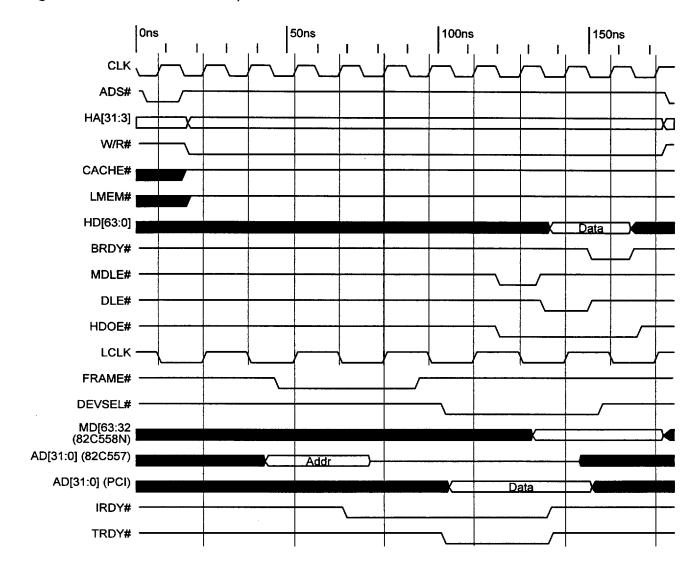

| Figure 4-28 | CPU Read from PCI, 32 Bits                                                  | 111 |

| Figure 4-29 | CPU Write to PCI, 32 Bits                                                   | 112 |

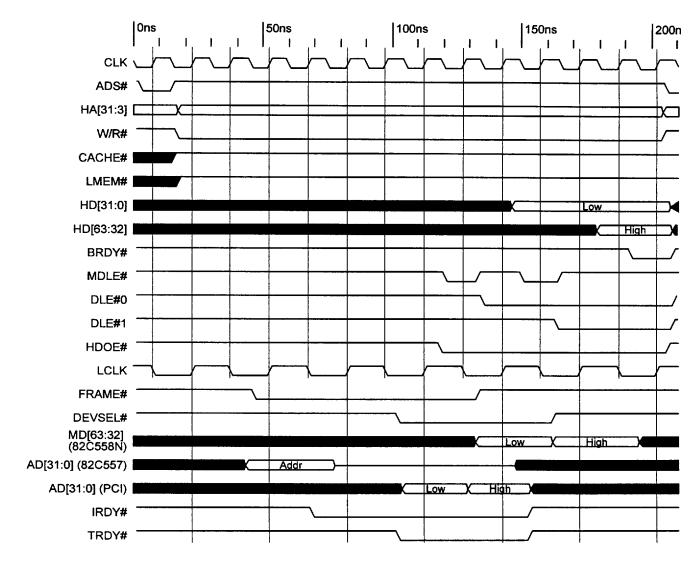

| Figure 4-30 | CPU Read from PCI, 64 Bits                                                  | 113 |

| Figure 4-31 | CPU Read from VL Slave                                                      | 114 |

| Figure 4-32 | CPU Write to VL Slave                                                       | 115 |

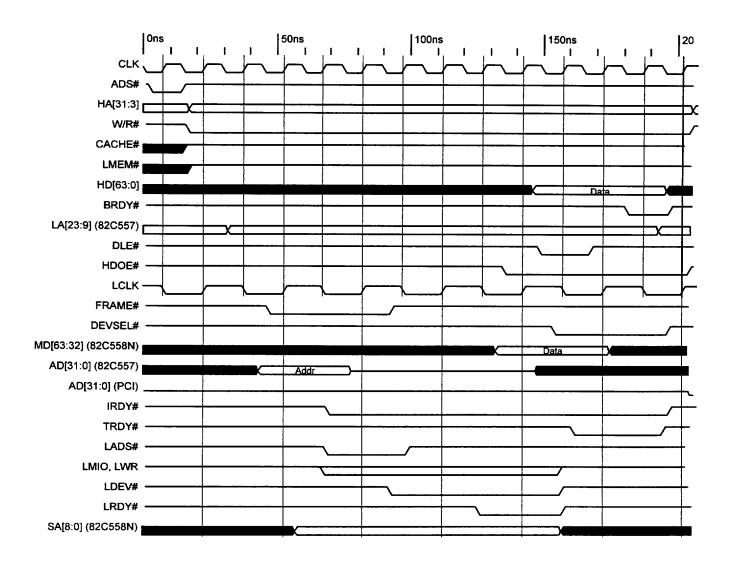

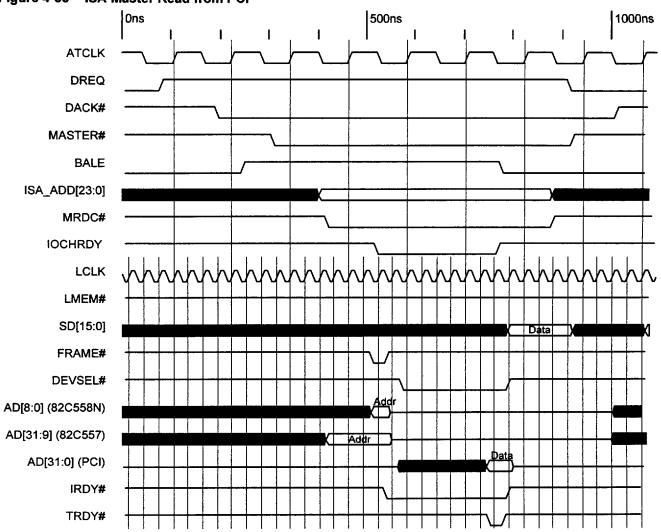

| Figure 4-33 | ISA Master Read from PCI                                                    | 116 |

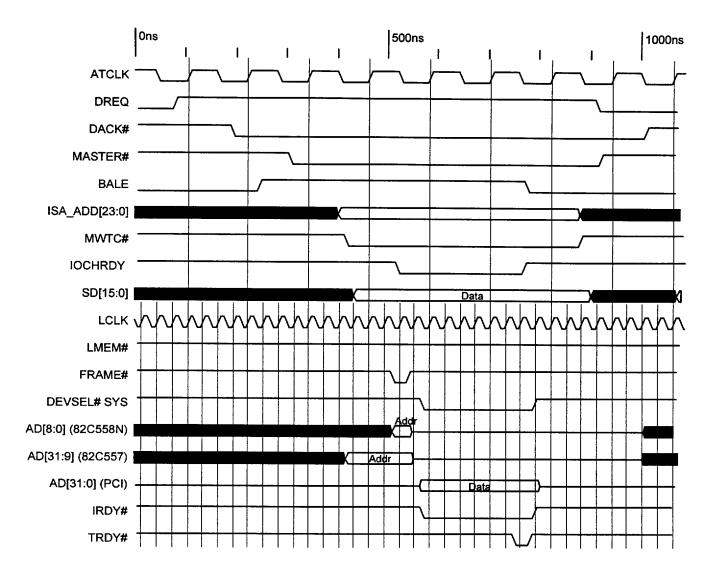

| Figure 4-34 | ISA Master Write to PCI                                                     | 117 |

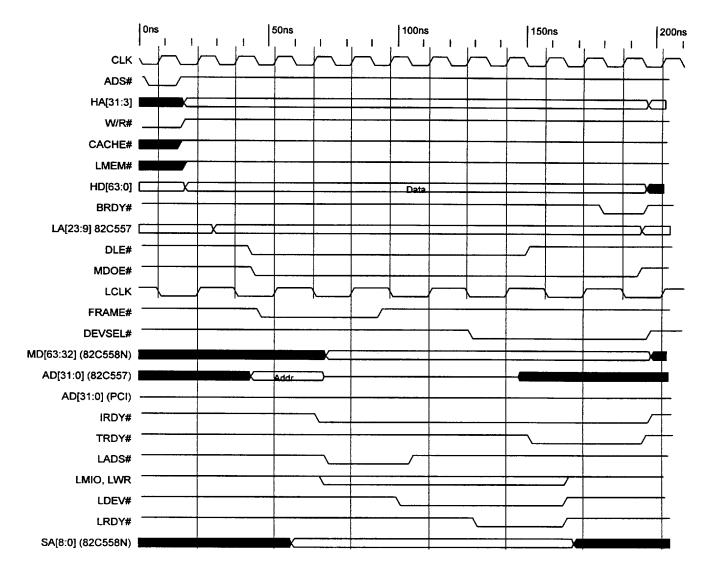

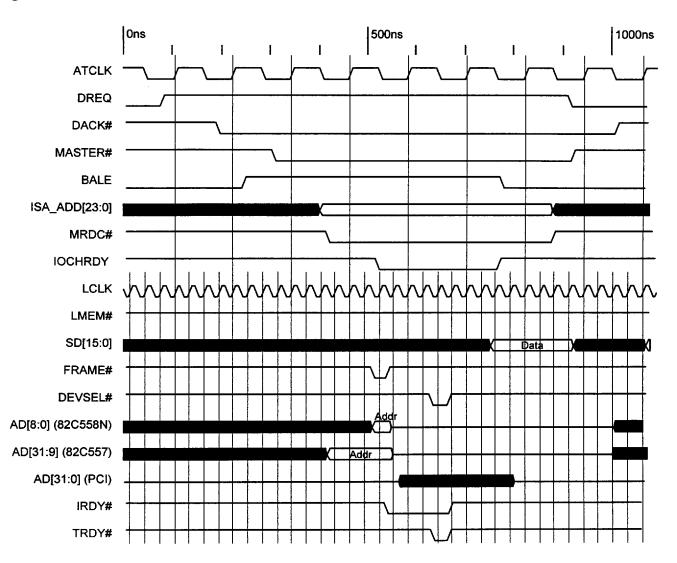

| Figure 4-35 | ISA Master Read from ISA Slave                                              | 118 |

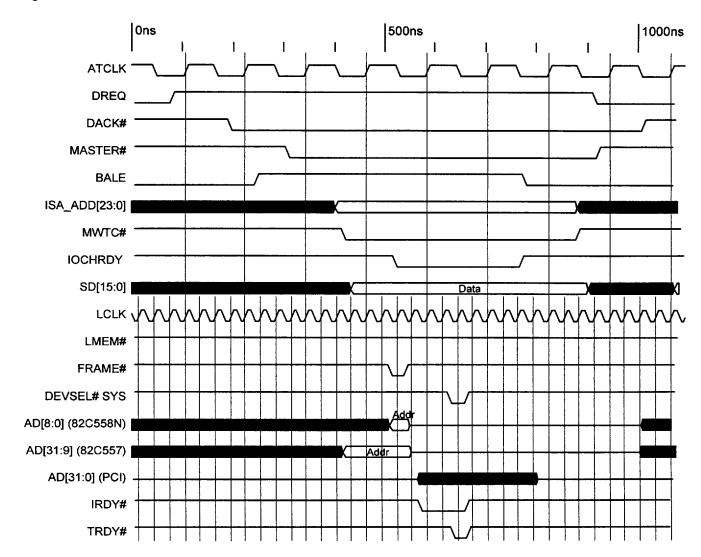

| Figure 4-36 | ISA Master Write to ISA Slave                                               | 119 |

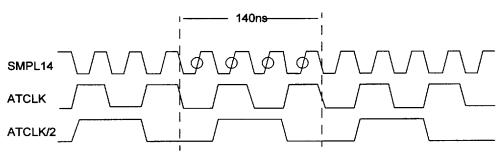

| Figure 4-37 | Multiplexed Input Sampling Points                                           | 122 |

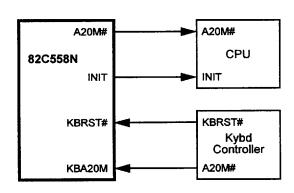

| Figure 4-38 | Connections with Keyboard Emulation Disabled                                | 131 |

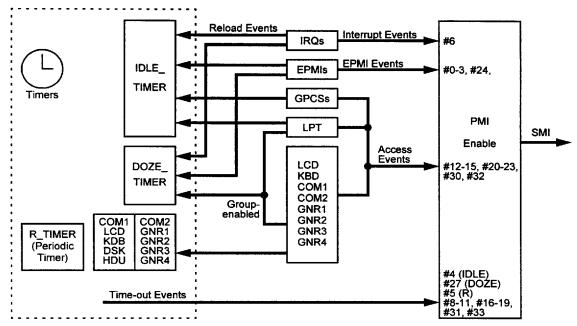

| Figure 4-39 | Activity Monitoring Block Diagram                                           | 137 |

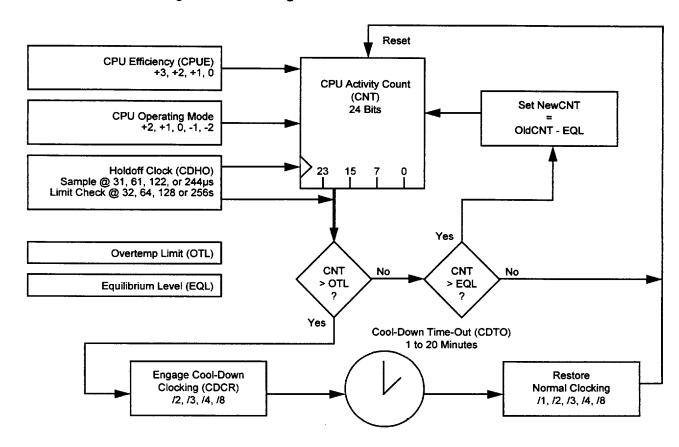

| Figure 4-40 | Thermal Management Block Diagram                                            | 157 |

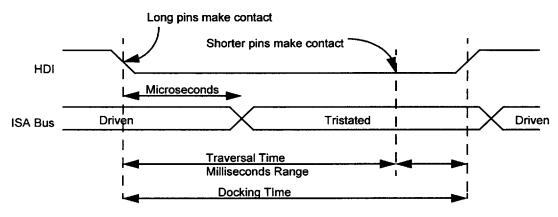

| Figure 4-41 | Insertion Times                                                             | 182 |

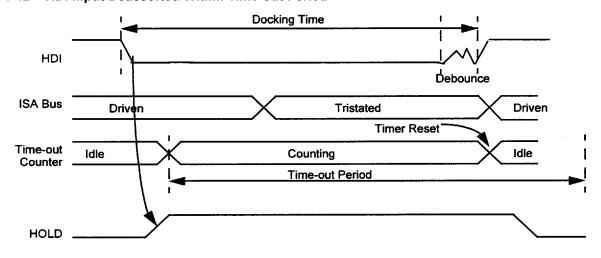

| Figure 4-42 | HDI Input Deasserted Within Time-out Period                                 | 182 |

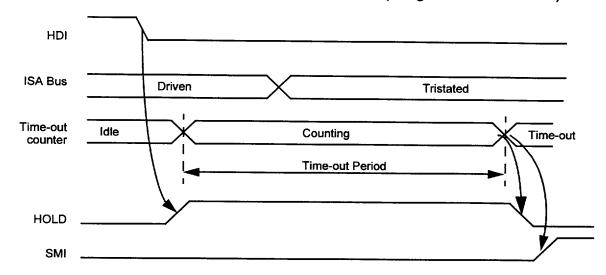

| Figure 4-43 | HDI Input Not Deasserted Within Time-out Period (SMI generated on time-out) | 183 |

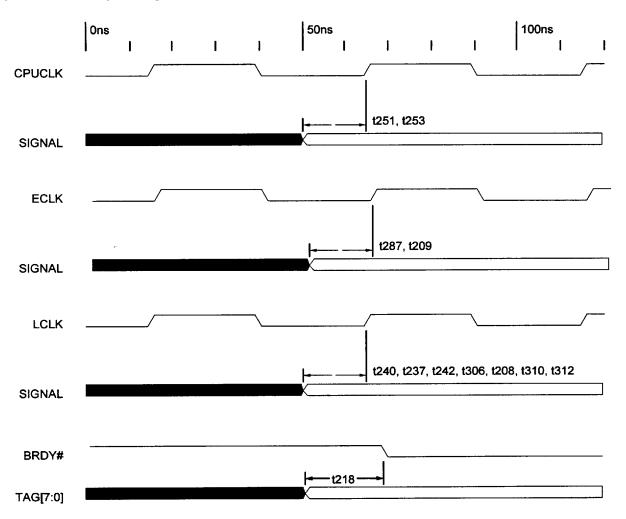

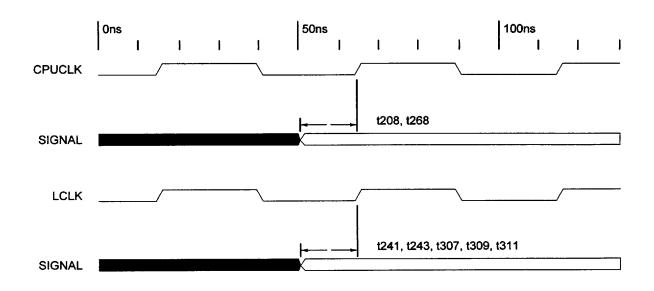

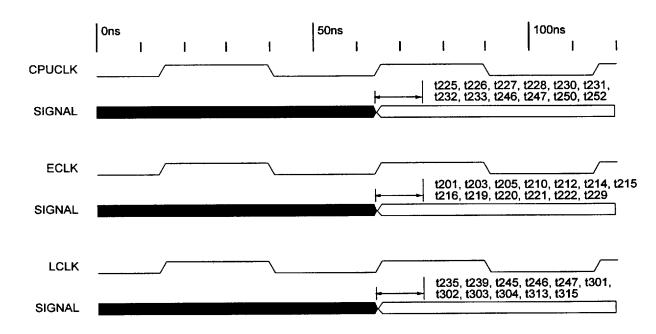

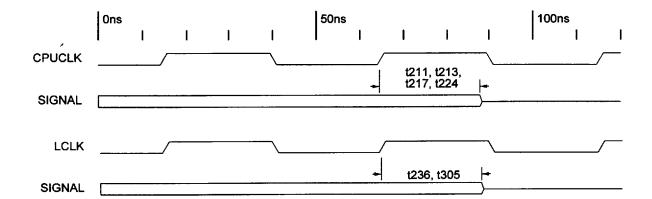

| Figure 6-1  | Setup Timing Waveform                                                       | 224 |

| Figure 6-2  | Hold Timing Waveform                                                        | 225 |

| Figure 6-3  | Output Delay Timing Waveform                                                | 225 |

| Figure 6-4  | Float Delay Timing Waveform                                                 | 226 |

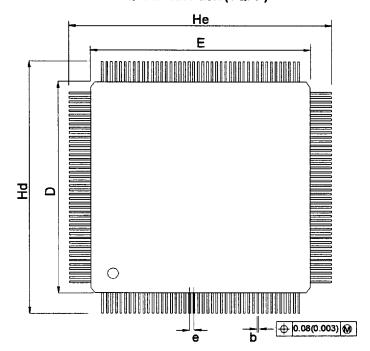

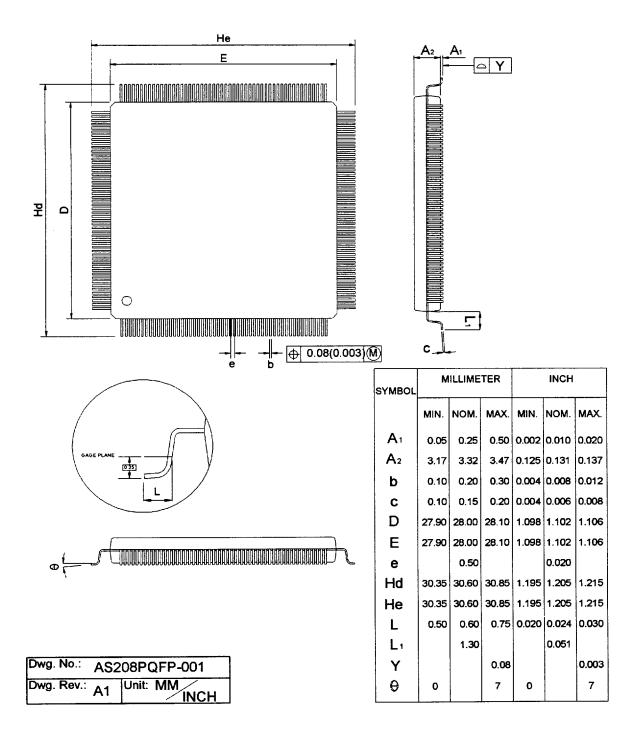

| Figure 8-1  | 176-Pin Thin Quad Flat Pack (TQFP)                                          | 233 |

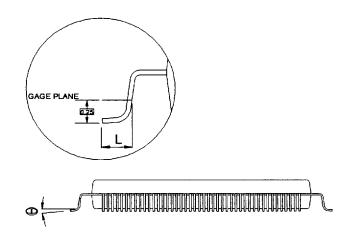

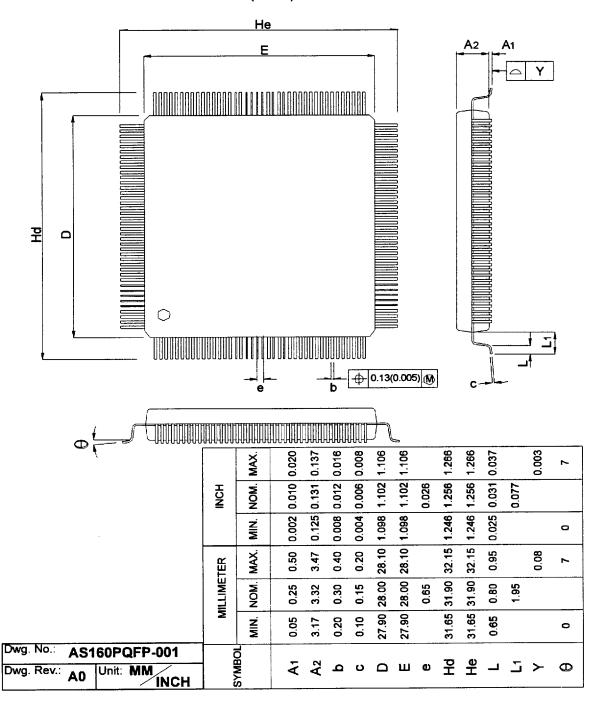

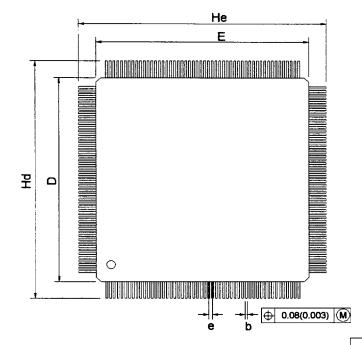

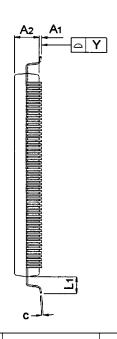

| Figure 8-2  | 160-Pin Plastic Quad Flat Pack (PQFP)                                       | 234 |

| Figure 8-3  | 208-Pin Thin Quad Flat Pack (TQFP)                                          | 235 |

| Figure 8-4  | 208-Pin Plastic Quad Flat Package (PQFP)                                    | 236 |

|             |                                                                             |     |

Page xii

Revision: 1.0

912-3000-032

9004196 0001158 036

# **List of Tables**

| Table 3-1  | Signal Definitions Legend                                   | 6  |

|------------|-------------------------------------------------------------|----|

| Table 3-2  | 82C556 Numerical Pin Cross-Reference List (176-Pin TQFP)    |    |

| Table 3-3  | 82C556 Alphabetical Pin Cross-Reference List (176-Pin TQFP) |    |

| Table 3-4  | 82C556 Numerical Pin Cross-Reference List (160-Pin PQFP)    |    |

| Table 3-5  | 82C556 Alphabetical Pin Cross-Reference List (160-Pin PQFP) |    |

| Table 3-6  | 82C556 Encoded Commands                                     | 16 |

| Table 3-7  | 82C557 Numerical Pin Cross-Reference List                   | 18 |

| Table 3-8  | 82C557 Alphabetical Pin Cross-Reference List                | 20 |

| Table 3-9  | 82C557 Pin Status During Suspend                            | 32 |

| Table 3-10 | 82C558N Numerical Pin Cross-Reference List                  | 35 |

| Table 3-11 | 82C558N Alphabetical Pin Cross-Reference List               | 37 |

| Table 3-12 | 82C558N Group-Wise Programmable Pins - Group 1              | 53 |

| Table 3-13 | 82C558N Group-Wise Programmable Pins - Group 2              | 53 |

| Table 3-14 | 82C558N Group-Wise Programmable Pins - Group 3              | 53 |

| Table 3-15 | 82C558N Group-Wise Programmable Pins - Group 4              | 54 |

| Table 3-16 | 82C558N Pin-Wise Programmable Pin #1                        | 54 |

| Table 3-17 | 82C558N Pin-Wise Programmable Pin #2                        | 54 |

| Table 3-18 | IDE Support Signals                                         | 54 |

| Table 3-19 | 82C558N Pin Status During Suspend                           | 55 |

| Table 4-1  | Burst Type Select Register Bit                              | 59 |

| Table 4-2  | Burst Modes                                                 | 60 |

| Table 4-3  | SRAM Bank Support Register Bit                              | 61 |

| Table 4-4  | Register Bits Associated with Write Policies                | 74 |

| Table 4-5  | Tag Compare Table                                           | 75 |

| Table 4-6  | Tag/Dirty RAM Control Register Bits                         | 76 |

| Table 4-7  | Test Mode Selection/Control Bits                            | 79 |

| Table 4-8  | DMA/Master Read Cycle Summary                               | 80 |

| Table 4-9  | DMA/Master Write Cycle Summary                              | 80 |

| Table 4-10 | Cacheability Area Control Bits                              | 85 |

| Table 4-11 | Shadow Control Register Bits                                | 86 |

| Table 4-12 | SYSCFG 08h[0]                                               |    |

| Table 4-13 | Cacheability Methods                                        |    |

| Table 4-14 | SRAM Requirements                                           |    |

|            |                                                             |    |

912-3000-032

Revision: 1.0

Page xi

■ 9004196 0001159 T72 ■

## List of Tables (cont.)

| Table 4-15 | Signal Functionality for Synchronous SRAM Implementation                              | 8   |

|------------|---------------------------------------------------------------------------------------|-----|

| Table 4-16 | Register Bits Associated with SRAM Support                                            | 89  |

| Table 4-17 | Cache Module Register Support                                                         | 91  |

| Table 4-18 | Data SRAM Asynchronous Configurations                                                 | 92  |

| Table 4-19 | Data SRAM (Asynchronous) and Tag SRAM Speed Requirements                              | 92  |

| Table 4-20 | Data SRAM (Synchronous) Configurations                                                | 92  |

| Table 4-21 | Data SRAM (Synchronous) Speed Requirements                                            | 92  |

| Table 4-22 | Tag SRAM Speed Requirements for Synchronous SRAMs                                     | 92  |

| Table 4-23 | SRAM Comparisons                                                                      | 93  |

| Table 4-24 | Skew Control Bits                                                                     | 93  |

| Table 4-25 | Full Memory Decode Mode and RAS Selection Bits                                        | 94  |

| Table 4-26 | DRAM Configuration Related Register Bits                                              | 95  |

| Table 4-27 | DRAM Row/Column MA to Address Bit Map                                                 | 96  |

| Table 4-28 | DRAM Programmable Control                                                             | 96  |

| Table 4-29 | Drive Strength Control Bit                                                            | 97  |

| Table 4-30 | DRAM Operation Programming Bits                                                       | 98  |

| Table 4-31 | DRAM Timing Mode Summary                                                              | 99  |

| Table 4-32 | DRAM Parity and Refresh Logic Associated Register Bits                                | 102 |

| Table 4-33 | DRAM Hole Control Related Registers                                                   | 104 |

| Table 4-34 | Register Bits Associated with Backward Compatibility for OPTi's 82C546/82C547 Chipset | 105 |

| Table 4-35 | DRAM Configurations                                                                   | 105 |

| Table 4-36 | ISA and VL Bus Space Access Bits                                                      | 106 |

| Table 4-37 | Byte/Word Merge Feature Register Bits                                                 | 108 |

| Table 4-38 | Delay Back-to-Back ISA Cycle Register Bit                                             | 120 |

| Table 4-39 | Registers Associated with ROMCS#                                                      | 121 |

| Table 4-40 | Internal IPC Configuration Bits.                                                      | 122 |

| Table 4-41 | INTC1 Initialization Command Words                                                    | 123 |

| Table 4-42 | INTC2 Initialization Command Words                                                    | 123 |

| Table 4-43 | INTC1 and INTC2 Operational Command Words.                                            | 124 |

| Table 4-44 | Interrupt Controller Shadow Register Index Values                                     | 125 |

| Table 4-45 | DMA Address and Count Registers                                                       | 125 |

| Table 4-46 | DMA Control and Status Registers                                                      | 125 |

|            |                                                                                       |     |

Page xiv Revision: 1.0 912-3000-032

9004196 0001160 794 📟

## List of Tables (cont.)

| Table 4-47 | DMAC1 Control and Status Bits                              | 126 |

|------------|------------------------------------------------------------|-----|

| Table 4-48 | DMAC2 Control and Status Bits                              | 127 |

| Table 4-49 | DMA Commands                                               | 127 |

| Table 4-50 | Timer Control and Status Registers                         | 128 |

| Table 4-51 | Timer Control Bits                                         | 128 |

| Table 4-52 | Timer Support Shadow Registers                             | 129 |

| Table 4-53 | RTC Index Register - I/O Port 070h (WO)                    | 130 |

| Table 4-54 | RTC Index Shadow Register - Index 98h (RO)                 | 130 |

| Table 4-55 | IRQ8 Polarity Bit - SYSCFG 50h                             | 130 |

| Table 4-56 | Keyboard Emulation Disable Bit                             | 131 |

| Table 4-57 | IDE Interface Control                                      | 133 |

| Table 4-58 | Automatic Cycle Settings Available through SYSCGF ACh[7:4] | 133 |

| Table 4-59 | 611 Register Set                                           | 134 |

| Table 4-60 | Operation with Primary I/O Range Selected                  | 135 |

| Table 4-61 | Operation with Secondary I/O Range Selected                | 135 |

| Table 4-62 | Timer Control Bits                                         | 138 |

| Table 4-63 | Time Interval Choices Applicable to _TIMER Settings        | 139 |

| Table 4-64 | Timer Clock Source Selection Registers                     | 139 |

| Table 4-65 | Timer Source Registers                                     | 140 |

| Table 4-66 | ACCESS Events and their Enabling Bit Locations             | 141 |

| Table 4-67 | PMU Control Registers                                      | 142 |

| Table 4-68 | General Purpose Access 1, 2, 3, and 4 Registers            | 143 |

| Table 4-69 | Activity Tracking Registers                                | 145 |

| Table 4-70 | Idle Reload Source Registers                               | 146 |

| Table 4-71 | External PMI Source Summary                                | 147 |

| Table 4-72 | EPMI Programming Registers                                 | 148 |

| Table 4-73 | Power Management Event Status                              | 149 |

| Table 4-74 | Register Bits Associated with STPCLK# Feature              | 150 |

| Table 4-75 | Doze Reset Bit                                             | 151 |

| Table 4-76 | Register Bits that Select Doze Mode Reset Events           | 152 |

| Table 4-77 | Hardware and Software Doze Mode Registers                  | 154 |

| Table 4-78 | SMI Generation on Doze Time-Out                            | 155 |

|            |                                                            |     |

912-3000-032

Revision: 1.0

Page xv

**- 9004196 0001161 620**

## List of Tables (cont.)

| Table 4-79  | PCI Bus Doze Reset Registers                                           | 155 |

|-------------|------------------------------------------------------------------------|-----|

| Table 4-80  | Operating Mode Power Levels                                            | 156 |

| Table 4-81  | Thermal Management Registers                                           | 159 |

| Table 4-82  | Suspend Control Register Bits                                          | 161 |

| Table 4-83  | Suspend Mode Power Saving Feature Bits                                 | 161 |

| Table 4-84  | SUS/RES# and Resume Event Associated Register Bits                     | 163 |

| Table 4-85  | Resume Source (Read Only)                                              | 163 |

| Table 4-86  | Keeper Resistors, 0V CPU Suspend, and Stopping IPC Clock Register Bits | 165 |

| Table 4-87  | Power Control Register Bits                                            | 166 |

| Table 4-88  | Resume Recovery and Suspend Auto Toggle Register Bits                  | 167 |

| Table 4-89  | Programmable Chip Select Registers                                     | 168 |

| Table 4-90  | SMI Sources                                                            | 169 |

| Table 4-91  | SMIACT# Interpretation                                                 | 170 |

| Table 4-92  | SMRAM Access Control Bits                                              | 171 |

| Table 4-93  | Software SMI Enable Register Bits                                      | 172 |

| Table 4-94  | Current and Next Access Registers                                      | 173 |

| Table 4-95  | INTRGRP IRQ Select Register Bits                                       | 174 |

| Table 4-96  | DMA DRQ Trap SMI Register Bits                                         | 174 |

| Table 4-97  | SMI Event Enable Registers                                             | 175 |

| Table 4-98  | SMI Service Registers                                                  | 177 |

| Table 4-99  | I/O SMI Trap Indication Registers                                      | 178 |

| Table 4-100 | Utility Registers                                                      | 179 |

| Table 4-101 | Hot Docking Control Register Bits                                      | 180 |

| Table 5-1   | Register Locations and Access Mechanisms Summary                       | 184 |

| Table 5-2   | 82C557 PCI Configuration Registers - PCIDV0 00h-43h                    | 185 |

| Table 5-3   | 82C557 System Control Registers - SYSCFG 00h-19h                       | 187 |

| Table 5-4   | 82C558N PCI Configuration Registers - PCIDV1 00h-3Fh                   | 194 |

| Table 5-5   | 82C558N System Control Registers - PCIDV1 40h-FFh                      | 196 |

| Table 5-6   | 82C558N Power Management Registers: SYSCFG 40h-F2h                     | 200 |

| Table 5-7   | System I/O Space Register Map                                          |     |

| Table 7-1   | 82C556 NAND Tree Test Mode Pins for 176-Pin TQFP                       |     |

| Table 7-2   | 82C556 NAND Tree Test Mode Pins for 160-Pin PQFP                       | 229 |

|             |                                                                        |     |

Page xvi Revision: 1.0

912-3000-032

**9**004196 0001162 567 **9**

## List of Tables (cont.)

| Table 7-3 | 82C557 NAND Tree Test Mode Pins     | 230 |

|-----------|-------------------------------------|-----|

| Table 7-4 | Drive High/Drive Low Test Mode Pins | 231 |

| Table 7-5 | 82C558N NAND Tree Test Mode Pins    | 232 |

**OPTi**

912-3000-032

Revision: 1.0

Page xvii

■ 9004196 0001163 4T3 ■

## **Viper Notebook Chipset**

#### 1.0 Features

#### **CPU Interface**

- Fully supports Intel's 3.3V Pentium™ Processor and dual processor configuration at 50, 60, and 66.667MHz

- Supports P54C<sup>™</sup>, P55C<sup>™</sup>, K5<sup>™</sup>, and M1<sup>™</sup> processors

- Supports the Cyrix® M1 Processor linear burst mode

- Three chip solution:

- 82C556 DBC (Data Buffer Controller) in a 160-pin PQFP (Plastic Quad Flat Pack) or 176-pin TQFP (Thin Quad Flat Pack)

- 82C557 SYSC (System Controller) in a 208-pin PQFP or TQFP

- 82C558N IPC (Integrated Peripherals Controller) in a 208-pin PQFP or TQFP

- Supports CPU address pipelining

#### Cache Interface

Write-back/write-through, direct-mapped cache with size selections: 64KB, 128KB, 256KB, 1MB and 2MB

- Support for synchronous and asynchronous SRAMs, pipelined synchronous SRAMs, and Intel standard BSRAMs (BiCMOS SRAMs)

- Support for the Sony SONIC-2WP™ Cache Module

- · Programmable cache write policy:

- Write-back

- Write-through

- Adaptive write-back

- Built-in tag auto-invalidation circuitry

- Fully programmable 3-2-2-2 asynchronous cache burst read/write cycles, 3-1-1-1/2-1-1-1 burst read/write support at 66/50MHz

- Options for cacheable, write protected, system and video BIOS

#### **DRAM Interface**

Supports six banks of 64-bit wide DRAMs with 256KB, 512KB, 1MB, 2MB, 4MB, 8MB and 16MB addressing page mode DRAMs

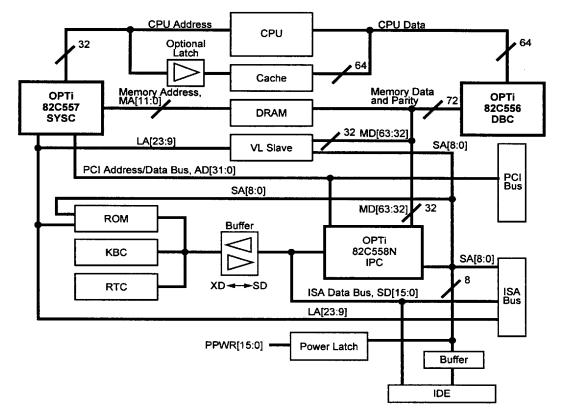

Figure 1-1 Viper-N System Block Diagram

912-3000-032 Revision: 1.0 Page 1

## Features (cont.)

- Supports DRAM configurations up to 512MB

- Supports 3-3-3 pipelined DRAM burst cycles

- 64-bit DRAM post write buffer

- Programmable drive currents for the DRAM control signals

- · Hidden refresh with CAS-before-RAS refresh supported

- Support for two programmable non-cacheable memory regions

#### **PCI** Interface

- Interfaces the CPU and standard buses to both Peripheral Component Interconnect (PCI) and VL bus operating in synchronous/asynchronous modes, with VL bus always running at PCI bus operating frequency

- Supports three PCI masters, one VL slave, and six ISA peripherals

- Supports PCI pre-snoop for PCI masters

- PCI byte/word merge support for CPU accesses to PCI bus, and support for PCI pre-fetch

- · Burst mode PCI accesses to local memory supported

#### Miscellaneous

- Integrated two drive VL-based IDE controller

- Self-refresh supported during Suspend mode

- Support for flash ROM

- Shadow RAM option

- Transparent 8042 emulation for fast CPU reset and Gate A20 generation

- Supports Port 092h, fast Gate A20 and fast reset

- Includes a fully integrated 82C206 with external real-time clock (RTC) interface

#### 2.0 Overview

The OPTi Viper (82C556/557/558N) Notebook Chipset provides a highly integrated solution for fully compatible, high performance PC/AT platforms based on Intel's 3.3V Pentium Processor, Cyrix's M1 Processor, and AMD's K5 Processor. The chipset provides 64-bit core logic, integrated PCI and VL support, and sophisticated power management features. This highly integrated approach supplies the foundation for a cost effective platform without compromising performance. Its feature set furnishes an array of control and status monitoring options that are accessed through a simple and straightforward interface. All major BIOS vendors provide extensive software hooks that allow system designers to integrate their own special features with minimal effort.

The Viper Notebook Chipset is comprised of three chips:

- · 82C556 Data Buffer Controller (DBC),

- 82C557 System Controller (SYSC).

- 82C558N Integrated Peripherals Controller (IPC)

Page 2

Revision: 1.0

912-3000-032

**=** 9004196 0001165 276 **=**

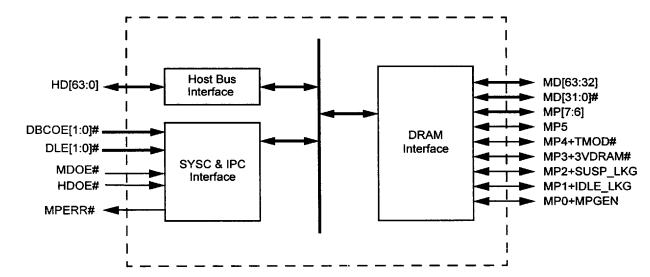

### 2.1 82C556 Data Buffer Controller (DBC)

The 82C556 DBC performs the task of buffering the CPU to the DRAM memory data path. It also performs parity checking.

- CPU to memory data buffer

- · CPU to local bus buffer

- · Memory to local bus buffer

- 176-pin TQFP or 160-pin PQFP

Figure 4-1 shows a block diagram of the 82C556 DBC.

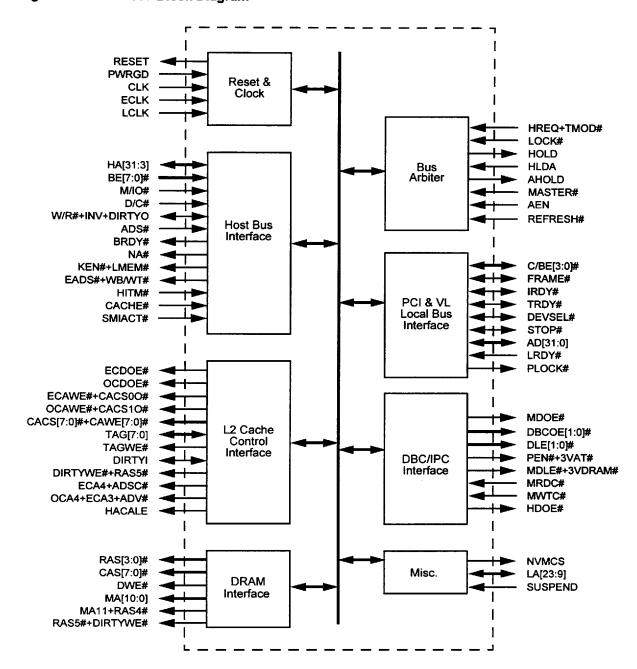

#### 2.2 82C557 System Controller (SYSC)

The 82C557 SYSC provides the control functions for the host CPU interface, the 64-bit Level-2 (L2) cache, the 64-bit DRAM bus, the VL bus interface, and the PCI interface. The SYSC also controls the data flow between the CPU bus, the DRAM bus, the local buses, and the 8/16-bit ISA bus. The SYSC interprets and translates cycles from the CPU, PCI bus master, ISA master, and DMA to the host memory, local bus slave, PCI bus slave, or ISA bus devices.

- · 3.3V CPU interface

- DRAM controller

- · L2 cache controller

- · L1 cache controller

- PCI interface

- · Arbitration logic

- Data bus buffer control (memory data bus to and from host data bus)

- · VL bus interface

- · 208-pin PQFP or TQFP

Figure 4-2 shows a block diagram of the 82C557 SYSC.

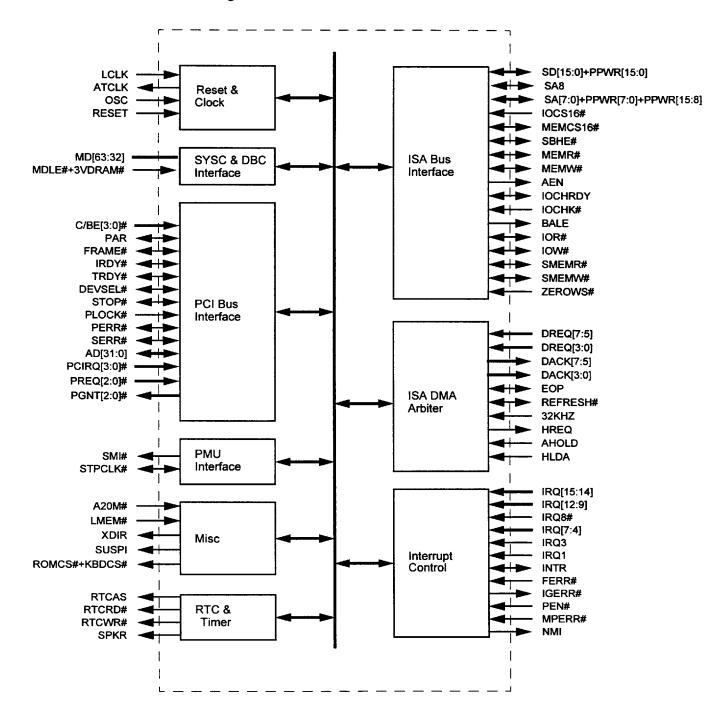

# 2.3 82C558N Integrated Peripherals Controller (IPC)

The 82C558N Integrated Peripherals Controller (IPC) contains the ISA bus controller and includes an 82C206, RTC interface, DMA controller, PCI arbitration logic, and a sophisticated system power management unit. It also includes buffers and steering control for the 32-bit PCI interface.

- · ISA bus controller

- Integrated 82C206 IPC

- · CPU thermal management functions

- · System power management functions

- · PCI local bus interface

- Keyboard emulation of A20M# and CPU warm reset

- · Port B and Port 92h Register

- · 208-pin PQFP or TQFP

Figure 4-3 shows a block diagram of the 82C558 IPC.

Figure 2-1 82C556 Block Diagram

OPTi

912-3000-032 Revision: 1.0

Page 3

**9**004196 0001166 102 **=**

Figure 2-2 82C557 Block Diagram

Page 4 Revision: 1.0

912-3000-032

**--** 9004196 0001167 049 **--**

Figure 2-3 82C558N Block Diagram

912-3000-032 Revision: 1.0 Page 5

■ 9004196 0001168 T85 ■

## 3.0 Signal Definitions

#### 3.1 Terminology/Nomenclature Conventions

The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name, the signal is asserted when at the high voltage level.

The terms "assertion" and "negation" are used extensively. This is done to avoid confusion when working with a mixture of "active low" and "active high" signals. The term "assert", or "assertion" indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term "negate", or "negation" indicates that a signal is inactive.

Some of the pin functions in the Viper-N Chipset are timemultiplexed, some have strap options, and some are selected via register programming. Included in each device's signal description is a column titled "Selected By" which explains how to implement/invoke the various functions that a pin may have. The terms PCIDV0, PCIDV1, and SYSCFG relate to registers located in the PCI Configuration Register Spaces and System Configuration Register Space of the Viper-N Chipset. Refer to Section 5.0, "Register Descriptions" for more details regarding these register spaces and their access mechanisms.

The tables in this section use several common abbreviations. Table 3-1 lists the mnemonics and their meanings. Note that TTL/CMOS/Schmitt-trigger levels pertain to inputs only. Outputs are driven at CMOS levels.

Table 3-1 Signal Definitions Legend

| Mnemonic | Description                       |  |

|----------|-----------------------------------|--|

| смоѕ     | CMOS-level compatible             |  |

| Ext      | External                          |  |

| G        | Ground                            |  |

| Int      | Internal                          |  |

| I/O      | Input/Output                      |  |

| OD       | Open drain                        |  |

| Р        | Power                             |  |

| PD       | Pull-down resistor                |  |

| PU       | Pull-up resistor                  |  |

| S        | Schmitt-trigger                   |  |

| TTL      | TTL-level compatible              |  |

| VCC3     | 3.3V power plane only             |  |

| VCC5     | 5.0V power plane only             |  |

| VCC_AT   | ISA bus power plane, 3.3V or 5.0V |  |

| VCC_MEM  | Memory power plane, 3.3V or 5.0V  |  |

Page 6 Revision: 1.0

912-3000-032

**==** 9004196 0001169 911 ==

912-3000-032

Revision: 1.0

Page 7

**==** 9004196 0001170 633 |

Table 3-2 82C556 Numerical Pin Cross-Reference List (176-Pin TQFP)

| Pin<br>No. | Pin Name     | Signal<br>Type | Drive<br>(mA)  | Power<br>Plane |

|------------|--------------|----------------|----------------|----------------|

| 1          | NC           |                |                |                |

| 2          | NC           |                |                |                |

| 3          | HD0          | VO-TTL         | 4              | VCC3           |

| 4          | HD1          | I/O-TTL        | 4              | VCC3           |

| 5          | HD2          | I/O-TTL        | 4              | VCC3           |

| 6          | HD3          | VO-TTL         | 4              | VCC3           |

| 7          | HD4          | VO-TTL         | 4              | VCC3           |

| 8          | HD5          | VO-TTL         | 4              | VCC3           |

| 9          | HD6          | VO-TTL         | 4              | VCC3           |

| 10         | HD7          | VO-TTL         | 4              | VCC3           |

| 11         | HD8          | I/O-TTL        | 4              | VCC3           |

| 12         | HD9          | VO-TTL         | 4              | VCC3           |

| 13         | HD10         | VO-TTL         | 4              | VCC3           |

| 14         | HD11         | VO-TTL         | 4              | VCC3           |

| 15         | HD12         | VO-TTL         | 4              | VCC3           |

| 16         | HD13         | VO-TTL         | 4              | VCC3           |

| 17         | HD14         | VO-TTL         | 4              | VCC3           |

| 18         | HD15         | VO-TTL         | 4              | VCC3           |

| 19         | HD16         | VO-TTL         | 4              | VCC3           |

| 20         | HD17         | VO-TTL         | 4              | VCC3           |

| 21         | HD18         | VO-TTL         | 4              |                |

| 22         | VCC3         | I-P            | +              | VCC3           |

|            |              |                | <del>   </del> | 1/000          |

| 23         | HD19         | I/O-TTL        | 4              | VCC3           |

| 24         | HD20         | VO-TTL         | 4              | VCC3           |

| 25         | GND          | I-G            | $\perp$        |                |

| 26         | GND          | I-G            | ļ              |                |

| 27         | HD21         | VO-TTL         | 4              | VCC3           |

| 28         | HD22         | I/O-TTL        | 4              | VCC3           |

| 29         | HD23         | VO-TTL         | 4              | VCC3           |

|            | HD24         | VO-TTL         | 4              | VCC3           |

| 31         | HD25         | VO-TTL         | 4              | VCC3           |

| 32         | VCC3         | I-P            |                |                |

| 33         | HD26         | VO-TTL         | 4              | VCC3           |

| 34         | HD27         | VO-TTL         | 4              | VCC3           |

| 35         | HD28         | VO-TTL         | 4              | VCC3           |

| 36         | HD29         | VO-TTL         | 4              | VCC3           |

| 37         | HD30         | VO-TTL         | 4              | VCC3           |

| 38         | HD31         | VO-TTL         | 4              | VCC3           |

| 39         | HD32         | VO-TTL         | 4              | VCC3           |

| 40         | HD33         | VO-TTL         | 4              | VCC3           |

| 41         | HD34         | VO-TTL         | 4              | VCC3           |

| 42         | HD35         | VO-TTL         | 4              | VCC3           |

| 43         | NC           |                | 1              |                |

| 44         | NC           |                | 1              |                |

| 45         | NC           |                | <del>  </del>  |                |

| 46         | NC           | <u> </u>       |                |                |

| 47         | HD36         | VO-TTL         | 4              | VCC3           |

|            | HD37         | VO-TTL         | 4              | VCC3           |

|            | HD38         | VO-TTL         | 4              | VCC3           |

|            | HD39         | VO-TTL         | 4              | VCC3           |

|            |              | VO-TTL         | 4              | VCC3           |

| _          | HD40<br>HD41 |                |                | VCC3           |

|            |              | VO-TTL         | 4              |                |

|            | HD42         | VO-TTL         | 4              | VCC3           |

|            | HD43         | VO-TTL         | 4              | VCC3           |

|            | HD44         | VO-TTL         | 4              | VCC3           |

|            | GND          | 1-G            |                | 11000          |

| _          | HD45         | VO-TTL         | 4              | VCC3           |

|            | HD46         | VO-TTL         | 4              | VCC3           |

|            | HD47         | VO-TTL         | 4              | VCC3           |

| 60         | HD48         | VO-TTL         | 4              | VCC3           |

| 61         | HD49         | VO-TTL         | 4              | VCC3           |

| Cross-Reference List (176-Pin 10 |                |                |               |                |

|----------------------------------|----------------|----------------|---------------|----------------|

| Pin<br>No.                       | Pin Name       | Signal<br>Type | Drive<br>(mA) | Power<br>Plane |

| 62                               | HD50           | VO-TTL         | 4             | VCC3           |

| 63                               | HD51           | VO-TTL         | 4             | VCC3           |

|                                  | HD52           | I/O-TTL        | 4             | VCC3           |

| 65                               | VCC3           | Ι-P            | ļ             |                |

| 66                               | HD53           | VO-TTL         | 4             | VCC3           |

| 67                               | HD54           | VO-TTL         | 4             | VCC3           |

| 68<br>69                         | HD55           | I/O-TTL        | 4             | VCC3           |

| 70                               | HD56<br>HD57   | VO-TTL         | 4             | VCC3           |

| 71                               | HD58           | VO-TTL         | 4             | VCC3           |

| 72                               | HD59           | I/O-TTL        | 4             | VCC3           |

|                                  | HD60           | I/O-TTL        | 4             | VCC3           |

| 74                               | HD61           | VO-TTL         | 4             | VCC3           |

| 75                               | HD62           | I/O-TTL        | 4             | VCC3           |

| 76                               | GND            | I-G            |               |                |

| 77                               | HD63           | I/O-TTL        | 4             | VCC3           |

| 78                               | MD0#           | I/O-CMOS       | 4             | VCC_MEM        |

| 79                               | MD1#           | VO-CMOS        | 4             | VCC_MEM        |

| 80                               | MD2#           | VO-CMOS        | 4             | VCC_MEM        |

| 81                               | MD3#           | I/O-CMOS       | 4             | VCC_MEM        |

| 82                               | MD4#           | VO-CMOS        | 4             | VCC_MEM        |

| 83                               | MD5#           | VO-CMOS        | 4             | VCC_MEM        |

| 84                               | MD6#           | VO-CMOS        | 4             | VCC_MEM        |

| 85                               | MD7#           | VO-CMOS        | 4             | VCC_MEM        |

| 86                               | MD8#           | VO-CMOS        | 4             | VCC_MEM        |

| 87                               | NC             |                |               |                |

| 88                               | NC             |                |               |                |

| 89                               | NC             |                |               |                |

| 90                               | NC             | 110 01100      |               | VOC MEN        |

| 91<br>92                         | MD9#           | I/O-CMOS       | 4             | VCC_MEM        |

| 93                               | MD10#<br>MD11# | I/O-CMOS       | 4             | VCC_MEM        |

| 94                               | MD12#          | I/O-CMOS       | 4             | VCC_MEM        |

| 95                               | MD13#          | I/O-CMOS       | 4             | VCC_MEM        |

| 96                               | MD14#          | I/O-CMOS       | 4             | VCC_MEM        |

| 97                               | MD15#          | I/O-CMOS       | 4             | VCC_MEM        |

| 98                               | MD16#          | I/O-CMOS       | 4             | VCC MEM        |

| 99                               | MD17#          | I/O-CMOS       | 4             | VCC_MEM        |

| 100                              | GND            | I-G            |               |                |

| 101                              | VCC_MEM        | I-P            |               |                |

| 102                              | MD18#          | I/O-CMOS       | 4             | VCC_MEM        |

| 103                              | MD19#          | I/O-CMOS       | 4             | VCC_MEM        |

| 104                              | MD20#          | I/O-CMOS       | 4             | VCC_MEM        |

| 105                              | MD21#          | I/O-CMOS       | 4             | VCC_MEM        |

| 106                              | MD22#          | I/O-CMOS       | 4             | VCC_MEM        |

|                                  | MD23#          | I/O-CMOS       | 4             | VCC_MEM        |

| 108                              | MD24#          | I/O-CMOS       | 4             | VCC_MEM        |

| _                                | MD25#          | I/O-CMOS       | 4             | VCC_MEM        |

|                                  | VCC_MEM        | I-P            |               |                |

|                                  | MD26#          | I/O-CMOS       | 4             | VCC_MEM        |

|                                  | GND            | I-G            |               |                |

|                                  | GND<br>MD27#   | I-G            | $\vdash$      | VCC MEN        |

|                                  | MD27#<br>MD28# | I/O-CMOS       | 4             | VCC_MEM        |

| 116                              | MD29#          | VO-CMOS        | 4             | VCC_MEM        |

| 117                              | MD30#          | I/O-CMOS       | 4             | VCC_MEM        |

|                                  | MD31#          | I/O-CMOS       | 4             | VCC_MEM        |

| 119                              | MD32           | I/O-CMOS       | 4             | VCC_MEM        |

|                                  | MD33           | I/O-CMOS       | 4             | VCC_MEM        |

|                                  | MD34           | I/O-CMOS       | 4             | VCC_MEM        |

| 122                              | MD35           | I/O-CMOS       | 4             | VCC_MEM        |

|                                  |                |                |               |                |

| ')            |                |                |               |                |

|---------------|----------------|----------------|---------------|----------------|

| Pin<br>No.    | Pin Name       | Signal<br>Type | Drive<br>(mA) | Power<br>Plane |

| 123           | MD36           | VO-CMOS        | 4             | VCC_MEM        |

| 124           | MD37           | I/O-CMOS       | 4             | VCC_MEM        |

| 125           | MD38           | I/O-CMOS       | 4             | VCC_MEM        |

| 126           | MD39           | I/O-CMOS       | 4             | VCC_MEM        |

| 127           | MD40           | I/O-CMOS       | 4             | VCC_MEM        |

| 128           | MD41           | I/O-CMOS       | 4             | VCC_MEM        |

| 129           | MD42           | I/O-CMOS       | 4             | VCC_MEM        |

| 130           | MD43           | I/O-CMOS       | 4             | VCC_MEM        |

| 131           | NC             |                |               |                |

| 132           | NC             |                |               |                |

| 133           | NC             |                |               |                |

| 134           | NC             | 110 01100      |               |                |

| 135           | MD44           | VO-CMOS        | 4             | VCC_MEM        |

| 136           | MD45           | VO-CMOS        | 4             | VCC_MEM        |

| 137           | MD46           | I/O-CMOS       | 4             | VCC_MEM        |

| 138           |                | I/O-CMOS       | 4             | VCC_MEM        |

| 139           | MD48           | I/O-CMOS       | 4             | VCC_MEM        |

| 140           | MD49<br>MD50   | I/O-CMOS       | 4             | VCC_MEM        |

| $\overline{}$ | VCC MEM        | I/O-CMOS       | 4             | VCC_MEM        |

| 143           | MD51           | I/O-CMOS       | 4             | VCC_MEM        |

| 144           | GND            | I-G            |               | VCC_MEM        |

| 145           | MD52           | VO-CMOS        | 4             | VCC MEM        |

| 146           | MD53           | VO-CMOS        | 4             | VCC MEM        |

| 147           | MD54           | VO-CMOS        | 4             | VCC MEM        |

| 148           | MD55           | VO-CMOS        | 4             | VCC MEM        |

| 149           | MD56           | I/O-CMOS       | 4             | VCC MEM        |

| 150           | MD57           | VO-CMOS        | 4             | VCC_MEM        |

| 151           | MD58           | VO-CMOS        | 4             | VCC_MEM        |

| 152           | MD59           | I/O-CMOS       | 4             | VCC_MEM        |

| 153           | MD60           | I/O-CMOS       | 4             | VCC_MEM        |

| 154           | MD61           | I/O-CMOS       | 4             | VCC_MEM        |

| 155           | VCC_MEM        | I-P            | 4             |                |

| 156           | MD62           | I/O-CMOS       | 4             | VCC_MEM        |

| 157           | MD63           | I/O-CMOS       | 4             | VCC_MEM        |

| 158           | MP7            | I/O-CMOS       | 4             | VCC_MEM        |

| 159           | MP6            | I/O-CMOS       | 4             | VCC_MEM        |

| 160           | MP5            | I/O-CMOS       | 4             | VCC_MEM        |

| 161           | MP4            | I/O-CMOS       | 4             | VCC_MEM        |

|               | TMOD#          |                |               | 1400 14514     |

| 162           | MP3            | I/O-CMOS       | 4             | VCC_MEM        |

| 163           | 3VDRAM#<br>MP2 | I/O-CMOS       | 4             | VCC_MEM        |

| 163           | SUSP LKG       | 1/O-CMICS      |               | ACC MEN        |

| 164           | GND            | I-G            |               |                |

| 165           | MP1            | I/O-CMOS       | 4             | VCC_MEM        |

| '             | IDLE_LKG       |                |               |                |

| 166           | MPO            | I/O-CMOS       | 4             | VCC_MEM        |

|               | MPGEN          |                |               | _              |

| 167           | VCC5           | I-P            |               |                |

|               | MPERR#         | 0              | 4             | VCC5           |

| 169           | HDOE#          | i-TTL          |               | VCC5           |

| 170           | MDOE#          | I-TTL          |               | VCC5           |

| 171           | DBCOE1#        | I-TTL          |               | VCC5           |

| _             | DBCOE0#        | I-∏L           |               | VCC5           |

|               | DLE1#          | I-TTL          |               | VCC5           |

|               | DLEO#          | I-∏L           | <b></b>       | VCC5           |

|               | NC             | _              |               |                |

| 176           | NC             |                |               |                |

Page 8 Revision: 1.0

912-3000-032

💻 9004196 0001171 57T 📟

Table 3-3 82C556 Alphabetical Pin Cross-Reference List (176-Pin TQFP)

|          | 0203       |

|----------|------------|

| Pin Name | Pin<br>No. |

| DBCOE0#  | 172        |

| DBCOE1#  | 171        |

| DLE0#    | 174        |

| DLE1#    | 173        |

| GND      | 25         |

| GND      | 26         |

| GND      | 56         |

| GND      | 76         |

| GND      | 100        |

| GND      | 112        |

| GND      | 113        |

| GND      | 144        |

| GND      | 164        |

| HD0      | 3          |

| HD1      | 4          |

| HD2      | 5          |

| HD3      | 6          |

| HD4      | 7          |

| HD5      | 8          |

| HD6      | 9          |

| HD7      | 10         |

| HD8      | 11         |

| HD9      | 12         |

| HD10     | 13         |

| HD11     | 14         |

| HD12     | 15         |

| HD13     | 16         |

| HD14     | 17         |

| HD15     | 18         |

| HD16     | 19         |

| HD17     | 20         |

| HD18     | 21         |

| HD19     | 23         |

| HD20     | 24         |

| HD21     | 27         |

| HD22     | 28         |

| HD23     | 29         |

| <u> </u> | D:-        |

|----------|------------|

| Pin Name | Pin<br>No. |

| HD24     | 30         |

| HD25     | 31         |

| HD26     | 33         |

| HD27     | 34         |

| HD28     | 35         |

| HD29     | 36         |

| HD30     | 37         |

| HD31     | 38         |

| HD32     | 39         |

| HD33     | 40         |

| HD34     | 41         |

| HD35     | 42         |

| HD36     | 47         |

| HD37     | 48         |

| HD38     | 49         |

| HD39     | 50         |

| HD40     | 51         |

| HD41     | 52         |

| HD42     | 53         |

| HD43     | 54         |

| HD44     | 55         |

| HD45     | 57         |

| HD46     | 58         |

| HD47     | 59         |

| HD48     | 60         |

| HD49     | 61         |

| HD50     | 62         |

| HD51     | 63         |

| HD52     | 64         |

| HD53     | 66         |

| HD54     | 67         |

| HD55     | 68         |

| HD56     | 69         |

| HD57     | 70         |

| HD58     | 71         |

| HD59     | 72         |

| HD60     | 73         |

| s-Reference L | .ist (1 |

|---------------|---------|

| Din Name      | Pin     |

| Pin Name      | No.     |

| HD61          | 74      |

| HD62          | 75      |

| HD63          | 77      |

| HDOE#         | 169     |

| MD0#          | 78      |

| MD1#          | 79      |

| MD2#          | 80      |

| MD3#          | 81      |

| MD4#          | 82      |

| MD5#          | 83      |

| MD6#          | 84      |

| MD7#          | 85      |

| MD8#          | 86      |

| MD9#          | 91      |

| MD10#         | 92      |

| MD11#         | 93      |

| MD12#         | 94      |

| MD13#         | 95      |

| MD14#         | 96      |

| MD15#         | 97      |

| MD16#         | 98      |

| MD17#         | 99      |

| MD18#         | 102     |

| MD19#         | 103     |

| MD20#         | 104     |

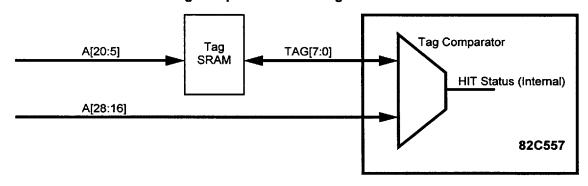

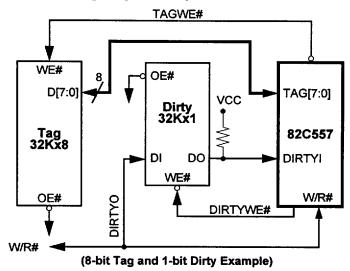

| MD21#         | 105     |