# DC-3GHz High Signal Level Down-Converting Mixer

July 2002

#### **FEATURES**

- Broadband RF, LO and IF Operation

- High Input IP3: +20dBm at 950MHz

- +17dBm at 1900MHz

- Typical Conversion Gain: 1dB at 1900MHz

- SSB Noise Figure: 14dB at 1900MHz

- Integrated LO Buffer: Insensitive to LO Drive Level

- Single-Ended or Differential LO Signal

- High LO-RF Isolation

- Enable Function

- 4.5V to 5.25V Supply Voltage Range

- 4mm × 4mm QFN Package

#### **APPLICATIONS**

- Cellular/PCS/UMTS Infrastructure

- CATV Downlink Infrastructure

- High Linearity Mixer Applications

#### DESCRIPTION

The LT®5512 is a broadband mixer IC optimized for high linearity downconverter applications including cable and wireless infrastructure. The IC includes a differential LO buffer amplifier driving a double-balanced mixer. An integrated RF buffer amplifier improves LO-RF isolation and eliminates the need for precision external bias resistors.

The LT5512 is a high-linearity alternative to passive diode mixers. Unlike passive mixers, which have conversion loss and require high LO drive levels, the LT5512 delivers conversion gain and requires significantly lower LO drive levels.

LT, LTC and LT are registered trademarks of Linear Technology Corporation.

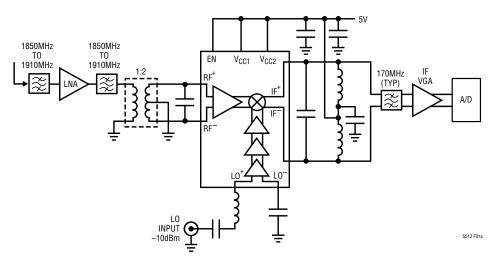

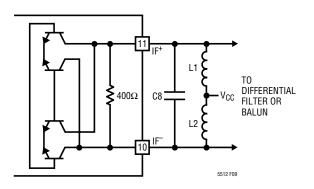

### TYPICAL APPLICATION

Figure 1. High Signal-Level Downmixer for Wireless Infastructure

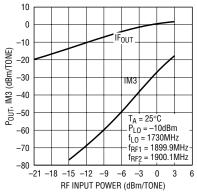

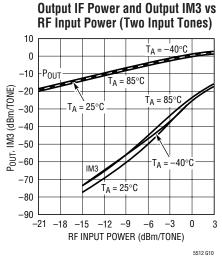

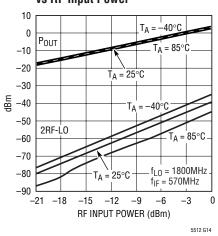

#### Output IF Power and Output IM3 vs RF Input Power (Two Input Tones)

5512 F01b

5512i

#### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| Supply Voltage                  | 5.5V                |

|---------------------------------|---------------------|

| Enable Voltage                  |                     |

| LO+ to LO- Differential Voltage | 00                  |

|                                 | (+6dBm equivalent)  |

| RF+ to RF- Differential Voltage |                     |

|                                 | (+10dBm equivalent) |

| Operating Temperature Range     | 40°C to 85°C        |

| Storage Temperature Range       | 65°C to 125°C       |

| Lead Temperature (Soldering, 10 | sec)300°C           |

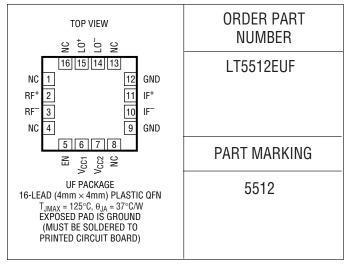

### PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

#### **ELECTRICAL CHARACTERISTICS**

| PARAMETER                              | CONDITIONS                    | MIN TYP    | MAX | UNITS |

|----------------------------------------|-------------------------------|------------|-----|-------|

| RF Input Frequency Range <sup>2</sup>  | Requires Appropriate Matching | DC to 3000 |     | MHz   |

| LO Input Frequency Range <sup>2</sup>  | Requires Appropriate Matching | DC to 3000 |     | MHz   |

| IF Output Frequency Range <sup>2</sup> | Requires Appropriate Matching | DC to 2000 |     | MHz   |

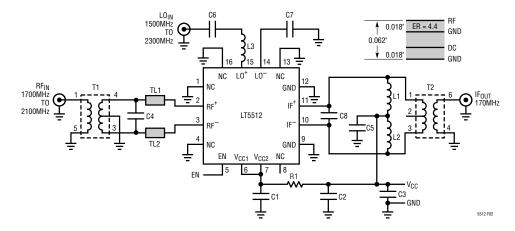

1900MHz Downmixer Application: (Test Circuit Shown in Figure 2)  $V_{CC} = 5V_{DC}$ , EN = High,  $T_A = 25^{\circ}C$ , RF input = 1900MHz at -10dBm, LO input = 1730MHz at -10dBm, IF output measured at 170MHz, unless otherwise noted. (Notes 2, 3)

| LO Input Power               |                                  | −15 to −5    | dBm             |

|------------------------------|----------------------------------|--------------|-----------------|

| Conversion Gain              |                                  | <b>-</b> 1 1 | dB              |

| Input 3rd Order Intercept    | 2-Tone, -10dBm/Tone, Δf = 200kHz | 17           | dBm             |

| LO to RF Leakage             |                                  | -53          | dBm             |

| LO to IF Leakage             |                                  | -46          | dBm             |

| RF to LO Isolation           |                                  | 50           | dB              |

| Output 1dB Compression       |                                  | 6.2          | dBm             |

| LO Input Common Mode Voltage | Internally Biased                | 2            | V <sub>DC</sub> |

| Single-Sideband Noise Figure |                                  | 14           | dB              |

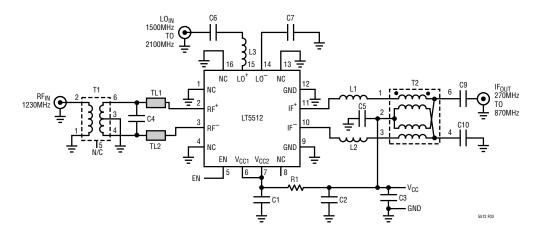

**ELECTRICAL CHARACTERISTICS** 1230MHz Cable Infrastructure Downmixer Application: (Test Circuit Shown in Figure 3)  $V_{CC} = 5V_{DC}$ , EN = High,  $T_A = 25^{\circ}C$ , RF input = 1230MHz at -10dBm, LO input swept from 1500MHz to 2100MHz,  $P_{L0} = -10dBm$ , IF output measured from 270MHz to 870MHz, unless otherwise noted.

| PARAMETER                    | CONDITIONS                                                                                   | MIN                                                      | TYP  | MAX | UNITS |

|------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------|------|-----|-------|

| Conversion Gain              | f <sub>LO</sub> = 1800MHz, f <sub>IF</sub> = 570MHz                                          |                                                          | 2.8  |     | dB    |

| Input 3rd Order Intercept    | 2-Tone RF Input, $-10$ dBm/Tone, $\Delta f = 1$ MHz, $f_{LO} = 1800$ MHz, $f_{ F} = 570$ MHz |                                                          | 17.9 |     | dBm   |

| LO to RF Leakage             |                                                                                              |                                                          | -56  |     | dBm   |

| LO to IF Leakage             |                                                                                              |                                                          | -40  |     | dBm   |

| RF to LO Isolation           | 51                                                                                           |                                                          | 51   |     | dB    |

| 2 • RF – LO Output Spur      | $f_{IF} = 570MHz$ , $P_{RF} = -18dBm$ , $f_{LO} = 1800MHz$                                   | $f_{IF} = 570MHz, P_{RF} = -18dBm, f_{LO} = 1800MHz$ -60 |      |     | dBc   |

| Single-Sideband Noise Figure | f <sub>LO</sub> = 1800MHz, f <sub>IF</sub> = 570MHz                                          | $f_{LO} = 1800MHz, f_{IF} = 570MHz$ 13.3                 |      |     | dB    |

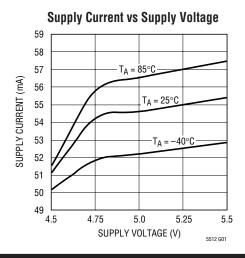

# **DC ELECTRICAL CHARACTERISTICS** (Test Circuit Shown in Figure 2) $V_{CC} = 5V_{DC}$ , EN = High, $T_A = 25^{\circ}C$ (Note 3), unless otherwise noted.

| PARAMETER                                    | CONDITIONS                             | MIN  | TYP | MAX  | UNITS           |

|----------------------------------------------|----------------------------------------|------|-----|------|-----------------|

| Enable (EN) Low = Off, High = On             | ·                                      |      |     |      |                 |

| Turn On Time                                 |                                        |      | 3   |      | μѕ              |

| Turn Off Time                                |                                        |      | 13  |      | μS              |

| Input Current                                | V <sub>ENABLE</sub> = 5V <sub>DC</sub> |      | 50  |      | μА              |

| Enable = High (On)                           |                                        | 3    |     |      | V <sub>DC</sub> |

| Enable = Low (Off)                           |                                        |      |     | 0.3  | V <sub>DC</sub> |

| Power Supply Requirements (V <sub>CC</sub> ) |                                        |      |     |      |                 |

| Supply Voltage                               |                                        | 4.50 |     | 5.25 | V <sub>DC</sub> |

| Supply Current                               |                                        |      | 57  | 74   | mA              |

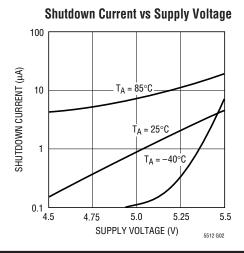

| Shutdown Current                             | EN = Low                               |      |     | 100  | μA              |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** External components on the final test circuit are optimized for operation at  $f_{RF}$  = 1900MHz,  $f_{LO}$  = 1730MHz and  $f_{IF}$  = 170MHz (Figure 2).

**Note 3:** Specifications over the  $-40^{\circ}$ C to  $85^{\circ}$ C temperature range are assured by design, characterization and correlation with statistical process controls.

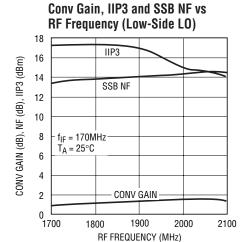

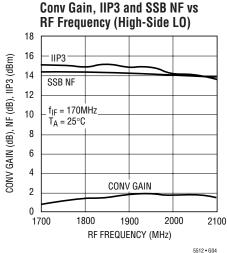

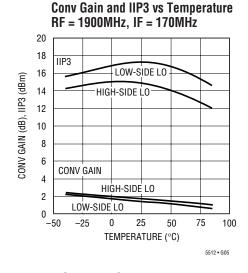

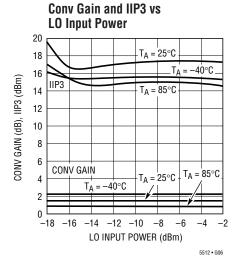

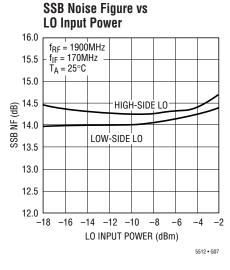

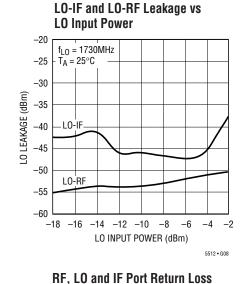

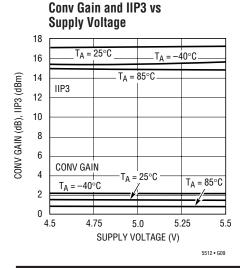

# TYPICAL PERFORMANCE CHARACTERISTICS (Test Circuit Shown in Figure 2)

5512

# TYPICAL PERFORMANCE CHARACTERISTICS (1900MHz Downmixer Application)

$V_{CC} = 5V_{DC}$ , EN = High,  $T_A = 25^{\circ}C$ , 1900MHz RF input matching, RF input = 1900MHz at -10dBm, LO input = 1730MHz at -10dBm, IF output measured at 170MHz, unless otherwise noted. (Test circuit shown in Figure 2).

5512 • G03

LINEAR TECHNOLOGY

4

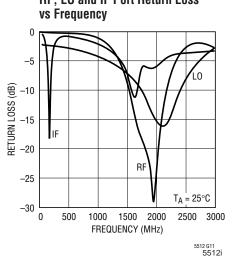

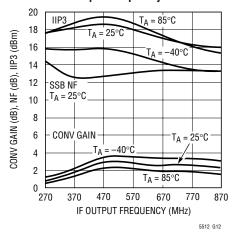

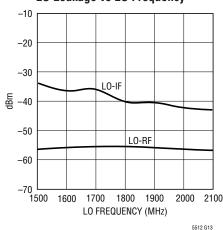

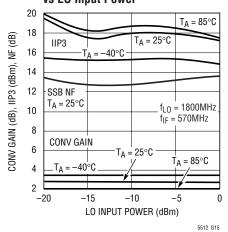

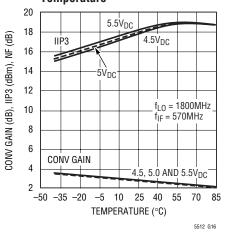

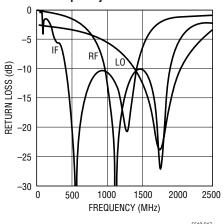

# **TYPICAL PERFORMANCE CHARACTERISTICS** (1230MHz Cable Infrastructure Downmixer Application) $V_{CC} = 5V_{DC}$ , EN = High, $T_A = 25^{\circ}C$ , RF input = 1230MHz at -10dBm, LO input swept from = 1500MHz to 2100MHz, $P_{L0} = -10dBm$ , IF output measured from 270MHz to 870MHz, unless otherwise noted. (Test circuit shown in Figure 3.)

#### Conv Gain, IIP3 and SSB NF vs IF Output Frequency

#### LO Leakage vs LO Frequency

IF Output Power and 2RF-LO Spur vs RF Input Power

Conv Gain, IIP3 and SSB NF vs LO Input Power

Conv Gain and IIP3 vs **Temperature**

RF, LO and IF Port Return Losses vs Frequency

#### PIN FUNCTIONS

**NC (Pins 1, 4, 8, 13, 16):** Not connected internally. These pins should be grounded on the circuit board for improved LO to RF and LO to IF isolation.

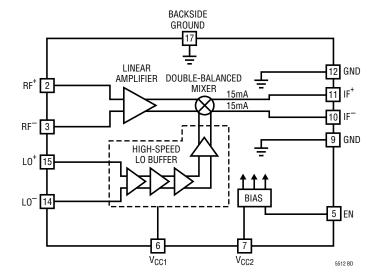

RF<sup>+</sup>, RF<sup>-</sup> (Pins 2, 3): Differential Inputs for the RF Signal. These pins must be driven with a differential signal. Each pin must be connected to a DC ground capable of sinking 15mA (30mA total). This DC bias return can be accomplished through the center-tap of a balun, or with shunt inductors. An impedance transformation is required to match the RF input to  $50\Omega$  (or  $75\Omega$ ).

**EN (Pin 5):** Enable Pin. When the input voltage is higher than 3V, the mixer circuits supplied through Pins 6, 7, 10, and 11 are enabled. When the input voltage is less than 0.3V, all circuits are disabled. Typical enable pin input current is  $50\mu\text{A}$  for EN = 5V and  $0\mu\text{A}$  when EN = 0V.

$V_{CC1}$  (Pin 6): Power Supply Pin for the LO Buffer Circuits. Typical current consumption is 22mA. This pin should be externally connected to the other  $V_{CC}$  pins, and decoupled with 100pF and 0.01 $\mu$ F capacitors.

**V<sub>CC2</sub>** (**Pin 7**): Power Supply Pin for the Bias Circuits. Typical current consumption is 4mA. This pin should be

externally connected to the other  $V_{CC}$  pins, and decoupled with 100pF and 0.01 $\mu$ F capacitors.

**GND** (Pins 9 and 12): Ground. These pins are internally connected to the backside ground for better isolation. They should be connected to RF ground on the circuit board, although they are not intended to replace the primary grounding through the backside contact of the package.

**IF**<sup>-</sup>, **IF**<sup>+</sup> (**Pins 10, 11**): Differential Outputs for the IF Signal. An impedance transformation may be required to match the outputs. These pins must be connected to  $V_{CC}$  through impedance matching inductors, RF chokes or a transformer center-tap.

**LO**<sup>-</sup>, **LO**<sup>+</sup> (**Pins 14, 15**): Differential Inputs for the Local Oscillator Signal. They can also be driven single-ended by connecting one to an RF ground through a DC blocking capacitor. These pins are internally biased to 2V; thus, DC blocking capacitors are required. An impedance transformation is required to match the LO input to  $50\Omega$  (or  $75\Omega$ ).

**GROUND (Backside Contact):** Circuit Ground Return for the Entire IC. This must be soldered to the printed circuit board ground plane.

#### **BLOCK DIAGRAM**

LINEAR TECHNOLOGY

# **TEST CIRCUITS**

| REF DES        | VALUE  | SIZE | PART NUMBER              | REF DES  | VALUE            | SIZE     | PART NUMBER             |

|----------------|--------|------|--------------------------|----------|------------------|----------|-------------------------|

| C1, C5, C6, C7 | 100pF  | 0402 | Murata GRP1555C1H101J    | L1, L2   | 47nH             | 0402     | Coilcraft 0402CS-47NX   |

| C2             | 0.01μF | 0402 | Murata GRP155R71C103K    | L3       | 5.6nH            | 0402     | Toko LL1005-FH5N6       |

| C3             | 1.0μF  | 0603 | Taiyo Yuden LMK107F105ZA | R1       | 10               | 0402     |                         |

| C4             | 1.5pF  | 0402 | Murata GRP1555C1H1R5C    | T1       | 2:1              |          | Murata LDB211G9010C-001 |

| C8             | 6.8pF  | 0402 | Murata GRP1555C1H6R8D    | T2       | 8:1              |          | Mini-Circuits TC8-1     |

|                |        |      |                          | TL1, TL2 | $Z_0 = 72\Omega$ | θ = 8.1° | (W = 0.4mm, L = 2mm)    |

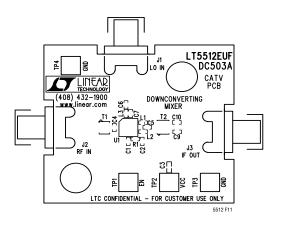

Figure 2. Test Schematic for 1900MHz Downconverter (PCS/UMTS Applications)

| REF DES     | VALUE  | SIZE | PART NUMBER              | REF DES  | VALUE            | SIZE     | PART NUMBER             |

|-------------|--------|------|--------------------------|----------|------------------|----------|-------------------------|

| C1, C5, C6, |        |      |                          | L1, L2   | 12nH             | 0402     | Toko LL1005-FH12N       |

| C7, C9, C10 | 100pF  | 0402 | Murata GRP1555C1H101J    | L3       | 8.2nH            | 0402     | Toko LL1005-FH8N2       |

| C2          | 0.01μF | 0402 | Murata GRP155R71C103K    | R1       | 10               | 0402     |                         |

| C3          | 1.0μF  | 0603 | Taiyo Yuden LMK107F105ZA | T1       | 1:1              |          | Murata LDB311G2705C-428 |

| C4          | 2.7pF  | 0402 | Murata GRP1555C1H2R7C    | T2       | 4:1              |          | M/A-COM ETC1.6-4-2-3    |

|             |        |      |                          | TL1, TL2 | $Z_0 = 72\Omega$ | θ = 5.4° | (W = 0.4mm, L = 2.0mm)  |

Figure 3. Test Schematic for 1230MHz Downconverter (Cable Infrastructure Downlink Transmitter Applications)

The LT5512 consists of a double-balanced mixer, RF buffer amplifier, high-speed limiting LO buffer, and bias/enable circuits. The RF, LO and IF ports are differential. All three ports can be matched from DC to 3GHz, although the IC has been optimized for downconverter applications where the RF and LO input signals are high frequency and the IF output frequency ranges from DC up to 2GHz. Low side or high side LO injection can be used.

#### **RF Input Port**

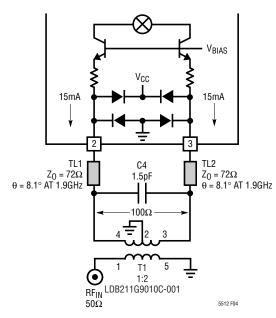

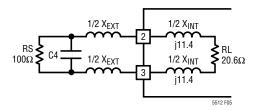

The RF input buffer has been designed to simplify impedance matching while improving LO-RF isolation and noise figure. A simplified schematic is shown in Figure 4 with the associated external impedance matching elements for a 1.9GHz application. Each RF input requires a low resistance DC return to ground capable of sinking 15mA. This can be accomplished with the center-tap of a balun as shown in Figure 4, or bias chokes connected from Pins 2 and 3 to ground.

Figure 4. RF Input with External Matching for a 1.9GHz Application

Table 1 lists the differential input impedance and differential reflection coefficient between Pins 2 and 3 for several common RF frequencies. As shown in Figures 4 and 5, low-pass impedance matching is used to transform the

differential input impedance up to the desired value for the balun input. The following example shows how to design the low-pass impedance transformation network for the RF input.

From Table 1, the differential input impedance at 1900MHz is 20.6 + j22.8. As shown in Figure 5, the 22.8  $\Omega$  reactance is split, with one half on each side of the 20.6  $\Omega$  load resistor. The matching network will consist of additional inductance in series with the internal inductance and a capacitor in parallel with the desired  $100\Omega$  source impedance. The capacitance (C4) and inductance are calculated as follows.

$$\begin{split} n &= R_S/R_L = 100/20.6 = 4.85 \\ Q &= \sqrt{n-1} = 1.963 \\ X_C &= R_S/Q = 100/1.963 = 50.9\Omega \\ C4 &= 1/(\omega Xc) = 1.6pF \text{ (use 1.5pF)} \\ X_L &= (R_L \bullet Q) = (20.6 \bullet 1.963) = 40.4\Omega \\ X_{EXT} &= X_L - X_{INT} = 40.4 - 22.8 = 17.6\Omega \\ L_{EXT} &= (X_{EXT}/\omega) = 1.47nH \end{split}$$

The external inductance is split in half (0.74nH), with each half connected between the pin and the shunt capacitor, as shown in Figure 5. The inductance is implemented with short (2mm) high-impedance printed transmission lines, which yield a compact board layout. Finally, the 2:1balun transforms the  $100\Omega$  differential impedance down to a  $50\Omega$  single-ended input for the RF signal.

Table 1. RF Input Differential Impedance

| Frequency | Differential Input | Differential S11 |       |

|-----------|--------------------|------------------|-------|

| (MHz)     | Impedance          | Mag              | Angle |

| 10        | 18.2 + j0.14       | 0.467            | 179.6 |

| 44        | 18.0 + j0.26       | 0.470            | 178.6 |

| 240       | 18.1 + j2.8        | 0.471            | 172.6 |

| 450       | 18.1 + j5.2        | 0.473            | 166.3 |

| 950       | 18.7 + j11.3       | 0.479            | 150.8 |

| 1900      | 20.6 + j22.8       | 0.503            | 124.3 |

| 2150      | 21.4 + j26.5       | 0.512            | 116.9 |

| 2450      | 22.5 + j30.5       | 0.522            | 109.2 |

| 2700      | 24.1 + j34.7       | 0.530            | 101.7 |

Figure 5. 1.9GHz RF Input Matching

It is also possible to eliminate the RF balun and drive the RF inputs differentially. In this case, inductors from Pins 2 and 3 to ground would be required to bias the input stage. The value of the inductors should be high enough to avoid reducing the input impedance at the frequency of interest.

#### **LO Input Port**

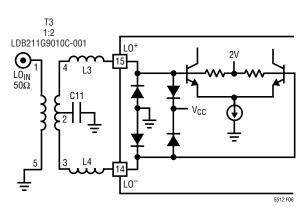

The LO buffer amplifier consists of high-speed limiting differential amplifiers, designed to drive the mixer quad for high linearity. The LO $^+$  and LO $^-$  pins are designed for differential or single-ended drive. An external balun is optional. Both LO pins are internally biased to  $2V_{DC}$ .

The LO input has been designed for simple impedance matching for frequencies up to 3GHz. A simplified schematic is shown in Figure 6 with the associated external impedance matching. The matching technique is similar to that described earlier for the RF port, except the match is not nearly as critical. Table 2 lists the differential input impedance and differential reflection coefficient between the LO<sup>+</sup> and LO<sup>-</sup> pins (Pin 15 to Pin 14). As shown, the real part of the series impedance is close to  $100\Omega$ . Series inductors (L3, L4) are used to tune out the capacitive portion of the differential impedance.

Figure 6. LO Input with External Matching Elements

Table 2. LO Input Differential Impedance

| Frequency | Differential Input | Differential S11 |       |

|-----------|--------------------|------------------|-------|

| (MHz)     | Impedance          | Mag              | Angle |

| 750       | 263 – j172         | 0.766            | -10.2 |

| 1000      | 213 – j178         | 0.760            | -13.4 |

| 1250      | 175 – j173         | 0.752            | -16.6 |

| 1500      | 146 – j164         | 0.743            | -19.8 |

| 1750      | 125 – j153         | 0.733            | -22.8 |

| 2000      | 108 – j142         | 0.722            | -25.8 |

| 2250      | 95 – j131          | 0.709            | -28.9 |

| 2500      | 86 – j122          | 0.695            | -31.8 |

| 2750      | 78 – j113          | 0.68             | -34.6 |

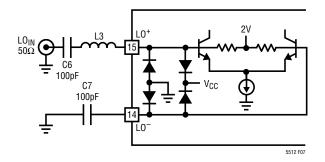

Single-ended LO drive can be used if a differential LO source is not available, or the added expense of a LO balun is undesirable. In this case, one LO input is AC-coupled to ground through a 100pf DC blocking capacitor as shown in Figure 7. The other input is matched to  $50\Omega$  using a series inductor and a second DC blocking capacitor. The LT5512 is characterized and production tested with single-ended LO drive.

Figure 7. Single-Ended LO Input Matching

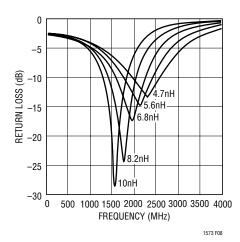

The differential port impedance listed in Table 2 can be used to compute the value of the series matching inductor, L3. Alternatively, Figure 8 shows measured L0 input return loss for various values of L3.

Figure 8. Single-Ended LO Port Return Loss vs Frequency for Various Values of L3

#### **IF Output Port**

The IF outputs, IF<sup>+</sup> and IF<sup>-</sup>, are internally connected to the collectors of the mixer switching transistors as shown in Figure 9. These differential outputs should be combined externally through an RF balun or  $180^{\circ}$  hybrid to achieve optimum performance. Both pins must be biased at the supply voltage, which can be applied through matching inductors (see Figure 2), or through the center-tap of an output transformer (see Figure 3). These pins are protected with ESD diodes; the diodes allow peak AC signal swing up to 1.3V above  $V_{CC}$ .

As shown in Table 3, the IF output differential impedance is approximately  $390\Omega$  in parallel with 0.44pF. A simple band-pass IF matching network suitable for wireless applications is shown in Figure 9. Here, L1, L2 and C8 set the desired IF output frequency. The  $390\Omega$  differential output can then be applied directly to a differential filter, or an 8:1 balun for impedance transformation down to  $50\Omega$ . To achieve maximum linearity, C8 should be located as close as possible to the IF+/IF— pins. Even small amounts of inductance in series with C8 (such as through a via) can significantly degrade IIP3. For high IF frequencies, the value of C8 should be reduced by the value of internal capacitance (see Table 3). This matching network is simple and offers good selectivity for narrow band IF applications.

An alternative matching network for a broadband CATV IF (270MHz to 870MHz) is shown in Figure 3. Here, a low-pass impedance transformer consisting of the internal capacitance, with L1 and L2, transforms the  $371\Omega$  output resistance at 870MHz to  $200\Omega$ . A 4:1 balun then completes the match down to  $50\Omega$ . Supply voltage is applied through the center-tap of the transformer.

Table 3. IF Output Differential Impedance (Parallel Equivalent)

| Frequency | Differential Output | Differential S11 |       |

|-----------|---------------------|------------------|-------|

| (MHz)     | Impedance           | Mag              | Angle |

| 10        | 396    - j10k       | 0.766            | 0     |

| 70        | 394    - j5445      | 0.775            | -1.1  |

| 170       | 393    - j2112      | 0.774            | -2.8  |

| 240       | 392    - j1507      | 0.773            | -3.9  |

| 450       | 387    - j798       | 0.772            | -7.3  |

| 750       | 377    - j478       | 0.768            | -12.2 |

| 860       | 371    - j416       | 0.766            | -14.0 |

| 1000      | 363    - j359       | 0.762            | -16.2 |

| 1250      | 363    - j295       | 0.764            | -19.6 |

| 1500      | 346    - j244       | 0.756            | -23.6 |

| 1900      | 317    - j192       | 0.743            | -29.9 |

Figure 9. IF Output Equivalent Circuit with Band-Pass Matching Elements

LINEAR

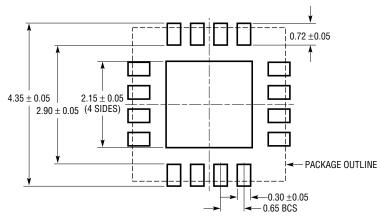

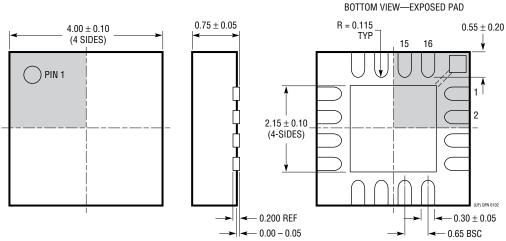

#### PACKAGE DESCRIPTION

#### **UF16 Package** 16-Lead Plastic QFN (4mm × 4mm)

(Reference LTC DWG # 05-08-1692)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

- NOTE:

1. DRAWING CONFORMS TO JEDEC PACKAGE OUTLINE MO-220 VARIATION (WGGC)

2. ALL DIMENSIONS ARE IN MILLIMETERS

3. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

4. EXPOSED PAD SHALL BE SOLDER PLATED

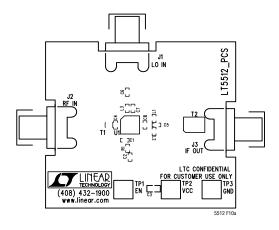

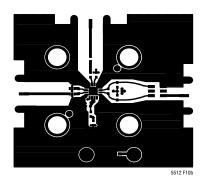

Figure 10. 1900MHz Evaluation Board Layout

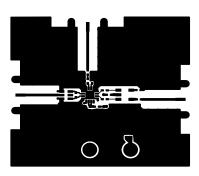

Figure 11. 1230MHz Cable Infrastructure Evaluation Board Layout (Wide Output Range Down-Converting Mixer for Downlink Transmitter)

# **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                                 | COMMENTS                                                                         |

|-------------|-------------------------------------------------------------|----------------------------------------------------------------------------------|

| LT5500      | 1.8GHz to 2.7GHz Receiver-Front End                         | 1.8V to 5.25V Supply, Dual-Gain LNA, Mixer, LO Buffer                            |

| LT5502      | 400MHz Quadrature IF Demodulator with RSSI                  | 1.8V to 5.25V Supply, 70MHz to 400MHz IF,<br>84dB Limiting Gain, 90db RSSI Range |

| LT5503      | 1.2GHz to 2.7GHz Direct IQ Modulator and Upconverting Mixer | 1.8V to 5.25V Supply, Four-Step RF Power Control,<br>120MHz Modulation Bandwidth |

| LT5504      | 800MHz to 2.7GHz RF Measuring Receiver                      | 80dB Dynamic Range, Temperature Compensated, 2.7V to 5.5V Supply                 |

| LTC5505     | RF Power Detectors with >40dB Dynamic Range                 | 300MHz to 3GHz, Temperature Compensated, 2.7V to 6V Supply                       |

| LTC5507     | 100kHz to 1000MHz RF Power Detector                         | Temperature Compensated, 2.7V to 6V Supply                                       |

| LT5511      | High Signal Level Upconverting Mixer                        | RF Output to 3GHz, 17dBm IIP3, Integrated LO Buffer                              |