**Features**

##

## **Smallest TEC Power Drivers for Optical Modules**

### **General Description**

The MAX8520/MAX8521 are designed to drive thermoelectric coolers (TECs) in space-constrained optical modules. Both devices deliver ±1.5A output current and control the TEC current to eliminate harmful current surges. On-chip FETs minimize external components and high switching frequency reduces the size of external components.

The MAX8520 and MAX8521 operate from a single supply and bias the TEC between the outputs of two synchronous buck regulators. This operation allows for temperature control without "dead zones" or other nonlinearities at low current. This arrangement ensures that the control system does not hunt when the set point is very close to the natural operating point, requiring a small amount of heating or cooling. An analog control signal precisely sets the TEC current.

Both devices feature accurate, individually adjustable heating current limit and cooling current limit, along with maximum TEC voltage limit to improve the reliability of optical modules. An analog output signal monitors the TEC current. A unique ripple cancellation scheme helps reduce noise.

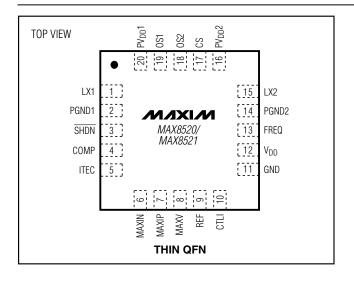

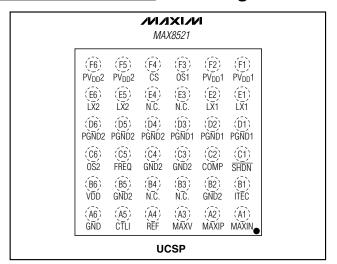

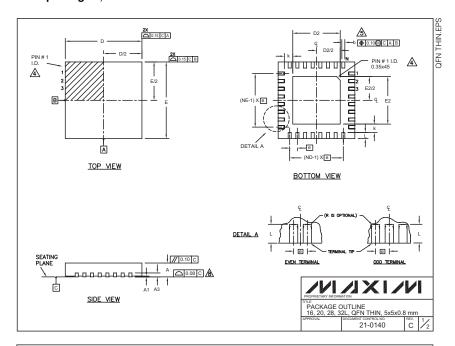

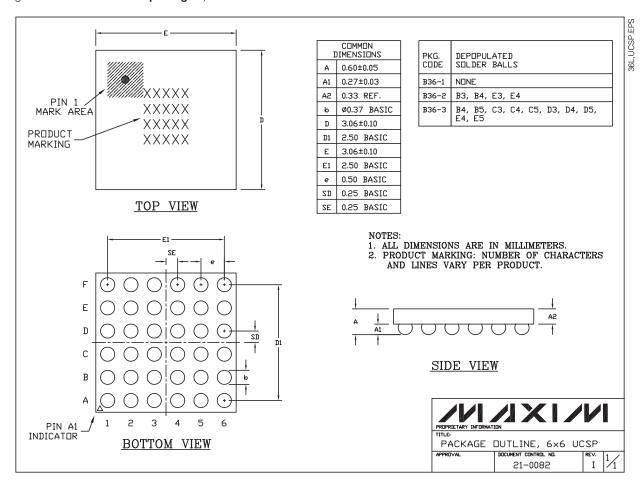

The MAX8520 is available in a 5mm x 5mm thin QFN package and its switching frequency is adjustable up to 1MHz through an external resistor. The MAX8521 is also available in a 5mm x 5mm thin QFN, as well as a spacesaving 3mm x 3mm UCSP™, with a pin-selectable switching frequency of 500kHz or 1MHz.

#### **Applications**

SFF/SFP Modules Fiber-Optic Laser Modules Fiber-Optic Network Equipment Biotech Lab Equipment

Pin Configurations appear at end of data sheet.

N/IXI/N/

UCSP is a trademark of Maxim Integrated Products, Inc.

## ♦ Circuit Footprint of 0.31in<sup>2</sup>

- **♦ Low-Profile Design**

- **♦ On-Chip Power MOSFETs**

- ♦ High-Efficiency Switch-Mode Design

- **♦ Ripple Cancellation for Low Noise**

- **♦ Direct Current Control Prevents TEC Current** Surges

- ♦ 5% Accurate Adjustable Heating/Cooling Current

- **♦ 2% Accurate TEC Voltage Limit**

- ♦ No Dead Zone or Hunting at Low Output Current

- **♦ ITEC Monitors TEC Current**

- ♦ 1% Accurate Voltage Reference

- ♦ Switching Frequency Up to 1MHz

- ♦ Synchronization (MAX8521)

## **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE           |

|------------|----------------|-----------------------|

| MAX8520ETP | -40°C to +85°C | 20 Thin QFN 5mm x 5mm |

| MAX8521EBX | -40°C to +85°C | 36 UCSP 3mm x 3mm     |

| MAX8521ETP | -40°C to +85°C | 20 Thin QFN 5mm x 5mm |

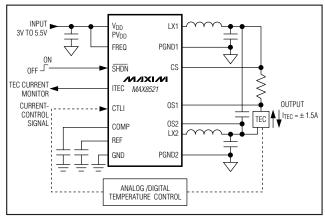

## **Typical Operating Circuit**

Maxim Integrated Products 1

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND                                    | 0.3V to +6V               |

|-----------------------------------------------------------|---------------------------|

| SHDN, MAXV, MAXIP, MAXIN,<br>CTLI to GND                  | 0.3V to +6V               |

| COMP, FREQ, OS1, OS2, CS, REF,                            |                           |

| ITEC to GND                                               | 0.3V to $(V_{DD} + 0.3V)$ |

| PV <sub>DD</sub> 1, PV <sub>DD</sub> 2 to GND             | 0.3V to $(V_{DD} + 0.3V)$ |

| PV <sub>DD</sub> 1, PV <sub>DD</sub> 2 to V <sub>DD</sub> |                           |

| PGND1, PGND2 to GND                                       | 0.3V to +0.3V             |

| COMP, REF, ITEC Short to GND                              | Indefinite                |

| LX Current (Note 1)                                       | ±2.25A LX Current         |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)<br>20-Pin 5mm x 5mm x 0.9mm QFN (derate 20.8mW/°C<br>above +70°C) (Note 2)1.67W | / |

|---------------------------------------------------------------------------------------------------------------------------------------|---|

| 3mm x 3mm ÚČSP (derate 22mW/°C above +70°C)                                                                                           | 1 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- **Note 1:** LX has internal clamp diodes to PGND and PVDD. Applications that forward bias these diodes should take care not to exceed the IC's package power dissipation limits.

- Note 2: Solder underside metal slug to PC board ground plane.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = PV_{DD}1 = PV_{DD}2 = \overline{SHDN} = 5V$ , 1MHz mode (Note 3). PGND1 = PGND2 = GND, CTLI = MAXV = MAXIP = MAXIN = REF, **T<sub>A</sub> = 0°C to +85°C**, unless otherwise noted. Typical values at T<sub>A</sub> = +25°C.)

| PARAMETER                   | SYMBOL                 | CONE                                                   | DITIONS                                    | MIN   | TYP  | MAX   | UNITS |  |

|-----------------------------|------------------------|--------------------------------------------------------|--------------------------------------------|-------|------|-------|-------|--|

| Input Supply Range          | $V_{DD}$               |                                                        |                                            | 3.0   |      | 5.5   | V     |  |

| Maximum TEC Current         |                        |                                                        |                                            | ±1.5  |      |       | Α     |  |

| Reference Voltage           | V <sub>REF</sub>       | V <sub>DD</sub> = 3V to 5.5V, I <sub>REF</sub> = 150μA |                                            | 1.485 | 1.5  | 1.515 | V     |  |

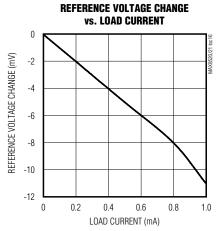

| Reference Load Regulation   | $\Delta V_{REF}$       | $V_{DD} = 3V \text{ to 5V, I}_{REF}$                   | = 10μA to 1mA                              |       | 1.2  | 5.0   | mV    |  |

|                             |                        |                                                        | V <sub>MAXI</sub> _ = V <sub>REF</sub>     | 140   | 150  | 160   |       |  |

| MAXIP/MAXIN Threshold       |                        | $V_{DD} = 5V$                                          | V <sub>MAXI</sub> _ = V <sub>REF</sub> /3  | 40    | 50   | 60    | \/    |  |

| Accuracy                    |                        |                                                        | V <sub>MAXI</sub> _ = V <sub>REF</sub>     | 143   | 150  | 155   | mV    |  |

|                             |                        | $V_{DD} = 3V$                                          | V <sub>MAXI</sub> _ = V <sub>REF</sub> /3  | 45    | 50   | 55    | ]     |  |

| NEET On Designation         | Б                      | V <sub>DD</sub> = 5V, I = 0.2A                         |                                            |       | 0.09 | 0.14  | 0     |  |

| NFET On-Resistance          | R <sub>DS</sub> (ON-N) | V <sub>DD</sub> = 3V, I = 0.2A                         |                                            |       | 0.11 | 0.16  | Ω     |  |

| DEET On Desistance          | Б                      | V <sub>DD</sub> = 5V, I = 0.2A                         |                                            |       | 0.14 | 0.23  | -     |  |

| PFET On-Resistance          | RDS(ON-P)              | $V_{DD} = 3V, I = 0.2A$                                |                                            | 0.17  | 0.30 | Ω     |       |  |

| NEET Laskage                | 1                      | $V_{LX} = V_{DD} = 5V, T_A = +25^{\circ}C$             |                                            |       | 0.03 | 4     | ^     |  |

| NFET Leakage                | ILEAK(N)               | $V_{LX} = V_{DD} = 5V, T_A$                            | $V_{LX} = V_{DD} = 5V, T_A = +85^{\circ}C$ |       | 0.3  |       | μA    |  |

| DEET Lasters                | 1                      | $V_{LX} = 0, T_A = +25^{\circ}C$                       | ,                                          |       | 0.03 | 4     | ^     |  |

| PFET Leakage                | ILEAK(P)               | $V_{LX} = 0, T_A = +85^{\circ}C$                       | ,                                          |       | 0.3  |       | μΑ    |  |

|                             |                        | VCOMP = VREF =                                         | 500kHz mode                                | 11    |      | 14    |       |  |

| No. 1 and Commonly Commonst | I <sub>DD(NO</sub>     | 1.500V, $V_{DD} = 5V$                                  | 1MHz mode                                  |       | 16   | 21    |       |  |

| No-Load Supply Current      | LOAD)                  | VCOMP = VREF =                                         | 500kHz mode                                |       | 8    | 11    | mA    |  |

|                             |                        | 1.500V, V <sub>DD</sub> = 3.3V                         | 1MHz mode                                  |       | 11   | 14    | 1     |  |

| Shutdown Supply Current     | I <sub>DD-SD</sub>     | SHDN = GND, V <sub>DD</sub> = 5V (Note 4)              |                                            |       | 2    | 3     | mA    |  |

| Thermal Shutdown            | TSHUTDOWN              | Hysteresis = 15°C                                      |                                            | +165  |      | °C    |       |  |

| UVLO Threshold              | \/. n n 5              | V <sub>DD</sub> rising                                 |                                            | 2.50  | 2.65 | 2.80  | V     |  |

| OVEO Mireshold              | V <sub>UVLO</sub>      | V <sub>DD</sub> falling                                | 2.40                                       | 2.55  | 2.70 | V     |       |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = PV_{DD}1 = PV_{DD}2 = \overline{SHDN} = 5V$ , 1MHz mode (Note 3). PGND1 = PGND2 = GND, CTLI = MAXV = MAXIP = MAXIN = REF, T<sub>A</sub> = 0°C to +85°C, unless otherwise noted. Typical values at T<sub>A</sub> = +25°C.)

| PARAMETER                      | SYMBOL                                                   | CONDITIONS                                                                         | MIN                       | TYP  | MAX                       | UNITS |

|--------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------|------|---------------------------|-------|

|                                |                                                          | MAX8521, FREQ= V <sub>DD</sub> , V <sub>DD</sub> = 3V to 5V                        | 0.8                       | 1    | 1.2                       |       |

|                                |                                                          | MAX8521, FREQ= 0, V <sub>DD</sub> = 3V to 5V                                       | 0.4                       | 0.5  | 0.6                       |       |

| Internal Oscillator Switching  | form                                                     | MAX8520, $R_{EXT} = 60$ k $\Omega$ , $V_{DD} = 5$ V                                | 0.8                       | 1    | 1.2                       | MHz   |

| Frequency                      | fsw-INT                                                  | MAX8520, $R_{EXT} = 60$ k $\Omega$ , $V_{DD} = 3$ V                                | 0.76                      | 0.93 | 1.10                      | IVITZ |

|                                |                                                          | MAX8520, $R_{EXT} = 150k\Omega$ , $V_{DD} = 5V$                                    | 0.4                       | 0.5  | 0.6                       |       |

|                                |                                                          | MAX8520, $R_{EXT} = 150k\Omega$ , $V_{DD} = 3V$                                    | 0.36                      | 0.46 | 0.56                      |       |

| External Sync Frequency Range  |                                                          | 25% < duty cycle <75% (MAX8521 only)                                               | 0.7                       |      | 1.2                       | MHz   |

| LX_ Duty Cycle                 |                                                          | (Note 5)                                                                           | 0                         |      | 100                       | %     |

| OS1, OS2, CS Input Current     | I <sub>OS1</sub> , I <sub>OS2</sub> ,<br>I <sub>CS</sub> | 0 or V <sub>DD</sub>                                                               | -100                      |      | +100                      | μΑ    |

| SHDN, FREQ Input Current       | I <u>SHDN,</u><br>IFREQ                                  | 0 or V <sub>DD</sub> , FREQ applicable for the MAX8521 only                        | -5                        |      | +5                        | μΑ    |

| SHDN, FREQ Input Low Voltage   | VIL                                                      | V <sub>DD</sub> = 3V to 5.5V, FREQ applicable for the MAX8521 only                 |                           |      | V <sub>DD</sub> x<br>0.25 | V     |

| SHDN, FREQ Input High Voltage  | V <sub>IH</sub>                                          | V <sub>DD</sub> = 3V to 5.5V, FREQ applicable for the MAX8521 only                 | V <sub>DD</sub> x<br>0.75 |      |                           | V     |

| MAYV/Threshold Assuracy        |                                                          | $V_{MAXV} = V_{REF} \times 0.67$ , $V_{OS1}$ to $V_{OS2} = \pm 4V$ , $V_{DD} = 5V$ | -2                        |      | +2                        | %     |

| MAXV Threshold Accuracy        |                                                          | $V_{MAXV} = V_{REF} \times 0.33$ , $V_{OS1}$ to $V_{OS2} = \pm 2V$ , $V_{DD} = 3V$ | -3                        |      | +3                        | %     |

| MAXV, MAXI_ Input Bias Current | I <sub>MAXV-BIAS</sub> ,<br>I <sub>MAXIBIAS</sub>        | V <sub>MAXV</sub> = V <sub>MAXI</sub> _ = 0.1V or 1.5V                             | -0.1                      |      | +0.1                      | μΑ    |

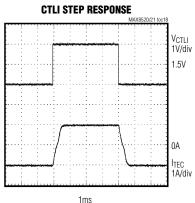

| CTLI Gain                      | Actli                                                    | V <sub>CTLI</sub> = 0.5V to 2.5V (Note 6)                                          | 9.5                       | 10   | 10.5                      | V/V   |

| CTLI Input Resistance          | RCTLI                                                    | 1M $\Omega$ terminated at REF                                                      | 0.5                       | 1    | 2.0                       | МΩ    |

| Error-Amp Transconductance     | Яm                                                       |                                                                                    | 50                        | 100  | 160                       | μS    |

| VITEC Accuracy                 |                                                          | Vos1 to Vcs = ±100mV, Vos1 = Vpd/2                                                 | -10                       |      | +10                       | %     |

### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = PV_{DD}1 = PV_{DD}2 = \overline{SHDN} = 5V, 1MHz \text{ mode (Note 2)}. PGND1 = PGND2 = GND, CTLI = MAXV = MAXIP = MAXIN = REF, T_A = -40^{\circ}C to +85^{\circ}C, unless otherwise noted.) (Note 7)$

| PARAMETER                     | SYMBOL                                                   | CONI                                                        | DITIONS                                 | MIN                       | MAX                       | UNITS |  |

|-------------------------------|----------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------|---------------------------|---------------------------|-------|--|

| Input Supply Range            | $V_{DD}$                                                 |                                                             |                                         | 3.0                       | 5.5                       | V     |  |

| Maximum TEC Current           |                                                          |                                                             |                                         | ±1.5                      |                           | А     |  |

| Reference Voltage             | V <sub>REF</sub>                                         | $V_{DD} = 3V \text{ to } 5.5V, I_{RE}$                      | F = 150μA                               | 1.480                     | 1.515                     | V     |  |

| Reference Load Regulation     | $\Delta V_{REF}$                                         | V <sub>DD</sub> = 3V to 5V, I <sub>REF</sub> = 10μA to 1mA  |                                         |                           | 5                         | mV    |  |

|                               |                                                          | \/                                                          | V <sub>MAXI</sub> = V <sub>REF</sub>    | 140                       | 160                       |       |  |

| MAXIP/MAXIN Threshold         |                                                          | $V_{DD} = 5V$                                               | V <sub>MAXI</sub> = V <sub>REF</sub> /3 | 40                        | 60                        | \ /   |  |

| Accuracy                      |                                                          | \/                                                          | V <sub>MAXI</sub> = V <sub>REF</sub>    | 143                       | 155                       | mV    |  |

|                               |                                                          | $V_{DD} = 3V$                                               | V <sub>MAXI</sub> = V <sub>REF</sub> /3 | 45                        | 55                        |       |  |

| NEET On Desistance            | D                                                        | $V_{DD} = 5V, I = 0.2A$                                     | •                                       |                           | 0.14                      | 0     |  |

| NFET On-Resistance            | R <sub>DS</sub> (ON-N)                                   | V <sub>DD</sub> = 3V, I = 0.2A                              |                                         |                           | 0.16                      | Ω     |  |

| DEET On Designation           | П                                                        | $V_{DD} = 5V, I = 0.2A$                                     |                                         |                           | 0.23                      |       |  |

| PFET On-Resistance            | R <sub>DS</sub> (ON-P)                                   | V <sub>DD</sub> = 3V, I = 0.2A                              |                                         |                           | 0.30                      | Ω     |  |

|                               |                                                          | V <sub>COMP</sub> = V <sub>REF</sub> =                      | 500kHz mode                             |                           | 14                        |       |  |

| No-Load Supply Current        | I <sub>DD(NO</sub>                                       | 1.500V, V <sub>DD</sub> = 5V                                | 1MHz mode                               |                           | 21                        | mA    |  |

| Tho-Load Supply Current       | LOAD)                                                    | V <sub>COMP</sub> = V <sub>REF</sub> =                      | 500kHz mode                             |                           | 11                        | IIIA  |  |

|                               |                                                          | $1.500V, V_{DD} = 3.3V$                                     | 1MHz mode                               |                           | 14                        |       |  |

| Shutdown Supply Current       | IDD-SD                                                   | SHDN = GND, $V_{DD}$ =                                      |                                         | 3                         | mA                        |       |  |

| UVLO Threshold                | VUVLO                                                    | V <sub>DD</sub> rising                                      |                                         | 2.50                      | 2.80                      | V     |  |

| 0.1000010                     | VUVLO                                                    | V <sub>DD</sub> falling                                     | 2.40                                    | 2.70                      | •                         |       |  |

|                               |                                                          | MAX8521, FREQ = $V_{DD}$ , $V_{DD}$ = 3V to 5V              |                                         | 0.8                       | 1.2                       | - MHz |  |

|                               |                                                          | MAX8521, FREQ = 0                                           | 0.4                                     | 0.6                       |                           |       |  |

| Internal Oscillator Switching | fsw-INT                                                  | MAX8520, $R_{EXT} = 60$                                     | 0.8                                     | 1.2                       |                           |       |  |

| Frequency                     | 1200-1101                                                | MAX8520, $R_{EXT} = 60$                                     | 0.76                                    | 1.10                      |                           |       |  |

|                               |                                                          | MAX8520, $R_{EXT} = 15$                                     | 0.4                                     | 0.6                       |                           |       |  |

|                               |                                                          | MAX8520, $R_{EXT} = 15$                                     | 0.36                                    | 0.56                      |                           |       |  |

| External Sync Frequency Range |                                                          | 25% < duty cycle <7                                         | 5% (MAX8521 only)                       | 0.7                       | 1.2                       | MHz   |  |

| LX_ Duty Cycle                |                                                          | (Note 5)                                                    |                                         | 0                         | 100                       | %     |  |

| OS1, OS2, CS Input Current    | I <sub>OS1</sub> , I <sub>OS2</sub> ,<br>I <sub>CS</sub> | 0 or V <sub>DD</sub>                                        |                                         | -100                      | +100                      | μΑ    |  |

| SHDN, FREQ Input Current      | ISHDN,<br>IFREQ                                          | 0 or V <sub>DD</sub> , FREQ applicable for the MAX8521 only |                                         | -5                        | +5                        | μA    |  |

| SHDN, FREQ Input Low Voltage  | VIL                                                      | V <sub>DD</sub> = 3V to 5.5V, FR<br>MAX8521 only            | EQ applicable for the                   |                           | V <sub>DD</sub> x<br>0.25 | V     |  |

| SHDN, FREQ Input High Voltage | V <sub>IH</sub>                                          | $V_{DD} = 3V$ to 5.5V, FR MAX8521 only                      | EQ applicable for the                   | V <sub>DD</sub> x<br>0.75 |                           | V     |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = PV_{DD}1 = PV_{DD}2 = \overline{SHDN} = 5V, 1MHz \text{ mode (Note 2)}. PGND1 = PGND2 = GND, CTLI = MAXV = MAXIP = MAXIN = REF, T_A = -40^{\circ}C to +85^{\circ}C, unless otherwise noted.) (Note 7)$

| PARAMETER                      | SYMBOL                                                 | CONDITIONS                                                                         | MIN  | MAX  | UNITS |

|--------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------|------|------|-------|

| MAXV Threshold Accuracy        |                                                        | $V_{MAXV} = V_{REF} \times 0.67$ , $V_{OS1}$ to $V_{OS2} = \pm 4V$ , $V_{DD} = 5V$ | -2   | +2   | %     |

| WAXV THESHOU Accuracy          |                                                        | $V_{MAXV} = V_{REF} \times 0.33$ , $V_{OS1}$ to $V_{OS2} = \pm 2V$ , $V_{DD} = 3V$ | -3   | +3   | %     |

| MAXV, MAXI_ Input Bias Current | I <sub>MAXV</sub> -<br>BIAS,<br>I <sub>MAXI</sub> BIAS | V <sub>MAXV</sub> = V <sub>MAXI</sub> _ = 0.1V or 1.5V                             | -0.1 | +0.1 | μΑ    |

| CTLI Gain                      | Actli                                                  | V <sub>CTLI</sub> = 0.5V to 2.5V (Note 6)                                          | 9.5  | 10.5 | V/V   |

| CTLI Input Resistance          | RCTLI                                                  | $1M\Omega$ terminated at REF                                                       | 0.5  | 2.0  | МΩ    |

| Error-Amp Transconductance     | Яm                                                     |                                                                                    | 50   | 160  | μS    |

| VITEC Accuracy                 |                                                        | $V_{OS1}$ to $V_{CS} = \pm 100$ mV, $V_{OS1} = V_{DD}/2$                           | -10  | +10  | %     |

**Note 3:** Enter 1MHz mode by tying a  $60k\Omega$  resistor from FREQ to ground for the MAX8520, and tying FREQ to V<sub>DD</sub> for the MAX8521.

Note 4: Includes PFET leakage.

Note 5: Duty-cycle specification is guaranteed by design and not production tested.

Note 6: CTLI Gain is defined as:

$$A_{CTLI} = \frac{\Delta V_{CTLI}}{\Delta \left( V_{OS1} - V_{CS} \right)}$$

Note 7: Specifications to -40°C are guaranteed by design and not production tested.

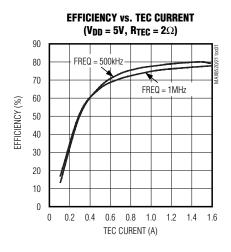

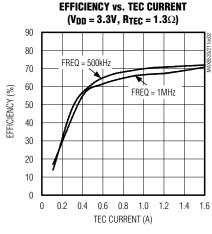

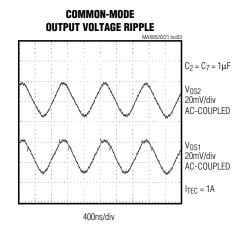

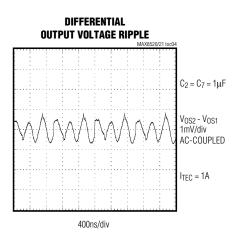

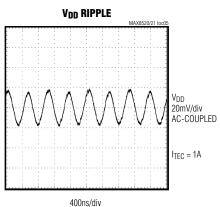

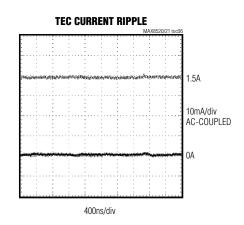

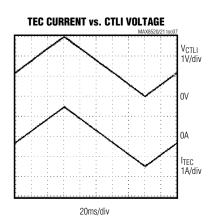

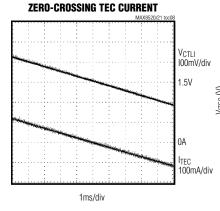

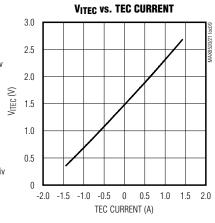

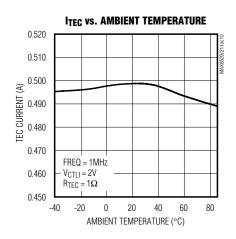

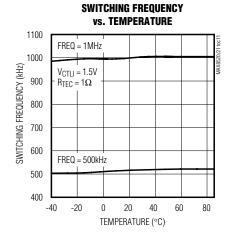

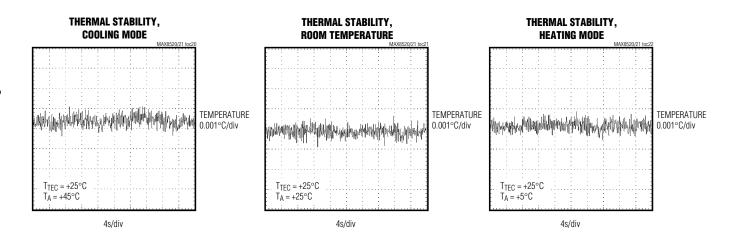

## Typical Operating Characteristics

(V<sub>DD</sub> = 5V, circuit of Figure 1, T<sub>A</sub> = +25°C, unless otherwise noted)

## **Typical Operating Characteristics (continued)**

(V<sub>DD</sub> = 5V, circuit of Figure 1, T<sub>A</sub> = +25°C, unless otherwise noted)

## Typical Operating Characteristics (continued)

(V<sub>DD</sub> = 5V, circuit of Figure 1, T<sub>A</sub> = +25°C unless otherwise noted)

## **Typical Operating Characteristics (continued)**

$(V_{DD} = 5V, circuit of Figure 1, T_A = +25^{\circ}C unless otherwise noted)$

## Pin Description

|     | PIN        |       | FUNCTION                                                                                                                                                                                                                                                                                                                          |  |  |

|-----|------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| QFN | UCSP       | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                          |  |  |

| 1   | E1, E2     | LX1   | Inductor Connection. LX1 is high-impedance in shutdown.                                                                                                                                                                                                                                                                           |  |  |

| 2   | D1, D2, D3 | PGND1 | ower Ground 1. Internal synchronous-rectifier ground connection. Connect all PGND ns together at power ground plane.                                                                                                                                                                                                              |  |  |

| 3   | C1         | SHDN  | Shutdown Control Input. Pull SHDN low to turn off PWM control and ITEC output.                                                                                                                                                                                                                                                    |  |  |

| 4   | C2         | COMP  | Current-Control Loop Compensation. Refer to the Compensation Capacitor section.                                                                                                                                                                                                                                                   |  |  |

| 5   | B1         | ITEC  | TEC Current-Monitor Output. The ITEC output voltage is a function of the voltage across the TEC current-sense resistor. V <sub>ITEC</sub> = V <sub>REF</sub> + 8 (V <sub>OS</sub> - V <sub>CS</sub> ). Keep capacitance on ITEC <150pF.                                                                                           |  |  |

| 6   | A1         | MAXIN | Maximum Negative TEC Current. Connect MAXIN to REF to set default negative current limit to -150mV/R <sub>SENSE</sub> . To lower this current limit, connect MAXIN to a resistor divider network from REF to GND. The current limit will then be equal to -(V <sub>MAXIN</sub> /V <sub>REF</sub> ) x (150mV/R <sub>SENSE</sub> ). |  |  |

| 7   | A2         | MAXIP | Maximum Positive TEC Current. Connect MAXIP to REF to set default positive current limit to 150mV/R <sub>SENSE</sub> . To lower this current limit, connect MAXIP to a resistor divider network from REF to GND. The current limit will then be equal to (VMAXIP/VREF) x (150mV/RSENSE).                                          |  |  |

| 8   | A3         | MAXV  | Maximum Bipolar TEC Voltage. Connect MAXV to REF to set default maximum TEC voltage to V <sub>DD</sub> . To lower this limit, connect MAXV to a resistor-divider network from REF to GND. The maximum TEC voltage is equal to 4 x V <sub>MAXV</sub> or V <sub>DD</sub> , whichever is lower.                                      |  |  |

| 9   | A4         | REF   | 1.50V Reference Output. Bypass REF to GND with a 0. 1µF ceramic capacitor.                                                                                                                                                                                                                                                        |  |  |

## Pin Description (continued)

|     | PIN               |                    | PIN NAME                                                                                                                                                                                                                         |  |  |

|-----|-------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| QFN | UCSP              | FUNCTION           |                                                                                                                                                                                                                                  |  |  |

| 10  | A5                | CTLI               | TEC Current-Control Input. Sets TEC current. Center point is 1.50V (no TEC current). The current is given by:<br>ITEC = (VOS1 - VCS) / RSENSE = (VCTLI - 1.50) / (10 x RSENSE). When (VCTLI - VREF) > 0, then VOS2 > VOS1 > VCS. |  |  |

| 11  | A6                | GND                | Analog Ground. Start connect to PGND at underside exposed pad for QFN package.                                                                                                                                                   |  |  |

| 12  | B6                | $V_{DD}$           | Analog Supply Voltage Input. Bypass V <sub>DD</sub> to GND with a 1µF ceramic capacitor.                                                                                                                                         |  |  |

|     |                   |                    | For MAX8520: Analog FREQ Set Pin (see the Switching Frequency section).                                                                                                                                                          |  |  |

| 13  | C5                | FREQ               | For MAX8521: Digital FREQ Selection Pin. Tie to V <sub>DD</sub> for 1MHz operation, tie to GND for 500kHz operation. The PWM oscillator can synchronize to FREQ by switching at FREQ between 700kHz and 1.2MHz.                  |  |  |

| 14  | D4, D5, D6        | PGND2              | Power Ground 2. Internal synchronous rectifier ground connection. Connect all PGND pins together at the power ground plane.                                                                                                      |  |  |

| 15  | E5, E6            | LX2                | Inductor Connection. LX2 is high impedance in shutdown.                                                                                                                                                                          |  |  |

| 16  | F5, F6            | PV <sub>DD</sub> 2 | Power Input 2. Connect all PVDD inputs together at the VDD power plane.                                                                                                                                                          |  |  |

| 17  | F4                | CS                 | Current-Sense Input. The current through the TEC is monitored between CS and OS1. The maximum TEC current is given by 150mV/R <sub>SENSE</sub> and is bipolar.                                                                   |  |  |

| 18  | C6                | OS2                | Output Sense 2. OS2 senses one side of the differential TEC voltage. OS2 is a sense point, not a power output. OS2 discharges to ground in shutdown.                                                                             |  |  |

| 19  | F3                | OS1                | Output Sense 1. OS1 senses one side of the differential TEC voltage. OS1 is a sense point, not a power output. OS1 discharges to ground in shutdown.                                                                             |  |  |

| 20  | F1, F2            | PV <sub>DD</sub> 1 | Power Input 1. Connect all PVDD inputs together at the VDD power plane.                                                                                                                                                          |  |  |

|     | B2, B5,<br>C3, C4 | GND2               | Ground. Additional ground pads aid in heat dissipation. Short to either GND or PGND plane.                                                                                                                                       |  |  |

|     | B3, B4<br>E3, E4  | N.C.               | No Connect. Connect no-connect pads to GND2 to aid in heat dissipation.                                                                                                                                                          |  |  |

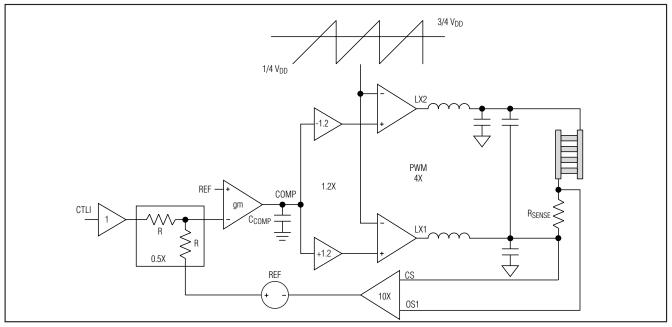

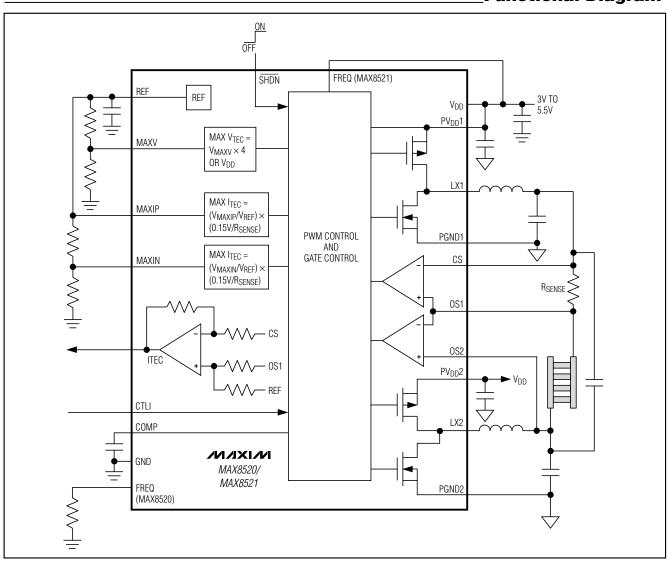

### **Detailed Description**

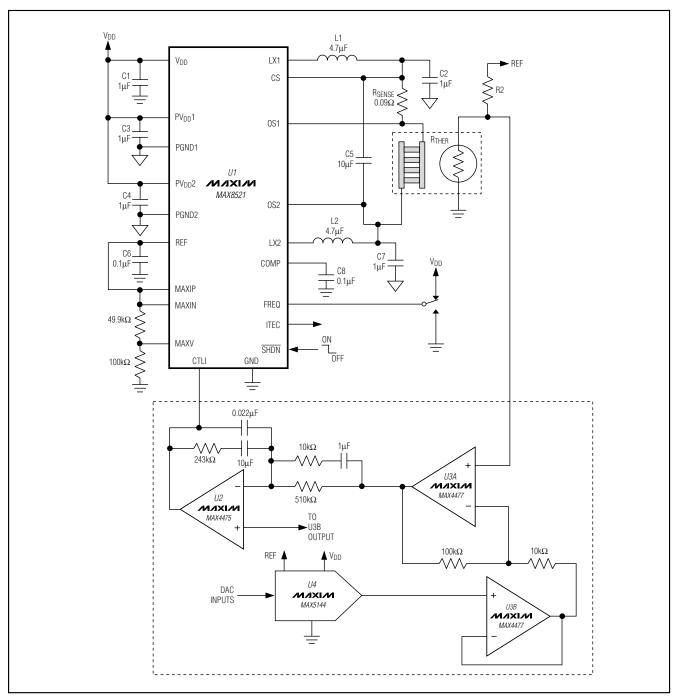

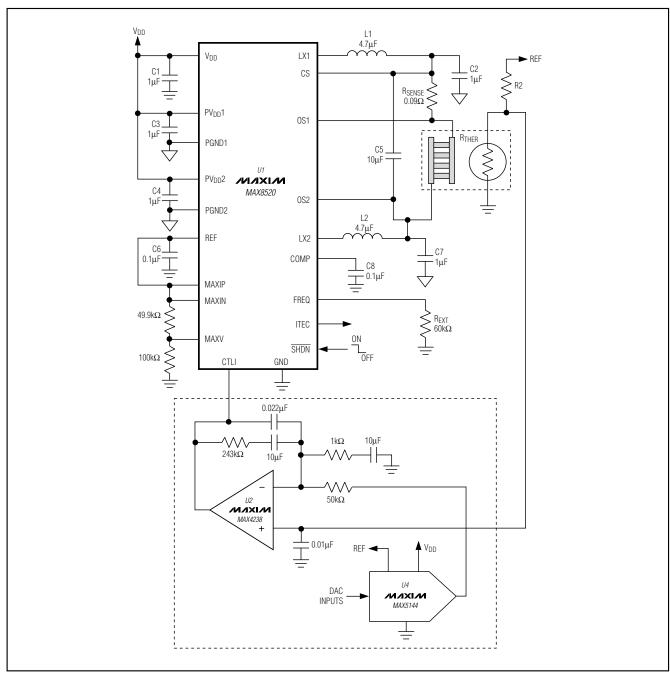

The MAX8520/MAX8521 TEC drivers consist of two switching buck regulators that operate together to directly control the TEC current. This configuration creates a differential voltage across the TEC, allowing bidirectional TEC current for controlled cooling and heating. Controlled cooling and heating allow accurate TEC temperature control to within ±0.01°C. The voltage at CTLI directly sets the TEC current. An external thermal- control loop is typically used to drive CTLI. Figures 1 and 2 show examples of the thermal control-loop circuit.

#### **Ripple Cancellation**

Switching regulators like those used in the MAX8520/MAX8521 inherently create ripple voltage on the output. The dual regulators in the MAX8520/MAX8521 switch in phase and provide complementary in-phase duty cycles so ripple waveforms at the TEC are greatly reduced. This feature suppresses ripple currents and electrical noise at the TEC to prevent interference with the laser diode.

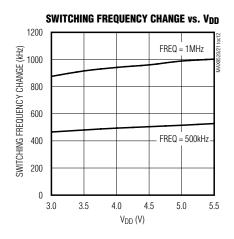

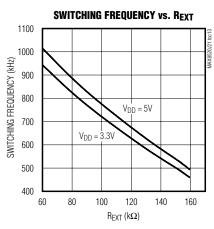

#### Switching Frequency

For the MAX8521, FREQ sets the switching frequency of the internal oscillator. With FREQ = GND, the oscillator frequency is set to 500kHz. The oscillator frequency is 1MHz when FREQ =  $V_{DD}$ .

For the MAX8520, connect a resistor (R<sub>EXT</sub> in Figure 2) from FREQ to GND. Choose R<sub>EXT</sub> =  $60k\Omega$  for 1MHz operation, and R<sub>EXT</sub> =  $150k\Omega$  for 500kHz operation. For any intermediary frequency between 500kHz and 1MHz, use the following equation to find the value of R<sub>EXT</sub> value needed for V<sub>DD</sub> = 5V:

$$R_{EXT} = 90 \times \left(\frac{1}{fs} - \frac{1}{3}\right)$$

where R<sub>EXT</sub> is the resistance given in k $\Omega$ , and fs is the desired frequency given in MHz. Note that for V<sub>DD</sub> < 5V, the frequency is reduced slightly, to the extent of about 7% when V<sub>DD</sub> reaches 3V. This should be taken into consideration when selecting the value for R<sub>EXT</sub> at a known supply voltage.

#### **Voltage and Current-Limit Setting**

Both the MAX8520 and MAX8521 provide control of the maximum differential TEC voltage. Applying a voltage to MAXV limits the maximum voltage across the TEC. The voltage at MAXIP and MAXIN sets the maximum positive and negative current through the TEC. These current limits can be independently controlled.

**Table 1. TEC Connection for Figure 1**

| TEC CONNECTION | THERMISTOR |

|----------------|------------|

| Heating mode   | PTC        |

| Cooling mode   | NTC        |

#### **Table 2. TEC Connection for Figure 2**

| TEC CONNECTION | THERMISTOR |

|----------------|------------|

| Heating mode   | NTC        |

| Cooling mode   | PTC        |

#### **Current Monitor Output**

ITEC provides a voltage output proportional to the TEC current (ITEC). See the *Functional Diagram* for more details:

$$VITEC = 1.5V + (8 \times (VOS1-VCS))$$

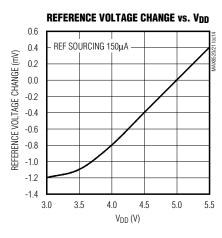

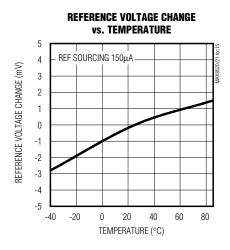

#### Reference Output

The MAX8520/MAX8521 include an on-chip voltage reference. The 1.50V reference is accurate to 1% over temperature. Bypass REF with  $0.1\mu F$  to GND. REF can be used to bias an external thermistor for temperature sensing as shown in Figures 1 and 2.

#### **Thermal and Fault-Current Protection**

The MAX8520/MAX8521 provide fault-current protection in either FET by turning off both high-side and low-side FETs when the peak current exceeds 3A in either FET. In addition, thermal-overload protection limits the total power dissipation in the chip. When the device's die junction temperature exceeds +165°C, an on-chip thermal sensor shuts down the device. The thermal sensor turns the device on again after the junction temperature cools down by 15°C.

#### **Design Procedures**

#### **Duty-Cycle Range Selection**

By design, the MAX8520/MAX8521 are capable of operating from 0% to 100% duty cycle, allowing both LX outputs to enter dropout. However, as the LX pulse width narrows, accurate duty-cycle control becomes difficult. This can result in a low-frequency noise appearing at the TEC output (typically in the 20kHz to 50kHz range). While this noise is typically filtered out by the low thermal-loop bandwidth, for best results, operate the PWM with a pulse width greater than 200ns. For a 500kHz application, the recommended duty-cycle range is from 10% to 90%. For a 1MHz application, it is from 20% to 80%.

Figure 1. MAX8521 Typical Application Circuit

Figure 2. Typical Application Circuit for the MAX8520 with Reduced Op-Amp Count Configuration

Figure 3. Functional Diagram of the Current-Control Loop

#### **Inductor Selection**

The MAX8520/MAX8521 dual buck converters operate in phase and in complementary mode to drive the TEC differentially in a current-mode control scheme. At zero TEC current, the differential voltage is zero; hence, the outputs with respect to GND are equal to half of VDD. As the TEC current demand increases, one output goes up and the other goes down from the initial point of 0.5VDD by an amount equal to 0.5 x VTEC (VTEC = ITEC x RTEC). Therefore, the operating duty cycle of each buck converter depends on the operating ITEC and RTEC. Since inductor current calculations for heating and cooling are identical, but reverse in polarity, the calculations only need to be carried out for either one.

For a given inductor and input voltage, the maximum inductor ripple current happens when the duty cycle is at 50%. Therefore, the inductor should be calculated at 50% duty cycle to find the maximum ripple current. The maximum desired ripple current of a typical standard buck converter is in the range of 20% to 40% of the maximum load. The higher the value of the inductor, the lower the ripple current. However, the size is physically larger. For the TEC driver, the thermal loop is inherently slow, so the inductor can be larger for lower ripple current for better noise and EMI performance. Picking an inductor to yield ripple current of 10% to 20% of the maximum TEC current is a good starting point.

Calculate the inductor value as follows:

$$L = \frac{(0.25 \times V_{DD})}{LIR \times I_{TEC(MAX)} \times fs}$$

where LIR is the selected inductor ripple-current ratio, ITEC(MAX) is the maximum TEC current, and fs is the switching frequency.

As an example, for  $V_{DD} = 3.3V$ , LIR = 12%, and fs = 1MHz, L =  $4.58\mu$ H.

Even though each inductor ripple current is at its maximum at 50% duty cycle (zero TEC current), the ripple cancels differentially because each is equal and in phase.

## Output Filter Capacitor Selection

#### **Common-Mode Filter Capacitors**

The common-mode filter capacitors (C2 and C7 of Figure 1) are used as filter capacitors to ground for each output. The output ripple voltage depends on the capacitance, the ESR of these capacitors, and the inductor ripple current. Ceramic capacitors are recommended for their low ESR and impedance at high frequency.

The output common-mode ripple voltage can be calculated as follows:

$V_{RIPPLE(P-P)} = LIR \times I_{TEC(MAX)} (ESR + 1/8 \times C \times fs)$

A 1µF ceramic capacitor with ESR of  $10m\Omega$  with LIR = 12% and ITEC(MAX) = 1.5A results in VRIPPLE(P-P) of 24.3mV. For size-constraint applications, the capacitor can be made smaller at the expense of higher ripple voltage. However, the capacitance must be high enough so that the LC resonant frequency is less than 1/5 the switching frequency:

$$f = \frac{1}{2\pi\sqrt{LC}}$$

where f is the resonant frequency of the output filter.

#### **Differential Mode Filter Capacitor**

The differential-mode filter capacitor (C5 in Figure 1) is used to bypass differential ripple current through the TEC as the result of unequal duty cycle of each output. This happens when the TEC current is not at zero. As TEC current increases from zero, both outputs move away from the 50% duty-cycle point complementarily. The common-mode ripple decreases, but the differential ripple does not cancel perfectly, and there is a resulting differential ripple. The maximum value happens when one output is at 75% duty cycle and the other is at 25% duty cycle. At this operating point, the differential ripple is equal to 1/2 of the maximum common-mode ripple. The TEC ripple current determines the TEC performance, because the maximum temperature differential that can be created between the terminals of the TEC depends on the ratio of ripple current and DC current. The lower the ripple current, the closer to the ideal maximum. The differential-mode capacitor provides a low-impedance path for the ripple current to flow, so that the TEC ripple current is greatly reduced. The TEC ripple current can then be calculated as follows:

ITEC(RIPPLE) = (0.5 x LIR x ITEC(MAX)) x (ZC5)/(RTEC + RSENSE + ZC5)

where  $Z_{C5}$  is the impedance of C5 at twice the switching frequency,  $R_{TEC}$  is the TEC equivalent resistance, and  $R_{SENSE}$  is the current-sense resistor.

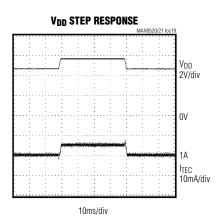

#### **Decoupling Capacitor Selection**

Decouple each power-supply input ( $V_{DD}$ ,  $PV_{DD}1$ ,  $PV_{DD}2$ ) with a 1µF ceramic capacitor close to the supply pins. In applications with long distances between the source supply and the MAX8520/MAX8521, additional

bypassing may be needed to stabilize the input supply. In such cases, a low-ESR electrolytic or ceramic capacitor of 100µF or more at V<sub>DD</sub> is sufficient.

#### **Compensation Capacitor**

A compensation capacitor is needed to ensure current-control-loop stability (see Figure 3). Select the capacitor so that the unity-gain bandwidth of the current-control loop is less than or equal to 10% the resonant frequency of the output filter:

$$C_{COMP} \ge \left(\frac{g_{m}}{f_{BW}}\right) \times \left(\frac{24 \times R_{SENSE}}{2\pi (R_{SENSE} \times R_{TEC})}\right)$$

where:

fBW = unity-gain bandwidth frequency, less than or equal to 10% the output filter resonant frequency

gm = loop transconductance, typically 100µA/V

CCOMP = value of the compensation capacitor

R<sub>TEC</sub> = TEC series resistance; use the minimum resistance value

Rsense = sense resistor

#### **Setting Voltage and Current Limits**

Certain TEC parameters must be considered to guarantee a robust design. These include maximum positive current, maximum negative current, and the maximum voltage allowed across the TEC. These limits should be used to set the MAXIP, MAXIN, and MAXV voltages.

#### Setting Max Positive and Negative TEC Current

MAXIP and MAXIN set the maximum positive and negative TEC currents, respectively. The default current limit is  $\pm 150 \text{mV/RSENSE}$  when MAXIP and MAXIN are connected to REF. To set maximum limits other than the defaults, connect a resistor-divider from REF to GND to set  $\text{V}_{\text{MAXI}}$ . Use resistors in the  $10 \text{k}\Omega$  to  $100 \text{k}\Omega$  range.  $\text{V}_{\text{MAXI}}$  is related to ITEC by the following equations:

VMAXIP = 10(ITECP(MAX) × RSENSE)

$V_{MAXIN} = 10(I_{TECN(MAX)} \times R_{SENSE})$

where ITECP(MAX) is the maximum positive TEC current and ITECN(MAX) is the negative maximum TEC current. Positive TEC current occurs when CS is less than OS1:

when ITEC > 0.

ITEC × RSENSE = CS - OS1

when ITEC < 0.

Take care not to exceed the positive or negative current limit on the TEC. Refer to the manufacturer's data sheet for these limits.

#### **Setting Max TEC Voltage**

Apply a voltage to the MAXV pin to control the maximum differential TEC voltage. MAXV can vary from 0 to REF. The voltage across the TEC is four times V<sub>MAXV</sub> and can be positive or negative:

IV<sub>OS1</sub> - V<sub>OS2</sub>I = 4 x V<sub>MAXV</sub> or V<sub>DD</sub>, whichever is lower Set V<sub>MAXV</sub> with a resistor-divider between REF and GND using resistors from 10k $\Omega$  to 100k $\Omega$ . V<sub>MAXV</sub> can vary from 0 to REF.

### **Control Inputs/Outputs**

#### **Output Current Control**

The voltage at CTLI directly sets the TEC current. CTLI is typically driven from the output of a temperature control loop. The transfer function relating current through the TEC (ITEC) and VCTLI is given by:

ITEC = (VCTLI - VREF) / (10 x RSENSE)

where VREF is 1.50V and:

CTLI is centered around REF (1.50V). ITEC is zero when CTLI = 1.50V. When  $V_{CTLI} > 1.50V$ , the current flow is from OS2 to OS1. The voltages on the pins relate as follows:

Vos2 > Vos1 > Vcs

The opposite applies when  $V_{CTLI}$  < 1.50V current flows from OS1 to OS2:

Vos2 < Vos1 < Vcs

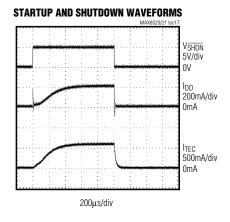

#### Shutdown Control

The MAX8520/MAX8521 can be <u>placed</u> in a power-saving shutdown mode by driving <u>SHDN</u> low. When the MAX8520/MAX8521 are shut down, the TEC is off (OS1 and OS2 decay to GND) and supply current is reduced to 2mA (typ).

#### ITEC Output

ITEC is a status output that provides a voltage proportional to the actual TEC current. V<sub>ITEC</sub> = REF when TEC current is zero. The transfer function for the ITEC output is:

$VITEC = 1.50 + 8 \times (VOS1 - VCS)$

Use ITEC to monitor the cooling or heating current through the TEC. For stability, keep the load capacitance on ITEC to less than 150pF.

### **Applications Information**

The MAX8520/MAX8521 typically drive a TEC inside a thermal-control loop. TEC drive polarity and power are regulated based on temperature information read from a thermistor or other temperature-measuring device to maintain a stable control temperature. Temperature stability of ±0.01°C can be achieved with carefully selected external components.

There are numerous ways to implement the thermal loop. Figures 1 and 2 show designs that employ precision op amps, along with a DAC or potentiometer to set the control temperature. The loop may also be implemented digitally, using a precision A/D to read the thermistor or other temperature sensor, a microcontroller to implement the control algorithm, and a DAC (or filtered-PWM signal) to send the appropriate signal to the MAX8520/MAX8521 CTLI input. Regardless of the form taken by the thermal-control circuitry, all designs are similar in that they read temperature, compare it to a set-point signal, and then send an error-correcting signal to the MAX8520/MAX8521 that moves the temperature in the appropriate direction.

#### **PC Board Layout and Routing**

High switching frequencies and large peak currents make PC board layout a very important part of design. Good design minimizes excessive EMI and voltage gradients in the ground plane, both of which can result in instability or regulation errors. Follow these guidelines for good PC board layout:

- 1) Place decoupling capacitors as close to the IC pins as possible.

- 2) Keep a separate power ground plane, which is connected to PGND1 and PGND2. PVDD1, PVDD2, PGND1, and PGND2 are noisy points. Connect decoupling capacitors from PVDDs to PGNDs as directly as possible. Output capacitors C2 and C7 returns are connected to PGND plane.

- 3) Connect a decoupling capacitor from V<sub>DD</sub> to GND. Connect GND to a signal ground plane (separate from the power ground plane above). Other V<sub>DD</sub> decoupling capacitors (such as the input capacitor) need to be connected to the PGND plane.

- 4) Connect GND and PGND\_ pins together at a single point, as close as possible to the chip.

- 5) Keep the power loop, which consists of input capacitors, output inductors, and capacitors, as compact and small as possible.

6) To ensure high DC loop gain and minimum loop error, keep the board layout adjacent to the negative input pin of the integrator (U2 in Figure1) clean and free of moisture. Any contamination or leakage current into this node can act to lower the DC gain of the integrator, which can degrade the accuracy of the thermal loop. If space is available, it can also be helpful to surround the negative input node of the integrator with a grounded guard ring. Refer to the MAX8520/MAX8521 evaluation kit for a PC board layout example.

Chip Information

TRANSISTOR COUNT: 3007

PROCESS: BiCMOS

## Pin Configurations

## Functional Diagram

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to www.maxim-ic.com/packages.)

|        | COMMON DIMENSIONS |           |            |           |         |           |      |         |           |         |      |      |

|--------|-------------------|-----------|------------|-----------|---------|-----------|------|---------|-----------|---------|------|------|

| PKG.   |                   | 16L 5x5   |            |           | 20L 5x5 |           |      | 28L 5x5 |           | 32L 5x5 |      |      |

| SYMBOL | MIN.              | NOM.      | MAX.       | MIN.      | NOM.    | MAX.      | MIN. | NOM.    | MAX.      | MIN.    | NOM. | MAX  |

| Α      | 0.70              | 0.75      | 0.80       | 0.70      | 0.75    | 0.80      | 0.70 | 0.75    | 0.80      | 0.70    | 0.75 | 0.80 |

| A1     | 0                 | 0.02      | 0.05       | 0         | 0.02    | 0.05      | 0    | 0.02    | 0.05      | 0       | 0.02 | 0.05 |

| A3     | (                 | 0.20 REF. |            | 0.20 REF. |         | 0.20 REF. |      |         | 0.20 REF. |         |      |      |

| ь      | 0.25              | 0.30      | 0.35       | 0.25      | 0.30    | 0.35      | 0.20 | 0.25    | 0.30      | 0.20    | 0.25 | 0.30 |

| D      | 4.90              | 5.00      | 5.10       | 4.90      | 5.00    | 5.10      | 4.90 | 5.00    | 5.10      | 4.90    | 5.00 | 5.10 |

| Е      | 4.90              | 5.00      | 5.10       | 4.90      | 5.00    | 5.10      | 4.90 | 5.00    | 5.10      | 4.90    | 5.00 | 5.10 |

|        |                   | 0.80 BS(  | <b>3</b> . | 0.65 BSC. |         | 0.50 BSC. |      |         | 0.50 BSC. |         |      |      |

| k      | 0.25              | -         | -          | 0.25      | -       | -         | 0.25 | -       | -         | 0.25    | -    | -    |

| L      | 0.45              | 0.55      | 0.65       | 0.45      | 0.55    | 0.65      | 0.45 | 0.55    | 0.65      | 0.30    | 0.40 | 0.50 |

| N      |                   | 16        |            |           | 20      |           | 28   |         |           | 32      |      |      |

| ND     | 4                 |           | 5          |           | 7       |           | 8    |         |           |         |      |      |

| NE     | 4                 |           | 5          |           | 7       |           | 8    |         |           |         |      |      |

| JEDEC  |                   | WHHB      |            |           | WHHC    |           |      | WHHD-   | 1         |         | WHHD | -2   |

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |

|------------------------|------|------|------|------|------|------|

| PKG.<br>CODES          | D2   |      |      | E2   |      |      |

|                        | MIN. | NOM. | MAX. | MIN. | NOM. | MAX. |

| T1655-1                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |

| T2055-2                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |

| T2855-1                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |

| T2855-2                | 2.60 | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 |

| T3255-2                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |

- 2. ALL DIMENSIONS ARE IN MILLIMETERS, ANGLES ARE IN DEGREES.

- 2. ALL DIMENSIONS ARE IN WILLIMS LEAD, AND LES ARE IN DEGREES.

3. NI STHE TOTAL NUMBER OF TERMINALS.

THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 96-1

SPR-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MIST BE LOCATED WITHIN THE

ZONE NIDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- ⚠ DIMENSION b APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

- ▲ ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- 9. DRAWING CONFORMS TO JEDEC MO220.

- 10. WARPAGE SHALL NOT EXCEED 0.10 mm

## Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.