# XICOR®

#### **New Industry Features**

- Programmable time sequencing

Integrated oscillator and dividers

- No crystal required

- Quad voltage monitors

- Remote delay selection

- Remote monitor/switch diagnostics

Cascade delays of multiple devices

# X80140/41/42/43/44

Voltage Supervisor/Sequencer Quad Programmable Time Delay with Local/ Remote Voltage Monitors

#### FEATURES

- Quad voltage Monitor and Sequencing

- Four independent voltage monitors

- Four time delay circuits (in circuit programmable)

- Remote delay via SMBus

- Programmable voltage thresholds and delay times

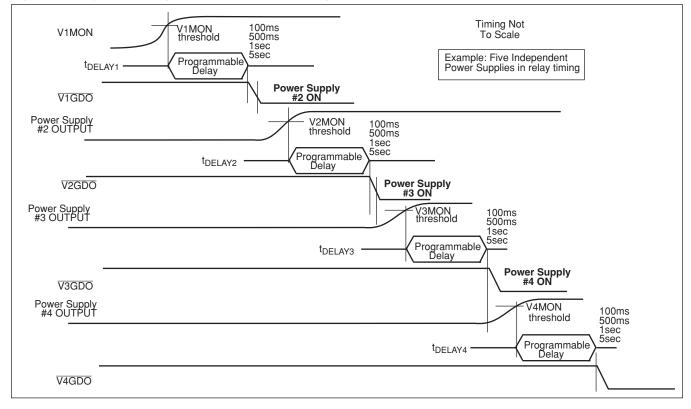

- Sequence up to 5 power supplies.

- · Fault detection register

- Remote diagnostics of voltage fail event.

- · Debounced manual reset input

- Manufacturing/Configuration Memory

- 2Kbits of EEPROM

- 400kHz SMBus interface

- Available packages

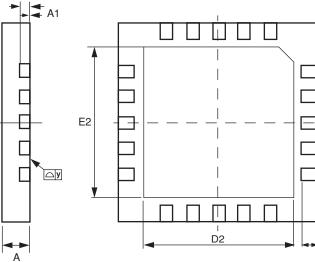

- 20-lead Quad No-Lead Frame (QFN 5 x 5 mm)

#### **APPLICATIONS**

- General Purpose Timers

- Long Time Delay Generation

- Cycle Timers / Waveform Generation

- ON/OFF Delay Timers

- Supply Sequencing for Distributed Power

- Programmable Delay Event Sequencing

- Multiple DC-DC ON/OFF Sequencing

- Voltage Window Monitoring with Reset

- ON/OFF switches with Programmable Delay

- Voltage Supervisor with Programmable Output Delays

- Databus Power Sequencing

- 100 ms to 5 secs Selectable Delay Switches

- ATE or Data Acquisition Timing Applications

- Datapath/Memory Timing Applications

- Data Pipeline Timing Applications

- Batch Timer/Sequencers

- Adjustable Duty Cycle Applications

#### **DESCRIPTION**

The X80140 is a voltage supervisor/sequencer with four built in voltage monitors. This allows the designer to monitor up to four voltages and sequence up to five events.

Low voltage detection circuitry protects the system from power supply failure or "brown out" conditions, resetting the system and resequencing the voltages when any of the monitored inputs fall below the minimum threshold level. The RESET pin is active until all monitored voltages reach proper operating levels and stabilize for a selectable period of time. Five common low voltage combinations are available, however, Xicor's unique circuits allow the any voltage monitor threshold to be reprogrammed for special needs or for applications requiring higher precision.

A manual reset input provides debounce circuitry for minimum reset component count. Activating the manual reset both controls the  $\overline{\text{RESET}}$  output and resequences the supplies through control of the  $\overline{\text{ViGDO}}$  pins.

The X80140 has 2kb of EEPROM for system configuration, manufacturing or maintenance information. This memory is protected to prevent inadvertent changes to the contents.

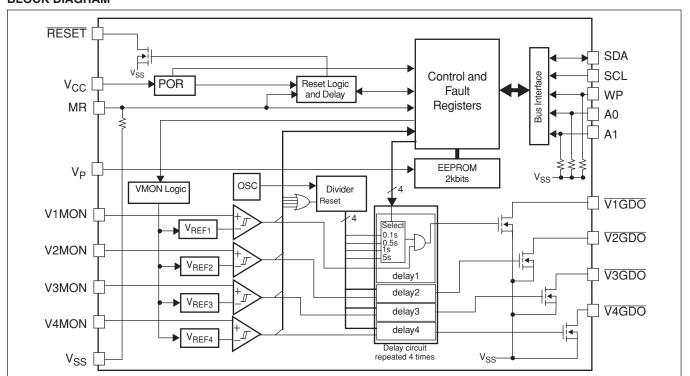

#### **BLOCK DIAGRAM**

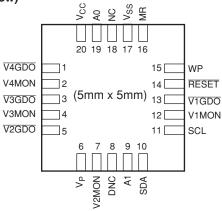

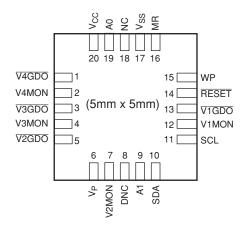

#### **PIN OUTS**

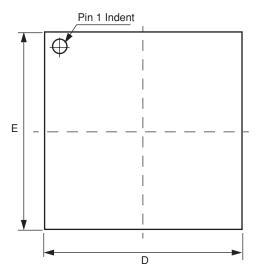

# QFN package (Top view)

#### **ORDERING INFORMATION**

| ORDER<br>NUMBER | V <sub>REF1</sub> | V <sub>REF2</sub> | V <sub>REF3</sub> | V <sub>REF4</sub> | Package |

|-----------------|-------------------|-------------------|-------------------|-------------------|---------|

| X80140Q20I      | 4.5               | 3.0               | 2.25              | 0.9               | QFN     |

| X80141Q20I      | 4.5               | 2.25              | 0.9               | 0.9               | QFN     |

| X80142Q20I      | 3.0               | 2.25              | 1.7               | 0.9               | QFN     |

| X80143Q20I      | 3.0               | 2.25              | 0.9               | 0.9               | QFN     |

| X80144Q20I      | 2.25              | 2.25              | 0.9               | 0.9               | QFN     |

#### **ABSOLUTE MAXIMUM RATINGS**

| Temperature under bias –65°C to +135°         | °C |

|-----------------------------------------------|----|

| Storage temperature –65°C to +150°            | °C |

| ViMON pins (i = 1 to 4)                       | 5V |

| ViGDO pins (i = 1 to 4)                       | 5V |

| RESET pin5.5                                  | 5V |

| SDA, SCL, WP, A0, A1 pins5.5                  | 5V |

| MR pin5.5                                     | 5V |

| V <sub>P</sub> pin14                          | 1V |

| D.C. output current5m                         | ۱A |

| Lead temperature (soldering, 10 seconds) 300° | °C |

#### COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; functional operation of the device (at these or any other conditions above those listed in the operational sections of this specification) is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

| Temperature    | Min.  | Max.  |

|----------------|-------|-------|

| Industrial (I) | −40°C | +85°C |

| Supply Voltage                          | П |

|-----------------------------------------|---|

| $V_{DD} = 2.7 \text{ to } 5.5 \text{V}$ |   |

#### **ELECTRICAL CHARACTERISTICS** (Standard Settings)

| Symbol                        | Parameter                                                        | Min.    | Тур. | Max.    | Unit | Test Conditions            |  |  |

|-------------------------------|------------------------------------------------------------------|---------|------|---------|------|----------------------------|--|--|

| DC Charac                     | DC Characteristics                                               |         |      |         |      |                            |  |  |

| V <sub>CC</sub>               | Supply Operating Range                                           | 2.7     |      | 5.5     | V    |                            |  |  |

| I <sub>CC</sub>               | Supply Current                                                   |         | 2.7  | 5       | mA   |                            |  |  |

| V <sub>P</sub> <sup>(3)</sup> | EEPROM programming voltage                                       | 9       |      | 12      | V    |                            |  |  |

| Ι <sub>P</sub>                | Programming Current                                              |         |      | 10      | mA   |                            |  |  |

| ILI                           | Input Leakage Current (MR)                                       |         |      | 10      | μA   | $V_{IL}$ = GND to $V_{CC}$ |  |  |

| I <sub>LO</sub>               | Output Leakage Current<br>(V1GDO, V2GDO, V3GDO,<br>V4GDO, RESET) |         |      | 15      | μA   |                            |  |  |

| V <sub>IL</sub>               | Input LOW Voltage (MR)                                           | -0.5    |      | 5 x 0.3 | V    |                            |  |  |

| V <sub>IH</sub>               | Input HIGH Voltage (MR)                                          | 5 x 0.7 |      | 5.5     | V    |                            |  |  |

| V <sub>OL</sub>               | Output LOW Voltage<br>(RESET, V1GDO, V2GDO,<br>V3GDO, V4GDO)     |         |      | 0.4     | V    | I <sub>OL</sub> = 4.0 mA   |  |  |

#### **ELECTRICAL CHARACTERISTICS** (Continued)(Standard Settings)

(Over the recommended operating conditions unless otherwise specified).

| COUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Symbol                              | Parameter                         | Min. | Тур. | Max. | Unit | Test Conditions       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------------|------|------|------|------|-----------------------|

| Variable   Variable | C <sub>OUT</sub> <sup>(1)</sup>     |                                   |      |      | 8    | pF   | V <sub>OUT</sub> = 0V |

| Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                     |                                   |      |      |      |      |                       |

| X80140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                     |                                   |      |      |      |      |                       |

| X80141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V <sub>REF1</sub>                   |                                   |      |      |      | V    |                       |

| X80142   2.95   3.00   3.05   X80143   2.95   3.00   3.05   X80144   2.20   2.25   2.30   X80144   0.85   0.90   0.95   X80145   X80146   0.85   0.90   0.95   X80146   0.85   0.90   0 |                                     |                                   | _    |      |      |      |                       |

| X80143   2.95   3.00   3.05   2.30   X80144   2.20   2.25   2.30   X80142   2.20   2.25   2.30   X80143   2.20   2.25   2.30   X80144   2.20   2.25   2.30   X80141   0.85   0.90   0.95   X80144   0.85   0.90   0.95   X80145   X80146   0.80   0.95   0.95   X80146   0.80   0.95   X80146   0.80   0.95   X80146   0.8 |                                     |                                   |      |      |      |      |                       |

| X80144   2.20   2.25   2.30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                     |                                   |      | 1    |      |      |                       |

| Valor Val |                                     |                                   |      |      |      |      |                       |

| X80140   2.95   3.00   3.05   X80141   2.20   2.25   2.30   X80142   2.20   2.25   2.30   X80143   2.20   2.25   2.30   X80143   2.20   2.25   2.30   X80144   2.20   2.25   2.30   X80144   2.20   2.25   2.30   X80144   2.20   2.25   2.30   X80141   0.85   0.90   0.95   X80141   0.85   0.90   0.95   X80142   1.65   1.70   1.75   X80143   0.85   0.90   0.95   X80144   0.85   0.90   0.95   X80145   0.85   0.90   0.95   X80146   0.85   0.90   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.95   0.9 |                                     |                                   |      | 2.25 |      |      |                       |

| X80141   2.20   2.25   2.30   X80142   2.20   2.25   2.30   X80143   2.20   2.25   2.30   X80144   0.85   0.90   0.95   X80141   0.85   0.90   0.95   X80142   1.65   1.70   1.75   X80143   0.85   0.90   0.95   X80144   0.85   0.90   0.95   X80146   0.85   0.90   0.95   0.95   X80146   0.85   0.90   0.9 | V <sub>REF2</sub>                   |                                   |      |      |      | V    |                       |

| X80142   2.20   2.25   2.30   X80143   2.20   X80144   2.20   2.25   2.30   X80141   0.85   0.90   0.95   X80142   1.65   1.70   1.75   X80143   0.85   0.90   0.95   X80144   0.85   0 |                                     |                                   |      |      |      |      |                       |

| X80143   2.20   2.25   2.30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                     |                                   |      |      |      |      |                       |

| Variable   Variable |                                     |                                   |      | 1    |      |      |                       |

| VREF3       V3MON Trip Point Voltage       0.80       3.5       V         X80140       2.20       2.25       2.30       V         X80141       0.85       0.90       0.95       V         X80142       1.65       1.70       1.75       V         X80143       0.85       0.90       0.95       V         VREF4       V4MON Trip Point Voltage       0.80       3.5       V         All Devices       0.85       0.90       0.95       V         AC Characteristics         t <sub>MR</sub> (3)       Minimum time high for reset valid on the MR pin       5       μs         t <sub>MRE</sub> (1)       Delay from MR enable to V1GDO HIGH       1.0       1.6       μs         t <sub>RESET_E</sub> (3)       Delay from ViGDO to RESET valid LOW       1       μs         t <sub>DPOR</sub> (3)       Internal Device Delay on power up       45       50       55       ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                     |                                   |      |      |      |      |                       |

| X80140   2.20   2.25   2.30   X80141   0.85   0.90   0.95   X80142   1.65   1.70   1.75   X80143   0.85   0.90   0.95   X80144   0.85   0.90   0.95   X80 |                                     |                                   |      | 2.25 |      |      |                       |

| X80141   0.85   0.90   0.95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>REF3</sub>                   |                                   |      |      |      | V    |                       |

| X80142   1.65   1.70   1.75   X80143   0.85   0.90   0.95   X80144   0.85   0.90   0.95   X80144   0.85   0.90   0.95   0.95   0.90   0.95   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.90   0.95   0.90   0.95   0.90   0.95   0.90   0.90   0.90   0.90   0.95   0.90   0.90   0.90   0.90   0.90   0.90   0.90   0.90   0.90  |                                     |                                   |      |      |      |      |                       |

| X80143   0.85   0.90   0.95   0.95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                     |                                   |      |      |      |      |                       |

| X80144   0.85   0.90   0.95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                     |                                   |      | 1    |      |      |                       |

| V <sub>REF4</sub> V4MON Trip Point Voltage All Devices         0.80 0.85         3.5 0.90         V           AC Characteristics         t <sub>MR</sub> <sup>(3)</sup> Minimum time high for reset valid on the MR pin         5 0.90         μs           t <sub>MR</sub> <sup>(3)</sup> On the MR pin         1.0 0.80         1.6 0.90         μs           t <sub>MRE</sub> <sup>(1)</sup> Delay from MR enable to V1GDO HIGH         1.0 0.95         1.6 0.90         μs           t <sub>RESET_E</sub> <sup>(3)</sup> Delay from ViGDO to RESET valid LOW         1 0.90         1 0.90         1 0.90         1 0.90           t <sub>DPOR</sub> <sup>(3)</sup> Internal Device Delay on power up         45 0.90         55 0.90         55 0.90         ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                     |                                   |      | 1    |      |      |                       |

| All Devices 0.85 0.90 0.95  AC Characteristics  t <sub>MR</sub> <sup>(3)</sup> Minimum time high for reset valid on the MR pin  t <sub>MRE</sub> <sup>(1)</sup> Delay from MR enable to V1GDO HIGH  t <sub>RESET_E</sub> <sup>(3)</sup> Delay from ViGDO to RESET valid LOW  t <sub>DPOR</sub> <sup>(3)</sup> Internal Device Delay on power up 45 50 55 ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                     |                                   |      | 0.90 |      |      |                       |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $V_{REF4}$                          |                                   |      |      |      | V    |                       |

| $t_{MR}^{(3)}$ Minimum time high for reset valid on the MR pin 5 μs $t_{MRE}^{(1)}$ Delay from MR enable to $\overline{V1GDO}$ HIGH 1.0 1.6 μs $t_{RESET\_E}^{(3)}$ Delay from $\overline{ViGDO}$ to $\overline{RESET}$ valid LOW 1 μs $t_{DPOR}^{(3)}$ Internal Device Delay on power up 45 50 55 ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                     | All Devices                       | 0.85 | 0.90 | 0.95 |      |                       |

| on the MR pin $t_{MRE}^{(1)}  \begin{array}{c} \text{Delay from MR enable to} \\ \hline v_{1}GDO \text{ HIGH} \end{array} \qquad \begin{array}{c} 1.0 \\ \hline \end{array} \qquad \begin{array}{c} 1.6 \\ \hline \end{array} \qquad \begin{array}{c} \mu_{S} \\ \hline \end{array}$ $t_{RESET\_E}^{(3)}  \begin{array}{c} \text{Delay from ViGDO to RESET valid} \\ LOW \\ \hline \end{array} \qquad \begin{array}{c} 1 \\ \hline \end{array} \qquad \begin{array}{c} \mu_{S} \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | AC Charac                           | teristics                         |      |      |      |      |                       |

| On the MR pin   Delay from MR enable to   1.0   1.6   μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | t <sub>MR</sub> <sup>(3)</sup>      | Minimum time high for reset valid | 5    |      |      | μs   |                       |

| V1GDO HIGH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                     | on the MR pin                     |      |      |      |      |                       |

| V1GDO HIGH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | t <sub>MRF</sub> <sup>(1)</sup>     | Delay from MR enable to           | 1.0  |      | 1.6  | μs   |                       |

| t <sub>DPOR</sub> <sup>(3)</sup> Internal Device Delay on power up 45 50 55 ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                     |                                   |      |      |      | '    |                       |

| t <sub>DPOR</sub> <sup>(3)</sup> Internal Device Delay on power up 45 50 55 ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | t <sub>BESET</sub> F <sup>(3)</sup> | Delay from ViGDO to RESET valid   |      |      | 1    | μs   |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                     | _                                 |      |      |      | '    |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | t <sub>DPOB</sub> (3)               | Internal Device Delay on power up | 45   | 50   | 55   | ms   |                       |

| 1111 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | t <sub>TO</sub> <sup>(3)</sup>      | ViGDO turn off time               |      | 50   |      | ns   |                       |

**Notes:**(1) This parameter is based on characterization data.

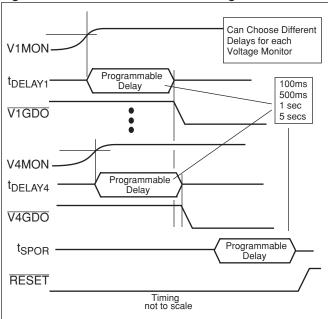

#### **ELECTRICAL CHARACTERISTICS** (Programmable Parameters)

| Symbol              | Parameter                    | Min. | Тур. | Max. | Unit | Test Conditions |

|---------------------|------------------------------|------|------|------|------|-----------------|

| t <sub>SPOR</sub>   | Delay before RESET assertion |      |      |      |      |                 |

|                     | TPOR1 = 0 $TPOR0 = 0$        | 90   | 100  | 110  | ms   | Factory Default |

|                     | TPOR1 = 0 TPOR0 = 1          | 450  | 500  | 550  | ms   | (3)             |

|                     | TPOR1 = 1 TPOR0 = 0          | 0.9  | 1    | 1.1  | S    | (3)             |

|                     | TPOR1 = 1                    | 4.5  | 5    | 5.5  | s    | (3)             |

| t <sub>DELAYi</sub> | Time Delay used in Power     |      |      |      |      |                 |

|                     | Sequencing (i = 1 to 4)      |      |      |      |      |                 |

|                     | TiD1 = 0 $TiD0 = 0$          | 90   | 100  | 110  | ms   | Factory Default |

|                     | TiD1 = 0 TiD0 = 1            | 450  | 500  | 550  | ms   | (3)             |

|                     | TiD1 = 1 $TiD0 = 0$          | 0.9  | 1    | 1.1  | s    | (3)             |

|                     | TiD1 = 1 TiD0 = 1            | 4.5  | 5    | 5.5  | S    | (3)             |

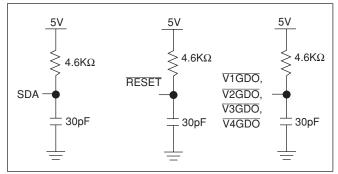

#### **EQUIVALENT A.C. OUTPUT LOAD CIRCUIT**

#### **A.C. TEST CONDITIONS**

| Input pulse levels             | V <sub>CC</sub> x 0.1 to V <sub>CC</sub> x 0.9 |

|--------------------------------|------------------------------------------------|

| Input rise and fall times      | 10ns                                           |

| Input and output timing levels | V <sub>CC</sub> x 0.5                          |

| Output load                    | Standard output load                           |

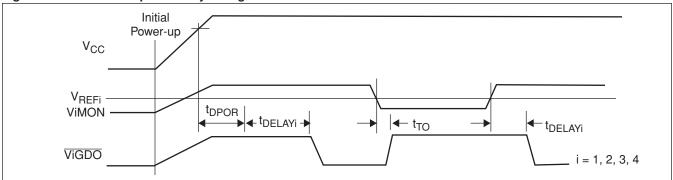

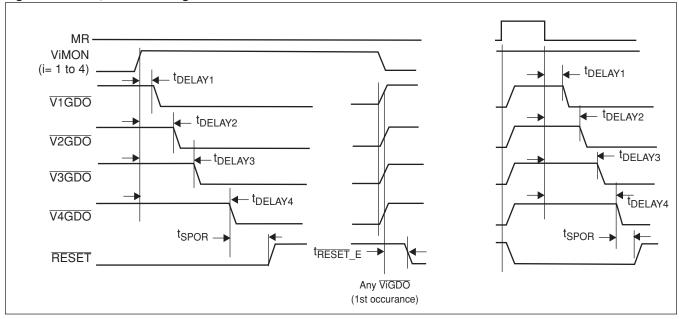

Figure 1. Initial Power up and delay timing

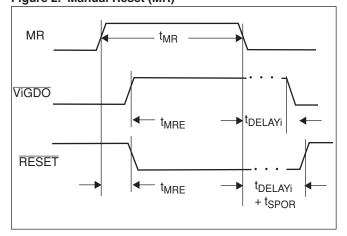

Figure 2. Manual Reset (MR)

#### **SYMBOL TABLE**

| WAVEFORM | INPUTS                            | OUTPUTS                            |

|----------|-----------------------------------|------------------------------------|

|          | Must be steady                    | Will be steady                     |

|          | May change<br>from LOW<br>to HIGH | Will change<br>from LOW<br>to HIGH |

|          | May change<br>from HIGH<br>to LOW | Will change<br>from HIGH<br>to LOW |

|          | Don't Care:<br>Changes<br>Allowed | Changing:<br>State Not<br>Known    |

Figure 3. VIGDO, RESET Timings

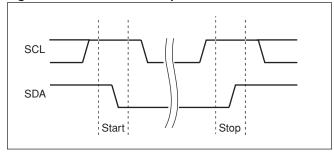

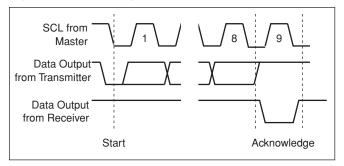

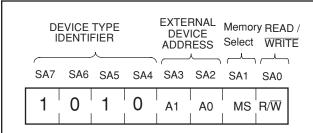

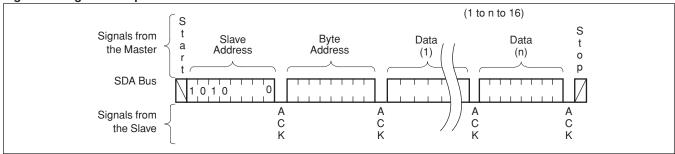

#### **SERIAL INTERFACE**

| Symbol           | Parameter                                                                            | Min.           | Тур. | Max.    | Unit | Test Conditions                                                            |  |

|------------------|--------------------------------------------------------------------------------------|----------------|------|---------|------|----------------------------------------------------------------------------|--|

| DC Charac        | DC Characteristics                                                                   |                |      |         |      |                                                                            |  |

| I <sub>CC1</sub> | Active Supply Current (V <sub>DD</sub> ) Read to Memory or registers                 |                |      | 2.5     | mA   | $V_{IL} = V_{CC} \times 0.1$<br>$V_{IH} = V_{CC} \times 0.9$ ,             |  |

| I <sub>CC2</sub> | Active Supply Current (V <sub>DD</sub> )<br>Write to Memory or registers             |                |      | 3.0     | mA   | f <sub>SCL</sub> = 400kHz                                                  |  |

| I <sub>LI</sub>  | Input Leakage Current (SCL, WP, A0, A1)                                              |                |      | 10      | μА   | $V_{IL}$ = GND to $V_{CC}$                                                 |  |

| I <sub>LO</sub>  | Output Leakage Current (SDA)                                                         |                |      | 10      | μA   | V <sub>SDA</sub> = GND to V <sub>CC</sub><br>Device is in Standby          |  |

| V <sub>IL</sub>  | Input LOW Voltage<br>(SDA, SCL, WP, A0, A1)                                          | -0.5           |      | 5 x 0.3 | V    |                                                                            |  |

| V <sub>IH</sub>  | Input HIGH Voltage<br>(SDA, SCL, WP, A0, A1)                                         | 5 x 0.7        |      | 5.5     | V    |                                                                            |  |

| V <sub>HYS</sub> | Schmidt Trigger Input Hysteresis • Fixed input level • V <sub>CC</sub> related level | 0.2<br>.05 x 5 |      |         | V    |                                                                            |  |

| V <sub>OL</sub>  | Output LOW Voltage (SDA)                                                             |                |      | 0.4     | V    | I <sub>OL</sub> = 4.0 mA (2.7-5.5V)<br>I <sub>OL</sub> = 2.0 mA (2.4-3.6V) |  |

#### **SERIAL INTERFACE** (Continued)

| Symbol                          | Parameter                                             | Min.     | Тур. | Max. | Unit | Test Conditions |  |

|---------------------------------|-------------------------------------------------------|----------|------|------|------|-----------------|--|

| AC Characteristics              |                                                       |          |      |      |      |                 |  |

| f <sub>SCL</sub>                | SCL Clock Frequency                                   |          |      | 400  | kHz  |                 |  |

| t <sub>IN</sub>                 | Pulse width Suppression Time at inputs                | 50       |      |      | ns   |                 |  |

| t <sub>AA</sub> <sup>(1)</sup>  | SCL LOW to SDA Data Out Valid                         | 0.1      |      | 1.5  | μs   |                 |  |

| t <sub>BUF</sub> <sup>(1)</sup> | Time the bus is free before start of new transmission | 1.3      |      |      | μs   |                 |  |

| t <sub>LOW</sub>                | Clock LOW Time                                        | 1.3      |      |      | μs   |                 |  |

| tHIGH                           | Clock HIGH Time                                       | 0.6      |      |      | μs   |                 |  |

| t <sub>SU:STA</sub>             | Start Condition Setup Time                            | 0.6      |      |      | μs   |                 |  |

| t <sub>HD:STA</sub>             | Start Condition Hold Time                             | 0.6      |      |      | μs   |                 |  |

| t <sub>SU:DAT</sub>             | Data In Setup Time                                    | 100      |      |      | ns   |                 |  |

| t <sub>HD:DAT</sub>             | Data In Hold Time                                     | 0        |      |      | μs   |                 |  |

| t <sub>SU:STO</sub>             | Stop Condition Setup Time                             | 0.6      |      |      | μs   |                 |  |

| t <sub>DH</sub> <sup>(1)</sup>  | Data Output Hold Time                                 | 50       |      |      | ns   |                 |  |

| t <sub>R</sub> <sup>(1)</sup>   | SDA and SCL Rise Time                                 | 20 +.1Cb |      | 300  | ns   |                 |  |

| t <sub>F</sub> <sup>(1)</sup>   | SDA and SCL Fall Time                                 | 20 +.1Cb |      | 300  | ns   |                 |  |

| t <sub>SU:WP</sub>              | WP Setup Time                                         | 0.6      |      |      | μs   |                 |  |

| t <sub>HD:WP</sub>              | WP Hold Time                                          | 0        |      |      | μs   |                 |  |

| t <sub>SU:ADR</sub>             | A0, A1 Setup Time                                     | 0.6      |      |      | μs   |                 |  |

| t <sub>HD:ADR</sub>             | A0, A1 Hold Time                                      | 0        |      |      | μs   |                 |  |

| t <sub>SU:VP</sub>              | V <sub>P</sub> Setup Time                             | 0.6      |      |      | μs   |                 |  |

| Cb <sup>(3)</sup>               | Capacitive load for each bus line                     |          |      | 400  | pF   |                 |  |

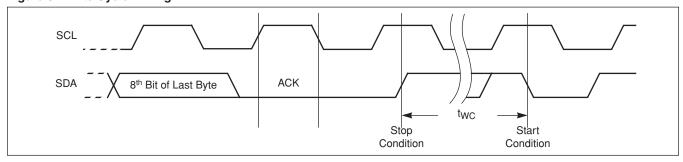

| t <sub>WC</sub> <sup>(2)</sup>  | EEPROM Write Cycle Time                               |          | 5    | 10   | ms   |                 |  |

Note: (2) t<sub>WC</sub> is the time from a valid stop condition at the end of a write sequence to the end of the self-timed internal nonvolatile write cycle. It is the minimum cycle time to be allowed for any nonvolatile write by the user, unless Acknowledge Polling is used.

<sup>(3)</sup> This parameter is not 100% tested.

#### **TIMING DIAGRAMS**

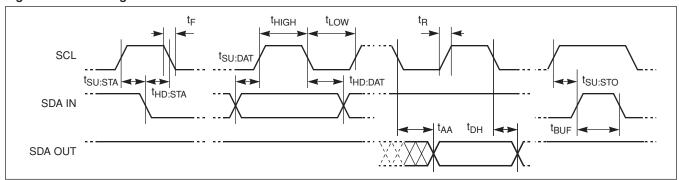

Figure 4. Bus Timing

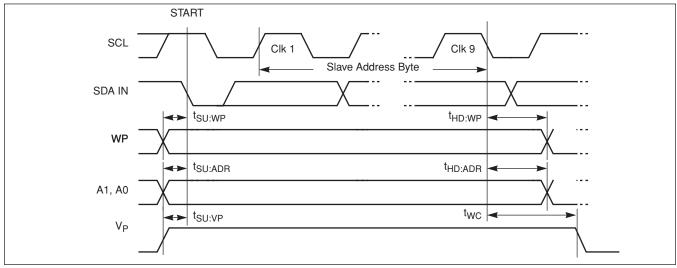

Figure 5. WP, A0, A1, V<sub>P</sub> Pin Timing

Figure 6. Write Cycle Timing

#### **PIN CONFIGURATION**

#### X80140/1/2/3/4

#### **PIN DESCRIPTIONS**

| Pin | Name           | Description                                                                                                                                                                                                                             |

|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V4GDO          | V4 Voltage Good Delay Output (Active LOW). This open drain output goes HIGH when V4MON is less than V <sub>REF4</sub> and goes LOW when V4MON is greater than V <sub>REF4</sub> . There is user selectable delay circuitry on this pin. |

| 2   | V4MON          | <b>V4 Voltage Monitor Input.</b> Fourth voltage monitor pin. If unused connect to V <sub>CC</sub> .                                                                                                                                     |

| 3   | V3GDO          | V3 Voltage Good Delay Output (Active LOW). This open drain output goes HIGH when V3MON is less than V <sub>REF3</sub> and goes LOW when V3MON is greater than V <sub>REF3</sub> . There is user selectable delay circuitry on this pin. |

| 4   | V3MON          | V3 Voltage Monitor Input. Third voltage monitor pin. If unused connect to V <sub>CC</sub> .                                                                                                                                             |

| 5   | V2GDO          | V2 Voltage Good Delay Output (Active LOW). This open drain output goes HIGH when V2MON is less than V <sub>REF2</sub> and goes LOW when V2MON is greater than V <sub>REF2</sub> . There is user selectable delay circuitry on this pin. |

| 6   | V <sub>P</sub> | EEPROM programming Voltage.                                                                                                                                                                                                             |

| 7   | V2MON          | <b>V2 Voltage Monitor Input.</b> Second voltage monitor pin. If unused connect to V <sub>CC</sub> .                                                                                                                                     |

| 8   | DNC            | Do Not Connect.                                                                                                                                                                                                                         |

| 9   | A1             | Address Select Input. It has an internal pull-down resistor. (>10M $\Omega$ typical) The A0 and A1 bits allow for up to 4 X80140 devices to be used on the same SMBus serial interface.                                                 |

| Pin | Name     | Description                                                                                                                                                                                                                                                                         |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10  | SDA      | Serial Data. SDA is a bidirectional pin used to transfer data into and out of the device. It has an open drain output and may be wire ORed with other open drain or open collector outputs. This pin requires a pull up resistor and the input buffer is always active (not gated). |

| 11  | SCL      | <b>Serial Clock.</b> The Serial Clock controls the serial bus timing for data input and output.                                                                                                                                                                                     |

| 12  | V1MON    | V1 Voltage Monitor Input. First voltage monitor pin. If unused connect to V <sub>CC</sub> .                                                                                                                                                                                         |

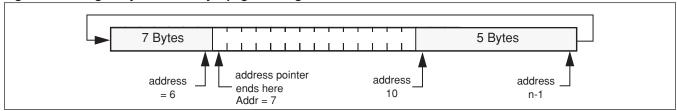

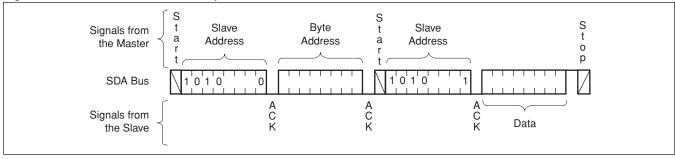

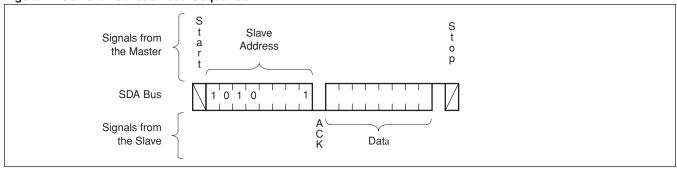

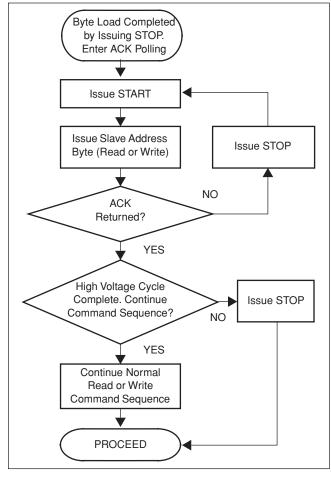

| 13  | V1GDO    | V1 Voltage Good Delay Output (Active LOW). This open drain output goes HIGH when V1MON is less than V <sub>REF1</sub> and goes LOW when V1MON is greater than V <sub>REF1</sub> . There is user selectable delay circuitry on this pin.                                             |