## Motor driver ICs

# FDD spindle motor driver BA6492BFS

The BA6492BFS is a one-chip IC designed for driving FDD spindle motors. This high-performance IC employs a 3-phase, full-wave soft switching drive system, and contains a digital servo, an index amplifier, two monostable multivibrator elements, and a power save circuit. The compactly packaged IC reduces the number of external components required.

ApplicationsFloppy disk drivers

#### Features

- 1) 3-phase, full-wave soft switching drive system.

- 2) Digital servo circuit.

- 3) Power save circuit.

- 4) Hall power supply switch.

- 5) Motor speed changeable.

- 6) Index amplifier. Built-in 2 monostable multivibrator.

#### •Absolute maximum ratings (Ta = $25^{\circ}$ C)

| Parameter                | Symbol | Limits   | Unit |

|--------------------------|--------|----------|------|

| Applied voltage          | Vcc    | 7.0      | V    |

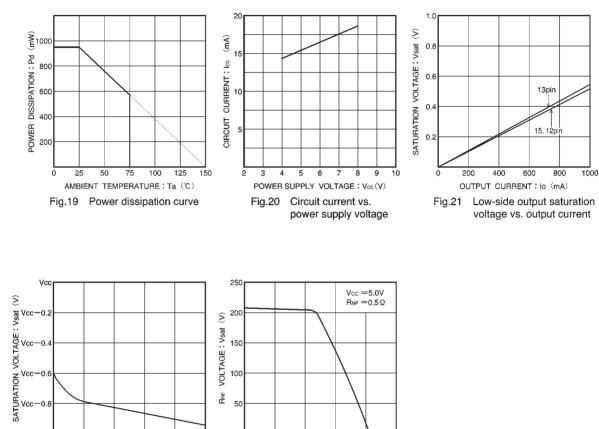

| Power dissipation        | Pd     | 950*     | mW   |

| Operating temperature    | Topr   | -25~+75  | °C   |

| Storage temperature      | Tstg   | -55~+150 | Ĉ    |

| Allowable output current | Юмах.  | 1000     | mA   |

\* Reduced by 7.6 mW for each increase in Ta of 1  $^\circ\!C$  over 25  $^\circ\!C.$

\* Mounted on a glass epoxy PCB (90 X 50 X 1.6 mm).

#### • Recommended operating conditions (Ta = $25^{\circ}$ C)

| Paramerter           | Symbol | Limits  | Unit |

|----------------------|--------|---------|------|

| Power supply voltage | Vcc    | 4.2~6.5 | V    |

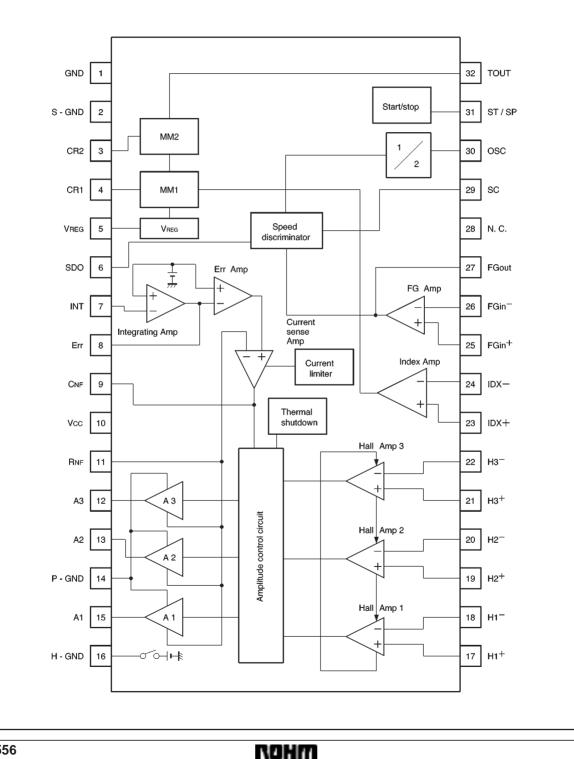

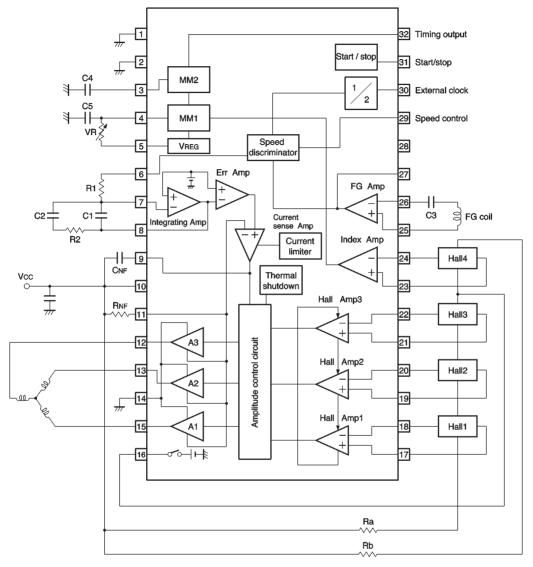

Block diagram

#### Pin descriptions

| Pin No. | Pin name          | Function                                                  |  |

|---------|-------------------|-----------------------------------------------------------|--|

| 1       | GND               | GND                                                       |  |

| 2       | S - GND           | Signal ground                                             |  |

| 3       | CR2               | Mono/multi device 2 timing setting                        |  |

| 4       | CR1               | Mono/multi device 1 timing setting                        |  |

| 5       | VREG              | Constant output voltage                                   |  |

| 6       | SDO               | Speed discriminator output                                |  |

| 7       | INT               | Integrating amplifier input (-)                           |  |

| 8       | Err               | Error amplifier input; integrating amplifier output       |  |

| 9       | CNF               | Current sensing amplifier output (for phase compensation) |  |

| 10      | Vcc               | Signal power supply                                       |  |

| 11      | RNF               | Driver power supply (current sensing pin)                 |  |

| 12      | A3                | Motor output 3                                            |  |

| 13      | A2                | Motor output 2                                            |  |

| 14      | P - GND           | Driver ground                                             |  |

| 15      | A1                | Motor output 1                                            |  |

| 16      | H - GND           | Hall device bias switch (ground)                          |  |

| 17      | H₁+               | Hall input amplifier 1 input (+)                          |  |

| 18      | H₁ <sup>_</sup>   | Hall input amplifier 1 input (-)                          |  |

| 19      | H₂ <sup>+</sup>   | Hall input amplifier 2 input (+)                          |  |

| 20      | H2 <sup>—</sup>   | Hall input amplifier 2 input (-)                          |  |

| 21      | H₃+               | Hall input amplifier 3 input (+)                          |  |

| 22      | H₃ <sup>—</sup>   | Hall input amplifier 3 input (-)                          |  |

| 23      | IDX <sup>+</sup>  | Index amplifier input (+)                                 |  |

| 24      | IDX <sup>-</sup>  | Index amplifier input (-)                                 |  |

| 25      | FGin <sup>+</sup> | FG amplifier input (+)                                    |  |

| 26      | FGin <sup>-</sup> | FG amplifier input (-)                                    |  |

| 27      | FGout             | FG amplifier output                                       |  |

| 28      | N. C.             | N. C.                                                     |  |

| 29      | SC                | Speed control                                             |  |

| 30      | OSC               | Oscillator input                                          |  |

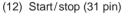

| 31      | ST / SP           | Start/stop pin                                            |  |

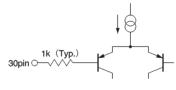

| 32      | TOUT              | Mono/multi device timing output                           |  |

#### Input/output circuits

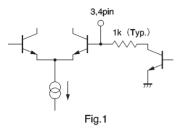

(1) Monostable multivibrator element timing setting (3, 4 pin)

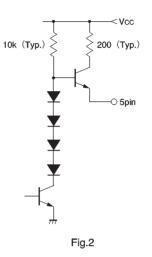

(2) Constant voltage output (5 pin)

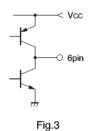

(3) Speed discriminator output (6 pin)

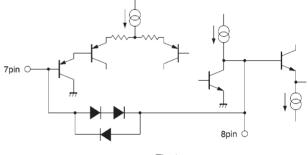

(4) Integrating amplifier (7, 8 pin)

Fig.4

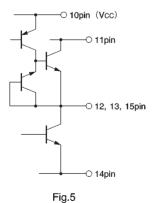

(5) Motor output  $(11 \sim 15 \text{ pin})$

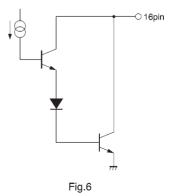

(6) Hall bias (16 pin)

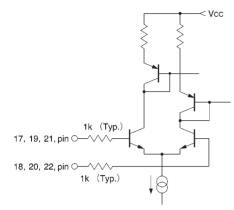

(7) Hall input (17~22 pin)

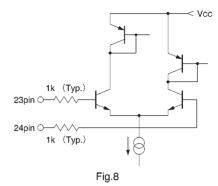

(8) Index input (23, 24 pin)

Fig.9

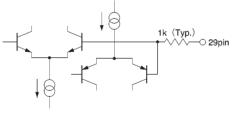

(10) Speed control (29 pin)

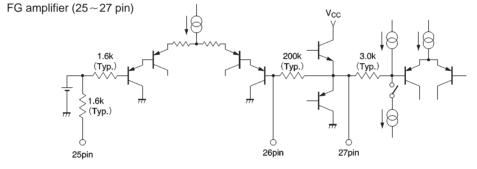

(9)

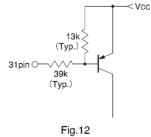

(11) External clock input (30 pin)

Fig.11

(13) Timing output (32 pin)

●Electrical characteristics (unless otherwise noted, Ta = 25°C, Vcc = 5V)

| Parameter                                      | Symbol             | Min.  | Тур. | Max. | Unit              | Conditions                                      |

|------------------------------------------------|--------------------|-------|------|------|-------------------|-------------------------------------------------|

| Supply current 1                               | lcct               | -     | 16   | 24   | mA                | Operating state                                 |

| Supply current 2                               | lcc2               | -     | -    | 3    | μA                | Standby state                                   |

| Hall in-phase input voltage range              | Vнв                | 1.5   | -    | 4.0  | V                 |                                                 |

| Hall amplifier input sensitivity               | VHin               | 60    | -    | _    | mV <sub>P-P</sub> | Differential input                              |

| Output saturation voltage 1                    | V <sub>sat1</sub>  | -     | 0.95 | 1.2  | V                 | lout= 350 mA (total of upper and lower values)  |

| Output saturation voltage 2                    | Vsat2              | -     | 1.2  | 1.6  | V                 | lout = 700 mA (total of upper and lower values) |

| Speed discriminator output high level voltage  | Vdн                | 4.7   | 4.9  | _    | V                 | Flow out 500 µ A                                |

| Speed discriminator output low level voltage   | Vdl                | -     | 0.1  | 0.25 | V                 | Flow in 500 μ A                                 |

| Integrated amplifier output high level voltage | VEinH              | 2.5   | 2.7  | 2.9  | V                 | 7pin=2.0V                                       |

| Integrated amplifier output low level voltage  | VEinL              | 1.3   | 1.5  | 1.7  | V                 | 7pin=3.0V                                       |

| FG amplifier gain                              | GFG                | 39    | 42   | 45   | dB                | f=300Hz                                         |

| Speed discriminator minimum input              | VFGmi              | 2.0   | -    | _    | mV <sub>P-P</sub> | FG amplifier input equivalent                   |

| Speed discriminator noise margin               | VFGnm              |       | -    | 0.5  | mV <sub>P-P</sub> | FG amplifier input equivalent                   |

| Error amplifier reference voltage              | VEn                | 2.35  | 2.55 | 2.75 | v                 |                                                 |

| Control input gain                             | GErr               | -14.5 | -11  | -8.5 | dB                | V8 pin versus V11 pin $R_{NF} = 0.5 \Omega$     |

| Current limiter voltage                        | Vcl                | 175   | 205  | 235  | mV                | Voltage between Vcc and V11 pins<br>R⊮==0.5Ω    |

| External clock frequency                       | fcк                | _     | 1000 | 1100 | kHz               |                                                 |

| External clock input threshold voltage         | Vск                | 1.0   | -    | 2.0  | v                 |                                                 |

| Start/stop voltage, HIGH                       | Vssh               | 3.0   | -    | 5.0  | v                 | Standby state                                   |

| Start/stop voltage, LOW                        | Vssl               | 0.0   | _    | 1.5  | v                 | Operating state                                 |

| Revolving speed switch voltage, HIGH           | Vscн               | 4.0   | _    | 5.0  | V                 | Synchronized at fFG= 360 Hz                     |

| Revolving speed switch voltage, MED            | Vscм               | 2.0   | _    | 3.0  | v                 | Synchronized at fFg= 600 Hz                     |

| Revolving speed switch voltage, LOW            | VSCL               | 0.0   | _    | 1.0  | v                 | Synchronized at fFg= 300 Hz                     |

| Hall bias saturation voltage                   | Vнg                | 1.2   | 1.5  | 1.8  | v                 | Flow in 10 mA                                   |

| Index in-phase input voltage range             | VBID               | 1.5   | _    | 4.0  | v                 |                                                 |

| Index input offset voltage                     | Vosid              | -5    | 0    | +5   | mV                |                                                 |

| Index input hysteresis 1                       | Vhyidi             | 8     | 18   | 28   | mV                |                                                 |

| Index input hysteresis 2                       | Vhy <sub>ID2</sub> | -28   | -18  | -8   | mV                |                                                 |

| Regulator voltage                              | Vreg               | 2.0   | 2.3  | 2.6  | V                 |                                                 |

| MM1 timing accuracy 1                          | T1                 | 1.80  | 2.00 | 2.20 | ms                | 29pin= "L"                                      |

| MM1 timing accuracy 2                          | T2                 | 1.50  | 1.67 | 1.83 | ms                | 29pin= "H"                                      |

| MM1 timing accuracy 3                          | Т3                 | 0.90  | 1.00 | 1.10 | ms                | 29pin="M"                                       |

| MM2 timing accuracy                            | T4                 | 1.50  | 2.14 | 2.78 | ms                |                                                 |

| MM1 timing ratio 1                             | T1 / T2            | 1.15  | 1.20 | 1.25 | -                 |                                                 |

| MM1 timing ratio 2                             | T1 / T3            | 1.90  | 2.00 | 2.10 | -                 |                                                 |

| Timing output resistance                       | Roid               | 17    | 25   | 33   | kΩ                |                                                 |

| Timing LOW level output voltage                | Volid              | -     | 0.2  | 0.4  | V                 | Flow in 500 µ A                                 |

ONot designed for radiation resistance.

#### Circuit operation

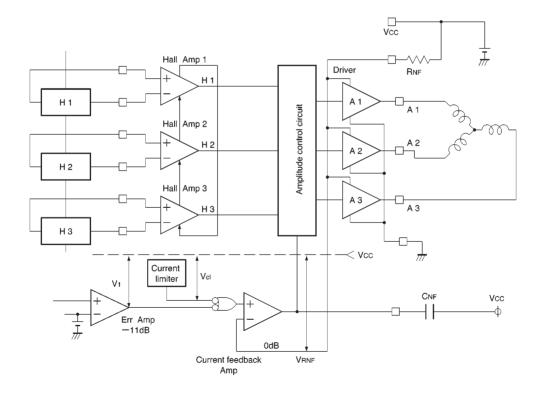

#### (1) Motor drive circuits

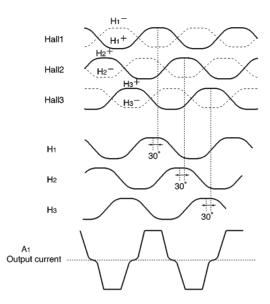

The motor driver employs a 3-phase, full-wave soft switching current drive system, in which the rotor position is sensed by Hall elements. The motor drive current is sensed by a small resistor (RNF). The total drive current is controlled and limited by sensing the voltage developed across this resistor. The motor drive circuit consists of Hall amplifiers, an amplitude control circuit, a driver, an error amplifier, and a current feedback amplifier (Fig. 14). The waveforms of different steps along the signal path from the Hall elements to the motor driver output are shown in Fig. 15. The Hall amplifiers receive the Hall elements voltage signals as differential inputs. Next, by deducting the voltage signal of Hall elements 2 from the voltage signal of Hall elements 1, current signal H1, which has a phase 30 degrees ahead of Hall elements 1. is created. Current signals H2 and H3 are created likewise. The amplitude control circuit then amplifies the H1, H2, and H3 signals according to the current feedback amplifier signal. Then, drive current signals are produced at A1, A2, and A3 by applying a constant magnification factor. Because a soft switching system is employed, the drive current has low noise and a low total current ripple. The total drive current is controlled by the error amplifier input voltage. The error amplifier has a voltage gain of about -11dB (a factor of 0.28). The current feedback amplifier regulates the total drive current, so that the error amplifier output voltage (V1) becomes equal to the VRNF voltage, which has been voltage-converted from the total drive current through the RNF pin. If V1 exceeds the current limiter voltage (Vcl), the constant voltage Vcl takes precedence, and a current limit is provided at the level of VcI/RNF.

The current feedback amplifier tends to oscillate because it receives all the feedback with a gain of 0dB. To prevent this oscillation, connect an external capacitor to the  $C_{NF}$  pin for phase compensation and for reducing the high frequency gain.

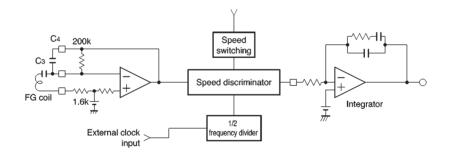

#### (2) Speed control circuit

The speed control circuit is a non-adjustable digital servo system that uses a frequency locked loop (FLL). The circuit consists of an 1/2 frequency divider, an FG amplifier, and a speed discriminator (Fig. 16).

An internal reference clock is generated from an external

clock signal input. The 1/2 frequency divider reduces the frequency of the OSC signal. The FG amplifier amplifies the minute voltage generated by the motor FG pattern and produces a rectangular-shaped speed signal. The FG amplifier gain (G<sub>FG</sub> = 42dB, typical) is determined by the internal resistance ratio.

For noise filtering, a high-pass filter is given by C3 and a resistor of 1.6k $\Omega$  (typical), and a low-pass filter is given by C4 and a resistor of 200k $\Omega$  (typical). The cutoff frequencies of high-pass and low-pass filters (f<sub>H</sub> and f<sub>L</sub>, respectively) are given by:

$$f_{H=} \ \frac{1}{2\pi \times 1.6 k\Omega \times C3} \quad f_{L=} \ \frac{1}{2\pi \times 200 k\Omega \times C4}$$

The C3 and C4 capacitances should be set so as to satisfy the following relationship:

$f_{\text{H}}\,{<}\,f_{\text{FG}}\,{<}\,f_{\text{L}}$

where  $f_{\text{FG}}$  is the FG frequency. Note that the FG amplifier inputs have a hysteresis.

The speed discriminator divides the reference clock and compares it with the reference frequency, and then outputs an error pulse according to the frequency difference. The motor rotational speed N is given by:

N=60 ·

$$\frac{f_{osc}}{n} \cdot \frac{1}{z}$$

(1)

fosc is the reference clock frequency,

n is (speed discriminator count)  $\times$  2,

z is the FG tooth number.

The discriminator count depends on the speed control pin voltage.

| Speed control pin | Count |

|-------------------|-------|

| Н                 | 1388  |

| М                 | 834   |

| L                 | 1666  |

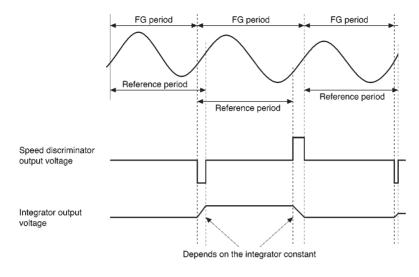

The integrator flattens out the error pulse of the speed discriminator and creates a control signal for the motor drive circuit (Fig. 17).

#### (3) Index signal circuit

The index signal circuit receives and amplifies differential inputs of Hall device signals. The Hall inputs have a hysteresis. The monostable multivibrator devices create a delay time from the zero-cross point, and outputs a pulse after the delay time. The delay time and the pulse width can be set arbitrarily with the time constant of the external CR. The following equations are given for the delay times T1, T2, and T3 for the speed control pin voltage levels of LOW, HIGH, and MEDIUM, respectively:

T1 $\doteq$ 1.35 × C5 × VR [sec] (Typ.) T2 $\doteq$ 1.13 × C5 × VR [sec] (Typ.) T3 $\doteq$ 0.68 × C5 × VR [sec] (Typ.) T4 $\doteq$ 2.14 × 10<sup>5</sup> × C4 [sec] (Typ.) T1/T2 = 1.2 (Typ.) T1/T3 = 2.0 (Typ.)

The delay angle remains constant regardless of changes in the motor speed.

#### (4) Other circuits

The start/stop circuit puts the IC to the operational state when the control pin is LOW, and to the standby state (circuit current is nearly zero) when the control pin is HIGH. The Hall elements bias switch, which is linked to the start/stop circuit, is turned off during the standby state, so that the Hall elements current is shut down.

The thermal shutdown circuit shuts down the IC currents when the chip junction temperature is increased to about  $175^{\circ}$ C (typical). The thermal shutdown circuit is deactivated when the temperature drops to about  $20^{\circ}$ C (typical).

Fig.14 Motor drive circuit

#### Circuit operation

Fig.15 I / O waveforms

Fig.16 Speed control circuit

Fig.17 Control signal waveforms

### Application example

#### Operation notes

(1) Thermal shutdown circuit

This circuit shuts down all the IC currents when the chip junction temperature is increased to about  $175^{\circ}C$  (typical). The circuit is deactivated when the temperature drops to about  $155^{\circ}C$  (typical).

(2) Hall elements connection

Hall elements can be connected in either series or paral-

lel. When connecting in series, care must be taken not to allow the Hall output to exceed the Hall common-mode input range.

(3) Hall input level

Switching noise may occur if the Hall input voltage  $(17 \sim 22 \text{ pin})$  is too high. Differential inputs of about 100mV (peak to peak) are recommended.

Motor driver ICs

(4) Driver ground pin (pin 14)

Pin 14, which is the motor current ground pin, is not connected to the signal ground pins (pin 1 and 2). Design a proper conductor pattern in consideration of the motor current that flows through pin 14.

## •Electrical characteristic curves

0.5

1.0

Fig.23

1.5

CONTROL INPUT VOLTAGE : V8pin

RNF voltage vs.

2.0

control input voltage

2.5

3.0

(5)

age.

External clock

For the external clock, make sure that the pin30 voltage

is always less than Vcc and more than the ground volt-

ō

Fig.22

200

400

OUTPUT CURRENT : Io ( µ A)

600

High-side output saturation

voltage vs.output current

800

1000

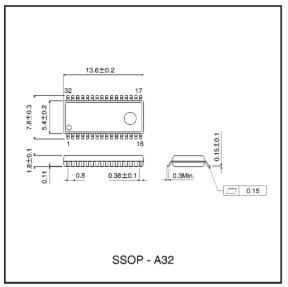

#### External dimensions (Units: mm)