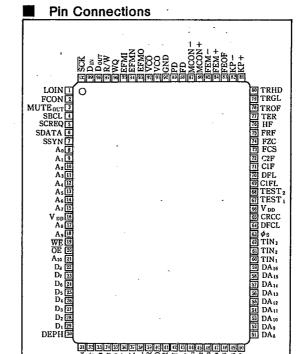

Top View

T-77-21

# LR37632

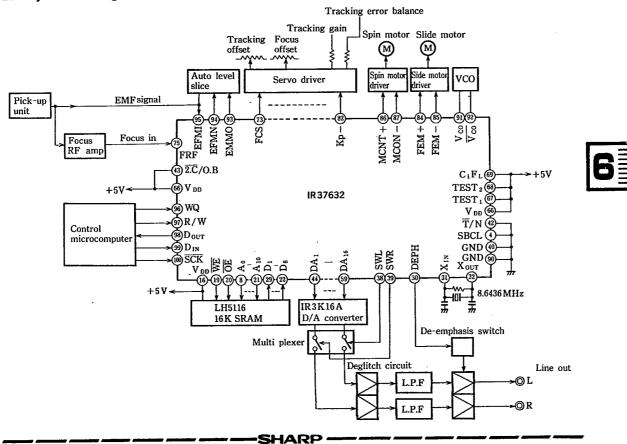

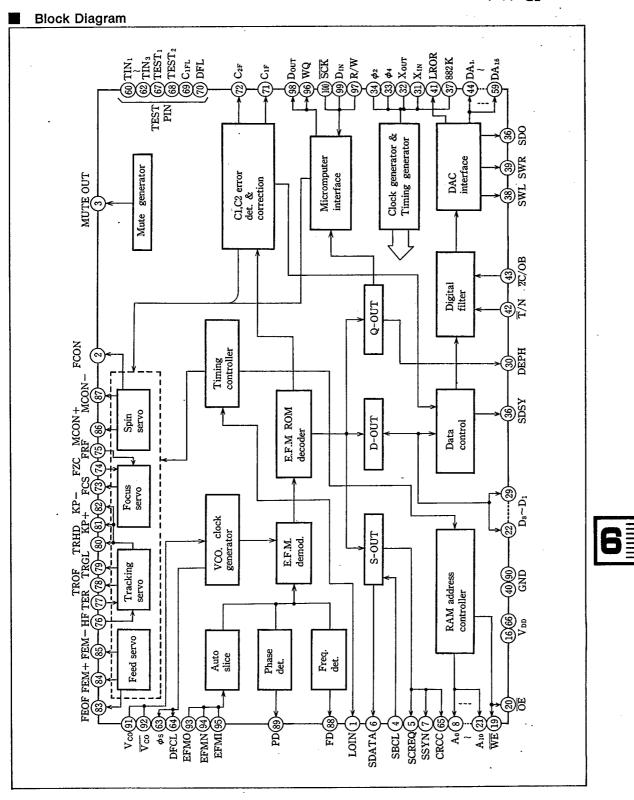

# 1-Chip Signal Processing LSI for CD

# Description

The LR37632 is a CMOS LSI for signal processing and servo control in DAD (Digital Audio Disc) system of CD (Compact Disc) unit.

This LSI provides functions of signal processing such as modulation of EFM signal being output from photoelectric pick-up, address generation of external RAM for de-interleave, detection and correction of error and digital filtering of double oversampling, and servo controls are executed with 1 chip.

# **Features**

- 1. Effective frame signal detection and protection function with a couple of synchronizing protection circuits

- 2. Automatic sequential control function which enables spin motor control by Start/Stop signal

- 3. Improvement of addressing efficiency of externally mounted RAM and realization of  $\pm 4.5$ frame jitter absorption margin

- 4. Smooth muting output without click sound

- 5. High accuracy and high-speed feed system capable of counting number of tracks

- 6. Heading function which enables designation by total time alone

- 7. 16-bit serial/parallel output

- 8. Double oversampling digital filter

- 9. Low power consumption

- 10. Single power supply: +5V

- 11. 100-pin quad flat package

LR37632

T-77-21

SHARP

LR37632

# ■ Pin Connection

| Pin<br>No. | Pin name                           | ľO  | Name                                  | Pin<br>No. | Pin name            | I/O | Name                                           |

|------------|------------------------------------|-----|---------------------------------------|------------|---------------------|-----|------------------------------------------------|

| 1          | LOIN                               | 0   | Synchronization coincidence signal    | 67-68      | TEST <sub>1-2</sub> | I   | Test pin (with pull-up resister)               |

| 2          | FCON                               | 0.  | Focus ON output                       | 69         | C <sub>1FL</sub>    | 0   | Test pin                                       |

| 3          | MUTEOUT                            | 0   | Mute output                           | 70         | $D_{FL}$            | 0   | Test pin                                       |

| 4          | SBCL                               | I   | Subcode clock input                   | 71         | C <sub>1F</sub>     | 0   | C <sub>1</sub> correction error monitor output |

| 5          | SCREQ                              | 0   | Subcode request output                | 72         | C <sub>2F</sub>     | 0   | C <sub>2</sub> correction error monitor output |

| 6          | SDATA                              | 0   | Subcode data output                   | 73         | FCS                 | 0   | Focus start output                             |

| 7          | SSYN                               | 0   | Subcode synchronizing signal          | 74         | FZC                 | I   | Focus zero cross point input                   |

| 8-15       | A <sub>0</sub> -A <sub>7</sub>     | 0   | Address output for external RAM       | 75         | FRF                 | I   | Disc reflection signal input                   |

| 16         | $V_{DD}$                           | +   | Power supply                          | 76         | HF                  | I   | HF envelope signal input                       |

| 17-18      | A <sub>8</sub> -A <sub>9</sub>     | 0   | Address output for external RAM       | 77         | TER                 | I   | Tracking error signal input                    |

| 19         | WE                                 | 0   | Write enable signal for external RAM  | 78         | TROF                | 0   | Tracking off signal output                     |

| 20         | ŌĒ                                 | 0   | Output enable signal for external RAM | 79         | TRGL                | 0   | Tracking gain signal output                    |

| 21         | A <sub>10</sub>                    | 0   | Address output for external RAM       | 80         | TRHD                | 0   | Tracking hold signal output                    |

| 22-29      | D <sub>8</sub> -D <sub>1</sub>     | I/O | Data input/output for external RAM    | 81         | KP+                 | 0   | Positive direction kick pulse output           |

| 30         | DEPH                               | 0   | De-emphasis control signal            | 82         | KP-                 | 0   | Negative direction kick pulse output           |

| 31         | X <sub>IN</sub>                    | I   | Crystal input                         | 83         | FEOF                | 0   | Feed off signal output                         |

| 32         | X <sub>out</sub>                   | 0   | Crystal output                        | 84         | FEM+                | 0   | Positive direction feed signal output          |

| 33         | <b>\$</b> 4                        | 0   | 4.3218 MHz output                     | 85         | FEM-                | 0   | Negative direction feed signal output          |

| 34         | <b>\$</b> 2                        | 0   | 2.1609 MHz output                     | 86         | MCON+               | 0   | Positive direction spin motor output           |

| 35         | SDO                                | 0   | Music data serial output              | 87         | MCON-               | 0   | Negative direction spin motor output           |

| 36         | SDSY                               | 0   | DAC control signal                    | 88         | FD                  | 0   | Frequency comparison output                    |

| 37         | 882K                               | 0   | DAC control signal                    | 89         | PD                  | 0   | Phase comparison output                        |

| 38         | SWL                                | 0   | Deglitch signal                       | 90         | GND                 | -   | GND                                            |

| 39         | SWR                                | 0   | Deglitch signal                       | 91         | VCO                 | I   | VCO input                                      |

| 40         | GND                                | _   | GND                                   | 92         | VCO                 | 0   | VCO output                                     |

| 41         | LROR                               | 0   | Data latch signal for DAC             | 93         | EFMO                | 0   | EFM signal automatic level slice               |

| 42         | T/N                                | I   | True/Double sampling switch input     | 94         | FEMN                | I/O | EFM signal automatic level slice               |

| 43         | 2.C/O.B                            | I   | Music data output format switch input | 95         | EFMI                | I   | EFM signal automatic level slice               |

| 44-59      | DA <sub>1</sub> -DA <sub>16</sub>  | 0   | Music data parallel output            | 96         | WQ                  | 0   | Q code write request output                    |

| 60-62      | TIN <sub>1</sub> -TIN <sub>3</sub> | 0   | Test pin                              | 97         | R/W                 | I   | Q code read/write selection in-<br>put         |

| 63         | φs                                 | 0   | VCO system clock output               | 98         | D <sub>OUT</sub>    | 0   | Q code data output                             |

| 64         | DFCL                               | 0   | VCO system frame synchronizing signal | 99         | D <sub>IN</sub>     | I   | Command input                                  |

| 65         | CRSS                               | 0   | CRSS error detection result signal    | 100        | SCK                 | I   | D <sub>OUT</sub> ·D <sub>IN</sub> clock input  |

| 66         | $V_{DD}$                           | _   | Power supply                          |            |                     |     |                                                |

# **Absolute Maximum Ratings**

| Parameter           | Symbol           | Ratings                  | Unit |

|---------------------|------------------|--------------------------|------|

| Supply voltage      | V <sub>DD</sub>  | -0.3  to  +7.0           | V    |

| Input voltage       | V <sub>IN</sub>  | $-0.3$ to $V_{DD} + 0.3$ | V    |

| Output voltage      | V <sub>OUT</sub> | $-0.3$ to $V_{DD} + 0.3$ | V    |

| Storage temperature | T <sub>stg</sub> | -55 to +150              | ဗ    |

# **Recommended Operating Conditions**

| Parameter             | Symbol            | MIN. | TYP.   | MAX. | Unit |

|-----------------------|-------------------|------|--------|------|------|

| Supply voltage        | $V_{\mathrm{DD}}$ | 4.   | 5.0    | 5.5  | V    |

| Operating temperature | Topr              | -10  |        | 70   | c    |

| Oscillation frequency | fosc              |      | 8.6436 |      | MHz  |

#### **DC** Characteristics

$(V_{DD}=5.0V\pm10\%, Ta=25\%)$

| Parameter                 | Symbol          | Conditions                      | MIN.               | TYP. | MAX.        | Unit | Note |

|---------------------------|-----------------|---------------------------------|--------------------|------|-------------|------|------|

| Operating current         | I <sub>op</sub> |                                 |                    | 25   | 50          | mA   | 1    |

|                           | V <sub>IH</sub> |                                 | $0.7V_{DD}$        |      | $V_{DD}$    | v    |      |

| Input voltage             | VIL             |                                 | GND                |      | $0.3V_{DD}$ | ٧    |      |

| 0                         | V <sub>OH</sub> | I <sub>OH</sub> =1 mA           | $V_{\rm DD} - 0.5$ |      |             | v    | 1    |

| Output voltage            | V <sub>OL</sub> | $I_{OL} = -1 \text{ mA}$        |                    |      | 0.5         |      |      |

| Input leakage current (1) | I <sub>L</sub>  | V <sub>I</sub> ="High" or "Low" |                    |      | 1.0         | μA   | 2    |

|                           | I <sub>LH</sub> | V <sub>I</sub> ="High"          |                    |      | 1.0         | Λ    | 3    |

| Input leakage current (2) | I <sub>LL</sub> | V <sub>I</sub> ="Low"           |                    | 60   | 120         | μA   |      |

Note 1: Circuits as shown below are connected to VCO system pins and EFM system pins.

CMOS 2K byte SRAM is connected to RAM pin. Measurement is taken when in crystal oscillation.

Output pins other than the above, TEST<sub>1</sub> and TEST<sub>2</sub> pins are in open state, and input pins other than the above are in "Low" state during measurement.

Note 2: Applied to input pins other than  $TEST_1$  and  $TEST_2$  pins. Note 3: Applied to  $TEST_1$  and  $TEST_2$  pins.

# **Test Circuit**

#### AC Characteristics

$(V_{DD}=5.0V\pm10\%, Ta=25\%)$

| Parameter                            | Symbol                          | Conditions           | MIN. | TYP. | MAX.     | Unit | Note  |

|--------------------------------------|---------------------------------|----------------------|------|------|----------|------|-------|

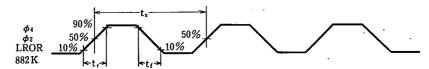

| VCO                                  | t <sub>r</sub> , t <sub>f</sub> | $C_L = 50pF$         |      | 25   | 50       | ns   |       |

| ,                                    | t <sub>r</sub> , t <sub>f</sub> | C =20nE              |      |      | 35       | ns   |       |

| \$ 4                                 | t <sub>x</sub>                  | $C_L=20pF$           |      | 231  |          | 113  |       |

| ,                                    | t <sub>r</sub> , t <sub>f</sub> | C 20nE               |      |      | 35       | ns   |       |

| <b>\$</b> 2                          | t <sub>x</sub>                  | $C_L=20pF$           |      | 463  |          | 113  |       |

| LDOD                                 | t <sub>r</sub> , t <sub>f</sub> | $C_L=20pF$           |      |      | 35       | ns   |       |

| LROR                                 | t <sub>x</sub>                  | C <sub>L</sub> -zopr |      | 5.8  |          | μs   |       |

| oge.                                 | t <sub>r</sub> , t <sub>f</sub> | C 20nE               | ļ    |      | 35       | ns   | _     |

| 882K                                 | t <sub>x</sub>                  | C <sub>L</sub> =20pF |      | 11.3 |          | μs   |       |

| Output pins other than above         | t <sub>r</sub> , t <sub>f</sub> | $C_L=20pF$           |      | 75   | 150      | ns   |       |

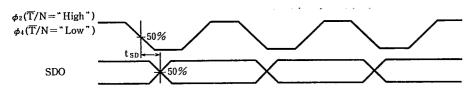

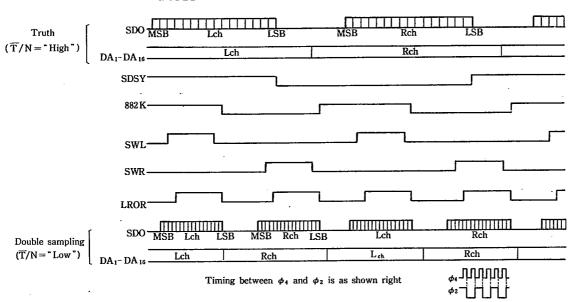

| φ <sub>4</sub> , φ <sub>2</sub> -SDO | t <sub>SD</sub>                 | $C_L = 20pF$         |      | 20   | 60       | ns   | 1     |

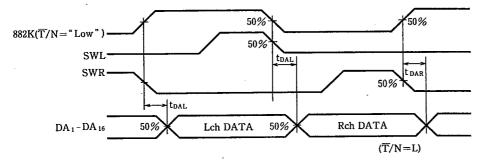

|                                      | t <sub>DAL</sub>                | $C_L = 20 pF$        | 250  |      |          | ns   | ·   2 |

| Parallel output timing               | t <sub>DAR</sub>                | C <sub>L</sub> =20pr | 250  |      |          |      |       |

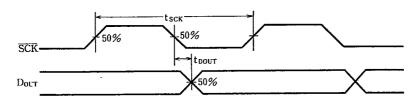

| 0 1                                  | t <sub>DOUT</sub>               | $C_L=20pF$           |      | 25   | 60       | ns   |       |

| Q code output timing                 | t <sub>SCK</sub>                |                      | 1    |      |          | μs   |       |

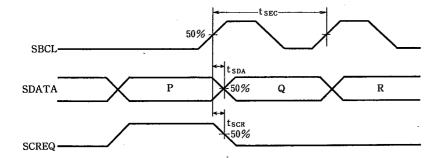

|                                      | t <sub>SEC</sub>                |                      | 1    |      | <u> </u> | μs   |       |

| Subcode output timing                | t <sub>SDA</sub>                | $C_L=20pF$           |      | 25   | 60       | 70   |       |

| • -                                  | t <sub>SCR</sub>                |                      |      | 20   |          | ns   | _     |

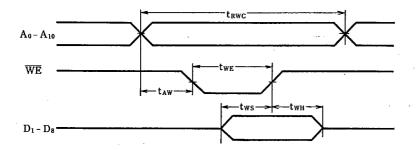

|                                      | t <sub>RWC</sub>                |                      |      | 231  | -        |      |       |

|                                      | t <sub>AW</sub>                 |                      |      | 58 ' |          | ]    |       |

| Write cycle timing                   | twe                             | $C_L = 30 \text{pF}$ |      | 126  |          | ns   |       |

| •                                    | tws                             | 1                    | 10   |      |          |      |       |

|                                      | t <sub>wH</sub>                 | 1                    | 10   |      |          |      |       |

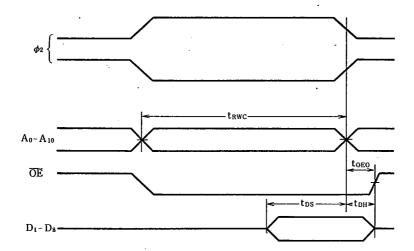

|                                      | t <sub>RWC</sub>                |                      |      | 231  |          | ]    |       |

| B 1 1 2 2 2                          | t <sub>DS</sub>                 |                      | 30   |      |          |      | 1     |

| Read cycle timing                    | t <sub>DH</sub>                 | $C_L = 50 pF$        | 0    |      |          | ns   |       |

|                                      | toEO                            | 1                    |      | 57.8 |          |      |       |

Note 1:  $\phi_4$  when  $\overline{T}/N =$  "Low",  $\phi_2$  when  $\overline{T}/N =$  "High"

Note 2:  $\phi_4$  when  $\overline{T}/N = \text{``Low''}$

# Functional Description

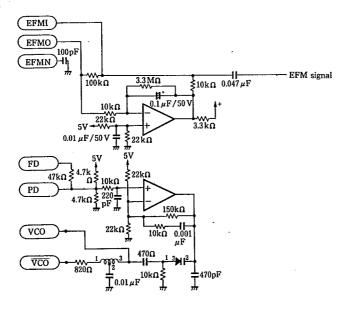

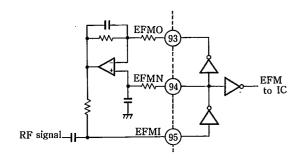

#### (1) Slice level control

Three pins of EFMI (input), EFMN (input/output) and EFMO (output) are provided to control the level slice of RF signal coming from the laser pick-up. Automatic level slice is realized with the following configuration.

# (2) Clock regeneration

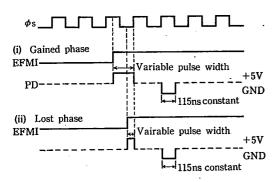

PD is the output from phase comparator. When PD output is HZ (high impedance), it has the following output format with respect to EFMI and  $\phi_S$  (4.3218 MHz standard). It becomes HZ for others.

When EFMI input signal is reversed, its phase is compared with  $\phi_S$  at the reversed point of change. The result is output from PD pin as the change in pulse width of "High" level. This is converted into DC level and input into VCO circuit. Thus clock  $\phi_S$  phase synchronized with EFM signal is generated.

By connecting LC resonance circuit between VCO and  $\overline{\text{VCO}}$ , clock oscillation (standard 8.6436 MHz) is carried out. It is possible to make a PLL system together with PD. This clock oscillation generates  $\phi_S$  by means of internal divider (1/2).

The FD pin is an output pin to synchronize PLL of VCO system much faster at spin motor rough servo.

# (3) Synchronization coincidence signal, system clock output and frame synchronizing signal output

The LOIN pin is used to output the coincidence of self-running synchronizing signal (by internal counter) with frame synchronizing signal. This will not be

Oscillation freq.

Typ. 8.6436 MHz

VCO

92

VCO

91

VDD

VDD

PD

89

FD

88

BIT CLOCK

Internal signal

DFCL

SBCL

output when synchronizing signal is missing or startstop is deviated.

This signal is continued for one frame length.

| LOIN | Content               |

|------|-----------------------|

| 1    | Synchronizing period  |

| 0    | Asynchronizing period |

$\phi_S$  is the output of VCO system clock standard (4.3218MHz).

DFCL is the output pin of VCO system synchronizing signal standard (7.35kHz; duty 50-50).

#### (4) Transmission of subcode

Pins related to subcode are provided for future expansion of the system.

When subcode synchronizing signals  $S_0$  or  $S_1$  is detected, "High" signal is output from SSYN pin at the point of  $S_1$  for one frame length.

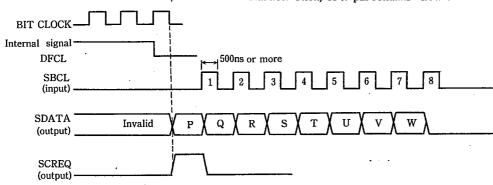

When all subcodes are taken into internal register of SDATA, SCREQ pin output becomes "High". When clock  $S_{BCL}$  is given from the system microcomputer after receiving this, subcodes P through W can be taken out from SDATA pin with bit serial manner. When any subcode is taken from SDATA pin, SCREQ becomes "Low". The timing chart at this instance is shown below.

Q code stated here has not completed CRC checking.

#### (5) Transmission of Q code

Q subcode of those obtained from the disc is processed by Q subcode processing circuit and CRCC circuit. When a correct Q code is obtained, it is stored in the buffer register and at the same time, "High" signal is output from WQ pin.

When the system microcomputer detects that WQ signal becomes "High", clock is input to  $\overline{SCK}$  pin and the data synchronized with that clock can be output from  $D_{OUT}$  pin with the following format in serial manner. Then, R/W pin remains "Low".

-SHARP

Subcode transmission timing

Result of CRCC error detection is output from CRCC pin. When no error is detected, "Low" level signal is output. If an error is detected, "High" level signal is output.

Content of Dour output

| 1<br>2 | Internal<br>CONT | STATE        | Internal STATE is shown below<br>CONT(4)00 * 0 2ch<br>10 * 0 4ch  emphasis |

|--------|------------------|--------------|----------------------------------------------------------------------------|

| 3      | Track            | number       | 00 * 1 2ch                                                                 |

| 4      | Inc              | lex          | 01 * 0 Date                                                                |

| 5      | M                | IN.          | Track                                                                      |

| 6      | SEC.             |              | Time from the start                                                        |

| 7      | FRA              | ME           | ] ) 57                                                                     |

| 8      | ALI              | <b>_</b> "0" | <b>] )</b>                                                                 |

| 9      | AM               | IN.          | Total time from the                                                        |

| 10     | ASI              | EC.          | start of DISK                                                              |

| 11     | AFR              | AMC.         | ]                                                                          |

Content of internal state of DOUT output

| SIGN | S <sub>2</sub> | Sı | 8F | 4F | MZ | FCO | NQ |    |

|------|----------------|----|----|----|----|-----|----|----|

| MSB  |                |    |    |    |    |     | L  | SB |

SIGN: Search polarity

S2, S1: Search mode

8F, 4F: Frame error

MZ: Disk motor stop

FCo: Focus out

NQ: Q code detection

WQ signal becomes "High" when MZ and FCO flags are changed or when NQ code is set.

As long as LSB (NQ) of the first one byte is being set when Q code is read out, subsequent 80 bits are read out continuously.

#### (6) Real time set

The head position in automatic search mode is controlled by "A" time (total time) instead of the time for every music.

As for this total time, "A" time data at Q code reading is stored into internal register. It is therefore necessary to read out all Q code data prior to SEARCH command execution and to renew real time in the internal register.

# (7) Receiving of commands

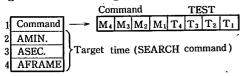

When a command is written from system control microcomputer, "High" signal is applied to R/W pin and serial 8-bit data is written to DIN pin synchronizing with the clock being entered into SCK pin.

⟨List of M₄ through M₁ commonds⟩

| Content of command | M <sub>4</sub> | $M_3$ | $M_2$ | M <sub>1</sub> |

|--------------------|----------------|-------|-------|----------------|

| STOP               | 0              | 0     | 0     | 0              |

| SIOP               | 0              | 0 -   | 0     | 1_             |

| FEED FOR.          | 0              | 0     | 1     | 0              |

| FEED RET.          | 0              | 0     | 1     | 1              |

| EOCHE CTART        | 0              | 1     | 0     | 0              |

| FOCUS START        | 0              | 1     | 0     | 1              |

| DISC START         | 0              | 1     | 1     | 0              |

| DISC BRAKE         | 0              | 1     | 1     | 1              |

| PLAY               | 1              | 0     | 0     | 0              |

| PLAY MUTE          | 1              | 0     | 0     | 1              |

| FF                 | 1              | 0     | 1     | 0              |

| FR                 | 1.             | 0     | 1     | 1              |

| FFF                | 1              | 1     | 0     | 0              |

| FFR                | 1              | 1     | 0     | 1              |

| ODADOU             | 1              | 1     | 1     | 0              |

| SEARCH             | 1              | 1     | 1 :   | 1.             |

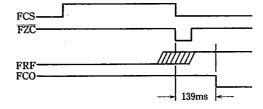

#### (8) Focus servo control

Upon receiving FOCUS START command from system microcomputer, focus servo initial pull-in signal is "High" output with from FCS pin. By generating potential in the external integration circuit to drive the focus coil, the focus moves. When focus point index signal is entered from FZC pin, pull-in by FCS is turned OFF.

When it is checked 139 ms later that FRF pin input became "High", internal state FCO (Focus OFF) flag is turned zero and write request signal WQ is output. Thus system microcomputer realizes completion of focus.

#### (9) Spin servo control

When DISC START is entered by the command from system microcomputer, spin servo control signal is output from MCON+, MCON- output pin while spin motor rotational speed is judged automatically. Upon receiving STOP command, brake is applied suddenly to the spin motor and a signal is output to stop it immediately.

Laser Light ON (H)/OFF (L) timing of a laser pick-up is output from FCON pin depending on spin servo condition.

# 1-Chip Signal Processing LSI for CD

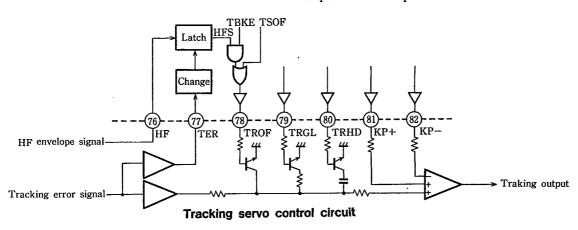

#### (10) Tracking servo control

Normally, an analog loop is created by amplifying a tracking error signal to execute tracking hold.

This circuit is not driven in normal state but actuated in manual or automatic search.

When in operation, KP+, KP- is output to execute tracking."TRHD" is output during operation to hold the tracking error signal.

"TRGL" output is used to improve the tracking gain after kick pulse is output.

Change in amplitude of "HF" signal generated by track crossing is sampled at zero cross point of tracking error signal "TER", HFS signal is created as an internal signal, "TROF" signal is output by the logic of internal circuit as shown above. Servo circuit is turned ON/OFF by this change in signal level so that the track can easily be caught.

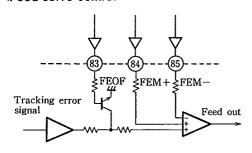

#### (11) Feed servo control

Feed servo control mode is initiated during high speed searching by FEED FOR and FEED RET .command or SEARCH command. Feed servo loop is discontinued by the signal output from FEOF pin, and field pulse signal for pick-up movement is output from FEM+ pin and FEM- pin. The pickup moves to the intended direction by this operation.

#### ⟨Feed servo control⟩

#### (12) Muting output

Signal output from MUTEOUT pin may be utilized as muting signal of PCM data output signal (16-bit music signal). MUTEOUT signal is output when frame synchronizing/asynchronizing is in the following states:

- i) Frame asynchronizing state continued for more than 6 ms.

- ii) When cumulative value exceeds 6 ms while asynchronizing time is added and synchronizing time is subtracted for the case where frame synchronization is unstable.

Muting signal is released 15 ms after frame synchronization is reset.

#### (13) Music signal output

DA<sub>1</sub>-DA<sub>16</sub> are 16-bit music signal parallel output pins, and SDO is serial output pin.

Music signal format is depending on 2C/OB and T/ N pin input state.

| Pin name | "High" or<br>"Low" | . Function                         |  |

|----------|--------------------|------------------------------------|--|

| ZC/OB    | "High"             | Offset binary output               |  |

| 2C/OB    | "Low"              | 2's complement output              |  |

| T/N      | "High"             | Pre-filtering is output (44.1kHz)  |  |

| 1/19     | "Low"              | Post-filtering is output (88.2kHz) |  |

Furthermore, signals SWR and SWL for DAC deglitching showing RIGHT signal and LEFT signal are output together with the data.

SDSY pin outputs a synchronizing signal that becomes "Low" when SDO is RIGHT signal and outputs a synchronizing signal that becomes "High" when SDO is LEFT signal. Data latch signal for DAC is output from LROR pin.

In the case music signal data that requires deemphasis operation is being output, "High" signal is output from DEPH pin.

# 1-Chip Signal Processing LSI for CD

#### (14) Error correction

A signal is output from  $C_{1F}$  pin and  $C_{2F}$  pins depending on error states at  $C_1$  correction and  $C_2$  correction.

Relation between error state and output is shown below. This is normally used with open state.

| Error state at C <sub>1</sub> correction | $C_{1F}$ |

|------------------------------------------|----------|

| 0                                        | "Low"    |

| 1                                        | "Low"    |

| More than 2                              | "High"   |

| LR error state aft | LR error state after C2 correction |        |  |  |  |

|--------------------|------------------------------------|--------|--|--|--|

| L                  | $C_{2F}$                           |        |  |  |  |

| ERROR              | ERROR                              | "Low"  |  |  |  |

| ERROR              | 0                                  | "High" |  |  |  |

| 0                  | ERROR                              | "High" |  |  |  |

| 0                  | 0                                  | "High" |  |  |  |

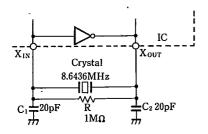

# (15) System clock oscillation circuit

$X_{\rm IN}$  and  $X_{\rm OUT}$  are crystal oscillation pins for 8.6436 (MHz).

Its external circuit is shown right. Constants shown here are for reference only.

#### (16) RAM address generation

RAM address generation circuit generates external 2K-byte RAM address and executes the following CIRC modulation using external RAM.

- 1. Jitter absorption of symbol data and one frame delay

- 2. De-interleave of symbol data is executed.

- 3. De-scramble of symbol data and two frame delay  $A_0$ - $A_{10}$ ,  $\overline{WE}$ ,  $\overline{OE}$ , and  $D_1$ - $D_8$  pins are address signal, data signal and input/output control signal to be connected to external RAM.

# (17) Test pins

$TIN_1$ - $TIN_3$ ,  $TEST_1$ ,  $TEST_2$ ,  $C_{1FL}$ ,  $D_{FL}$

All these pins are used for test.  $TEST_1$ ,  $TEST_2$  and  $C_{1FL}$  are used with "High" sate. Other pins are used with open state.

LR37632

# Timing Diagram

# (1) Clock timing

# (2) Serial bit output timing

# (3) Parallel bit output timing

# (4) Q code output timing

# (5) Subcode output timing

# (6) Write cycle timing

# (7) Read cycle timing

# \$2.25 30 35 40 45 48.0 5 10 15 20 25 \$2.25 10 10 10 15 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10

# System Configuration Example