# INTEGRATED CIRCUITS

Product data Replaces NE5517/NE5517A dated 2001 Aug 03 2002 Dec 06

# NE5517/NE5517A/ AU5517

### DESCRIPTION

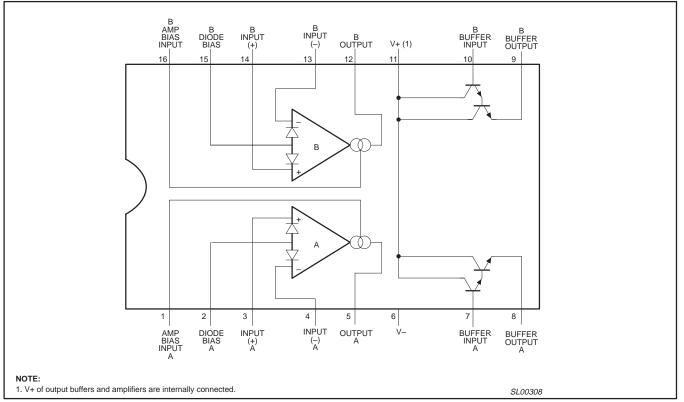

The AU5517 and NE5517 contain two current-controlled transconductance amplifiers, each with a differential input and push-pull output. The AU5517/NE5517 offers significant design and performance advantages over similar devices for all types of programmable gain applications. Circuit performance is enhanced through the use of linearizing diodes at the inputs which enable a 10 dB signal-to-noise improvement referenced to 0.5% THD. The AU5517/NE5517 is suited for a wide variety of industrial and consumer applications.

Constant impedance buffers on the chip allow general use of the AU5517/NE5517. These buffers are made of Darlington transistors and a biasing network that virtually eliminate the change of offset voltage due to a burst in the bias current  $I_{ABC}$ , hence eliminating the audible noise that could otherwise be heard in high quality audio applications.

### **FEATURES**

- Constant impedance buffers

- $\bullet$   $\Delta V_{BE}$  of buffer is constant with amplifier  $I_{BIAS}$  change

- Excellent matching between amplifiers

- Linearizing diodes

- High output signal-to-noise ratio

## APPLICATIONS

- Multiplexers

- Timers

- Electronic music synthesizers

- Dolby™ HX Systems

- Current-controlled amplifiers, filters

- Current-controlled oscillators, impedances

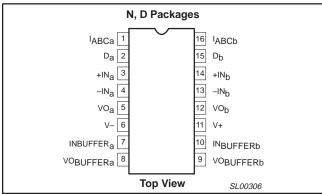

#### **PIN CONFIGURATION**

Figure 1. Pin Configuration

## **PIN DESIGNATION**

| PIN NO. | SYMBOL                | NAME AND FUNCTION      |  |  |

|---------|-----------------------|------------------------|--|--|

| 1       | I <sub>ABCa</sub>     | Amplifier bias input A |  |  |

| 2       | Da                    | Diode bias A           |  |  |

| 3       | +IN <sub>a</sub>      | Non-inverting input A  |  |  |

| 4       | –IN <sub>a</sub>      | Inverting input A      |  |  |

| 5       | V <sub>Oa</sub>       | Output A               |  |  |

| 6       | V–                    | Negative supply        |  |  |

| 7       | IN <sub>BUFFERa</sub> | Buffer input A         |  |  |

| 8       | VO <sub>BUFFERa</sub> | Buffer output A        |  |  |

| 9       | VO <sub>BUFFERb</sub> | Buffer output B        |  |  |

| 10      | IN <sub>BUFFERb</sub> | Buffer input B         |  |  |

| 11      | V+                    | Positive supply        |  |  |

| 12      | V <sub>Ob</sub>       | Output B               |  |  |

| 13      | –IN <sub>b</sub>      | Inverting input B      |  |  |

| 14      | +IN <sub>b</sub>      | Non-inverting input B  |  |  |

| 15      | D <sub>b</sub>        | Diode bias B           |  |  |

| 16      | I <sub>ABCb</sub>     | Amplifier bias input B |  |  |

### ORDERING INFORMATION

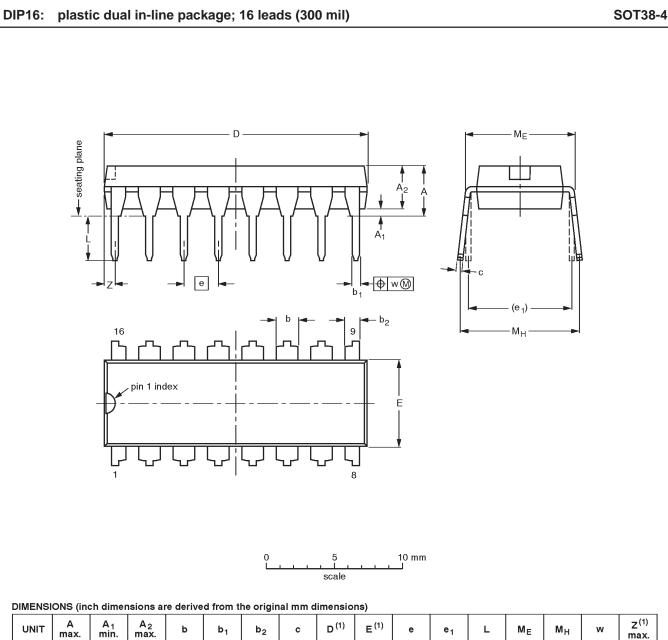

| DESCRIPTION                               | TEMPERATURE RANGE | ORDER CODE | DWG #    |

|-------------------------------------------|-------------------|------------|----------|

| 16-Pin Plastic Dual In-Line Package (DIP) | 0 to +70 °C       | NE5517N    | SOT38-4  |

| 16-Pin Plastic Dual In-Line Package (DIP) | 0 to +70 °C       | NE5517AN   | SOT38-4  |

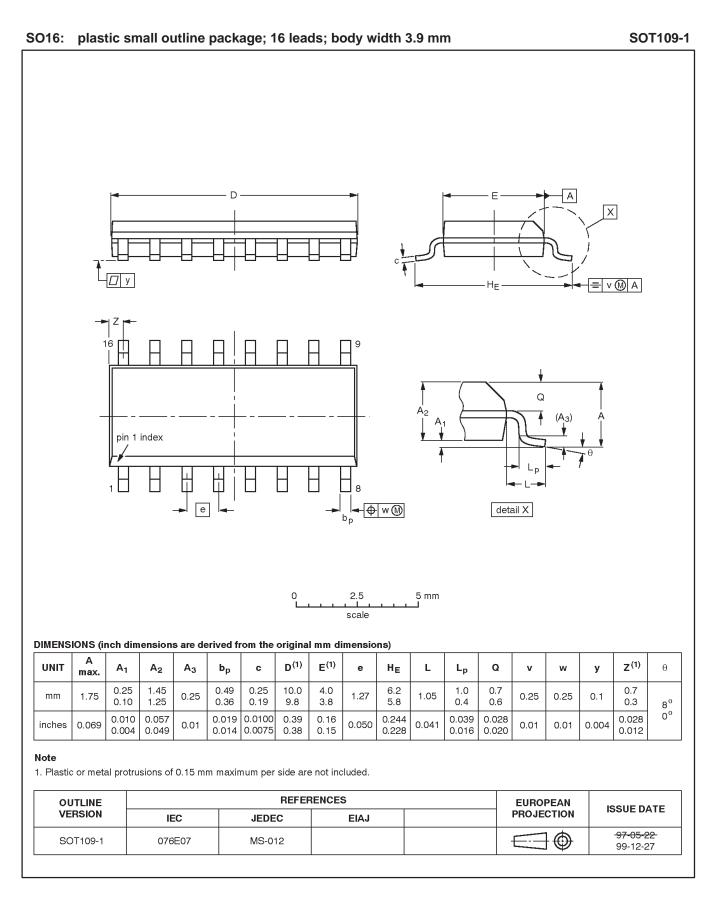

| 16-Pin Small Outline (SO) Package         | 0 to +70 °C       | NE5517D    | SOT109-1 |

| 16-Pin Small Outline (SO) Package         | –40 to +125 °C    | AU5517D    | SOT109-1 |

Dolby is a registered trademark of Dolby Laboratories Inc., San Francisco, Calif.

# NE5517/NE5517A/ AU5517

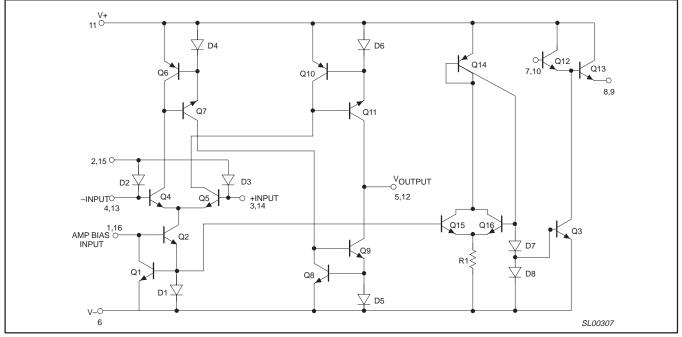

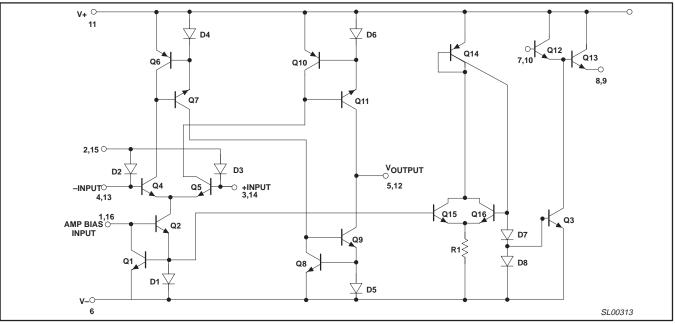

## **CIRCUIT SCHEMATIC**

Figure 2. Circuit Schematic

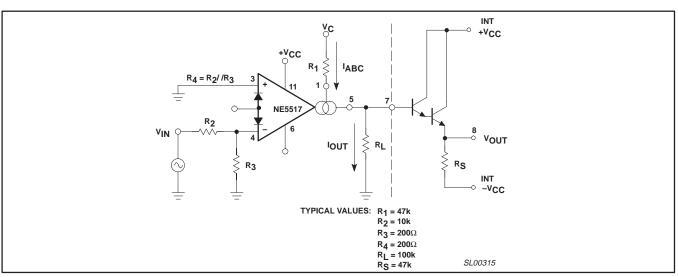

## **CONNECTION DIAGRAM**

Figure 3. Connection Diagram

# NE5517/NE5517A/ AU5517

## **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL           | PARAMETER                                                          | RATING                             | UNIT |

|------------------|--------------------------------------------------------------------|------------------------------------|------|

| V <sub>S</sub>   | Supply voltage <sup>1</sup>                                        | 44 V <sub>DC</sub> or ±22          | V    |

| P <sub>D</sub>   | Power dissipation,<br>$T_{amb} = 25 \ ^{\circ}C \ (still \ air)^2$ |                                    |      |

|                  | NE5517N, NE5517AN                                                  | 1500                               | mW   |

|                  | NE5517D, AU5517D                                                   | 1125                               | mW   |

| V <sub>IN</sub>  | Differential input voltage                                         | ±5                                 | V    |

| I <sub>D</sub>   | Diode bias current                                                 | 2                                  | mA   |

| I <sub>ABC</sub> | Amplifier bias current                                             | 2                                  | mA   |

| I <sub>SC</sub>  | Output short-circuit duration                                      | Indefinite                         | 1    |

| I <sub>OUT</sub> | Buffer output current <sup>3</sup>                                 | 20                                 | mA   |

| T <sub>amb</sub> | Operating temperature range                                        |                                    |      |

|                  | NE5517N, NE5517AN                                                  | 0 °C to +70 °C                     | °C   |

|                  | AU5517D                                                            | –40 °C to +125 °C                  | °C   |

| V <sub>DC</sub>  | DC input voltage                                                   | +V <sub>S</sub> to -V <sub>S</sub> |      |

| T <sub>stg</sub> | Storage temperature range                                          | –65 °C to +150 °C                  | °C   |

| T <sub>sld</sub> | Lead soldering temperature (10 sec max)                            | 230                                | °C   |

NOTES:

Product data

#### 2002 Dec 06

# Dual operational transconductance amplifier

## DC ELECTRICAL CHARACTERISTICS<sup>1</sup>

| SYMBOL               | DADAMETED                        |                                                                                                                  | AU   | 5517/NE5 | 517  | NE5517A |       |      | UNIT  |

|----------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------|------|----------|------|---------|-------|------|-------|

| STMBOL               | PARAMETER                        | TEST CONDITIONS                                                                                                  | Min  | Тур      | Max  | Min     | Тур   | Max  |       |

|                      |                                  |                                                                                                                  |      | 0.4      | 5    |         | 0.4   | 2    | mV    |

| V <sub>OS</sub>      | Input offset voltage             | Over temperature range                                                                                           |      |          |      |         |       | 5    | mV    |

|                      |                                  | Ι <sub>ΑΒC</sub> 5 μΑ                                                                                            |      | 0.3      | 5    |         | 0.3   | 2    | mV    |

|                      | $\Delta V_{OS} / \Delta T$       | Avg. TC of input offset voltage                                                                                  |      | 7        |      |         | 7     |      | μV/°C |

|                      | V <sub>OS</sub> including diodes | Diode bias current ( $I_D$ ) = 500 $\mu$ A                                                                       |      | 0.5      | 5    |         | 0.5   | 2    | mV    |

| V <sub>OS</sub>      | Input offset change              | $5~\mu A \leq I_{ABC} \leq 500~\mu A$                                                                            |      | 0.1      |      |         | 0.1   | 3    | mV    |

| I <sub>OS</sub>      | Input offset current             |                                                                                                                  |      | 0.1      | 0.6  |         | 0.1   | 0.6  | μΑ    |

|                      | $\Delta I_{OS} / \Delta T$       | Avg. TC of input offset current                                                                                  |      | 0.001    |      |         | 0.001 |      | μA/°C |

| lau a                | Input bias current               |                                                                                                                  |      | 0.4      | 5    |         | 0.4   | 5    | μΑ    |

| BIAS                 | Input bias current               | Over temperature range                                                                                           |      | 1        | 8    |         | 1     | 7    | μΑ    |

|                      | $\Delta I_{B} / \Delta T$        | Avg. TC of input current                                                                                         |      | 0.01     |      |         | 0.01  |      | μA/°C |

| Ям                   | Forward transconductance         |                                                                                                                  | 6700 | 9600     | 1300 | 7700    | 9600  | 1200 | μmho  |

| 9101                 |                                  | Over temperature range                                                                                           | 5400 |          |      | 4000    |       |      | μmho  |

|                      | g <sub>M</sub> tracking          |                                                                                                                  |      | 0.3      |      |         | 0.3   |      | dB    |

|                      |                                  | $R_L = 0$ , $I_{ABC} = 5 \mu A$                                                                                  |      | 5        |      | 3       | 5     | 7    | μA    |

| IOUT                 | Peak output current              | $R_L = 0$ , $I_{ABC} = 500 \mu A$                                                                                | 350  | 500      | 650  | 350     | 500   | 650  | μA    |

|                      | Deal and a site of               | $R_L = 0$                                                                                                        | 300  |          |      | 300     |       |      | μΑ    |

| \/                   | Peak output voltage<br>Positive  | R <sub>L</sub> = ∞, 5 μA ≤ I <sub>ABC</sub> ≤ 500 μA                                                             | +12  | +14.2    |      | +12     | +14.2 |      | v     |

| V <sub>OUT</sub>     | Negative                         | $R_L = \infty$ , 5 $\mu A \le I_{ABC} \le 500 \ \mu A$<br>$R_L = \infty$ , 5 $\mu A \le I_{ABC} \le 500 \ \mu A$ | -12  | -14.4    |      | -12     | -14.4 |      | v     |

| I <sub>CC</sub>      | Supply current                   | $I_{ABC} = 500 \ \mu$ A, both channels                                                                           |      | 2.6      | 4    |         | 2.6   | 4    | mA    |

|                      | V <sub>OS</sub> sensitivity      |                                                                                                                  |      |          |      |         |       |      |       |

|                      | Positive                         | $\Delta V_{OS} / \Delta V_{+}$                                                                                   |      | 20       | 150  |         | 20    | 150  | μV/V  |

|                      | Negative                         | $\Delta$ V <sub>OS</sub> / $\Delta$ V–                                                                           |      | 20       | 150  |         | 20    | 150  | μV/V  |

| CMRR                 | Common-mode rejection            |                                                                                                                  | 80   | 110      |      | 80      | 110   |      | dB    |

|                      | ration                           |                                                                                                                  |      |          |      |         |       |      |       |

|                      | Common-mode range                |                                                                                                                  | ±12  | ±13.5    |      | ±12     | ±13.5 |      | V     |

|                      | Crosstalk                        | Referred to input <sup>2</sup><br>20 Hz < f < 20 kHz                                                             |      | 100      |      |         | 100   |      | dB    |

| I <sub>IN</sub>      | Differential input current       | $I_{ABC} = 0$ , input = $\pm 4 V$                                                                                |      | 0.02     | 100  |         | 0.02  | 10   | nA    |

|                      | Leakage current                  | I <sub>ABC</sub> = 0 (Refer to test circuit)                                                                     |      | 0.2      | 100  |         | 0.2   | 5    | nA    |

| R <sub>IN</sub>      | Input resistance                 |                                                                                                                  | 10   | 26       |      | 10      | 26    |      | kΩ    |

| B <sub>W</sub>       | Open-loop bandwidth              |                                                                                                                  |      | 2        |      |         | 2     |      | MHz   |

| SR                   | Slew rate                        | Unity gain compensated                                                                                           |      | 50       |      |         | 50    |      | V/µs  |

| IN <sub>BUFFER</sub> | Buffer input current             | 5                                                                                                                |      | 0.4      | 5    |         | 0.4   | 5    | μA    |

| VO <sub>BUFFER</sub> | Peak buffer output voltage       | 5                                                                                                                | 10   | 1        |      | 10      |       |      | V     |

|                      | ∆V <sub>BE</sub> of buffer       | Refer to Buffer V <sub>BE</sub> test circuit <sup>3</sup>                                                        |      | 0.5      | 5    |         | 0.5   | 5    | mV    |

NOTES:

NOTES:

These specifications apply for V<sub>S</sub> = ±15 V, T<sub>amb</sub> = 25 °C, amplifier bias current (I<sub>ABC</sub>) = 500 μA, Pins 2 and 15 open unless otherwise specified. The inputs to the buffers are grounded and outputs are open.

These specifications apply for V<sub>S</sub> = ±15 V, I<sub>ABC</sub> = 500 μA, R<sub>OUT</sub> = 5 kΩ connected from the buffer output to -V<sub>S</sub> and the input of the buffer is connected to the transconductance amplifier output.

V<sub>S</sub> = ±15, R<sub>OUT</sub> = 5 kΩ connected from Buffer output to -V<sub>S</sub> and 5 μA ≤ I<sub>ABC</sub> ≤ 500 μA.

# NE5517/NE5517A/ AU5517

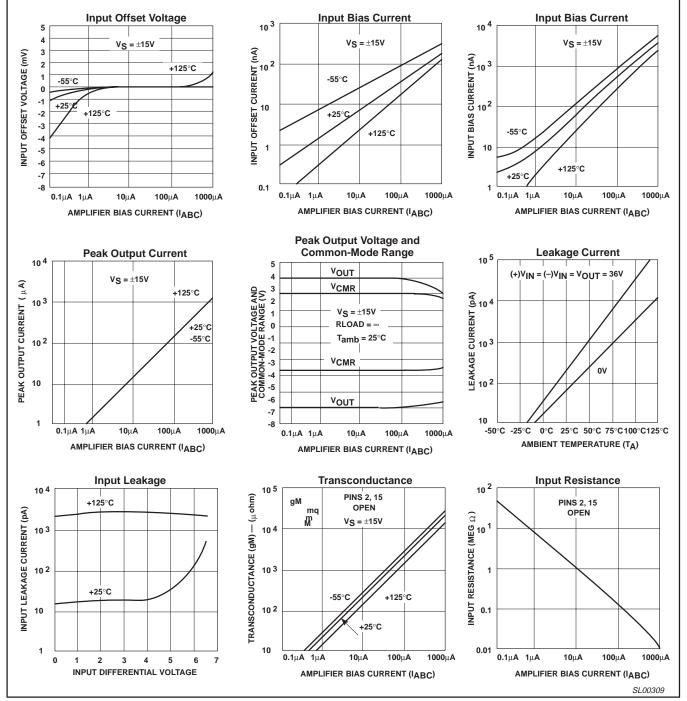

## **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 4. Typical Performance Characteristics

# NE5517/NE5517A/ AU5517

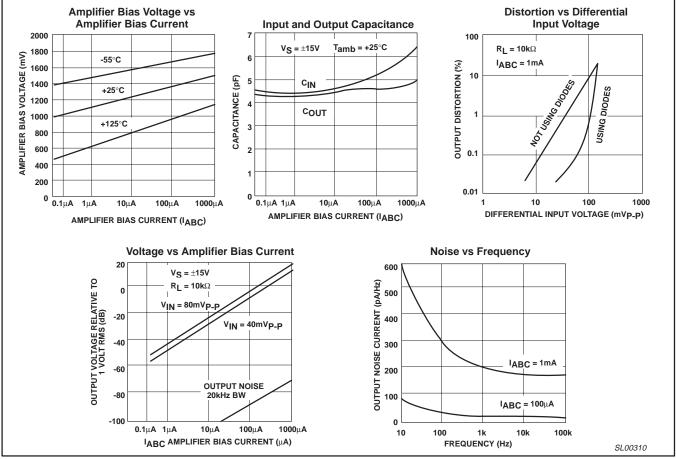

## TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

Figure 5. Typical Performance Characteristics (cont.)

## NE5517/NE5517A/ AU5517

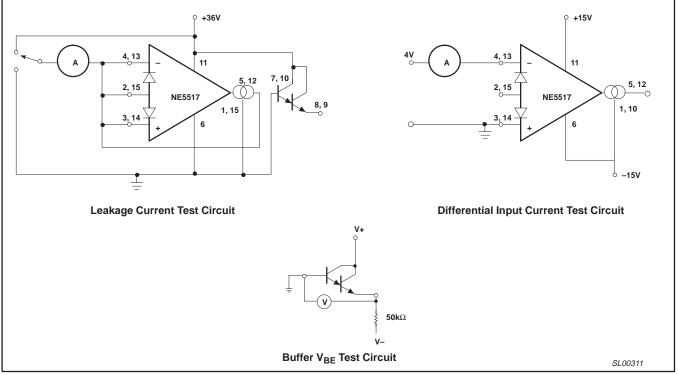

## TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

Figure 6. Typical Performance Characteristics (cont.)

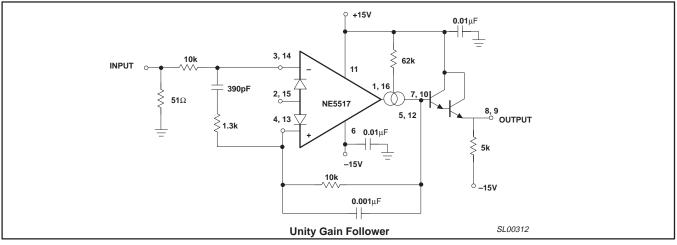

## **APPLICATIONS**

Figure 7. Applications

# NE5517/NE5517A/ AU5517

#### **CIRCUIT DESCRIPTION**

The circuit schematic diagram of one-half of the AU5517/NE5517, a dual operational transconductance amplifier with linearizing diodes and impedance buffers, is shown in Figure 8.

#### 1. Transconductance Amplifier

The transistor pair, Q<sub>4</sub> and Q<sub>5</sub>, forms a transconductance stage. The ratio of their collector currents (I<sub>4</sub> and I<sub>5</sub>, respectively) is defined by the differential input voltage, V<sub>IN</sub>, which is shown in equation 1.

$$V_{\rm IN} = \frac{\rm KT}{\rm q} \, \ln \frac{\rm l_5}{\rm l_4} \tag{1}$$

Where  $V_{IN}$  is the difference of the two input voltages

$KT \cong 26 \text{ mV}$  at room temperature (300 °k).

Transistors  $Q_1$ ,  $Q_2$  and diode  $D_1$  form a current mirror which focuses the sum of current  $I_4$  and  $I_5$  to be equal to amplifier bias current  $I_B$ :

$$I_4 + I_5 = I_B$$

(2)

If  $V_{\text{IN}}$  is small, the ratio of  $I_5$  and  $I_4$  will approach unity and the Taylor series of In function can be approximated as

$$\frac{\mathrm{KT}}{\mathrm{q}} \ln \frac{\mathrm{I}_{5}}{\mathrm{I}_{4}} \approx \frac{\mathrm{KT}}{\mathrm{q}} \frac{\mathrm{I}_{5} - \mathrm{I}_{4}}{\mathrm{I}_{4}} \tag{3}$$

and  $I_4\cong I_5\cong I_B$

$$\frac{KT}{q} \ln \frac{I_5}{I_4} \approx \frac{KT}{q} \frac{I_5 - I_4}{1/2I_B} = \frac{2KT}{q} \frac{I_5 - I_4}{I_B} = V_{IN}$$

(4)

$$I_5 - I_4 = V_{IN} \frac{(I_B^{\ q})}{2KT}$$

The remaining transistors ( $Q_6$  to  $Q_{11}$ ) and diodes ( $D_4$  to  $D_6$ ) form three current mirrors that produce an output current equal to  $I_5$  minus  $I_4$ . Thus:

$$V_{IN}\left(I_{B}\frac{q}{2KT}\right) = I_{O}$$

(5)

The term  $\frac{(I_B^{q})}{2KT}$  is then the transconductance of the amplifier and is proportional to I<sub>B</sub>.

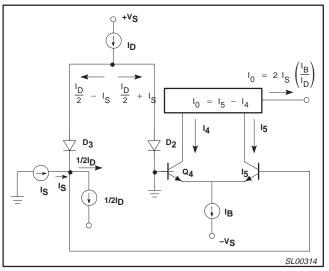

#### 2. Linearizing Diodes

For V<sub>IN</sub> greater than a few millivolts, equation 3 becomes invalid and the transconductance increases non-linearly. Figure 9 shows how the internal diodes can linearize the transfer function of the operational amplifier. Assume D<sub>2</sub> and D<sub>3</sub> are biased with current sources and the input signal current is I<sub>S</sub>. Since

$$I_4 + I_5 = I_B$$

and  $I_5 - I_4 = I_0$ , that is

$$I_4 = (I_B - I_0), I_5 = (I_B + I_0)$$

For the diodes and the input transistors that have identical geometries and are subject to similar voltages and temperatures, the following equation is true:

$$\frac{T}{q} \ln \frac{\frac{I_D}{2} + I_S}{\frac{I_D}{2} - I_S} = \frac{KT}{q} \ln \frac{1/2(I_B + I_O)}{1/2(I_B - I_O)}$$

(6)

$$I_O = I_S \frac{2^{IB}}{I_D} \text{ for } |I_S| < \frac{I_D}{2}$$

The only limitation is that the signal current should not exceed ID.

#### 3. Impedance Buffer

The upper limit of transconductance is defined by the maximum value of  $I_B$  (2 mA). The lowest value of  $I_B$  for which the amplifier will function therefore determines the overall dynamic range. At low values of  $I_B$ , a buffer with very low input bias current is desired. A Darlington amplifier with constant-current source (Q<sub>14</sub>, Q<sub>15</sub>, Q<sub>16</sub>, D<sub>7</sub>, D<sub>8</sub>, and R<sub>1</sub>) suits the need.

### **APPLICATIONS**

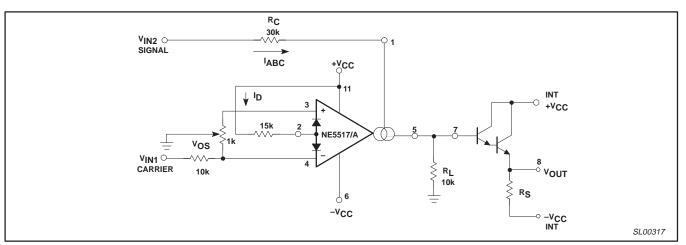

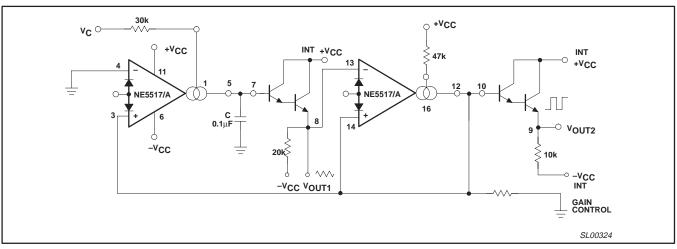

#### Voltage-Controlled Amplifier

In Figure 10, the voltage divider  $R_2$ ,  $R_3$  divides the input-voltage into small values (mV range) so the amplifier operates in a linear manner.

$$I_{OUT} = -V_{IN} \cdot \frac{R_3}{R_2 + R_3} \cdot gM;$$

$V_{OUT} = I_{OUT} \cdot R_L;$

$$A = \frac{V_{OUT}}{V_{IN}} = \frac{R_3}{R_2 + R_3} \cdot gM \cdot R_L$$

(3)  $g_M = 19.2 I_{ABC}$

$(g_M \text{ in } \mu \text{ mhos for } I_{ABC} \text{ in } mA)$

Since  $g_M$  is directly proportional to  $I_{ABC}$ , the amplification is controlled by the voltage  $V_C$  in a simple way.

When V<sub>C</sub> is taken relative to –V<sub>CC</sub> the following formula is valid:

$$I_{ABC} = \frac{(V_C - 1.2V)}{R_1}$$

The 1.2 V is the voltage across two base-emitter baths in the current mirrors. This circuit is the base for many applications of the AU5517/NE5517.

# NE5517/NE5517A/ AU5517

Figure 8. Circuit Diagram of NE5517

Figure 9. Linearizing Diode

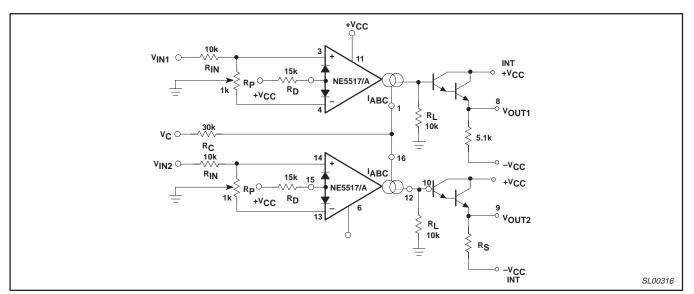

## **Stereo Amplifier With Gain Control**

Figure 11 shows a stereo amplifier with variable gain via a control input. Excellent tracking of typical 0.3 dB is easy to achieve. With the potentiometer, R<sub>P</sub> the offset can be adjusted. For AC-coupled amplifiers, the potentiometer may be replaced with two 510  $\Omega$  resistors.

### Modulators

Because the transconductance of an OTA (Operational Transconductance Amplifier) is directly proportional to  $I_{ABC}$ , the amplification of a signal can be controlled easily. The output current is the product from transconductance×input voltage. The circuit is effective up to approximately 200 kHz. Modulation of 99% is easy to achieve.

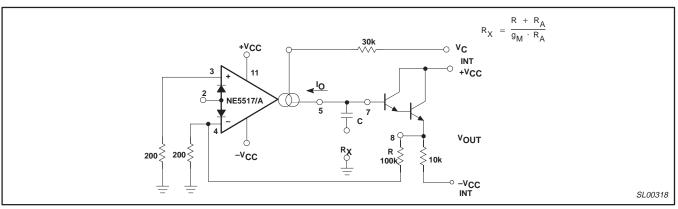

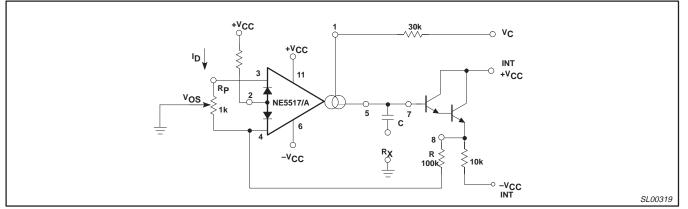

## Voltage-Controlled Resistor (VCR)

Because an OTA is capable of producing an output current proportional to the input voltage, a voltage variable resistor can be made. Figure 13 shows how this is done. A voltage presented at the  $R_X$  terminals forces a voltage at the input. This voltage is multiplied by  $g_M$  and thereby forces a current through the  $R_X$  terminals:

$$R_{X} = \frac{R + R_{A}}{gM + R_{A}}$$

where  $g_M$  is approximately 19.21  $\mu$ MHOs at room temperature. Figure 14 shows a Voltage Controlled Resistor using linearizing diodes. This improves the noise performance of the resistor.

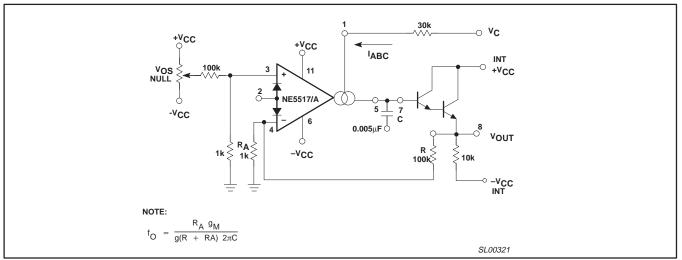

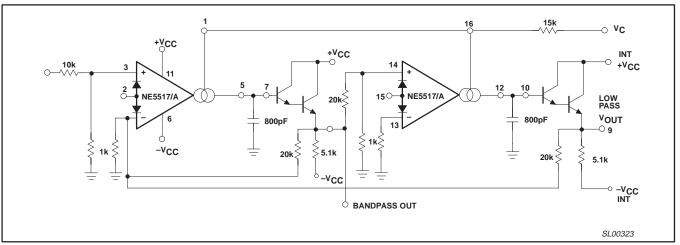

### **Voltage-Controlled Filters**

Figure 15 shows a Voltage Controlled Low-Pass Filter. The circuit is a unity gain buffer until  $X_C/g_M$  is equal to  $R/R_A$ . Then, the frequency response rolls off at a 6dB per octave with the –3 dB point being defined by the given equations. Operating in the same manner, a Voltage Controlled High-Pass Filter is shown in Figure 16. Higher order filters can be made using additional amplifiers as shown in Figures 17 and 18.

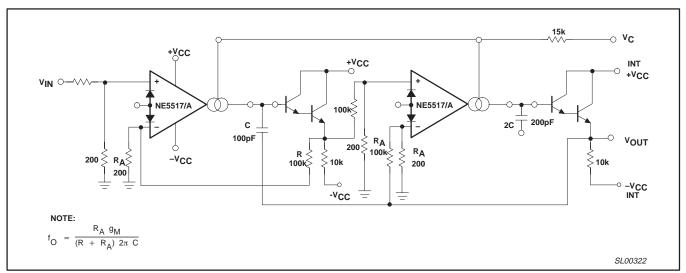

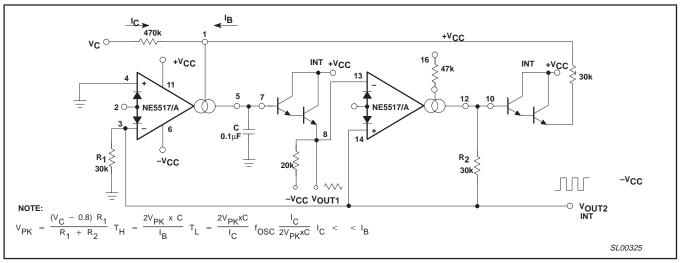

### **Voltage-Controlled Oscillators**

Figure 19 shows a voltage-controlled triangle-square wave generator. With the indicated values a range from 2 Hz to 200 kHz is possible by varying  $I_{ABC}$  from 1 mA to 10  $\mu$ A.

The output amplitude is determined by  $I_{OUT} \times R_{OUT}.$

Please notice the differential input voltage is not allowed to be above 5 V.

With a slight modification of this circuit you can get the sawtooth pulse generator, as shown in Figure 20.

# NE5517/NE5517A/ AU5517

### **APPLICATION HINTS**

To hold the transconductance  $g_M$  within the linear range,  $I_{ABC}$  should be chosen not greater than 1 mA. The current mirror ratio should be as accurate as possible over the entire current range. A current mirror with only two transistors is not recommended. A suitable current mirror can be built with a PNP transistor array which causes excellent matching and thermal coupling among the

transistors. The output current range of the DAC normally reaches from 0 to -2 mA. In this application, however, the current range is set through R<sub>REF</sub> (10 k $\Omega$ ) to 0 to -1 mA.

$$I_{DACMAX} = 2 \cdot \frac{V_{REF}}{R_{REF}} = 2 \cdot \frac{5V}{10k\Omega} = 1mA$$

Figure 11. Gain-Controlled Stereo Amplifier

Figure 12. Amplitude Modulator

Figure 13. VCR

Figure 14. VCR with Linearizing Diodes

AU5517

NE5517/NE5517A/

# Dual operational transconductance amplifier

#### 30k -0 V**C** +Vcc IABC INT 100k 0 11 +VCC 3 VIN O **2** NE5517/A 5 7 C 150pF 6 VOUT R 5 200§ RA 200 -VCC 10k ° -VCC INT + NOTE: R<sub>A</sub>g<sub>M</sub> $f_0 =$ $\overline{g(R + RA) 2\pi C}$ SL00320

Figure 15. Voltage-Controlled Low-Pass Filter

Figure 16. Voltage-Controlled High-Pass Filter

Figure 17. Butterworth Filter - 2nd Order

Figure 18. State Variable Filter

Figure 19. Triangle-Square Wave Generator (VCO)

Figure 20. Sawtooth Pulse VCO

# NE5517/NE5517A/ AU5517

0.76

0.030

| UNIT   | А<br>max. | min.  | max. | b              | b <sub>1</sub> | b <sub>2</sub> | c              | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | e <sub>1</sub> | L            | ME           | M <sub>H</sub> | w     |

|--------|-----------|-------|------|----------------|----------------|----------------|----------------|------------------|------------------|------|----------------|--------------|--------------|----------------|-------|

| mm     | 4.2       | 0.51  | 3.2  | 1.73<br>1.30   | 0.53<br>0.38   | 1.25<br>0.85   | 0.36<br>0.23   | 19.50<br>18.55   | 6.48<br>6.20     | 2.54 | 7.62           | 3.60<br>3.05 | 8.25<br>7.80 | 10.0<br>8.3    | 0.254 |

| inches | 0.17      | 0.020 | 0.13 | 0.068<br>0.051 | 0.021<br>0.015 | 0.049<br>0.033 | 0.014<br>0.009 | 0.77<br>0.73     | 0.26<br>0.24     | 0.10 | 0.30           | 0.14<br>0.12 | 0.32<br>0.31 | 0.39<br>0.33   | 0.01  |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| REFER | EUROPEAN | ISSUE DATE |            |                                  |

|-------|----------|------------|------------|----------------------------------|

| JEDEC | EIAJ     |            | PROJECTION | ISSUE DATE                       |

|       |          |            | $\bigcirc$ | <del>-92-11-17</del><br>95-01-14 |

|       | 1        | 1          |            | JEDEC EIAJ PROJECTION            |

## NE5517/NE5517A/ AU5517

## **REVISION HISTORY**

| Rev | Date     | Description                                                                                                                                                          |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _3  | 20021206 | Product data (9397 750 10796); type number AU5517 added. ECN 853–0887 29176 of 08 November 2002; supersedes Product data NE5517_NE5517A version 2 of 03 August 2001. |

|     |          | Modifications:                                                                                                                                                       |

|     |          | <ul> <li>Type number AU5517 added.</li> </ul>                                                                                                                        |

|     |          | "Description" section edited.                                                                                                                                        |

| _2  | 20010803 | Product data (9397 750 09175); NE5517/NE5517A only; ECN 853-0887 26833 of 2001 Aug 03 .                                                                              |

## NE5517/NE5517A/ AU5517

### Data sheet status

| Level | Data sheet status <sup>[1]</sup> | Product<br>status <sup>[2] [3]</sup> | Definitions                                                                                                                                                                                                                                                                                    |  |  |  |  |

|-------|----------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| I     | Objective data                   | Development                          | This data sheet contains data from the objective specification for product development.<br>Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                 |  |  |  |  |

| II    | Preliminary data                 | Qualification                        | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.             |  |  |  |  |

| 111   | Product data                     | Production                           | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). |  |  |  |  |

[1] Please consult the most recently issued data sheet before initiating or completing a design.

[2] The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

[3] For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.

#### Definitions

Short-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### Disclaimers

Life support — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes in the products—including circuits, standard cells, and/or software—described or contained herein in order to improve design and/or performance. When the product is in full production (status 'Production'), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

#### **Contact information**

For additional information please visit http://www.semiconductors.philips.com. Fax:

Fax: +31 40 27 24825

Date of release: 12-02

All rights reserved. Printed in U.S.A.

© Koninklijke Philips Electronics N.V. 2002

For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com

Document order number:

9397 750 10796

Let's make things better.