LB8107M

# **Portable CD Player Actuator Driver**

### Overview

The LB8107M is a portable CD player mechanism actuator driver. It operates on a 2.4 V power supply, which corresponds to two rechargeable Ni-Cd cells.

### **Functions and Features**

- Four H bridge driver channels on chip, one each for the four CD actuators; focus coil, tracking coil, spindle motor and sled motor

- Built-in step-up circuit to power the associated 5.0 V CD LSIs, including the DSP and microprocessor.

(The drive transistor, L, Di and C are external components: step-up circuit) Io 150 mA, maximum

- Extremely low loss drive can be achieved, since the LB8107M detects the largest signal of the four drive channels and supplies that voltage to the H bridge driver blocks in each of the four channels using PWM voltage conversion.

- (The drive PNP transistor, L, Di and C are external components: step-down circuit)

- System start and stop can be performed at the microprocessor output.

- Support for switching between step drive mode, which has a high current reduction effect, and normal V control for the sled motor drive (The other three channels all are V type drive only.)

- Built-in battery check comparator

- Built-in integrating amplifier to handle the application of digital servo control to earlier spindle motors (This function integrates the PWM output.)

- A defect function is provided. This function improves the tracking ability by setting the voltage supplied to the H bridge drivers to the maximum in the presence of disk defects during playback.

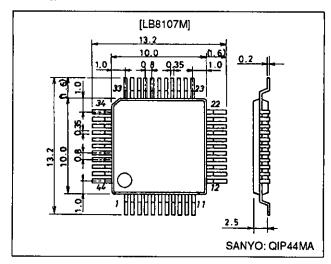

### **Package Dimensions**

unit: mm

#### 3148-QIP44MA

## **Specifications**

### Absolute Maximum Ratings at Ta = 25°C

| Parameter                      | Symbol              | Conditions                            | Ratings     | Unit |

|--------------------------------|---------------------|---------------------------------------|-------------|------|

| Maximum supply voltage         | V <sub>CC</sub> max |                                       | 7.0         | V    |

| H bridge output current        | lout                | Taking 400 mA/channel as the maximum. | 800         | mA   |

| Step-up circuit output current | Icp                 |                                       | 150         | mA   |

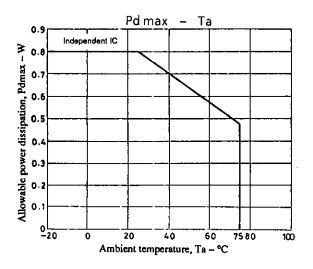

| Allowable power dissipation    | Pd max              |                                       | 800         | mW   |

| Operating temperature          | Topr                |                                       | -25 to +75  | °C   |

| Storage temperature            | Tstg                |                                       | -40 to +125 | °C   |

# Allowable Operating Ranges at $Ta = 25^{\circ}C$

| Parameter        | Symbol          | Conditions | min | typ | max | Unit |

|------------------|-----------------|------------|-----|-----|-----|------|

| Supply voltage   | V <sub>CC</sub> |            | 2.0 | 2.4 | 4.0 | V    |

| Operating output |                 |            |     | 150 |     | mW   |

# Electrical Characteristics at Ta = 25°C, $V_{CC}$ = 2.4 V

|                                     | <del></del>                        |                                                                  | ····                        |                              |                             |                |

|-------------------------------------|------------------------------------|------------------------------------------------------------------|-----------------------------|------------------------------|-----------------------------|----------------|

| Parameter                           | Symbol                             | Conditions                                                       | min                         | typ                          | max                         | Unit           |

| [Power Supply]                      |                                    |                                                                  |                             |                              |                             |                |

| Standby current drain               | Icco                               | S/S1 = H, S/S2 = H                                               |                             |                              | - 10                        | μΑ             |

| Quiescent current                   | 1 <sub>CC</sub>                    |                                                                  |                             | 18                           | 27                          | mA             |

| [Step-up Circuit]                   |                                    |                                                                  |                             | •                            |                             | •              |

| Output voltage                      | V <sub>CD</sub>                    |                                                                  | 4.75                        | 5.0                          | 5.25                        | V              |

| NPN transistor drive current        | Ino                                |                                                                  |                             | 3.0                          |                             | mA             |

| Load characteristics                | ΔV <sub>CD</sub> /I <sub>CD</sub>  |                                                                  |                             |                              | 0.01                        | %/mA           |

| Voltage characteristics             | ΔV <sub>CD</sub> /V <sub>CC</sub>  |                                                                  |                             |                              | 100                         | mV/V           |

| Minimum off duty                    | Ì                                  |                                                                  |                             | 50                           |                             | %              |

| [Oscillator Circuit]                |                                    |                                                                  |                             |                              |                             |                |

| Synchronization signal              | Enviso                             |                                                                  |                             |                              |                             |                |

| input frequency                     | Fsvync                             |                                                                  | 80                          |                              | 100                         | kHz            |

| [H Bridge Outputs]                  |                                    |                                                                  |                             |                              |                             |                |

| Saturation voltage                  | V <sub>CC</sub> (sat)              | 200 mA, TOP + BOTTOM                                             |                             | 0.26                         | 0.39                        | ν              |

| [Motor Control Block]               |                                    |                                                                  | -                           |                              |                             |                |

| Input voltage                       | V <sub>IN</sub>                    | The linear region where V <sub>REF</sub> 1 = 1/2 V <sub>CD</sub> | V <sub>REF</sub> 1<br>- 1.0 | V <sub>REF</sub> 1           | V <sub>REF</sub> 1<br>+ 1.0 | v              |

| Input bias current                  | I <sub>BDR</sub>                   |                                                                  |                             | 1.0                          |                             | μА             |

| Transmission gain (+)               | G <sub>VTR</sub>                   |                                                                  |                             | 7.95                         |                             | dB             |

| Transmission gain ratio (+)/(-)     | ΔG <sub>VTR</sub>                  | Within the same channel                                          |                             | ±1                           |                             | dB             |

| Input dead band voltage             | Vdz                                |                                                                  |                             |                              | V <sub>REF</sub> 1 + 100    | mV             |

| input dead band voltage offset      | Vdzof                              | At the forward/reverse transition within a channel               |                             |                              | ±10                         | mV             |

| [PWM]                               |                                    |                                                                  | <u> </u>                    |                              | L                           |                |

| Maximum output voltage              | V <sub>OUT</sub>                   |                                                                  | 2.1                         | 2.4                          | 2.7                         | V              |

| PNP transistor drive current        | lpi                                | *                                                                | -                           | V <sub>OUT</sub> /600        |                             | mA             |

| Load characteristics                | ΔV <sub>OUT</sub> /Ird             |                                                                  |                             |                              | 0.03                        | %/mA           |

| Voltage characteristics             | ∆V <sub>OUT</sub> /V <sub>CC</sub> |                                                                  |                             |                              | 50                          | mV/V           |

| [Sled Drive Circuit]                | •                                  | -                                                                | <del>-</del>                |                              |                             |                |

| Drive Reference Voltage (step mode) | V <sub>REFO</sub>                  |                                                                  |                             | V <sub>REF</sub> 1<br>+ 0.65 |                             | V              |

| SLS on voltage                      | V <sub>SLS ON</sub>                |                                                                  | 2.0                         |                              |                             | v              |

| SLL input bias current              | IBSLL                              |                                                                  |                             |                              | 300                         | Aις            |

| SLH input bias current              | IBSLH                              |                                                                  |                             |                              | 300                         | μΑ             |

| Defect voltage                      | V <sub>DEF</sub> ON                |                                                                  | 2.0                         |                              |                             | v              |

| [S/S Pins 1 and 2]                  |                                    |                                                                  | - I                         |                              | l                           |                |

| P-on voltage                        |                                    |                                                                  |                             |                              | V <sub>CC</sub> - 1.0       | V              |

| P-off voltage                       |                                    |                                                                  | V <sub>CC</sub> - 0.5       |                              |                             | <del>- v</del> |

| [Reference Voltage Pin]             | 1                                  |                                                                  | 1 00                        |                              | l                           | •              |

| Output current                      | IREFO                              |                                                                  | ·   · · · ·                 |                              | 100                         | μA             |

| Output voltage                      | V <sub>REF</sub> 2                 |                                                                  |                             | 1.2                          |                             | v              |

| [WP Pin]                            | , , , , , ,                        |                                                                  |                             |                              | <u></u>                     | · ·            |

| Output voltage                      | V <sub>OPW</sub>                   |                                                                  | V <sub>CD</sub> 1<br>- 0.15 |                              |                             | ν              |

| [Battery Check Block]               |                                    |                                                                  |                             |                              |                             |                |

| Bl input bias current               | I <sub>BBI</sub>                   |                                                                  |                             |                              | 1.5                         | μΑ             |

| BO output voltage                   | V <sub>OBO</sub>                   | l <sub>OBO</sub> = 500 μA                                        |                             |                              | 0.3                         | ī              |

|                                     | , 500                              |                                                                  |                             |                              |                             |                |

Note: \* This is a design guarantee and is not measured.

Continued on next page.

## Continued from preceding page.

| Parameter                             | Symbol             | Conditions            | min                                   | typ           | max      | Unit |

|---------------------------------------|--------------------|-----------------------|---------------------------------------|---------------|----------|------|

| [CLK Block]                           |                    |                       |                                       | 7,5           |          | 1    |

| CLK input voltage                     | V <sub>CLK</sub>   |                       | 2                                     |               | <u> </u> | Ιv   |

| [Oscillator Block]                    |                    |                       |                                       |               |          | 1    |

| Oscillator power voltage              | Vosce              |                       | V <sub>CC</sub> - 0.15                |               | T        | V    |

| OSC pin input bias current            | IBOSC              |                       |                                       |               | -1.5     | μА   |

| [Integrating Amplifier Block]         |                    |                       |                                       |               |          | L    |

| Input bias current                    | BIA                |                       | · · · · · · · · · · · · · · · · · · · | <del></del> - | 500      | nA   |

| First stage amplifier gain            | GV1                | Open loop, f = 1 kHz* |                                       | 55            |          | dB   |

| Second stage amplifier gain           | GV2                | Internal closed loop  |                                       | 0             |          | dB   |

| First stage output saturation voltage | V <sub>O</sub> 1-1 | t mA SOURCE           | V <sub>CD</sub> - 1.3                 |               |          | V    |

|                                       | V <sub>O</sub> 1-2 | 1 mA SINK             |                                       |               | 1.3      |      |

| Second stage output                   | V <sub>O</sub> 2-1 | 1 mA SOURCE           | V <sub>CD</sub> - 1.3                 |               |          | V    |

| saturation voltage                    | V <sub>O</sub> 2-2 | 1 mA SINK             |                                       |               | 1.3      | V    |

Note: \* This is a design guarantee and is not measured.

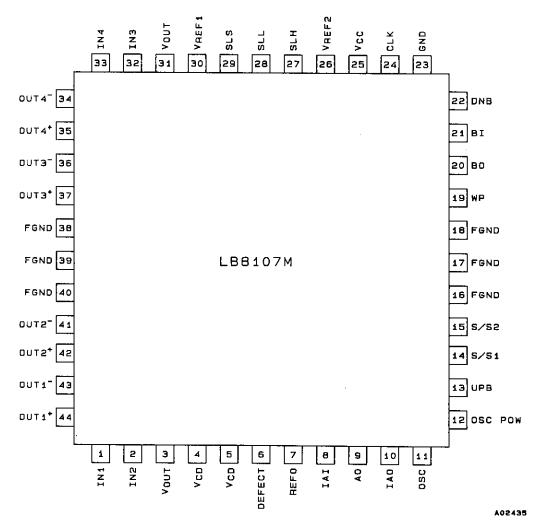

### **Pin Assignment**

Top view

### **Pin Functions**

Unit (resistance:  $\Omega$ )

| Pin No. | Symbol          | 1/0 | Pin function                                                                                                                  |

|---------|-----------------|-----|-------------------------------------------------------------------------------------------------------------------------------|

| 1       | IN1             | 1   | Actuator control input: focus                                                                                                 |

| 2       | IN2             | ı   | Actuator control input: tracking                                                                                              |

| 3, 31   | Vout            |     | Power supply for the four H bridge channels                                                                                   |

| 4, 5    | V <sub>CD</sub> | t   | Step-up circuit output voltage                                                                                                |

| 6       | DEFECT          | 1   | Sets V <sub>OUT</sub> to its maximum voltage on defect input.  VCC  50 # A  A02425                                            |

| 7       | REFO            | 0   | Sled drive reference voltage                                                                                                  |

| 8       | IAI             |     | Integrating amplifier input                                                                                                   |

| 9       | AO              | 0   | Inverting amplifier output                                                                                                    |

| 10      | IAO             |     | Integrating amplifier output                                                                                                  |

| 11      | osc             |     | Free-running oscillator: RC circuit connection                                                                                |

| 12      | OSCPOW          | 0   | Free-running oscillator: RC circuit power supply                                                                              |

| 13      | UPB             | 0   | VCC VCC                                                                                                                       |

| 14      | S/S1            | 1   | Starts the system when a low level is applied as the LB8107M start input (power on lock from the microprocessor)  VCC  AD2427 |

| 15      | S/S2            | 1   | Provides a logical or function with the S/S1 input (for starting from a switch input)  VCC  15  A02428                        |

Continued on next page.

Continued from preceding page.

Unit (resistance:  $\Omega$ )

| Pin No. Symbol I/O Pin function  16, 17, 18, 38, 39, 40  Microprocessor start-up output linked to S/S2. pnp open collector output  VCD1 (5pin)  19 WP  O  Battery low output. npn open collector output; Low: battery low  20 BO  Battery voltage detection pin  VCC |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 38, 39, 40  Microprocessor start-up output linked to S/S2. pnp open collector output  VCD1 (5pin)  A02429  Battery low output. npn open collector output; Low: battery low  A02430  Battery voltage detection pin                                                    |  |

| Battery voltage detection pin  VCD1 (5pin)  VCD1 (5pin)  A02429  A02429  VCD1 (5pin)  A02429  A02429                                                                                                                                                                 |  |

| 20 BO O Battery voltage detection pin                                                                                                                                                                                                                                |  |

| Vcc Vcc                                                                                                                                                                                                                                                              |  |

| 21 Bi I 200 HA A02431                                                                                                                                                                                                                                                |  |

| Voltage reduction pnp transistor drive output  VCC  A08432                                                                                                                                                                                                           |  |

| 23 GND Signal ground                                                                                                                                                                                                                                                 |  |

| CLK  External clock input pin  VCC  SOMA  BOK  BOK  BOK  A02433                                                                                                                                                                                                      |  |

| 25 V <sub>CC</sub> Power supply: 2.0 to 4.0 V                                                                                                                                                                                                                        |  |

| 26 V <sub>REF</sub> 2 Reference voltage: 1.2 V                                                                                                                                                                                                                       |  |

| 27 SLH I Sled drive starting voltage adjustment                                                                                                                                                                                                                      |  |

Continued on next page.

Continued from preceding page.

Unit (resistance:  $\Omega$ )

| Pin No. | Symbol             | 1/0 | Pin function                                                               |

|---------|--------------------|-----|----------------------------------------------------------------------------|

| 28      | SLL                | 1   | Sled drive stop voltage adjustment                                         |

| 29      | SLS                | ı   | Sled switching  VCC  50 M A  A02434                                        |

| 30      | V <sub>REF</sub> 1 | ı   | Motor control block input reference voltage: supplied from the CD servo IC |

| 32      | IN3                | 1   | Actuator control input; Spindle                                            |

| 33      | IN4                | I   | Actuator control input: Sled                                               |

| 34      | OUT4 (-)           | 0   | Actuator control output (-): Sled                                          |

| 35      | OUT4 (+)           | 0   | Actuator control output (+): Sled                                          |

| 36      | OUT3 (-)           | 0   | Actuator control output (-): Spindle                                       |

| 37      | OUT3 (+)           | 0   | Actuator control output (+): Spindle                                       |

| 41      | OUT2 (-)           | 0   | Actuator control output (-): Tracking                                      |

| 42      | OUT2 (+)           | 0   | Actuator control output (+): Tracking                                      |

| 43      | OUT1 (-)           | 0   | Actuator control output (-): Focus                                         |

| 44      | OUT1 (+)           | 0   | Actuator control output (+): Focus                                         |

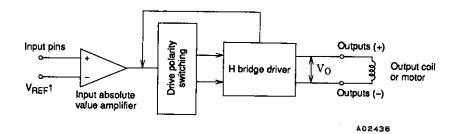

### **Functional Description**

1. Actuator drivers (focus, tracking, spindle and sled)

$V_{REF}1$  is supplied from the CD DSP that is powered by the stepped-up voltage (5.0 V) created by the LB8107M. (Normally,  $V_{REF}1$  will be 1/2  $V_{CD}2$ .)

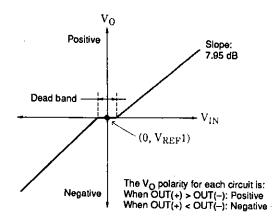

The figure below shows the form of the I/O transmission characteristics.

That is, the LB8107M implements a polarity reversing V-type drive with respect to the input signals (from the DSP) referenced to  $V_{REF}1$ .

The transmission gain  $\Delta V_O/\Delta V_{IN}$  is 7.95 (typical) and the LB8107M provides a region (dead band) around  $V_{REF}1$  where the output does not change with the input. (The dead band is  $V_{REF}1 \pm 100$  mV (maximum).)

The LB8107M provides excellent gain precision since the a feedback structure is adopted in the drive circuits.

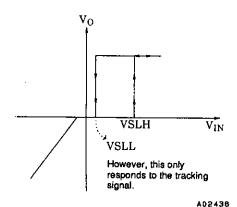

2. Sled motor step drive switching (selected when the SLS pin is low)

While it goes without saying that the V-type drive described above can be used for sled motor drive, the LB8107M also supports a step drive scheme to reduce sled motor drive power.

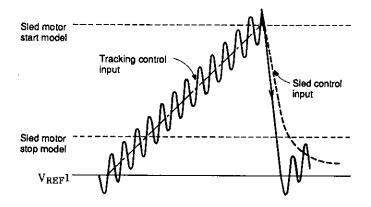

Since a signal that is generated by integrating the tracking output is usually used as the sled motor control input, step drive attempts to drive the sled motor only during certain periods by providing a sled motor start command from the sled motor control input and a sled motor stop command from the tracking control input.

The start and stop levels are set by an external resistor connected between the V<sub>REF</sub>1 pin and the REFO pin.

Note that for inputs that are lower than V<sub>REF</sub>1 this system operates normally regardless of the SLS pin.

Also, as will be discussed later, the maximum voltage is symplical to

Also, as will be discussed later, the maximum voltage is supplied to the H bridge in step drive mode.

#### 3. Step-up Circuit

The step-up circuit can be used to power not only the four driver channel control stages, but also external circuits. (V<sub>DD</sub> is 5.0 V (typical) with an Io of 150 mA (maximum).)

This step-up circuit operates from the built-in oscillator's free-running mode immediately after the system is started.

(The frequency is determined by the RC circuit connected to the OSCP\* pin. When C is 400 pF and R is 30 k $\Omega$ , the frequency will be about 80 kHz.)

Note: \* This pin is used for current pass prevention in standby mode.

After the system is started, (to bring up the CD DSP and other circuits) when a clock with a frequency (e.g., 2fc = 88.2 kHz) greater than the free-running frequency is input to the CLK pin, the oscillator synchronizes with the input clock. → frequency only synchronization. (Since the frequency range is from 80 to 100 kHz, 88.2 kHz is optimal as the input frequency.)

Since the on/off duty ratio is set to have a maximum of 50%, i.e., the on period ranges from 0 to 50%, this provides a protection function for the output transistors when large loads are applied. (We strongly recommend using output transistors with an  $h_{FE}$  as large as possible. Also, for efficiency, we recommend using Schottky diodes.)

### 4. PWM Power Supply Scheme

To improve power efficiency as much as possible in the LB8107M, maximum value output PWM voltage conversion is used in the power supply for each of the four H bridge driver channels.

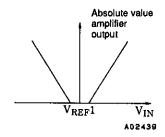

5. The maximum value of the control block outputs (the outputs of the absolute value amplifiers with respect to their

inputs) for each of the drivers is detected, and a voltage consisting of that voltage plus a margin (the offset) is supplied to the H bridge for each channel using PWM voltage conversion (step-down converter). (This allows the actuators to be driven with the minimum power in cases such as, for example, when the operating voltages for all four actuator channels are identical and small.) Unlike schemes in which a PWM converter is provided for each channel, only one L/C pair is required, and furthermore, since the actuator drive is linear, this scheme does not generate the noise levels associated with direct PWM schemes. Also, since the voltage supplied to the H bridges by this PWM scheme is limited to 2.4 V (typical), there are no

changes in the maximum currents supplied to the actuators associated with changes in the power supply voltage used. Furthermore, this scheme is designed so that the maximum voltage is supplied when the defect signal from the DSP, which indicates the presence of defects, is high or when in sled motor step drive mode.

#### 6. System Start and Stop Commands

The LB8107M is designed so that the system can be started and stopped by the control microprocessor.

#### [Start]

The pins S/S1 and S/S2 are provided as system startup pins. Of these, S/S1 locks the system power supply when it is set low by the microprocessor as a power on lock. S/S2 is provided to be used for startup from a switch and the function operates by taking the logical with S/S1. However, the microprocessor can still apply the S/S1 power on lock by reading the WP (wake up) pin output, since this output is goes high when S/S2 is low.

### [Stop]

The system power supply can be shut down by setting both S/S1 and S/S2 high. This puts the LB8107M in standby mode.

#### [Other notes]

- Circuit blocks that use VCD1 as the power supply

Integrating amplifier, inverting amplifier, sled switching circuit (including SLS, SLH and SLL) and the maximum value circuit

- Circuit blocks that use VCC as the power supply

Step-up circuit, step-down circuit, reference voltage, battery check, oscillator, edge start and other circuits.

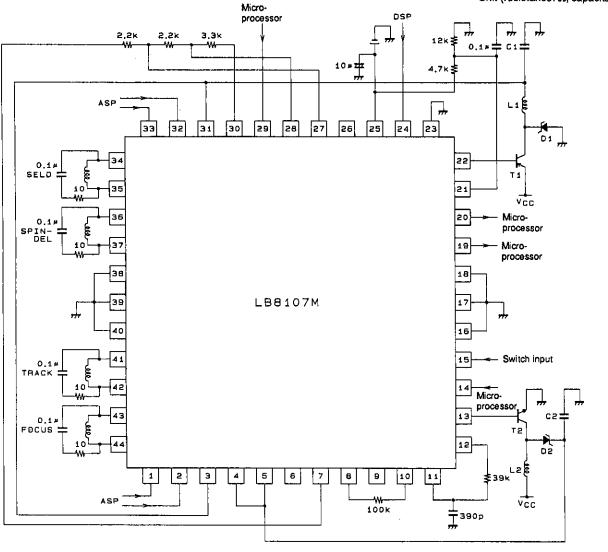

### **Application Circuit**

Unit (resistance:  $\Omega$ , capacitance: F)

A02440

| T1      | 2SB815   |

|---------|----------|

| T2      | 2SC3650  |

| D1 = D2 | SB07-03C |

| L1 = L2 | 30 μH    |

| 04 00   |          |

C1 = C2 .......100  $\mu$ F

To control the spindle motor using a digital servo scheme, input the PWM output to pin 8, set up the external integration constant, and input the output from pin 9 to the spindle input.

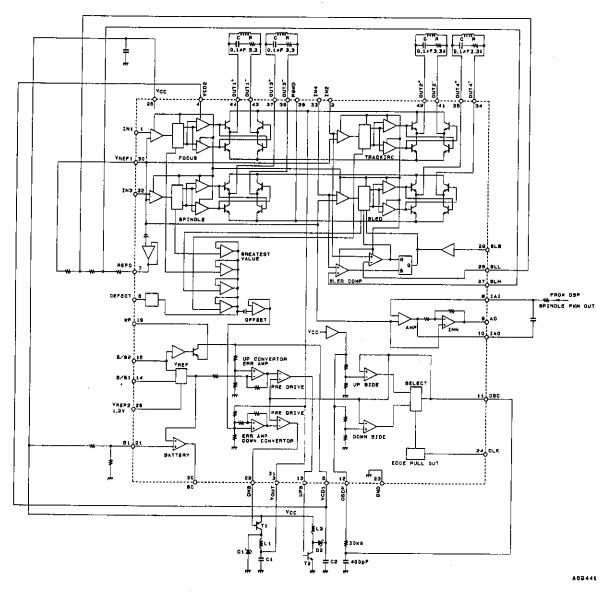

### **Internal Equivalent Circuit**

### Reference values

| meterice value: | 5                            |

|-----------------|------------------------------|

| T1              | 2SB815                       |

| T2              | 2SC3650                      |

| D1 = D2         | SB07-03C                     |

| L1 = L2         | 30 μH (under 1.35 Ω, 600 mA) |

| C1 = C2         | 100 μF                       |

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- 2 Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.