PM7323 RCMP-200

DATASHEET PMC-960543

ISSUE 2

ROUTING CONTROL, MONITORING, & POLICING 200 MBPS

# PM7323

# **RCMP-200**

# ATM LAYER ROUTING CONTROL, MONITORING AND POLICING 200 MBPS

**ISSUE 2: NOVEMBER 1997**

DATASHEET PMC-960543

ISSUE 2

ISSUE 2

PMC-Sierra, Inc.

ROUTING CONTROL, MONITORING, & POLICING 200 MBPS

# **CONTENTS**

| 1 | FEATURES 1   |                                                                          |  |  |  |

|---|--------------|--------------------------------------------------------------------------|--|--|--|

| 2 | APPLICATIONS |                                                                          |  |  |  |

| 3 | REFE         | REFERENCES                                                               |  |  |  |

| 4 | APPL         | ICATION EXAMPLES6                                                        |  |  |  |

| 5 | BLOC         | K DIAGRAM                                                                |  |  |  |

| 6 | DESC         | RIPTION 10                                                               |  |  |  |

| 7 | PIN D        | IAGRAM 12                                                                |  |  |  |

| 8 | PIN D        | ESCRIPTION (TOTAL 240) 13                                                |  |  |  |

| 9 | FUNC         | TIONAL DESCRIPTION                                                       |  |  |  |

|   | 9.1          | INPUT BUFFERING                                                          |  |  |  |

|   | 9.2          | VC IDENTIFICATION                                                        |  |  |  |

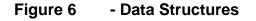

|   |              | 9.2.1 SEARCH TABLE DATA STRUCTURE                                        |  |  |  |

|   | 9.3          | CELL PROCESSING 41                                                       |  |  |  |

|   |              | 9.3.1 CONFIGURATION AND STATUS 42                                        |  |  |  |

|   |              | 9.3.2 HEADER TRANSLATION                                                 |  |  |  |

|   |              | 9.3.3 CELL ROUTING 45                                                    |  |  |  |

|   |              | 9.3.4 CELL RATE POLICING 46                                              |  |  |  |

|   |              | 9.3.5 CELL COUNTING 50                                                   |  |  |  |

|   |              | 9.3.6 OPERATIONS, ADMINISTRATION AND MAINTENANCE<br>(OAM) CELL SERVICING |  |  |  |

|   |              | 9.3.7 FAULT MANAGEMENT CELLS 55                                          |  |  |  |

PMC-Sierra, Inc.

ISSUE 2

|    |      | 9.3.8 PERFORMANCE MANAGEMENT CELLS                |

|----|------|---------------------------------------------------|

|    |      | 9.3.9 ACTIVATION/DEACTIVATION CELLS               |

|    |      | 9.3.10 RESOURCE MANAGEMENT CELLS 59               |

|    |      | 9.3.11 BACKWARD OAM AND RM CELL IDENTIFICATION 59 |

|    | 9.4  | MULTICASTING 60                                   |

|    | 9.5  | OUTPUT BUFFERING 61                               |

|    | 9.6  | CONGESTION CONTROL                                |

|    | 9.7  | JTAG TEST ACCESS PORT INTERFACE 62                |

|    | 9.8  | MICROPROCESSOR INTERFACE 62                       |

|    |      | 9.8.1 SRAM ACCESSES                               |

|    |      | 9.8.2 WRITING CELLS                               |

|    |      | 9.8.3 READING CELLS                               |

|    |      | 9.8.4 NORMAL MODE REGISTER MEMORY MAP 68          |

| 10 | NORI | MAL MODE REGISTER DESCRIPTIONS                    |

|    | 10.1 | MASTER REGISTERS                                  |

| 11 | TEST | FEATURES DESCRIPTION 152                          |

|    | 11.1 | TEST MODE 0 DETAILS 154                           |

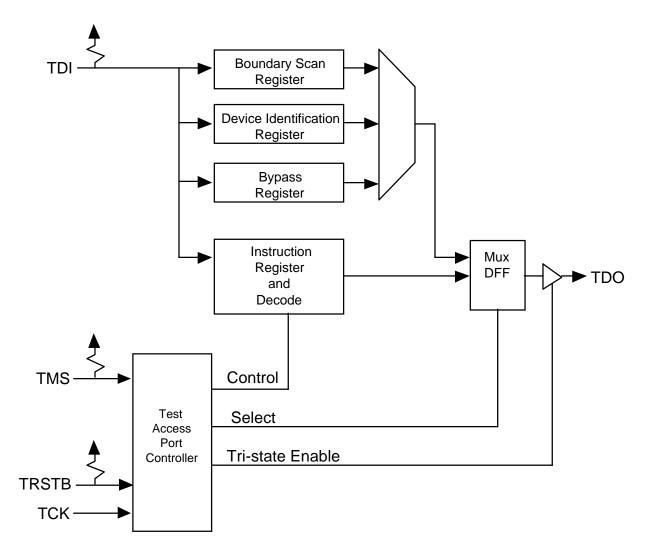

|    | 11.2 | JTAG TEST PORT 155                                |

| 12 | OPEF | RATION 158                                        |

|    | 12.1 | SCI-PHY EXTENDED CELL FORMAT 158                  |

|    | 12.2 | SYNCHRONOUS STATIC RAMS 160                       |

|    | 12.3 | OAM CELL FORMAT 160                               |

PMC-Sierra, Inc.

| DATASHEET  |         |                                                     |

|------------|---------|-----------------------------------------------------|

| РМС-960543 | ISSUE 2 | ROUTING CONTROL, MONITORING, & POLICING<br>200 MBPS |

|    |      | 12.3.1 RECEIVED OAM CELLS 161                   |

|----|------|-------------------------------------------------|

|    |      | 12.3.2 GENERATED OAM CELLS 163                  |

|    | 12.4 | VC IDENTIFICATION SEARCH ALGORITHM 164          |

|    |      | 12.4.1 OVERVIEW                                 |

|    |      | 12.4.2 INITIALIZATION                           |

|    |      | 12.4.3 ADDING A CONNECTION 166                  |

|    |      | 12.4.4 REMOVING A CONNECTION 171                |

|    |      | 12.4.5 MULTICAST CONNECTIONS 172                |

|    | 12.5 | JTAG SUPPORT 175                                |

| 13 | FUNC | TIONAL TIMING 182                               |

|    | 13.1 | INPUT CELL INTERFACE 182                        |

|    | 13.2 | OUTPUT CELL INTERFACE                           |

| 14 | ABSC | DLUTE MAXIMUM RATINGS 188                       |

| 15 | D.C. | CHARACTERISTICS                                 |

| 16 | MICR | OPROCESSOR INTERFACE TIMING CHARACTERISTICS 191 |

| 17 | RCM  | P-200 TIMING CHARACTERISTICS 197                |

| 18 | MECH | HANICAL INFORMATION                             |

DATASHEET PMC-960543

ISSUE 2

PMC-Sierra, Inc.

ROUTING CONTROL, MONITORING, & POLICING 200 MBPS

# LIST OF REGISTERS

| REGISTER 0X00: MASTER RESET AND IDENTITY / LOAD METERS             |

|--------------------------------------------------------------------|

| REGISTER 0X01: MASTER CONFIGURATION                                |

| REGISTER 0X02: MASTER INTERRUPT STATUS #1                          |

| REGISTER 0X03: MASTER INTERRUPT STATUS #2                          |

| REGISTER 0X04: MASTER INTERRUPT ENABLE #1 83                       |

| REGISTER 0X05: MASTER INTERRUPT ENABLE #2 85                       |

| REGISTER 0X06: MASTER CLOCK MONITOR 86                             |

| REGISTER 0X07: LATEST ALARMED VIRTUAL CONNECTIONS 88               |

| REGISTER 0X08: INPUT CELL FIFO CONFIGURATION                       |

| REGISTER 0X09: PHYSICAL LAYER CELL COUNT                           |

| REGISTER 0X0A: INPUT CELL COUNTER (LSB)                            |

| REGISTER 0X0B: INPUT CELL COUNTER (MSB)                            |

| REGISTER 0XC: INPUT POLLING CONFIGURATION                          |

| REGISTER 0X10: MICROPROCESSOR EXTRACT BUFFER CONTROL AND<br>STATUS |

| REGISTER 0X11: MICROPROCESSOR INSERT BUFFER CONTROL AND<br>STATUS  |

| REGISTER 0X12: MICROPROCESSOR CELL DATA                            |

| REGISTER 0X18: CELL PROCESSOR CONFIGURATION 108                    |

| REGISTER 0X19: PERFORMANCE MONITORING CONFIGURATION 1 112          |

| REGISTER 0X1A: PERFORMANCE MONITORING CONFIGURATION 2 114          |

PMC-Sierra, Inc.

DATASHEET PMC-960543

ISSUE 2

| REGISTER 0X1C: VBR/CBR CELL RATE POLICING CONFIGURATION118REGISTER 0X1D: ROUTING CONFIGURATION121REGISTER 0X20: CRAM CONFIGURATION125REGISTER 0X21: EXTERNAL RAM ADDRESS (LSB)128REGISTER 0X22: EXTERNAL RAM ADDRESS (MSB) AND ACCESS<br>CONTROL129REGISTER 0X23: EXTERNAL RAM DATA (LSB)131REGISTER 0X24: EXTERNAL RAM DATA (LSB)133REGISTER 0X25: EXTERNAL RAM DATA (MSB)133REGISTER 0X26: MAXIMUM VC TABLE INDEX134REGISTER 0X27: SEARCH KEY CONSTRUCTION135REGISTER 0X28: FIELD A LOCATION AND LENGTH139REGISTER 0X30: COUNTER STATUS141REGISTER 0X31: VALID OAM CELL COUNT145REGISTER 0X32: ERRORED OAM CELL COUNT146REGISTER 0X33: INVALID CELL COUNT146REGISTER 0X34: COUNT OF CELLS DROPPED DUE TO CONGESTION 147148REGISTER 0X38: OUTPUT CELL FIFO CONFIGURATION148REGISTER 0X38: OUTPUT CELL COUNTER (LSB)150REGISTER 0X38: OUTPUT CELL COUNTER (MSB)151REGISTER 0X38: OUTPUT CELL COUNTER (MSB)151REGISTER 0X38: OUTPUT CELL COUNTER (MSB)151REGISTER 0X40: MASTER TEST153 | REGISTER 0X1B: ABR CELL RATE POLICING CONFIGURATION 116     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| REGISTER 0X20: CRAM CONFIGURATION125REGISTER 0X21: EXTERNAL RAM ADDRESS (LSB)128REGISTER 0X22: EXTERNAL RAM ADDRESS (MSB) AND ACCESS<br>CONTROL129REGISTER 0X23: EXTERNAL RAM DATA (LSB)131REGISTER 0X24: EXTERNAL RAM DATA (LSB)131REGISTER 0X25: EXTERNAL RAM DATA (MSB)133REGISTER 0X26: MAXIMUM VC TABLE INDEX134REGISTER 0X27: SEARCH KEY CONSTRUCTION135REGISTER 0X28: FIELD A LOCATION AND LENGTH137REGISTER 0X30: COUNTER STATUS141REGISTER 0X31: VALID OAM CELL COUNT143REGISTER 0X32: ERRORED OAM CELL COUNT146REGISTER 0X33: INVALID CELL COUNT146REGISTER 0X38: OUTPUT CELL SDROPPED DUE TO CONGESTION 147REGISTER 0X38: OUTPUT CELL COUNTER (MSB)150REGISTER 0X38: OUTPUT CELL COUNTER (MSB)151                                                                                                                                                                                                                                                                          | REGISTER 0X1C: VBR/CBR CELL RATE POLICING CONFIGURATION 118 |

| REGISTER 0X21: EXTERNAL RAM ADDRESS (LSB)128REGISTER 0X22: EXTERNAL RAM ADDRESS (MSB) AND ACCESS<br>CONTROL129REGISTER 0X23: EXTERNAL RAM DATA (LSB)131REGISTER 0X24: EXTERNAL RAM DATA (LSB)131REGISTER 0X25: EXTERNAL RAM DATA (MSB)133REGISTER 0X26: MAXIMUM VC TABLE INDEX.134REGISTER 0X27: SEARCH KEY CONSTRUCTION.135REGISTER 0X28: FIELD A LOCATION AND LENGTH.137REGISTER 0X29: FIELD B LOCATION AND LENGTH.139REGISTER 0X31: VALID OAM CELL COUNT.143REGISTER 0X32: ERRORED OAM CELL COUNT.146REGISTER 0X33: INVALID CELL COUNT.147REGISTER 0X38: OUTPUT CELL FIFO CONFIGURATION.148REGISTER 0X38: OUTPUT CELL COUNTER (MSB)150REGISTER 0X38: OUTPUT CELL COUNTER (MSB)151                                                                                                                                                                                                                                                                                                  | REGISTER 0X1D: ROUTING CONFIGURATION 121                    |

| REGISTER 0X22: EXTERNAL RAM ADDRESS (MSB) AND ACCESS<br>CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | REGISTER 0X20: CRAM CONFIGURATION 125                       |

| CONTROL129REGISTER 0X23: EXTERNAL RAM DATA (LSB)131REGISTER 0X24: EXTERNAL RAM DATA.132REGISTER 0X25: EXTERNAL RAM DATA (MSB)133REGISTER 0X26: MAXIMUM VC TABLE INDEX.134REGISTER 0X27: SEARCH KEY CONSTRUCTION.135REGISTER 0X28: FIELD A LOCATION AND LENGTH.137REGISTER 0X29: FIELD B LOCATION AND LENGTH.139REGISTER 0X30: COUNTER STATUS141REGISTER 0X31: VALID OAM CELL COUNT.143REGISTER 0X32: ERRORED OAM CELL COUNT.146REGISTER 0X34: COUNT OF CELLS DROPPED DUE TO CONGESTION 147REGISTER 0X38: OUTPUT CELL FIFO CONFIGURATION.148REGISTER 0X38: OUTPUT CELL COUNTER (MSB)151                                                                                                                                                                                                                                                                                                                                                                                                | REGISTER 0X21: EXTERNAL RAM ADDRESS (LSB) 128               |

| REGISTER 0X24:EXTERNAL RAM DATA132REGISTER 0X25:EXTERNAL RAM DATA (MSB)133REGISTER 0X26:MAXIMUM VC TABLE INDEX134REGISTER 0X27:SEARCH KEY CONSTRUCTION135REGISTER 0X28:FIELD A LOCATION AND LENGTH137REGISTER 0X29:FIELD B LOCATION AND LENGTH139REGISTER 0X30:COUNTER STATUS141REGISTER 0X31:VALID OAM CELL COUNT143REGISTER 0X32:ERRORED OAM CELL COUNT145REGISTER 0X33:INVALID CELL COUNT146REGISTER 0X34:COUNT OF CELLS DROPPED DUE TO CONGESTION 147148REGISTER 0X38:OUTPUT CELL FIFO CONFIGURATION148REGISTER 0X38:OUTPUT CELL COUNTER (LSB)150REGISTER 0X3B:OUTPUT CELL COUNTER (MSB)151                                                                                                                                                                                                                                                                                                                                                                                       |                                                             |

| REGISTER 0X25: EXTERNAL RAM DATA (MSB)133REGISTER 0X26: MAXIMUM VC TABLE INDEX.134REGISTER 0X27: SEARCH KEY CONSTRUCTION.135REGISTER 0X28: FIELD A LOCATION AND LENGTH.137REGISTER 0X29: FIELD B LOCATION AND LENGTH.139REGISTER 0X30: COUNTER STATUS141REGISTER 0X31: VALID OAM CELL COUNT.143REGISTER 0X32: ERRORED OAM CELL COUNT.146REGISTER 0X33: INVALID CELL COUNT.146REGISTER 0X34: COUNT OF CELLS DROPPED DUE TO CONGESTION 147REGISTER 0X38: OUTPUT CELL FIFO CONFIGURATION.148REGISTER 0X3A: OUTPUT CELL COUNTER (LSB)150REGISTER 0X3B: OUTPUT CELL COUNTER (MSB)151                                                                                                                                                                                                                                                                                                                                                                                                       | REGISTER 0X23: EXTERNAL RAM DATA (LSB) 131                  |

| REGISTER 0X26: MAXIMUM VC TABLE INDEX.134REGISTER 0X27: SEARCH KEY CONSTRUCTION.135REGISTER 0X28: FIELD A LOCATION AND LENGTH.137REGISTER 0X29: FIELD B LOCATION AND LENGTH.139REGISTER 0X30: COUNTER STATUS141REGISTER 0X31: VALID OAM CELL COUNT.143REGISTER 0X32: ERRORED OAM CELL COUNT.145REGISTER 0X33: INVALID CELL COUNT.146REGISTER 0X34: COUNT OF CELLS DROPPED DUE TO CONGESTION 147REGISTER 0X38: OUTPUT CELL FIFO CONFIGURATION.148REGISTER 0X3A: OUTPUT CELL COUNTER (LSB)150REGISTER 0X3B: OUTPUT CELL COUNTER (MSB)151                                                                                                                                                                                                                                                                                                                                                                                                                                                | REGISTER 0X24: EXTERNAL RAM DATA 132                        |

| REGISTER 0X27: SEARCH KEY CONSTRUCTION.135REGISTER 0X28: FIELD A LOCATION AND LENGTH.137REGISTER 0X29: FIELD B LOCATION AND LENGTH.139REGISTER 0X30: COUNTER STATUS141REGISTER 0X31: VALID OAM CELL COUNT.143REGISTER 0X32: ERRORED OAM CELL COUNT.145REGISTER 0X33: INVALID CELL COUNT.146REGISTER 0X34: COUNT OF CELLS DROPPED DUE TO CONGESTION 147REGISTER 0X38: OUTPUT CELL FIFO CONFIGURATION.148REGISTER 0X3A: OUTPUT CELL COUNTER (LSB)150REGISTER 0X3B: OUTPUT CELL COUNTER (MSB)151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | REGISTER 0X25: EXTERNAL RAM DATA (MSB) 133                  |

| REGISTER 0X28: FIELD A LOCATION AND LENGTH.137REGISTER 0X29: FIELD B LOCATION AND LENGTH.139REGISTER 0X30: COUNTER STATUS141REGISTER 0X31: VALID OAM CELL COUNT.143REGISTER 0X32: ERRORED OAM CELL COUNT.145REGISTER 0X33: INVALID CELL COUNT.146REGISTER 0X34: COUNT OF CELLS DROPPED DUE TO CONGESTION 147REGISTER 0X38: OUTPUT CELL FIFO CONFIGURATION.148REGISTER 0X3A: OUTPUT CELL COUNTER (LSB)150REGISTER 0X3B: OUTPUT CELL COUNTER (MSB)151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | REGISTER 0X26: MAXIMUM VC TABLE INDEX 134                   |

| REGISTER 0X29: FIELD B LOCATION AND LENGTH.139REGISTER 0X30: COUNTER STATUS141REGISTER 0X31: VALID OAM CELL COUNT.143REGISTER 0X32: ERRORED OAM CELL COUNT.145REGISTER 0X33: INVALID CELL COUNT.146REGISTER 0X34: COUNT OF CELLS DROPPED DUE TO CONGESTION 147REGISTER 0X38: OUTPUT CELL FIFO CONFIGURATION.148REGISTER 0X3A: OUTPUT CELL COUNTER (LSB)150REGISTER 0X3B: OUTPUT CELL COUNTER (MSB)151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | REGISTER 0X27: SEARCH KEY CONSTRUCTION 135                  |

| REGISTER 0X30: COUNTER STATUS141REGISTER 0X31: VALID OAM CELL COUNT143REGISTER 0X32: ERRORED OAM CELL COUNT145REGISTER 0X33: INVALID CELL COUNT146REGISTER 0X34: COUNT OF CELLS DROPPED DUE TO CONGESTION 147REGISTER 0X38: OUTPUT CELL FIFO CONFIGURATION148REGISTER 0X3A: OUTPUT CELL COUNTER (LSB)150REGISTER 0X3B: OUTPUT CELL COUNTER (MSB)151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | REGISTER 0X28: FIELD A LOCATION AND LENGTH                  |

| REGISTER 0X31: VALID OAM CELL COUNT.143REGISTER 0X32: ERRORED OAM CELL COUNT.145REGISTER 0X33: INVALID CELL COUNT.146REGISTER 0X34: COUNT OF CELLS DROPPED DUE TO CONGESTION 147REGISTER 0X38: OUTPUT CELL FIFO CONFIGURATION.148REGISTER 0X3A: OUTPUT CELL COUNTER (LSB)150REGISTER 0X3B: OUTPUT CELL COUNTER (MSB)151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | REGISTER 0X29: FIELD B LOCATION AND LENGTH                  |

| REGISTER 0X32: ERRORED OAM CELL COUNT.145REGISTER 0X33: INVALID CELL COUNT.146REGISTER 0X34: COUNT OF CELLS DROPPED DUE TO CONGESTION 147REGISTER 0X38: OUTPUT CELL FIFO CONFIGURATION.148REGISTER 0X3A: OUTPUT CELL COUNTER (LSB)150REGISTER 0X3B: OUTPUT CELL COUNTER (MSB)151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | REGISTER 0X30: COUNTER STATUS 141                           |

| REGISTER 0X33: INVALID CELL COUNT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | REGISTER 0X31: VALID OAM CELL COUNT 143                     |

| REGISTER 0X34: COUNT OF CELLS DROPPED DUE TO CONGESTION 147<br>REGISTER 0X38: OUTPUT CELL FIFO CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | REGISTER 0X32: ERRORED OAM CELL COUNT 145                   |

| REGISTER 0X38: OUTPUT CELL FIFO CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | REGISTER 0X33: INVALID CELL COUNT 146                       |

| REGISTER 0X3A: OUTPUT CELL COUNTER (LSB) 150<br>REGISTER 0X3B: OUTPUT CELL COUNTER (MSB) 151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | REGISTER 0X34: COUNT OF CELLS DROPPED DUE TO CONGESTION 147 |

| REGISTER 0X3B: OUTPUT CELL COUNTER (MSB) 151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | REGISTER 0X38: OUTPUT CELL FIFO CONFIGURATION               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | REGISTER 0X3A: OUTPUT CELL COUNTER (LSB) 150                |

| REGISTER 0X40: MASTER TEST 153                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | REGISTER 0X3B: OUTPUT CELL COUNTER (MSB) 151                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | REGISTER 0X40: MASTER TEST 153                              |

DATASHEET PMC-960543

ISSUE 2

PMC-Sierra, Inc.

ROUTING CONTROL, MONITORING, & POLICING 200 MBPS

# LIST OF FIGURES

| FIGURE 1 - OC-3 SWITCH PORT APPLICATION                                                            |

|----------------------------------------------------------------------------------------------------|

| FIGURE 2 - DS-1 PHY ADDRESSING APPLICATION                                                         |

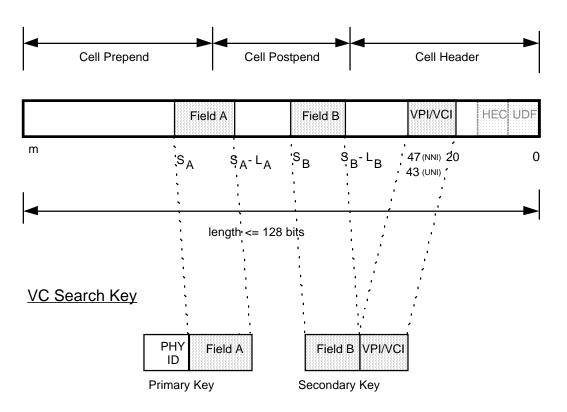

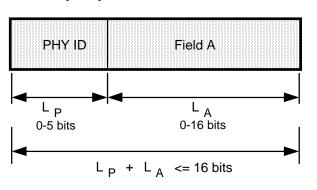

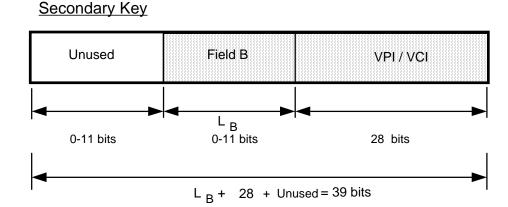

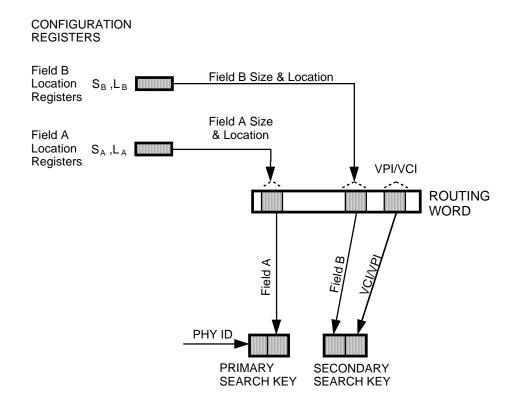

| FIGURE 3 - VC SEARCH KEY COMPOSITION                                                               |

| FIGURE 4 - PARAMETERS OF PRIMARY KEY AND SECONDARY KEY 35                                          |

| FIGURE 5 - CONSTRUCTION OF SEARCH KEYS                                                             |

| FIGURE 6 - DATA STRUCTURES                                                                         |

| FIGURE 7 - EIGHT BIT WIDE CELL FORMAT 159                                                          |

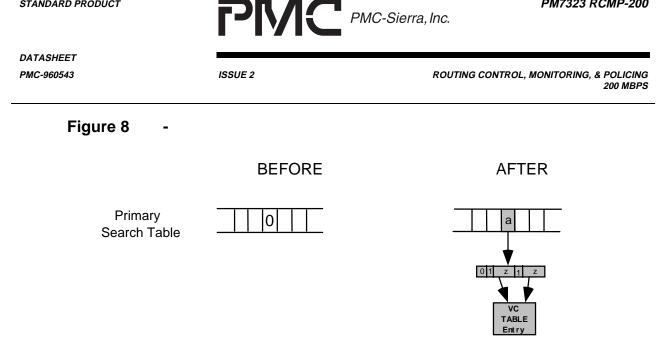

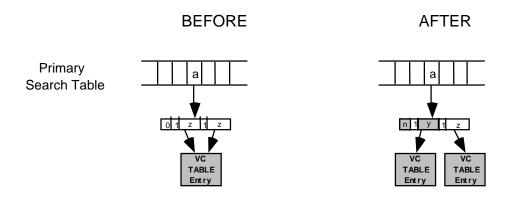

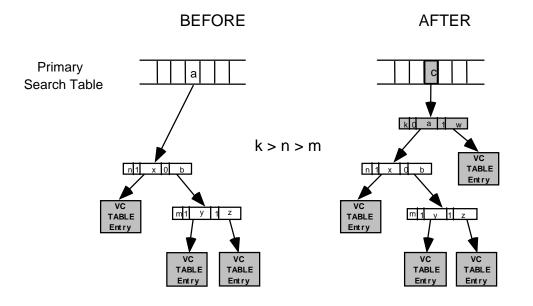

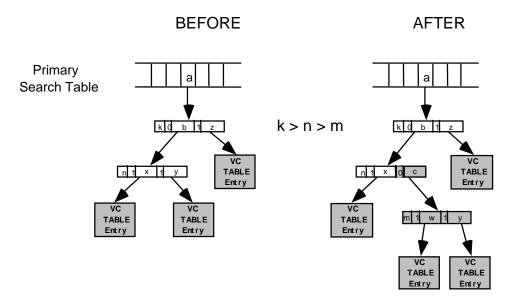

| FIGURE 8 168                                                                                       |

| FIGURE 9 168                                                                                       |

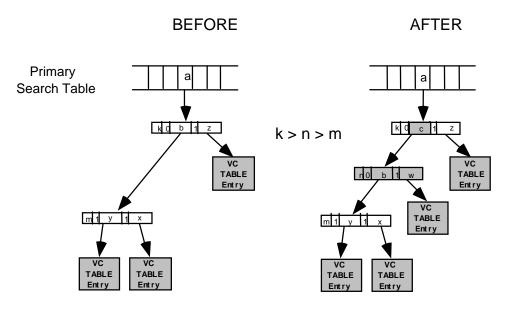

| FIGURE 10 169                                                                                      |

| FIGURE 11 170                                                                                      |

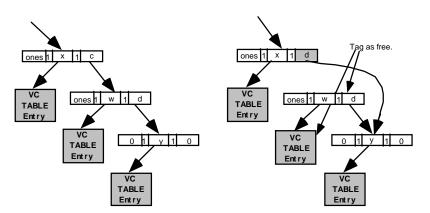

| FIGURE 12 171                                                                                      |

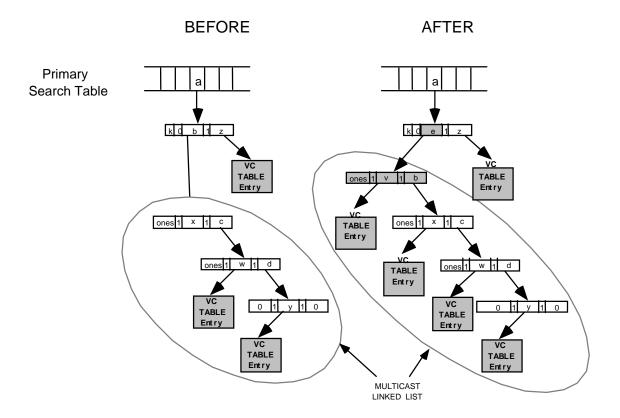

| FIGURE 13 173                                                                                      |

| FIGURE 14 174                                                                                      |

| FIGURE 15- BOUNDARY SCAN ARCHITECTURE 176                                                          |

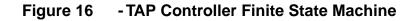

| FIGURE 16- TAP CONTROLLER FINITE STATE MACHINE                                                     |

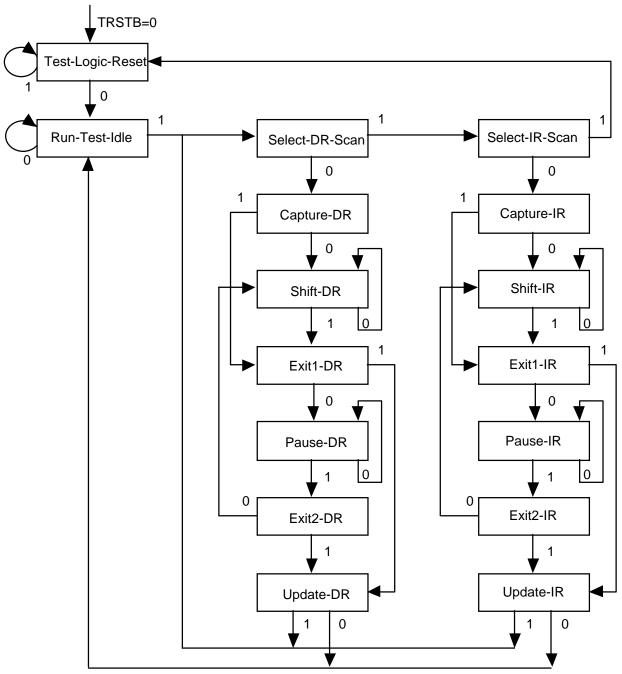

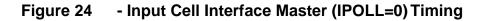

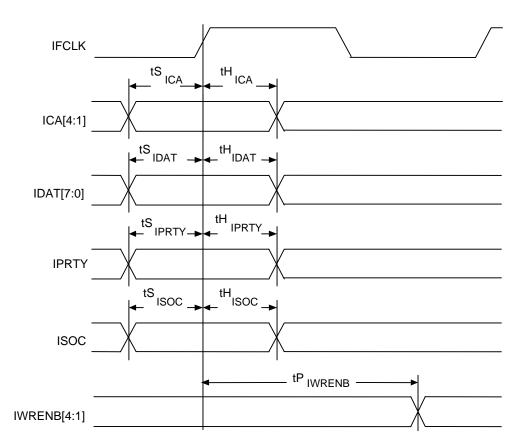

| FIGURE 17- INPUT CELL MASTER INTERFACE (IPOLL=0) 182                                               |

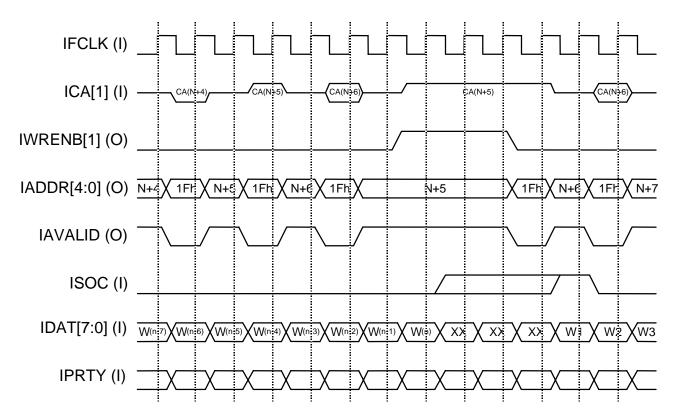

| FIGURE 18- INPUT CELL INTERFACE ADDRESS LINE POLLING MASTER<br>CONFIGURATION (IPOLL=1) – EXAMPLE 1 |

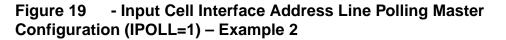

| FIGURE 19- INPUT CELL INTERFACE ADDRESS LINE POLLING MASTER<br>CONFIGURATION (IPOLL=1) – EXAMPLE 2 |

PMC-Sierra, Inc.

DATASHEET PMC-960543

ISSUE 2

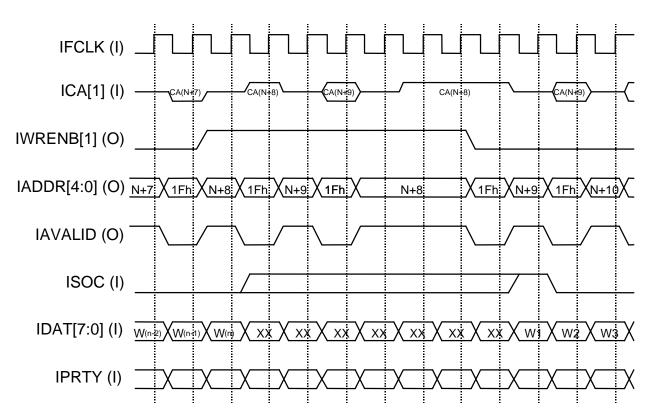

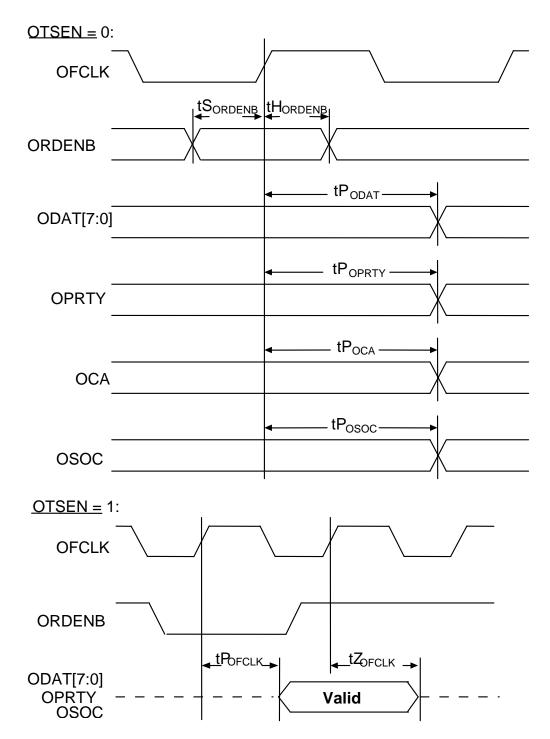

| FIGURE 20- OUTPUT CELL INTERFACE SINGLE-PHY SLAVE ( OTSEN=0)186   |

|-------------------------------------------------------------------|

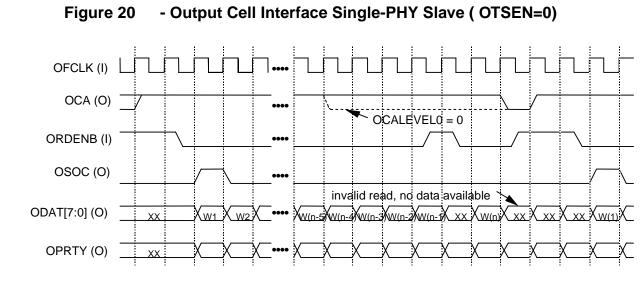

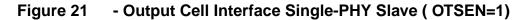

| FIGURE 21- OUTPUT CELL INTERFACE SINGLE-PHY SLAVE ( OTSEN=1)187   |

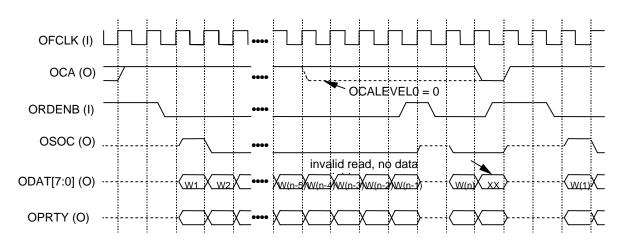

| FIGURE 22- MICROPROCESSOR INTERFACE READ TIMING 192               |

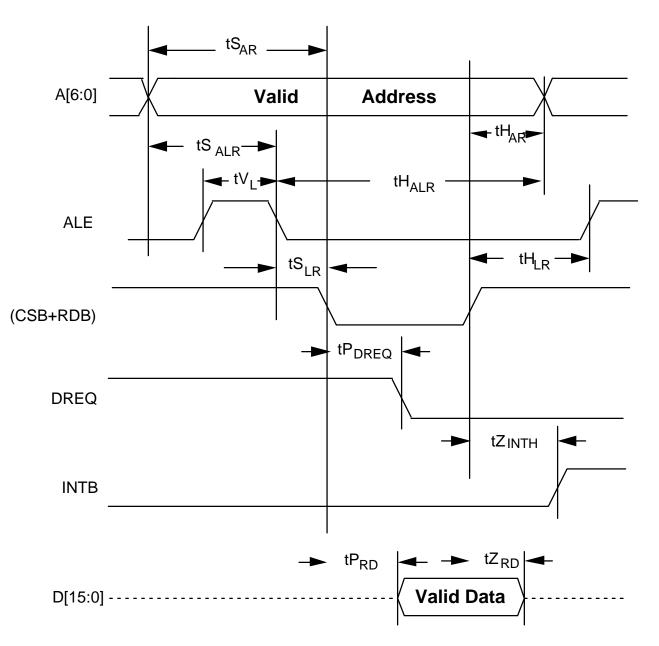

| FIGURE 23- MICROPROCESSOR INTERFACE WRITE TIMING 195              |

| FIGURE 24- INPUT CELL INTERFACE MASTER (IPOLL=0) TIMING           |

| FIGURE 25- INPUT CELL INTERFACE MASTER (IPOLL=1) TIMING           |

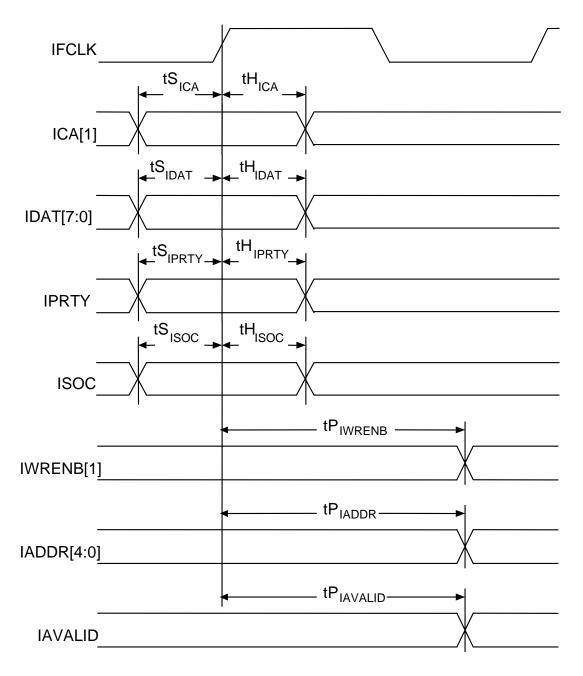

| FIGURE 26- OUTPUT CELL INTERFACE SLAVE TIMING 201                 |

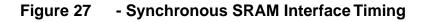

| FIGURE 27- SYNCHRONOUS SRAM INTERFACE TIMING 203                  |

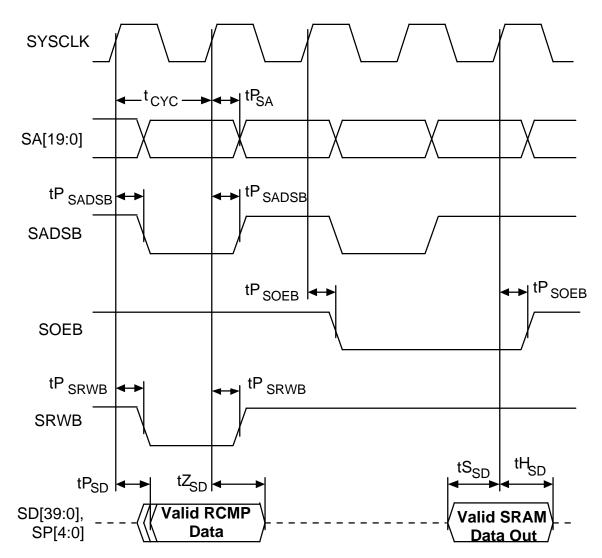

| FIGURE 28- JTAG PORT INTERFACE TIMING 205                         |

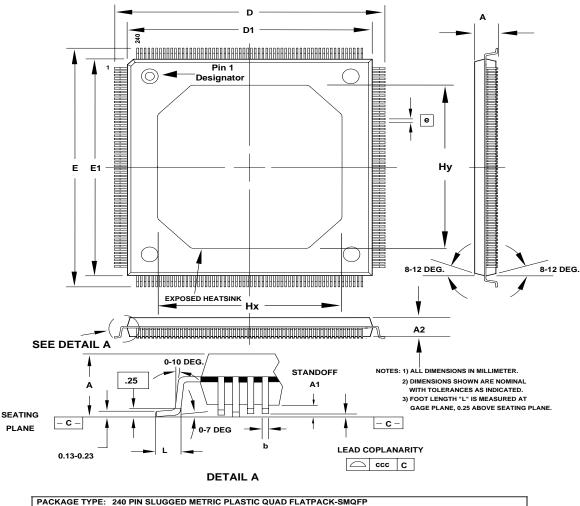

| FIGURE 29- 240 PIN SLUGGED PLASTIC QUAD FLAT PACK (S SUFFIX): 207 |

DATASHEET PMC-960543

ISSUE 2

PMC-Sierra, Inc.

ROUTING CONTROL, MONITORING, & POLICING 200 MBPS

## LIST OF TABLES

| TABLE 1  | - OUTPUT CELL INTERFACE SIGNALS (24) 13      |

|----------|----------------------------------------------|

| TABLE 2  | - INPUT CELL INTERFACE SIGNALS (30) 15       |

| TABLE 3  | - SYNCHRONOUS SRAM INTERFACE SIGNALS (70) 20 |

| TABLE 4  | - MICROPROCESSOR INTERFACE SIGNALS (30)      |

| TABLE 5  | - MISC. INTERFACE SIGNALS (66)               |

| TABLE 6  | - VC TABLE RECORD                            |

| TABLE 7  |                                              |

| TABLE 8  |                                              |

| TABLE 9  |                                              |

| TABLE 10 |                                              |

| TABLE 11 |                                              |

| TABLE 12 |                                              |

| TABLE 13 |                                              |

| TABLE 14 |                                              |

| TABLE 15 |                                              |

| TABLE 16 |                                              |

| TABLE 17 |                                              |

| TABLE 18 | 70                                           |

| TABLE 19 |                                              |

| TABLE 20 | - INSTRUCTION REGISTER 156                   |

| TABLE 21 | - BOUNDARY SCAN REGISTER 157                 |

PMC-Sierra, Inc.

| TABLE 23 - RCMP-200 ABSOLUTE MAXIMUM RATINGS 188                               |  |

|--------------------------------------------------------------------------------|--|

| TABLE 24 - RCMP-200 D.C. CHARACTERISTICS                                       |  |

| TABLE 25       - MICROPROCESSOR INTERFACE READ ACCESS (FIGURE 22)              |  |

| TABLE 26       - MICROPROCESSOR INTERFACE WRITE ACCESS (FIGURE 23)         194 |  |

| TABLE 27 - INPUT CELL INTERFACE (FIGURE 24 AND FIGURE 25) 197                  |  |

| TABLE 28       - OUTPUT CELL INTERFACE (FIGURE 26)                             |  |

| TABLE 29 - SYNCHRONOUS SRAM INTERFACE (FIGURE 27) 202                          |  |

| TABLE 30 - JTAG PORT INTERFACE (FIGURE 28)                                     |  |

DATASHEET PMC-960543

ISSUE 2

ROUTING CONTROL, MONITORING, & POLICING 200 MBPS

## 1 FEATURES

Monolithic single chip device which handles ATM switch Ingress VPI/VCI address translation, cell appending, cell rate policing, counting, and OAM requirements for 65,536 VCs (virtual circuits)

PMC PMC-Sierra, Inc.

- Instantaneous transfer rate of 200 Mbit/s supports a cell transfer rate of 0.355x10<sup>6</sup> cells/s (one STS-3c).

- Concentrates the traffic from several PHY interfaces into one switch port.

- 8 bit PHY interface using direct addressing for up to 4 PHYs (compatible with Utopia Level 1 cell-level handshake) and Multi-PHY addressing for up to 32 PHYs (Utopia Level 2 compatible).

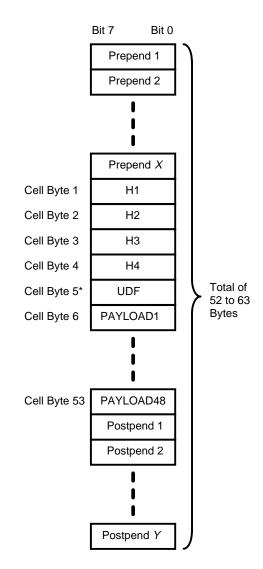

- 8 bit extended cell format SCI-PHY (52 64 byte extended ATM cell with prepend/postpend) interface at output to switch fabric.

- Compatible with wide range of switching fabrics and traffic management architectures including per VC or per PHY queuing.

- Provides identification/tagging of RM cells to support adjunct processing applications such as Virtual Source/Virtual Destination ABR service.

- Supports logical multicast.

- Flexible CAM-type cell identification which can use *arbitrary* VPI/VCI values and/or cell appended bytes for identification.

- Discards on command all low priority (high CLP bit) cells to relieve switch congestion.

- Can discard or tag the remainder of an AAL5 packet if a single cell in that packet is discarded or tagged due to policing.

- Includes a 16-bit FIFO buffered microprocessor bus interface for cell extraction and insertion (including OAM), VC table access, control and status monitoring, and configuration of the device.

- Supports DMA access for cell extraction and insertion.

ISSUE 2

ROUTING CONTROL, MONITORING, & POLICING 200 MBPS

• Uses common synchronous SRAMs for maintaining per-VC information.

PMC PMC-Sierra, Inc.

- Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board test purposes.

- Provides a generic 16-bit microprocessor bus interface for configuration, control and status monitoring.

- Low power, 0.6 micron, +5 Volt CMOS technology.

- 240 copper slugged plastic quad flat pack (PQFP) package.

#### Policing

- Policing is performed for adherence to peak cell rate (PCR), cell delay variation (CDV), sustained cell rate (SCR) and burst tolerance (BT). Violating cells can be noted, dropped or have CLP bits set to 1.

- Policing performed by an approximation to the Generic Cell Rate Algorithm (GCRA).

- Two policing instantiations available per VC. The policed cell streams can be any combination of user cells, OAM cells, Resource Management, high priority cells or low priority cells.

#### Cell Counting

- Counts maintained on a per VC basis include total low priority cells, total high priority cells and cells violating the traffic contract.

- Performance management counts are maintained for forward and reverse flows on a per VC basis: lost cells, misinserted cells, BIP-16 errors and the number of Severely Errored Cell Blocks (SECB).

- Counts maintained for entire device include total cells input, total cells output, OAM cells, cells discarded due to congestion, corrupted OAM cells, and cells with unassigned/invalid VPI/VCIs.

DATASHEET PMC-960543

ISSUE 2

ROUTING CONTROL, MONITORING, & POLICING 200 MBPS

## OAM Handling and Performance Monitoring

OAM performance monitoring for all VCs as described in ITU-T Recommendation I.610, Bellcore TR-NWT-001248 and Bellcore GR-1113-CORE.

PMC PMC-Sierra, Inc.

- Automatic OAM handling includes reception and generation of AIS, RDI, Forward Monitoring and Backward Reporting cells.

- Backward generated OAM cell identification/tagging provided to enable direct extraction by Egress device.

- Incoming OAM cells can be terminated or passed to the Output Cell Interface and/or microprocessor.

- Outgoing OAM cells sourced from automatic OAM generating circuitry, Input Cell Interface or microprocessor.

ISSUE 2

ROUTING CONTROL, MONITORING, & POLICING 200 MBPS

## 2 APPLICATIONS

- ATM Hubs and Workgroup Switches

- ATM Enterprise, Edge and Access Switches

DATASHEET PMC-960543

ISSUE 2

ROUTING CONTROL, MONITORING, & POLICING 200 MBPS

#### 3 REFERENCES

- ATM Forum ATM User-Network Interface Specification, V3.0, October, 1993

- ITU-T Recommendation I.361 "B-ISDN ATM Layer Specification", March 1993

PMC PMC-Sierra, Inc.

- ITU-T Recommendation I.371 "Traffic Control and Congestion Control in B-ISDN", March 1993

- ITU-T Recommendation I.610 "B-ISDN Operation and Maintenance Principles and Functions", Helsinki, March 1993.

- Bell Communications Research Broadband Switching System (BSS) Generic Requirements, GR-1110-CORE, Issue 1, September 1994.

- Bell Communications Research -Asynchronous Transfer Mode (ATM) and ATM Adaptation Layer (AAL) Protocols, GR-1113-CORE, Issue 1, July 1994.

- Bell Communications Research Generic Requirements for Operations of Broadband Switching Systems, TA-NWT-001248, Issue 2, October 1993.

- IEEE 1149.1 Standard Test Access Port and Boundary Scan Architecture, May 21, 1990.

- PMC-940212, ATM\_SCI\_PHY, "SATURN Compliant Interface For ATM Devices", July 1994, Issue 2.

- PMC-960338, "Asynchronous SRAM for RCMP-200", April 1996, Issue 1.

- ATM Forum/95-0013R9, Draft Version 3.0 of ATM Forum Traffic Management Specification Version 4.0, October, 1995

DATASHEET PMC-960543

ISSUE 2

ROUTING CONTROL, MONITORING, & POLICING 200 MBPS

#### 4 APPLICATION EXAMPLES

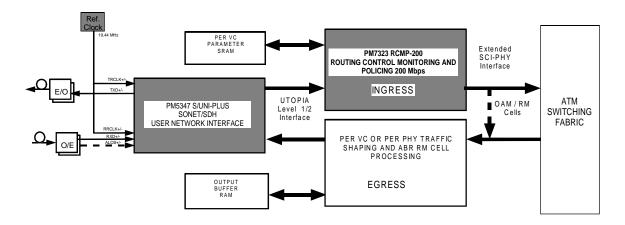

The RCMP-200 device is combined with up to 32 PHY devices to implement the ingress direction an ATM switch port. Two ATM switch port applications are shown in Figure 1 and Figure 2.

PMC PMC-Sierra, Inc.

The RCMP-200 device accepts standard 53 byte cells through a SCI-PHY interface and outputs cells with variable length pre-pends or post-pends through an extended cell format SCI-PHY interface. The appendages added by the RCMP-200 are used by the switch for routing. The HEC can optionally be omitted. The combined pre-pend and post-pend length can vary from 0 to 10 bytes, with the cells correspondingly being 52 to 63 octets or 26 to 32 words.

Backward generated OAM cells and Resource Management cells are specially labelled by overwriting an appended byte to allow these cells to be processed and routed in the reverse direction.

The RCMP-200 utilizes external synchronous RAMs to store VPI/VCI translation tables and per VPI/VCI switch-specific routing appendages, as well as per VPI/VCI policing and performance monitoring information. All of this information is stored in a single structure called the *VC table*.

#### Figure 1 - OC-3 Switch Port Application

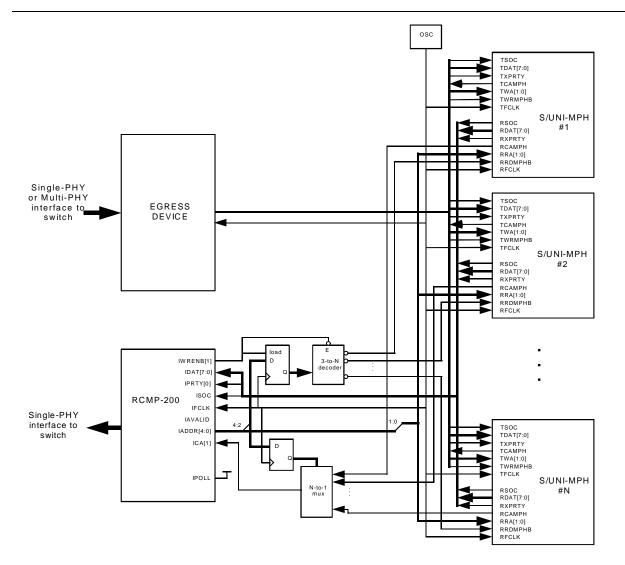

# Figure 2 - DS-1 PHY Addressing Application

PMC-Sierra, Inc.

STANDARD PRODUCT

DATASHEET PMC-960543

ISSUE 2

ROUTING CONTROL, MONITORING, & POLICING 200 MBPS

Figure 2 illustrates how up to 32 PHY Utopia Level 1 entities may be interfaced to an RCMP-200. With a minimum amount of support circuitry (eg. a single PAL), the PHY addressing mode of operation polls the PHY devices to determine the next cell for transfer. In this example, a quad DS-1 ATM device, the S/UNI-MPH (PM7344), provides the PHY transmission convergence function. Eight S/UNI-MPH devices would be required to provide 32 DS-1 ports.

The S/UNI-MPH supports PHY address polling by sampling the two least significant address bits (RRA[1:0] and TWA[1:0]) and generating the cell available status for the selected PHY entity. It also holds the last state of

ISSUE 2

ROUTING CONTROL, MONITORING, & POLICING 200 MBPS

RRA[1:0] and TWA[1:0] before the assertion of RRDMPHB and TWRMPHB, respectively, thus latching the PHY address resolved by the polling process. The only support logic is that required to select between the S/UNI-MPH devices.

PMC PMC-Sierra, Inc.

The IAVALID output is not required for this application.

In this application, the aggregate throughput is less than 6.144 Mbyte/s with 32 DS-1 ports; therefore, the clock oscillator frequency can be as low as 6.5 MHz. To lower system cost further, asynchronous SRAM's may also be used in this application with the addition of external circuitry. Refer to the application note PMC-960308 "Asynchronous SRAM for RCMP-200" for a detailed description.

DATASHEET PMC-960543

ISSUE 2

ROUTING CONTROL, MONITORING, & POLICING 200 MBPS

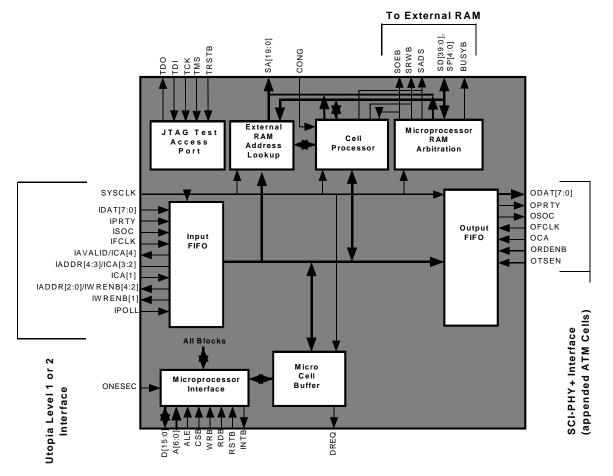

#### 5 BLOCK DIAGRAM

DATASHEET PMC-960543 PMC PMC-Sierra, Inc.

ISSUE 2

ROUTING CONTROL, MONITORING, & POLICING 200 MBPS

#### 6 DESCRIPTION

The PM7322 Routing Control, Monitoring and Policing 200 Mbps (RCMP-200) device is a monolithic integrated circuit that implements ATM layer functions that include fault and performance monitoring, header translation and cell rate policing. The RCMP-200 is intended to be situated between a switch core and the physical layer devices in the ingress direction. The RCMP-200 supports a sustained aggregate throughput of 0.355x10<sup>6</sup> cells/s. The RCMP-200 uses external SRAM to store per-VPI/VCI data structures. The device is capable of supporting up to 65536 connections.

The Input Cell Interface can be connected to up to 32 physical layer devices through a SCI-PHY compatible bus. The 53 byte ATM cell is encapsulated in a data structure which can contain pre-pended or post-pended routing information. Received cells are buffered in a four cell deep FIFO. All Physical Layer and unassigned cells are discarded. For the remaining cells, a subset of ATM header and appended bits is used as a search key to find the VC Table Record for the virtual connection. If a connection is not provisioned and the search terminates unsuccessfully as a result, the cell is discarded and a count of invalid cells is incremented. If the search is successful, subsequent processing of the cell is dependent on contents of the cell and configuration fields in the VC Table Record.

The RCMP-200 performs header translation if so configured. The ATM header is replaced by contents of fields in the VC Table Record for the connection. The VCI contents are passed through transparently for VPCs. Appended bytes can be replaced, added or removed.

If the RCMP-200 is the end point for a F4 or F5 OAM stream, the OAM cells are dropped and processed. If the RCMP-200 is not the end point, the OAM cells are passed to the Output Cell Interface with an optional copy passed to the Microprocessor Cell Buffer. The reception of an AIS or RDI cell results in the appropriate alarm. Upon the arrival of a Forward Monitoring or Monitoring/Reporting cell, error counts are updated and a Backward Reporting cell is optionally generated. Activate/Deactivate cells are passed to the Microprocessor Cell Buffer for external processing. Continuity Check cells can be generated if no user cells have been received in the latest 1.5 +/- 0.5 or 2.5 +/- 0.5 (default) seconds.

ISSUE 2

ROUTING CONTROL, MONITORING, & POLICING 200 MBPS

Cell rate policing is supported through two instances of the Generic Cell Rate Algorithm (GCRA) for each connection. Each cell that violates the traffic contract can be tagged (CLP bit set high) or discarded. To allow full flexibility, each GCRA instance can be programmed to police any combination of user cells, OAM cells, Resource Management, high priority cells or low priority cells.

PMC PMC-Sierra, Inc.

The RCMP-200 supports multicasting. A single received cell can result in an arbitrary number of cells presented on the Output Cell Interface, each with its own unique VPI/VCI value and appended bytes. The ATM cell payload is duplicated without modification.

The Output Cell Interface can be connected to the switch core through an extended cell format SCI-PHY compatible bus. Cells are stored in a four cell deep FIFO until the downstream devices are ready to accept them. The details of how cells are handled in this FIFO depends on the particular application of the RCMP-200 and are presented in "Operational Modes" section.

The Microprocessor Interface is provided for device configuration, control and monitoring by an external microprocessor. This interface provides access to the external SRAM to allow creation of the data structure, configuration of individual connections and monitoring of the connections. The Microprocessor Cell Buffer gives access to the cell stream, either directly or through intervention by a DMA controller. Programmed cell types can be routed to a microprocessor readable sixteen cell FIFO. The microprocessor can send cells over the Output Cell Interface.

The RCMP-200 is implemented in low power, 0.6 micron, +5 Volt CMOS technology. It has TTL compatible inputs and outputs and is packaged in a 240 pin copper slugged plastic QFP package.

DATASHEET PMC-960543

ISSUE 2

ROUTING CONTROL, MONITORING, & POLICING 200 MBPS

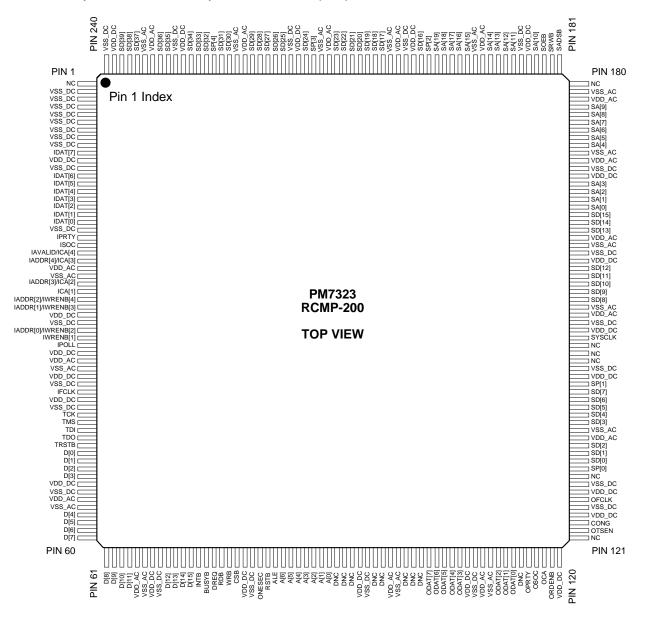

### 7 PIN DIAGRAM

The RCMP-200 is packaged in a 240 pin slugged plastic QFP package having a body size of 32 mm by 32 mm and a pin pitch of 0.5 mm.

PMC PMC-Sierra, Inc.

PMC-Sierra, Inc.

ISSUE 2

ROUTING CONTROL, MONITORING, & POLICING 200 MBPS

# 8 PIN DESCRIPTION (TOTAL 240)

#### Table 1 - Output Cell Interface Signals (24)

| Pin Name                                            | Туре              | Pin<br>No.                                                                                                                                                           | Feature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OFCLK                                               | Input             | 126                                                                                                                                                                  | The output FIFO clock (OFCLK) is used to read<br>words from the Output Cell Interface. OFCLK<br>must cycle at a 25 MHz or lower instantaneous<br>rate, but at a high enough rate to avoid FIFO<br>overflow. OSOC, OCA, OPRTY and ODAT[7:0]<br>are updated on the rising edge of OFCLK.<br>ORDENB is sampled using the rising edge of<br>OFCLK.                                                                                                                                                                                                                                        |

| ORDENB                                              | Input             | 119                                                                                                                                                                  | The active low read enable (ORDENB) signal is<br>used to indicate transfers from the Output Cell<br>Interface. When ORDENB is sampled low using<br>the rising edge of OFCLK, a word is read from<br>the internal synchronous FIFO and output on bus<br>ODAT[7:0]. When ORDENB is sampled high<br>using the rising edge of OFCLK, no read is<br>performed and outputs ODAT[7:0], OPRTY and<br>OSOC are tristated if the OTSEN input is high.<br>ORDENB must operate in conjunction with<br>OFCLK to access the FIFO at a high enough<br>instantaneous rate as to avoid FIFO overflows. |

| ODAT[0]<br>ODAT[1]<br>ODAT[2]<br>ODAT[3]<br>ODAT[4] | Tristate          | 114<br>113<br>112<br>107<br>106                                                                                                                                      | The output cell data (ODAT[7:0]) bus carries the ATM cell octets that are read from the output FIFO. If the IBUS8 input is high, only ODAT[7:0] carries cell octets. The ODAT[7:0] bus is updated on the rising edge of OFCLK.                                                                                                                                                                                                                                                                                                                                                        |

| ODAT[5]<br>ODAT[6]<br>ODAT[7]                       | 105<br>104<br>103 | When the Output Cell Interface is configured for tristate operation using the OTSEN input, tristating of the ODAT[7:0] output bus is controlled by the ORDENB input. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                     |                   |                                                                                                                                                                      | When OTSEN is low, the ODAT[7:0] bus is low when no cell is being transferred.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

PMC-Sierra, Inc.

DATASHEET PMC-960543

ISSUE 2

| Pin Name | Туре     | Pin<br>No. | Feature                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPRTY    | Tristate | 116        | The output parity (OPRTY) signals indicate the parity of the ODAT[7:0] bus. Odd or even parity selection can be made using a register bit. OPRTY is updated on the rising edge of OFCLK.                                                                                                                                                                                                                                                   |

|          |          |            | When the Output Cell Interface is configured for tristate operation using the OTSEN input, tristating of the OPRTY output bus is controlled by the ORDENB input.                                                                                                                                                                                                                                                                           |

| OSOC     | Tristate | 117        | The output start of cell (OSOC) signal marks the start of cell on the ODAT[7:0] bus. When OSOC is high, the first word of the cell structure is present on the ODAT[7:0] stream. OSOC is updated on the rising edge of OFCLK.                                                                                                                                                                                                              |

|          |          |            | When the Output Cell Interface is configured for tristate operation using the OTSEN input, tristating of the OSOC output is controlled by the ORDENB input.                                                                                                                                                                                                                                                                                |

| OCA      | Output   | 118        | The active polarity of this signal is programmable and defaults to active high.                                                                                                                                                                                                                                                                                                                                                            |

|          |          |            | OCA indicates when a cell is available in the<br>output FIFO. When asserted, the OCA signal<br>indicates that the output FIFO has at least one<br>cell available to be read. The OCA signal is<br>deasserted when the output FIFO contains four<br>or zero words available for the current cell.<br>Selection is made using the OCALEVEL0 bit in<br>the Output FIFO Configuration register. OCA is<br>updated on the rising edge of OFCLK. |

| OTSEN    | Input    | 122        | The tristate enable (OTSEN) signal allows tristate<br>control over the ODAT[7:0], OPRTY and OSOC<br>outputs. When OTSEN is high, the active low<br>read enable input, ORDENB, controls when the<br>ODAT[7:0], OPRTY and OSOC outputs are<br>driven. When OTSEN is low, the ODAT[7:0],<br>OPRTY and OSOC outputs are always driven.                                                                                                         |

ISSUE 2

ROUTING CONTROL, MONITORING, & POLICING 200 MBPS

| Pin Name | Туре | Pin<br>No. | Feature |

|----------|------|------------|---------|

|          |      |            |         |

PMC-Sierra, Inc.

### Table 2 - Input Cell Interface Signals (30)

| Pin Name | Туре  | Pin<br>No. | Feature                                                                                                                                                                                                                                                                                                                      |

|----------|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IFCLK    | Input | 41         | The input FIFO clock (IFCLK) is used to write<br>words to the synchronous FIFO interface.<br>IFCLK must cycle at a 25 MHz or lower<br>instantaneous rate. ISOC, ICA[4:1], IPRTY and<br>IDAT[7:0] are sampled on the rising edge of<br>IFCLK. IWRENB[4:1], IADDR[4:0] and IAVALID<br>are updated on the rising edge of IFCLK. |

| IPOLL    | Input | 35         | The input polling select (IPOLL) pin determines the method used to poll PHY devices.                                                                                                                                                                                                                                         |

|          |       |            | If IPOLL is low, the IWRENB[4:1] and ICA[4:1] signals are connected directly to up to four single-PHY entities.                                                                                                                                                                                                              |

|          |       |            | If IPOLL is high, polling using address lines is<br>used. The RCMP-200 uses the IADDR[4:0] and<br>IAVALID outputs to perform sequential polling of<br>the PHY devices to determine the next cell to<br>transfer.                                                                                                             |

PMC-Sierra, Inc.

ISSUE 2

| Pin Name                                     | Туре                           | Pin<br>No.                  | Feature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------|--------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IWRENB[1]<br>IWRENB[2]<br>IWRENB[3]          | Output                         | Output 34<br>33<br>30<br>29 | The active low write enable (IWRENB[4:1]) inputs are used to initiate writes to the input FIFO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| IWRENB[4]                                    |                                |                             | If the IPOLL input is low, the RCMP-200 asserts<br>one of the IWRENB[4:1] outputs to transfer a<br>cell from one of up to four PHY devices. A valid<br>word is expected on the IDAT[7:0] bus at the<br>second rising edge of IFCLK after one of the<br>enables is asserted low. When all of the enables<br>are high, no valid data is expected. The<br>IWRENB[4:1] outputs are updated on the rising<br>edge of IFCLK. See Figure 7.                                                                                                                                                                                                                                                      |

|                                              |                                |                             | If the IPOLL input is high, the IWRENB[4:2] pins<br>are redefined as IADDR[2:0]. The IWRENB[1]<br>pin is used to transfer all cells. The source PHY<br>is selected by the IADDR[4:0] signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| IADDR[4]<br>IADDR[3]<br>IADDR[2]<br>IADDR[1] | I/O 24<br>27<br>29<br>30<br>33 | 27<br>29                    | If the IPOLL input is high, the IADDR[4:0] pins<br>are used for PHY addressing. If the IPOLL input<br>is low, the IADDR[4:0] pins are redefined as<br>ICA[3:2] and IWRENB[4:2].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| IADDR[0]                                     |                                | 33                          | If the IPOLL input is high, the IADDR[4:0]<br>signals are outputs and are used to address up<br>to 32 PHY devices for the purposes of polling<br>and selection for cell transfer. When conducting<br>polling, in order to avoid bus contention, the<br>RCMP-200 inserts gap cycles during which<br>IADDR[4:0] is set to 1F hex and IAVALID to logic<br>0. When this occurs, no PHY device should<br>drive ICA[1] during the following clock cycle.<br>Polling is performed in a incrementing sequential<br>order. The PHY device selected for transfer is<br>based on the IADDR[4:0] value present when<br>IWRENB[1] falls. The IADDR[4:0] bus is<br>updated on the rising edge of IFCLK. |

PMC-Sierra, Inc.

DATASHEET PMC-960543

ISSUE 2

| Pin Name                                                                             | Туре  | Pin<br>No.                                   | Feature                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------|-------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IAVALID                                                                              | I/O   | 23                                           | If the IPOLL input is high, the PHY Address<br>Valid (IAVALID) pin is active. If the IPOLL input<br>is low, the IAVALID pin is redefined as ICA[4].                                                                                                                                                                                                                              |

|                                                                                      |       |                                              | If the IPOLL input is high, the IAVALID pin<br>indicates that the IADDR[4:0] bus is outputting a<br>valid PHY address for polling purposes. When<br>this signal is deasserted, the IADDR[4:0] bus is<br>set to 1F hex.                                                                                                                                                           |

|                                                                                      |       |                                              | IAVALID is not necessary when less than 32<br>PHY links are being polled.                                                                                                                                                                                                                                                                                                        |

| IDAT[0]<br>IDAT[1]<br>IDAT[2]<br>IDAT[3]<br>IDAT[4]<br>IDAT[5]<br>IDAT[6]<br>IDAT[7] | Input | 19<br>18<br>17<br>16<br>15<br>14<br>13<br>10 | The input cell data (IDAT[7:0]) bus carries the<br>ATM cell octets that are written to the input<br>FIFO. The IDAT[7:0] bus is sampled on the<br>rising edge of IFCLK and is considered valid<br>only when one of the IWRENB[4:1] signals so<br>indicates.                                                                                                                       |

| IPRTY                                                                                | Input | 21                                           | The input parity (IPRTY) signals indicate the<br>parity of the IDAT[7:0] bus. Odd or even parity<br>selection can be made using a register. A<br>maskable interrupt status is generated upon a<br>parity error; no other actions are taken. IPRTY<br>is sampled on the rising edge of IFCLK and is<br>considered valid only when one of the<br>IWRENB[4:1] signals so indicates. |

PMC-Sierra, Inc.

DATASHEET PMC-960543

ISSUE 2

| Pin Name | Туре  | Pin<br>No. | Feature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISOC     | Input | 22         | The input start of cell (ISOC) signal marks the<br>start of cell on the IDAT[7:0] bus. When ISOC is<br>high, the first word of the cell structure is present<br>on the IDAT[7:0] stream. It is not necessary for<br>ISOC asserted for each cell. An interrupt may<br>be generated if ISOC is high during any word<br>other than the first word of the cell structure.<br>ISOC is sampled on the rising edge of IFCLK<br>and is considered valid only when one of the<br>IWRENB[4:1] signals so indicates. |

PMC-Sierra, Inc.

ISSUE 2

ROUTING CONTROL, MONITORING, & POLICING 200 MBPS

| Pin Name         | Туре | Pin<br>No. | Feature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ICA[1]<br>ICA[2] | I/O  | 28<br>27   | The active polarity of these signals is programmable and defaults to active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ICA[3]<br>ICA[4] |      | 24<br>23   | If the IPOLL input is low, the RCMP-200 asserts<br>the appropriate IWRENB[4:1] signal in response<br>to a round-robin polling of the ICA[4:1] signals.<br>Once committed, the RCMP-200 will transfer an<br>entire cell from a single physical link before<br>servicing the next. The RCMP-200 will complete<br>the read of an entire cell even if the associated<br>ICA[4:1] input is deasserted during the cell.<br>Sampling of ICA[4:1] resumes the cycle after the<br>last octet of a cell has been transferred.                                                                                                                                                                                               |

|                  |      |            | Note that ICA[1] is an input only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                  |      |            | If the IPOLL input is high, the ICA[3:2] pins are redefined as IADDR[4:3] and the ICA[4] pin is redefined as IAVALID.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                  |      |            | If the IPOLL input is high, the RCMP-200 polls<br>up to 32 PHY devices using the PHY address<br>signals IADDR[4:0]. A PHY device being<br>addressed by IADDR[4:0] is expected to indicate<br>whether or not it has a complete cell available<br>for transfer by driving ICA[1] during the clock<br>cycle following that in which it is addressed.<br>(When a cell transfer is in progress, the RCMP-<br>200 will not poll the PHY device which is<br>sending the cell and so PHY devices need not<br>support cell availability indication during cell<br>transfer.) The selection of a particular PHY<br>device from which to transfer a cell is indicated<br>by the state of IADDR[4:0] when IWRENB[1]<br>falls. |

|                  |      |            | Note that ICA[1] is an input only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

DATASHEET PMC-960543

ISSUE 2

ROUTING CONTROL, MONITORING, & POLICING 200 MBPS