## FULL SPEED USB INTEGRATED MICROCONTROLLER

# W81E381D/W81E381AD Full Speed USB Integrated Microcontroller

#### W81E381D/AD Data Sheet Revision History

|    | Pages                                         | Dates   | Version | Version on Web | Main Contents                                                                                                                            |

|----|-----------------------------------------------|---------|---------|----------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | n.a.                                          | 03/2001 | 0.50    | n.a.           | First published                                                                                                                          |

| 2  | P.9, P.11, P.14,<br>P.35, P.36, P.47,<br>P.48 | 09/2001 | 0.51    | n.a.           | Modify pin function of SCIO & SCCLK     Revise register description of SCCR (AC) and SCECR (AD)     Revise the USB register descriptions |

| 3  | P.14, P.53, P.54                              | 01/2002 | 0.52    | n.a.           | Revise register description of CHPCON (CF)     Modify the description of SFRCN & CHPCON                                                  |

| 4  |                                               |         |         |                |                                                                                                                                          |

| 5  |                                               |         |         |                |                                                                                                                                          |

| 6  |                                               |         |         |                |                                                                                                                                          |

| 7  |                                               |         |         |                |                                                                                                                                          |

| 8  |                                               |         |         |                |                                                                                                                                          |

| 9  |                                               |         |         |                |                                                                                                                                          |

| 10 |                                               |         |         |                |                                                                                                                                          |

Please note that all data and specifications are subject to change without notice. All the trademarks of products and companies mentioned in this datasheet belong to their respective owners.

#### **LIFE SUPPORT APPLICATIONS**

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Winbond customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Winbond for any damages resulting from such improper use or sales.

## **TABLE OF CONTENTS**

| !. General 1 | Descriptions:                                            | 5  |

|--------------|----------------------------------------------------------|----|

| . FEATUR     | ?ES:                                                     | 6  |

| 3. PIn confi | guration                                                 | 7  |

| 3.1 W81E     | E381D 48-pin LQFP PINOUT                                 | 7  |

|              | E381AD 100-pin LQFP PINOUT                               |    |

|              | ning interface                                           |    |

| _            | ter map                                                  |    |

| Ü            | SH Category – Descriptions Summary                       |    |

|              | ategory - Descriptions Summary                           |    |

|              |                                                          |    |

|              | Category - Descriptions Summary                          |    |

| 4.5 Indiv    | idual register description                               | 16 |

| 4.5.1        | Register Descriptions - USB Power Control Registers (E7) | 16 |

| 4.5.2        | Register Descriptions - USB Interrupt System SFRs (A2)   | 18 |

| 4.5.3        | Register Descriptions - USB Interrupt System SFRs (C0)   | 19 |

| 4.5.4        | Register Descriptions - USB Interrupt System SFRs (B1)   |    |

| 4.5.4        | Register Descriptions - USB Interrupt System SFRs (B1)   | 20 |

| 4.5.5        | Register Descriptions - USB Function SFRs (E1)           | 21 |

| 4.5.6        | Register Descriptions - USB Function SFRs (F1)           | 23 |

| 4.5.7        | Register Descriptions - USB Function SFRs (8F)           | 24 |

| 4.5.8        | Register Descriptions - USB Function SFRs (E6)           | 26 |

| 4.5.9        | Register Descriptions - USB Function SFRs (E4)           |    |

| 4.5.10       | Register Descriptions - USB Function SFRs (E3)           | 28 |

| 4.5.11       | Register Descriptions - USB Function SFRs (E5)           |    |

| 4.5.12       | Register Descriptions - USB Function SFRs (E2)           |    |

| 4.5.13       | Register Descriptions - USB Function SFRs (F6)           |    |

| 4.5.14       | Register Descriptions - USB Function SFRs (F4)           |    |

| 4.5.15       | Register Descriptions - USB Function SFRs (F3)           |    |

| 4.5.16       | Register Descriptions - USB Function SFRs (F5)           |    |

| 4.5.17       | Register Descriptions - USB Function SFRs (F2)           |    |

| 4.5.18       | Register Descriptions - USB Device SFRs (B7)             |    |

| 4.5.19       | Register Descriptions - USB Device SFRs (BF)             |    |

| 4.5.20       | Register Descriptions - SC Interrupt SFRs (AA)           |    |

| 4.5.21       | Register Descriptions - SC Interrupt SFRs (AB)           |    |

| 4.5.22       | Register Descriptions - SC Control SFRs (A3)             |    |

| 4.5.24       | Register Descriptions - SC Control SFRs (AC)             |    |

| 4.5.25       | Register Descriptions - SC Control SFRs (AD)             |    |

| 4.5.26       | Register Descriptions - SC Control SFRs (AE, A4)         |    |

| 4.5.27       | Register Descriptions - SC Control SFRs (A5)             |    |

| 4.5.28       | Register Descriptions - SC Data SFRs (A6, A7)            |    |

| 4.5.29       | Register Descriptions – ISP Registers (C4, C5)           |    |

| 4.5.30       | Register Descriptions – ISP Registers (C6, C7)           | 53 |

- 3 -

| 4.5.31        | Register Descriptions – uC Control Registers (CF)      | 54 |

|---------------|--------------------------------------------------------|----|

| 4.5.32        |                                                        |    |

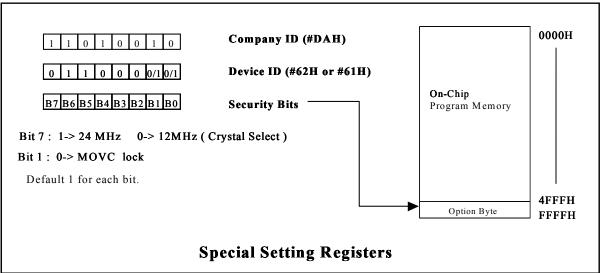

| 4.6 MTP-      | ROM PROGRAMMING                                        | 56 |

| 5. Security   |                                                        | 57 |

| 6. Electrical | Characteristics                                        | 58 |

| 7. Mechanic   | cal information                                        | 59 |

| 7.1 W81E      | 2381D 48 LQFP (7x7x1.4mm footprint 2.0mm) PACKAGE      | 59 |

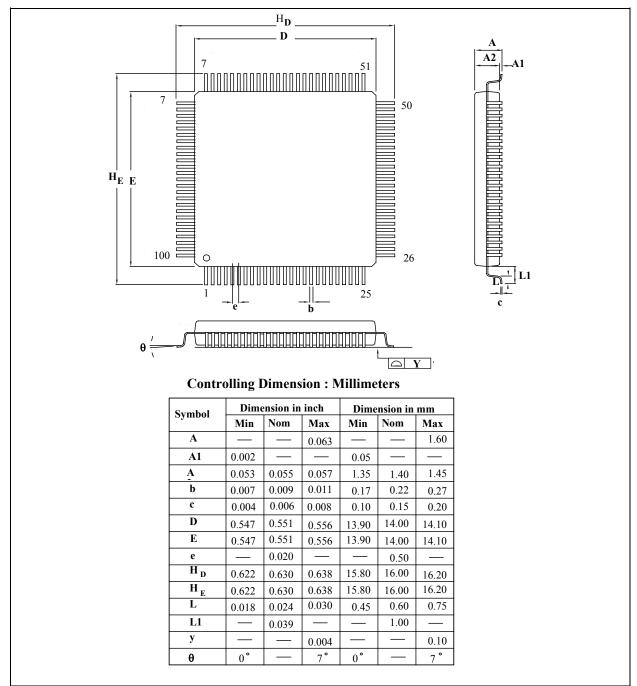

| 7.2 W81E      | C381AD 100 LQFP (14x14x1.4 mm footprint 2.0mm) PACKAGE | 60 |

| 8. TYPICAL    | APPLICATION                                            | 61 |

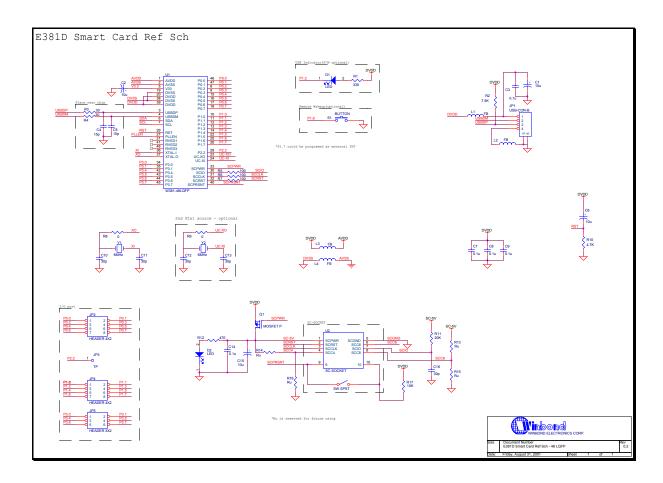

| 8.1 W81E      | E381D reference schematic                              | 61 |

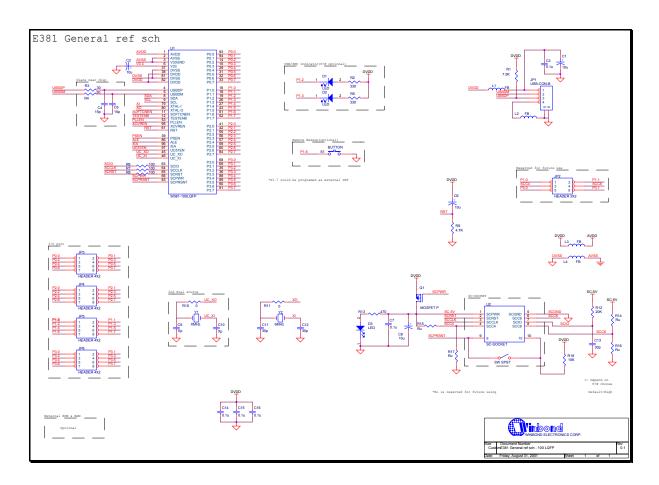

| 8.2 W81E      | E381AD reference schematic                             | 62 |

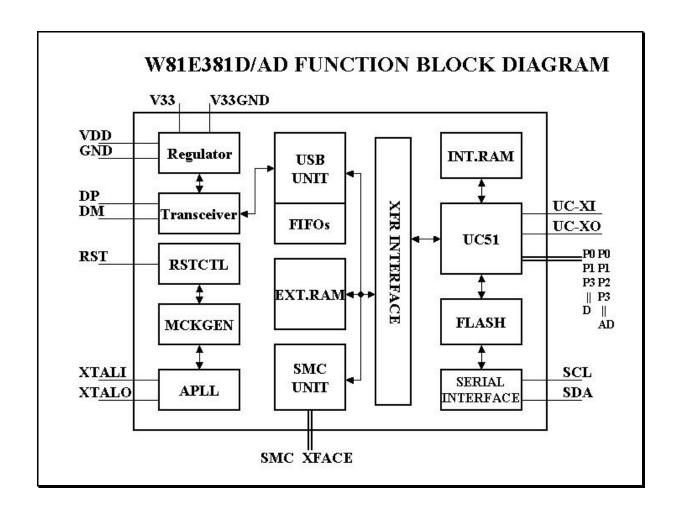

#### 1. GENERAL DESCRIPTIONS:

The W81E381 is 8052-based USB device with 20 Kbytes flash memory. By integrating the USB1.1 transceiver, SIE, enhanced 8032 code, 20K Flash memory, extra 256 Byte RAM, power regulator, and general purpose I/O in single chip, W81E381D/W81E381AD creates a very low cost-effective solution that provides superior time-to-market advantages. The GPIO provides an easy interface to popular interface, such as ATAPI, EPP, RS232, MCU and DSP interface.

#### 2. FEATURES:

- Fully compliant with the Universal Serial Bus Specification version 1.1.

- Support USB Suspend and Resume operation for power-down standby.

- Support USB remote wake up function.

- Embedded microprocessor--8052 with extra 256Bytes RAM for data processing/storage, 20

Kbytes of In-System Programmable Flash memory.

- Internal generated 12MHz clock for 8052 use (the same as standard 8052 uses 24 MHz clock outside)

- External and separated 8052 clock input supported

- 6 clock per instruction 8052 core

- Flash support 512Byte erase block

- Software setting, 2KByte block programmable write protection for Flash memory

- 6-Mhz crystal/oscillator input for both Full speed application with limited EMI affection

- Support smart card interface, including serial interface memory card, and SCIO & SCCLK pins could be programmed as GPIO pins by registers setting

- Built-in 3.3V power regulator for single 5V power operation

- Internal PLL for USB and SC requirements

- Support one Control endpoint for command (8 bytes), and four endpoints 1, 2, 3, 4 (Bulk In, Bulk Out Interrupt In, and Interrupt Out) for data.

- BulkIn, BulkOut with 16 bytes FIFO

- InterruptIn, InterruptOut with 8 bytes FIFO

- W81E381D: 48LQFP package

- W81E381AD: 100LQFP package

#### **Ordering Information**

| Part Number | Package Type | Production Flow          |

|-------------|--------------|--------------------------|

| W81E381D    | 48-PIN LQFP  | Commercial, 0°C to +70°C |

| W81E381AD   | 100-PIN LQFP | Commercial, 0°C to +70°C |

#### 3. PIN CONFIGURATION

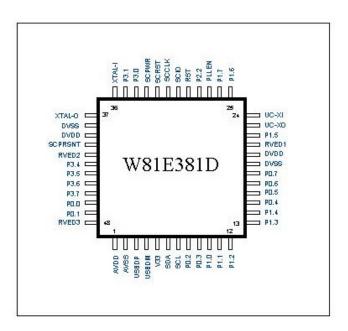

#### 3.1 W81E381D 48-pin LQFP PINOUT

## 3.1.1 48- pin LQFP package description

| A          |       |                          |                                                                                                                                                                               |  |  |  |  |  |

|------------|-------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SYMBOL     | TYPE  | PIN NO                   | DESCRIPTIONS                                                                                                                                                                  |  |  |  |  |  |

| USB Pins   |       |                          |                                                                                                                                                                               |  |  |  |  |  |

| AVdd       | PWR   | 1                        | Analog 5V power supply                                                                                                                                                        |  |  |  |  |  |

| AVss       | PWR   | 2                        | Analog 5V power ground                                                                                                                                                        |  |  |  |  |  |

| V33        | PWR   | 5                        | USB DC power 3.3V output.                                                                                                                                                     |  |  |  |  |  |

| D+         | I/O   | 3                        | USB signal (+)                                                                                                                                                                |  |  |  |  |  |

| D-         | I/O   | 4                        | USB signal (-)                                                                                                                                                                |  |  |  |  |  |

| XTALI      | I     | 36                       | Crystal input. Use 6M Hz crystal. A 6 MHz clock source may also be used.                                                                                                      |  |  |  |  |  |

| XTALO      | 0     | 37                       | Crystal output.                                                                                                                                                               |  |  |  |  |  |

| Extra Pins |       |                          |                                                                                                                                                                               |  |  |  |  |  |

| PLLEN      | I     | 27                       | PLL enable pin; Schmitt-trigger pull up input                                                                                                                                 |  |  |  |  |  |

| uC Pins    |       |                          |                                                                                                                                                                               |  |  |  |  |  |

| RVED1-3    | X     | 21,41,                   | Reserved pins. Leave these pins floating.                                                                                                                                     |  |  |  |  |  |

|            |       | 48                       |                                                                                                                                                                               |  |  |  |  |  |

| RST        | I L   | 29                       | RESET: A high on this pin for two machine cycles while the oscillator is running resets the device.                                                                           |  |  |  |  |  |

| P0.0-P0.7  | I/O D | 46,47,<br>8,9,<br>15,16, | PORT 0: Function is the same as that of the standard 8052.                                                                                                                    |  |  |  |  |  |

| P1.0       | I/O   | 17,18<br>10              | It is a high drive I/O pad. Used as a GPIO pin for memory-type SC                                                                                                             |  |  |  |  |  |

| P1.1       | 1/0   | 11                       | It is a high drive I/O pad. Used as a GPIO pin for memory-type SC                                                                                                             |  |  |  |  |  |

| P1.2       | I/O   | 12                       | Used as a GPIO pin for memory-type SC                                                                                                                                         |  |  |  |  |  |

| P1.3       | I/O   | 13                       | Used as a GPIO pin for memory-type SC                                                                                                                                         |  |  |  |  |  |

| P1.4       | I/O   | 14                       | Used as a GPIO pin for memory-type SC                                                                                                                                         |  |  |  |  |  |

| P1.5       | I/O   | 22                       | Used as a GPIO pin for memory-type SC                                                                                                                                         |  |  |  |  |  |

|            |       | 25                       |                                                                                                                                                                               |  |  |  |  |  |

| P1.6       | 1/0   |                          | GPIO & remote wakeup pin                                                                                                                                                      |  |  |  |  |  |

| P1.7       | I/O   | 26                       | GPIO & external interrupt pin                                                                                                                                                 |  |  |  |  |  |

| P2.2       | I/O H | 28                       | It's a bi-directional I/O port with internal pull-ups. It can be programmed to be an output-latched port like an on-chip 74373, or a buffer input port like an on-chip 74244. |  |  |  |  |  |

#### 3.1.1 48-PIN LQFP package DESCRIPTION, continued

| SYMBOL         | TYPE     | PIN NO | DESCRIPTIONS                                               |

|----------------|----------|--------|------------------------------------------------------------|

| P3.0-P3.1      | I/O H    | 34,35  | PORT 3: Function is the same as that of the standard 8052. |

| P3.4-P3.7      | I/O H    | , ,    | PORT 3: Function is the same as that of the standard 8052. |

|                |          | 44,45  |                                                            |

| UC-XI          | I        | 24     | uC Crystal input.                                          |

| UC-XO          | 0        | 23     | uC Crystal output.                                         |

| Power Pins     |          |        |                                                            |

| Vss            | PWR      | 19,38  | GROUND: ground potential.                                  |

| Vdd            | PWR      | 20,39  | POWER SUPPLY: Supply voltage for operation.                |

| Serial Interfa | ce       |        |                                                            |

| SDA            | I/O      | 6      | Data input/output of serial interface                      |

| SCL            | I        | 7      | Clock input of serial interface                            |

| Smart Card F   | Reader F | Pins   |                                                            |

| SCPWR          | 0        | 33     | Smart card power supplier enable pin                       |

| SCIO           | I/O      | 30     | Smart card serial data input/output pin or GPIO pin        |

| SCCLK          | O (I/O)  | 31     | Smart card clock output (default 3M Hz) or GPIO pin        |

| SCRST          | 0        | 32     | Smart card reset signal                                    |

| SCPRSNT        | I        | 40     | Smart card existed indicator. Schmitt-trigger input        |

\*Note: TYPE I: input, O: output, I/O: bi-directional, H: pull-high, L: pull-low, D: open drain, PWR: Power pins, X: Floating

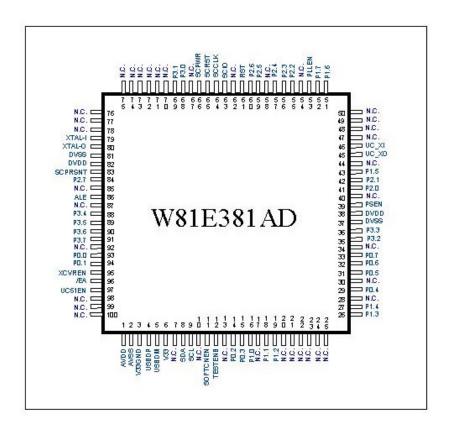

#### 3.2 W81E381AD 100-pin LQFP PINOUT

#### 3.2.1 100-pin LQFP package description

| AVDD         PWR         1         Analog 5V power supply           AVSS         PWR         2, 3         Analog 5V power ground           V33         PWR         6         USB DC power 3.3V output.           D+         I/O         4         USB signal (+)           D-         I/O         5         USB signal (-)           XTALI         I         79         Crystal input. Use 6MHz crystal. A 6MHz clock source may also be used.           XTALO         O         80         Crystal output.           Smart Card Reader Pins         SCPWR         O         66         Smart card power supplier enable pin           SCIO         I/O         63         Smart card serial data input/output pin or GPIO pin           SCCLK         O (I/O)         64         Smart card clock output (default 3MHz) or GPIO pin           SCRST         O         65         Smart card reset signal           SCPRSNT         I         83         Smart card existed indicator. Schmitt-trigger input           Extra Pins         FLL enable pin; Schmitt-trigger pull up input           XCVREN         I         95         XCVR enable pin; Schmitt-trigger pull up input           XCVREN         I         11         Software connection enable pin; Schmitt-trigger pull up input | 3.2.1 100-pi   |          |        |                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------|--------|------------------------------------------------------------------------|

| AVDD         PWR         1         Analog 5V power supply           AVSS         PWR         2, 3         Analog 5V power ground           V33         PWR         6         USB DC power 3.3V output.           D+         I/O         4         USB signal (+)           D-         I/O         5         USB signal (-)           XTALI         I         79         Crystal input. Use 6MHz crystal. A 6MHz clock source may also be used.           XTALO         O         80         Crystal output.           Smart Card Reader Pins         SCPWR         O         66         Smart card power supplier enable pin           SCIO         I/O         63         Smart card serial data input/output pin or GPIO pin           SCCLK         O (I/O)         64         Smart card clock output (default 3MHz) or GPIO pin           SCRST         O         65         Smart card reset signal           SCPRSNT         I         83         Smart card existed indicator. Schmitt-trigger input           Extra Pins         FLL enable pin; Schmitt-trigger pull up input           XCVREN         I         95         XCVR enable pin; Schmitt-trigger pull up input           XCVREN         I         11         Software connection enable pin; Schmitt-trigger pull up input | SYMBOL         | TYPE     | PIN NO | DESCRIPTIONS                                                           |

| AVSS PWR 2, 3 Analog 5V power ground  V33 PWR 6 USB DC power 3.3V output.  D+ I/O 4 USB signal (+)  D- I/O 5 USB signal (-)  XTALI I 79 Crystal input. Use 6MHz crystal. A 6MHz clock source may also be used.  XTALO O 80 Crystal output.  Smart Card Reader Pins  SCPWR O 66 Smart card power supplier enable pin  SCIO I/O 63 Smart card serial data input/output pin or GPIO pin  SCCLK O (I/O) 64 Smart card clock output (default 3MHz) or GPIO pin  SCRST O 65 Smart card existed indicator. Schmitt-trigger input  Extra Pins  PLLEN I 53 PLL enable pin; Schmitt-trigger pull up input  XCVREN I 95 XCVR enable pin; Schmitt-trigger pull up input  SOFTCNEN I 11 Software connection enable pin; Schmitt-trigger pull up input  TESTENB I 12 Test enable pin; Schmitt-trigger pull up input  Power Pins  VSD PWR 37,81 GROUND: ground potential.  VDD PWR 38,82 POWER SUPPLY: Supply voltage for operation.  Serial Interface  SDA I/O 8 Data input/output of serial interface                                                                                                                                                                                                                                                                                                         | USB Pins       |          |        |                                                                        |

| PWR 6 USB DC power 3.3V output.  D+ I/O 4 USB signal (+)  D- I/O 5 USB signal (-)  XTALI I 79 Crystal input. Use 6MHz crystal. A 6MHz clock source may also be used.  XTALO O 80 Crystal output.  Smart Card Reader Pins  SCPWR O 66 Smart card power supplier enable pin  SCIO I/O 63 Smart card serial data input/output pin or GPIO pin  SCCLK O (I/O) 64 Smart card clock output (default 3MHz) or GPIO pin  SCRST O 65 Smart card existed indicator. Schmitt-trigger input  Extra Pins  PLLEN I 53 PLL enable pin; Schmitt-trigger pull up input  XCVREN I 95 XCVR enable pin; Schmitt-trigger pull up input  SOFTCNEN I 11 Software connection enable pin; Schmitt-trigger pull up input  TESTENB I 12 Test enable pin; Schmitt-trigger pull up input  Power Pins  VSS PWR 37,81 GROUND: ground potential.  VDD PWR 38,82 POWER SUPPLY: Supply voltage for operation.  Serial Interface  SDA I/O 8 Data input/output of serial interface                                                                                                                                                                                                                                                                                                                                                   | AVdd           | PWR      | 1      | Analog 5V power supply                                                 |

| D+ I/O 4 USB signal (+) D- I/O 5 USB signal (-)  XTALI I 79 Crystal input. Use 6MHz crystal. A 6MHz clock source may also be used.  XTALO O 80 Crystal output.  Smart Card Reader Pins  SCPWR O 66 Smart card power supplier enable pin  SCIO I/O 63 Smart card serial data input/output pin or GPIO pin  SCCLK O (I/O) 64 Smart card clock output (default 3MHz) or GPIO pin  SCRST O 65 Smart card reset signal  SCPRSNT I 83 Smart card existed indicator. Schmitt-trigger input  Extra Pins  PLLEN I 53 PLL enable pin; Schmitt-trigger pull up input  XCVREN I 95 XCVR enable pin; Schmitt-trigger pull up input  SOFTCNEN I 11 Software connection enable pin; Schmitt-trigger pull up input  TESTENB I 12 Test enable pin; Schmitt-trigger pull up input  Power Pins  VSS PWR 37,81 GROUND: ground potential.  VDD PWR 38,82 POWER SUPPLY: Supply voltage for operation.  Serial Interface  SDA I/O 8 Data input/output of serial interface                                                                                                                                                                                                                                                                                                                                               | AVss           | PWR      | 2, 3   | Analog 5V power ground                                                 |

| D- I/O 5 USB signal (-)  XTALI I 79 Crystal input. Use 6MHz crystal. A 6MHz clock source may also be used.  XTALO O 80 Crystal output.  Smart Card Reader Pins  SCPWR O 66 Smart card power supplier enable pin  SCIO I/O 63 Smart card serial data input/output pin or GPIO pin  SCCLK O (I/O) 64 Smart card clock output (default 3MHz) or GPIO pin  SCRST O 65 Smart card reset signal  SCPRSNT I 83 Smart card existed indicator. Schmitt-trigger input  Extra Pins  PLLEN I 53 PLL enable pin; Schmitt-trigger pull up input  XCVREN I 95 XCVR enable pin; Schmitt-trigger pull up input  SOFTCNEN I 11 Software connection enable pin; Schmitt-trigger pull up input  TESTENB I 12 Test enable pin; Schmitt-trigger pull up input  Power Pins  VSS PWR 37,81 GROUND: ground potential.  VDD PWR 38,82 POWER SUPPLY: Supply voltage for operation.  Serial Interface  SDA I/O 8 Data input/output of serial interface                                                                                                                                                                                                                                                                                                                                                                       | V33            | PWR      | 6      | USB DC power 3.3V output.                                              |

| XTALI   79   Crystal input. Use 6MHz crystal. A 6MHz clock source may also be used.  XTALO   O   80   Crystal output.  Smart Card Reader Pins  SCPWR   O   66   Smart card power supplier enable pin  SCIO   I/O   63   Smart card serial data input/output pin or GPIO pin  SCCLK   O (I/O)   64   Smart card clock output (default 3MHz) or GPIO pin  SCRST   O   65   Smart card reset signal  SCPRSNT   I   83   Smart card existed indicator. Schmitt-trigger input  Extra Pins  PLLEN   I   53   PLL enable pin; Schmitt-trigger pull up input  XCVREN   I   95   XCVR enable pin; Schmitt-trigger pull up input  SOFTCNEN   I   11   Software connection enable pin; Schmitt-trigger pull up input  TESTENB   I   12   Test enable pin; Schmitt-trigger pull up input  Power Pins  Vss   PWR   37,81   GROUND: ground potential.  VDD   PWR   38,82   POWER SUPPLY: Supply voltage for operation.  Serial Interface  SDA   I/O   8   Data input/output of serial interface                                                                                                                                                                                                                                                                                                                | D+             | I/O      | 4      | USB signal (+)                                                         |

| used.     XTALO   O   80   Crystal output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D-             | I/O      | 5      | USB signal (-)                                                         |

| Smart Card Reader Pins  SCPWR O 66 Smart card power supplier enable pin  SCIO I/O 63 Smart card serial data input/output pin or GPIO pin  SCCLK O (I/O) 64 Smart card clock output (default 3MHz) or GPIO pin  SCRST O 65 Smart card reset signal  SCPRSNT I 83 Smart card existed indicator. Schmitt-trigger input  Extra Pins  PLLEN I 53 PLL enable pin; Schmitt-trigger pull up input  XCVREN I 95 XCVR enable pin; Schmitt-trigger pull up input  SOFTCNEN I 11 Software connection enable pin; Schmitt-trigger pull up input  TESTENB I 12 Test enable pin; Schmitt-trigger pull up input  Power Pins  VSS PWR 37,81 GROUND: ground potential.  VDD PWR 38,82 POWER SUPPLY: Supply voltage for operation.  Serial Interface  SDA I/O 8 Data input/output of serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | XTALI          | I        | 79     | Crystal input. Use 6MHz crystal. A 6MHz clock source may also be used. |

| SCPWR O 66 Smart card power supplier enable pin SCIO I/O 63 Smart card serial data input/output pin or GPIO pin SCCLK O (I/O) 64 Smart card clock output (default 3MHz) or GPIO pin SCRST O 65 Smart card reset signal SCPRSNT I 83 Smart card existed indicator. Schmitt-trigger input  Extra Pins  PLLEN I 53 PLL enable pin; Schmitt-trigger pull up input XCVREN I 95 XCVR enable pin; Schmitt-trigger pull up input SOFTCNEN I 11 Software connection enable pin; Schmitt-trigger pull up input TESTENB I 12 Test enable pin; Schmitt-trigger pull up input  Power Pins  VSS PWR 37,81 GROUND: ground potential.  VDD PWR 38,82 POWER SUPPLY: Supply voltage for operation.  Serial Interface  SDA I/O 8 Data input/output of serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | XTALO          | 0        | 80     | Crystal output.                                                        |

| SCIO I/O 63 Smart card serial data input/output pin or GPIO pin  SCCLK O (I/O) 64 Smart card clock output (default 3MHz) or GPIO pin  SCRST O 65 Smart card reset signal  SCPRSNT I 83 Smart card existed indicator. Schmitt-trigger input  Extra Pins  PLLEN I 53 PLL enable pin; Schmitt-trigger pull up input  XCVREN I 95 XCVR enable pin; Schmitt-trigger pull up input  SOFTCNEN I 11 Software connection enable pin; Schmitt-trigger pull up input  TESTENB I 12 Test enable pin; Schmitt-trigger pull up input  Power Pins  VSS PWR 37,81 GROUND: ground potential.  VDD PWR 38,82 POWER SUPPLY: Supply voltage for operation.  Serial Interface  SDA I/O 8 Data input/output of serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Smart Card F   | Reader F | Pins   |                                                                        |

| SCCLK O (I/O) 64 Smart card clock output (default 3MHz) or GPIO pin  SCRST O 65 Smart card reset signal  SCPRSNT I 83 Smart card existed indicator. Schmitt-trigger input  Extra Pins  PLLEN I 53 PLL enable pin; Schmitt-trigger pull up input  XCVREN I 95 XCVR enable pin; Schmitt-trigger pull up input  SOFTCNEN I 11 Software connection enable pin; Schmitt-trigger pull up input  TESTENB I 12 Test enable pin; Schmitt-trigger pull up input  Power Pins  Vss PWR 37,81 GROUND: ground potential.  VDD PWR 38,82 POWER SUPPLY: Supply voltage for operation.  Serial Interface  SDA I/O 8 Data input/output of serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SCPWR          | 0        | 66     | Smart card power supplier enable pin                                   |

| SCRST O 65 Smart card reset signal SCPRSNT I 83 Smart card existed indicator. Schmitt-trigger input  Extra Pins  PLLEN I 53 PLL enable pin; Schmitt-trigger pull up input  XCVREN I 95 XCVR enable pin; Schmitt-trigger pull up input  SOFTCNEN I 11 Software connection enable pin; Schmitt-trigger pull up input  TESTENB I 12 Test enable pin; Schmitt-trigger pull up input  Power Pins  Vss PWR 37,81 GROUND: ground potential.  VDD PWR 38,82 POWER SUPPLY: Supply voltage for operation.  Serial Interface  SDA I/O 8 Data input/output of serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SCIO           | I/O      | 63     | Smart card serial data input/output pin or GPIO pin                    |

| SCPRSNT I 83 Smart card existed indicator. Schmitt-trigger input  Extra Pins  PLLEN I 53 PLL enable pin; Schmitt-trigger pull up input  XCVREN I 95 XCVR enable pin; Schmitt-trigger pull up input  SOFTCNEN I 11 Software connection enable pin; Schmitt-trigger pull up input  TESTENB I 12 Test enable pin; Schmitt-trigger pull up input  Power Pins  Vss PWR 37,81 GROUND: ground potential.  VDD PWR 38,82 POWER SUPPLY: Supply voltage for operation.  Serial Interface  SDA I/O 8 Data input/output of serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SCCLK          | O (I/O)  | 64     | Smart card clock output (default 3MHz) or GPIO pin                     |

| Extra Pins  PLLEN I 53 PLL enable pin; Schmitt-trigger pull up input  XCVREN I 95 XCVR enable pin; Schmitt-trigger pull up input  SOFTCNEN I 11 Software connection enable pin; Schmitt-trigger pull up input  TESTENB I 12 Test enable pin; Schmitt-trigger pull up input  Power Pins  Vss PWR 37,81 GROUND: ground potential.  VDD PWR 38,82 POWER SUPPLY: Supply voltage for operation.  Serial Interface  SDA I/O 8 Data input/output of serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SCRST          | 0        | 65     | Smart card reset signal                                                |

| PLLEN I 53 PLL enable pin; Schmitt-trigger pull up input  XCVREN I 95 XCVR enable pin; Schmitt-trigger pull up input  SOFTCNEN I 11 Software connection enable pin; Schmitt-trigger pull up input  TESTENB I 12 Test enable pin; Schmitt-trigger pull up input  Power Pins  VSS PWR 37,81 GROUND: ground potential.  VDD PWR 38,82 POWER SUPPLY: Supply voltage for operation.  Serial Interface  SDA I/O 8 Data input/output of serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SCPRSNT        | I        | 83     | Smart card existed indicator. Schmitt-trigger input                    |

| XCVREN I 95 XCVR enable pin; Schmitt-trigger pull up input SOFTCNEN I 11 Software connection enable pin; Schmitt-trigger pull up input TESTENB I 12 Test enable pin; Schmitt-trigger pull up input  Power Pins VSS PWR 37,81 GROUND: ground potential. VDD PWR 38,82 POWER SUPPLY: Supply voltage for operation.  Serial Interface SDA I/O 8 Data input/output of serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Extra Pins     |          |        |                                                                        |

| SOFTCNEN I 11 Software connection enable pin; Schmitt-trigger pull up input TESTENB I 12 Test enable pin; Schmitt-trigger pull up input  Power Pins  VSS PWR 37,81 GROUND: ground potential.  VDD PWR 38,82 POWER SUPPLY: Supply voltage for operation.  Serial Interface  SDA I/O 8 Data input/output of serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PLLEN          | I        | 53     | PLL enable pin; Schmitt-trigger pull up input                          |

| TESTENB I 12 Test enable pin; Schmitt-trigger pull up input  Power Pins  Vss PWR 37,81 GROUND: ground potential.  VDD PWR 38,82 POWER SUPPLY: Supply voltage for operation.  Serial Interface  SDA I/O 8 Data input/output of serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | XCVREN         | I        | 95     | XCVR enable pin; Schmitt-trigger pull up input                         |

| Power Pins  Vss PWR 37,81 GROUND: ground potential.  VDD PWR 38,82 POWER SUPPLY: Supply voltage for operation.  Serial Interface  SDA I/O 8 Data input/output of serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SOFTCNEN       | I        | 11     | Software connection enable pin; Schmitt-trigger pull up input          |

| VSS PWR 37,81 GROUND: ground potential.  VDD PWR 38,82 POWER SUPPLY: Supply voltage for operation.  Serial Interface  SDA I/O 8 Data input/output of serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TESTENB        | I        | 12     | Test enable pin; Schmitt-trigger pull up input                         |

| VDD PWR 38,82 POWER SUPPLY: Supply voltage for operation.  Serial Interface  SDA I/O 8 Data input/output of serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Power Pins     |          |        |                                                                        |

| Serial Interface  SDA I/O 8 Data input/output of serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Vss            | PWR      | 37,81  | GROUND: ground potential.                                              |

| SDA I/O 8 Data input/output of serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Vdd            | PWR      | 38,82  | POWER SUPPLY: Supply voltage for operation.                            |

| ' '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Serial Interfa | се       |        |                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SDA            | I/O      | 8      | Data input/output of serial interface                                  |

| SCL I Glock input of serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SCL            | I        | 9      | Clock input of serial interface                                        |

3.2.1 100-pin LQFP package description, continued

| SYMBOL   | TYPE  | PIN NO                     | DESCRIPTIONS                                                                                                                                                                                                                                                                      |

|----------|-------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uC Pins  |       | •                          |                                                                                                                                                                                                                                                                                   |

| EA       | I     | 96                         | EXTERNAL ACCESS ENABLE: This pin forces the processor to execute the external ROM. The ROM address and data will not be present on the bus if the $\overline{\text{EA}}$ pin is high and the program counter is within the 64 KB area. Otherwise they will be present on the bus. |

| UC51EN   | I     | 97                         | EXTERNAL uC51 ENABLE: to enable external processor                                                                                                                                                                                                                                |

| PSEN     | ОН    | 39                         | PROGRAM STORE ENABLE: PSEN enables the external ROM data in the Port 0 address/data bus.                                                                                                                                                                                          |

|          |       |                            | When internal ROM access is performed, no $\overline{\text{PSEN}}$ strobe signal outputs originate from this pin.                                                                                                                                                                 |

| ALE      | ОН    | 86                         | ADDRESS LATCH ENABLE: ALE is used to enable the address latch that separates the address from the data on Port 0. ALE runs at 1/6th of the oscillator frequency. An ALE pulse is omitted during external data memory accesses.                                                    |

| RST      | I L   | 61                         | RESET: A high on this pin for two machine cycles while the oscillator is running resets the device.                                                                                                                                                                               |

| UC-XO    | 0     | 45                         | uC Crystal output.                                                                                                                                                                                                                                                                |

| UC-XI    | I     | 46                         | uC Crystal input.                                                                                                                                                                                                                                                                 |

| P0.0 - 7 | I/O D | 93,94,14,15<br>29,31,32,33 | PORT 0: Function is the same as that of the standard 8052.                                                                                                                                                                                                                        |

| P1.0     | I/O   | 16                         | It is a high drive I/O pad. Used as a GPIO pin for memory-type SC                                                                                                                                                                                                                 |

| P1.1     | I/O   | 18                         | It is a high drive I/O pad. Used as a GPIO pin for memory-type SC                                                                                                                                                                                                                 |

| P1.2     | I/O   | 19                         | Used as a GPIO pin for memory-type SC                                                                                                                                                                                                                                             |

| P1.3     | I/O   | 26                         | Used as a GPIO pin for memory-type SC                                                                                                                                                                                                                                             |

| P1.4     | I/O   | 27                         | Used as a GPIO pin for memory-type SC                                                                                                                                                                                                                                             |

| P1.5     | I/O   | 43                         | Used as a GPIO pin for memory-type SC                                                                                                                                                                                                                                             |

| P1.6     | I/O   | 51                         | GPIO & remote wakeup pin                                                                                                                                                                                                                                                          |

| P1.7     | I/O   | 52                         | GPIO & external interrupt pin                                                                                                                                                                                                                                                     |

| P2.0 – 7 | I/O H | 41,42,55,56<br>57,59,60,84 | PORT 2: Bi-directional I/O port with internal pull-ups. Also provides the upper address bits for external memory. Can be programmed as output-latched port as on-chip 74373, or a buffer input port as an on-chip 74244.                                                          |

| P3.0 - 7 | I/O H | 68,69,35,36<br>88,89,90,91 | PORT 3: Function is the same as that of the standard 8052.                                                                                                                                                                                                                        |

\*Note: **TYPE** I: input, O: output, I/O: bi-directional, H: pull-high, L: pull-low, D: open drain, PWR: Power pins

#### 4. PROGRAMMING INTERFACE

## 4.1 Register map

|    | 0/8                | 1/9                             | 2/A                 | 3/B                             | 4/C                | 5/D                | 6/E                 | 7/F                             | •  |

|----|--------------------|---------------------------------|---------------------|---------------------------------|--------------------|--------------------|---------------------|---------------------------------|----|

| F8 |                    |                                 |                     |                                 |                    |                    |                     |                                 | FF |

| F0 | B<br>0000 0000     | EPINDEX xxxx xxx0               | TXSTAT<br>0xx0 0000 | TXDAT<br>xxxx xxxx<br>xxx0 0000 | TXCON<br>0xxx 0xxx | TXFLG<br>x0xx 1000 | TXCNT<br>xxxx 0000  | USBIDR                          | F7 |

| E8 |                    |                                 |                     |                                 |                    |                    |                     |                                 | EF |

| E0 | ACC<br>0000 0000   | EPCON<br>001x 0101<br>000x 0000 | RXSTAT<br>0000 0000 | RXDAT<br>0000 0000              | RXCON<br>0xx0 0xxx | RXFLG<br>x0xx 1000 | RXCNT<br>xxxx 0000  | FPCON<br>0000 0000<br>000- 1000 | E7 |

| D8 |                    |                                 |                     |                                 |                    |                    |                     |                                 | DF |

| D0 | PSW 0000 00x0      |                                 |                     | AUX<br>0000 0110                | PMPR1<br>xxxx xx00 | PMPR2<br>0000 0000 | CHPENR<br>0000 0000 |                                 | D7 |

| C8 |                    |                                 |                     |                                 |                    |                    |                     | CHPCON<br>0xx0 0000             | CF |

| C0 | FIFLG<br>xxx0 x000 |                                 |                     |                                 | SFRAL<br>0000 0000 | SFRAH<br>0000 0000 | SFRFD<br>0000 0000  | SFRCN<br>0000 0000              | C7 |

| В8 | IP<br>xxx0 0000    |                                 |                     |                                 |                    |                    |                     | SCON                            | BF |

| В0 | P3<br>1111 1111    | IEN1<br>0xxx 0x0x<br>-xxx       |                     |                                 |                    |                    |                     | DCON                            | В7 |

| A8 | IE<br>0xx0 0000    |                                 | SCIER<br>0000 0000  | SCISR<br>0000 0000              | SCCR<br>0001 0110  | SCECR<br>0000 0000 | SCGTR<br>0000 0000  |                                 | AF |

| A0 | P2<br>1111 1111    |                                 | FIE<br>xxx0 x000    | SCSR<br>0000 0000               | SCBDR<br>0000 0001 | SCCBR<br>0000 0001 | SCRDR<br>0000 0000  | SCTDR<br>0000 0000              | A7 |

| 98 | SCON<br>0000 0000  | SBUF<br>xxxx xxxx               |                     |                                 |                    |                    |                     |                                 | 9F |

| 90 | P1<br>1111 1111    |                                 |                     |                                 |                    |                    |                     |                                 | 97 |

| 88 | TCON<br>0000 0000  | TMOD<br>0000 0000               | TL0<br>0000 0000    | TL1<br>0000 0000                | TH0<br>0000 0000   | TH1<br>0000 0000   |                     | FADDR<br>0000 0000              | 8F |

| 80 | P0<br>1111 1111    | SP<br>0000 0011                 | DPL<br>0000 0000    | DPH<br>0000 0000                |                    |                    |                     | PCON<br>00xx 0000               | 87 |

|    | 0/8                | 1/9                             | 2/A                 | 3/B                             | 4/C                | 5/D                | 6/E                 | 7/F                             | •  |

| 8052 uC SFRs                     |

|----------------------------------|

| USB SFRs                         |

| Flash SFRs                       |

| Smart Card SFRs                  |

| Endpoint-Indexed SFRs by EPINDEX |

#### 4.2 FLASH Category - Descriptions Summary

| Mnemonic | ISP Registers                                        | Address |      |      |      | Descri | ption |       |       |         |

|----------|------------------------------------------------------|---------|------|------|------|--------|-------|-------|-------|---------|

| SFRCN    | The Control Register of uC ISP Function              | S:C7H   | -    | -    | OEN  | CEN    | CTRL3 | CTRL2 | CTRL1 | CTRL0   |

| SFRFD    | The Programming Data Register for Flash Memory       | S:C6H   | FD7  | FD6  | FD5  | FD4    | FD3   | FD2   | FD1   | FD0     |

| SFRAH    | The High Byte of the Programming Address             | S:C5H   | HA7  | HA6  | HA5  | HA4    | HA3   | HA2   | HA1   | HA0     |

| SFRAL    | The Low Byte of the Programming Address              | S:C4H   | LA6  | LA6  | LA5  | LA4    | LA3   | LA2   | LA1   | LA0     |

| Mnemonic | uC Control Registers                                 | Address |      |      |      | Descri | ption |       |       |         |

| CHPCON   | On-chip Programming Control<br>Register              | S:CFH   | ı    | -    | ı    | -      | ı     | -     | -     | FPROGEN |

| PMPR2    | Flash Memory Protective Blocks<br>Configure Register | S:D5H   | LBP7 | LBP6 | LBP5 | LBP4   | LBP3  | LBP2  | LBP1  | LBP0    |

| PMPR1    | Flash Memory Protective Blocks<br>Configure Register | S:D4H   | -    | _    | -    | _      | -     | _     | HBP1  | HBP0    |

#### 4.3 SC Category - Descriptions Summary

| Mnemonic | SC Interrupt SFRs              | Address |        | Description |        |             |          |        |      |        |

|----------|--------------------------------|---------|--------|-------------|--------|-------------|----------|--------|------|--------|

| SCIER    | SC Interrupt Enable Register   | S:AAH   | -      | ESCPTI      | WCE    | -           | RDRE     | PBE    | EXIE | -      |

| SCISR    | SC Interrupt Status Register   | S:ABH   | -      | SCPTI       | WCI    | TDI         | RDRI     | PBRI   | EXI  | EXI_16 |

| Mnemonic | SC Control SFRs                | Address |        |             |        | Des         | cription |        |      |        |

| SCSR     | SC Status Register             | S:A3H   | -      | -           | -      | -           | SCPRSNT  | -      | -    | CA     |

| SCCR     | SC Control Register            | S:ACH   | -      | -           | -      | CLKSTPL     | S_CK1    | S_CK0  | EPE  | EXINTH |

| SCECR    | SC Extended Control Register   | S:ADH   | CRDRST | PWRENP      | VCC_EN | -           | -        | CLKSTP | SCIO | SCRRST |

| SCGTR    | SC Guard Time Control Register | S:AEH   | BIT7   | BIT6        | BIT5   | BIT4        | BIT3     | BIT2   | BIT1 | BIT0   |

| SCBDR    | SC Baud Rate Divider Register  | S:A4H   | BIT7   | BIT6        | BIT5   | BIT4        | BIT3     | BIT2   | BIT1 | BIT0   |

| SCCBR    | SC Clock Base Register         | S:A5H   | BIT7   | BIT6        | BIT5   | BIT4        | BIT3     | BIT2   | BIT1 | BIT0   |

| Mnemonic | SC Data SFRs                   | Address |        |             |        | Description |          |        |      |        |

| SCRDR    | SC RX Data Register            | S:A6H   | RD7    | RD6         | RD5    | RD4         | RD3      | RD2    | RD1  | RD0    |

| SCTDR    | SC TX Data Register            | S:A7H   | TD7    | TD6         | TD5    | TD4         | TD3      | TD2    | TD1  | TD0    |

## 4.4 USB Category - Descriptions Summary

| Mnemonic | USB Power Control SFRs Address Description |         |           |          |         |         |          |          |          |          |

|----------|--------------------------------------------|---------|-----------|----------|---------|---------|----------|----------|----------|----------|

| FPCON    | Function Power Control Register            | S:E7H   | FPD       | FRWUPE   | FWKP    | URDIS   | URST     | FRWU     | FRSM     | FSUS     |

| Mnemonic | USB Interrupt System SFRs                  | Address |           |          |         | Desc    | ription  |          |          |          |

| FIE      | USB Function Interrupt Enable Register     | S:A2H   | -         | -        | FRXIE4  | FTXIE3  | FRXIE2   | FTXIE1   | FRXIE0   | FTXIE0   |

| FIFLG    | USB Function Interrupt Flag<br>Register    | S:C0H   | -         | ı        | FRXD4   | FTXD3   | FRXD2    | FTXD1    | FRXD0    | FTXD0    |

| IEN1     | USB Interrupt Enable Register              | S:B1H   | EA        | 1        | -       | -       | EFSR     | 1        | EF       | -        |

| Mnemonic | USB Function SFRs                          | Address |           |          |         | Desc    | ription  |          |          |          |

| EPCON*   | Endpoint Control Register                  | S:E1H   | RXSTL     | TXSTL    | CTLEP   | -       | RXIE     | RXEPEN   | TXOE     | TXEPEN   |

| EPINDEX  | Endpoint Index Register                    | S:F1H   | -         | -        | -       | -       | -        | EPINX2   | EPINX1   | EPINX0   |

| FADDR    | Function Address Register                  | S:8FH   | -         | A6       | A5      | A4      | A3       | A2       | A1       | A0       |

| RXCNT*   | Receive FIFO Byte-Count Register           | S:E6H   | -         | -        | -       | BC4     | BC3      | BC2      | BC1      | BC0      |

| RXCON*   | Receive FIFO Control Register              | S:E4H   | RXCLR     | -        | -       | RXFFRC  | RXISO    | -        | -        | -        |

| RXDAT*   | Receive FIFO Data Register                 | S:E3H   | RD7       | RD6      | RD5     | RD4     | RD3      | RD2      | RD1      | RD0      |

| RXFLG*   | Receive FIFO Flag Register                 | S:E5H   | -         | RXFIFO   | -       | -       | RXEMP    | RXFULL   | RXURF    | RXOVF    |

| RXSTAT*  | Endpoint Receive Status Register           | S:E2H   | RXSEQ     | RXSETUP  | STOVW   | EDOVW   | RXSOVW   | RXVOID   | RXERR    | RXACK    |

| TXCNT*   | Transmit FIFO Byte-Count Register          | S:F6H   | -         | -        | -       | BC4     | BC3      | BC2      | BC1      | BC0      |

| TXCON*   | Transmit FIFO Control Register             | S:F4H   | TXCLR     | -        | -       | -       | -        | -        | -        | -        |

| TXDAT*   | Transmit FIFO Data Register                | S:F3H   | TD7       | TD6      | TD5     | TD4     | TD3      | TD2      | TD1      | TD0      |

| TXFLG*   | Transmit FIFO Flag Register                | S:F5H   | -         | TXFIFO   | -       | -       | TXEMP    | TXFULL   | TXURF    | TXOVF    |

| TXSTAT*  | Endpoint Transmit Status Register          | S:F2H   | TXSEQ     | -        | -       | TXFLUSH | TXSOVW   | TXVOID   | TXERR    | TXACK    |

| Mnemonic | USB Device SFRs                            | Address |           |          |         | Desc    | ription  |          |          |          |

| DCON     | Device Control Register 1                  | S:B7H   | TEST_MODE | SCGPIOSL | SCIOGPE | SCIOGPD | SCCLKGPE | SCCLKGPD | PTRWUEN  | CONPUEN  |

| SCON     | SIE Control Register                       | S:BFH   | SIERXDE   | SIELSE   | SECKPAT | STODPAT | SEOSMOD1 | SEOSMOD0 | SEOPMOD1 | SEOPMOD0 |

#### 4.5 Individual register description

#### 4.5.1 Register Descriptions - USB Power Control Registers (E7)

FPCON Address: S:E7H

System Reset State: 0000 0000H USB Reset State: 000–1000H

Function Power Control Register. Facilitates the control and status relating to power-down mode, remote-wakeup enable, function wakeup, USB reset separation, remote wake-up control and function resume/suspend.

7 6 5 4 3 2 1 0 **FPD FRWUPE FWKP FRIE FRST FRWU FRSM FSUS**

| Bit<br>Number | Bit<br>Mnemonic | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7             | FPD             | Function Power-down Mode Bit:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |