# MT90880/1/2/3

January 2003

TDM to Packet Processors Data Sheet

# Features

- WAN interface, consisting of 32 input and output streams at 2.048 or 8.192 Mbit/s

- Up to 1024 bi-directional 64 Kbit/s channels

- N \* 64 Kbit/s trunking of channels across any stream and channel

- 1K by 1K non-blocking TDM switch

- Local TDM interface, with 32 streams at 2.048, 4.096 and 8.192 Mbit/s

- Flexible, multi-protocol packet encapsulation

- Dual 100Mbit/s MII interfaces for redundancy or for load balancing

- Quality of service features, including weighted fair queuing, strict priority and queue size limit thresholds

- High performance 33MHz / 66MHz 32 bit PCI bus

- Integral Stratum 4E PLL for synchronisation to the TDM domain

- Power consumption of less than 0.75 W

# Applications

- Packet backplane interconnection

- Circuit Emulation over packet domain

- Internet Off-load

- Remote Access Concentrators

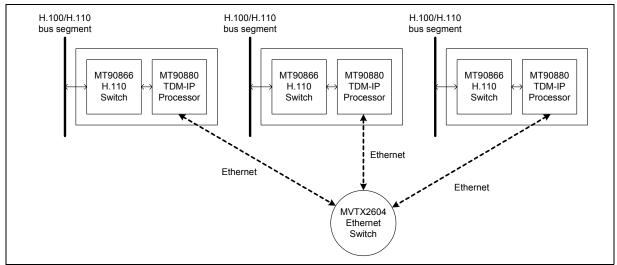

- H.100/H.110 extension and expansion

| Ordering Information     |               |  |

|--------------------------|---------------|--|

| MT90880B/IG/BP1N         | 456 ball PBGA |  |

| MT90881A/IG/BP1N         | 456 ball PBGA |  |

| MT90882B/IG/BP1N         | 456 ball PBGA |  |

| MT90883A/IG/BP1N         | 456 ball PBGA |  |

| -40 to 85 <sup>0</sup> C |               |  |

# Description

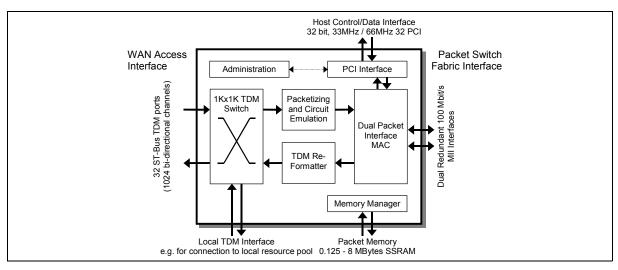

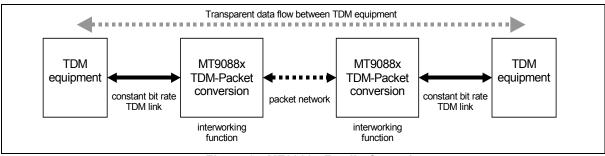

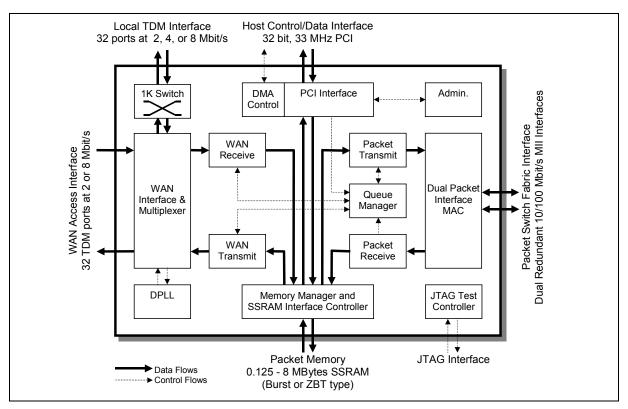

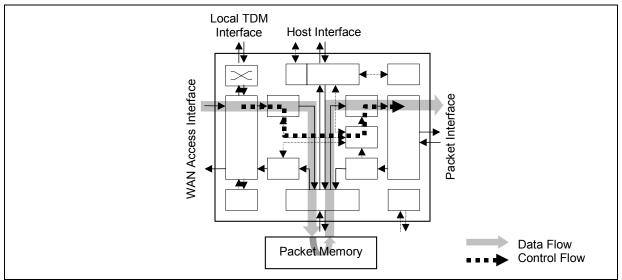

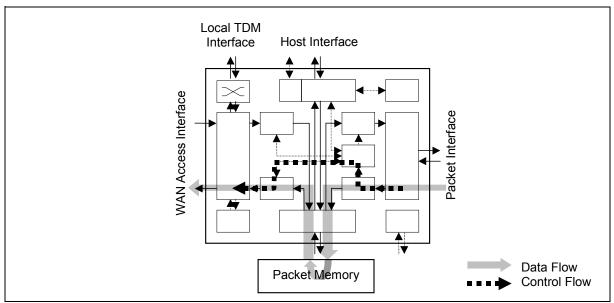

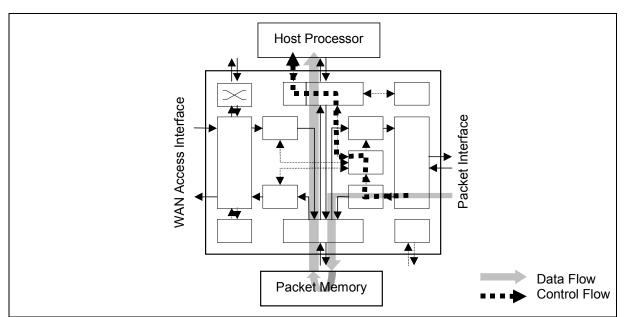

The MT9088x is a family of highly functional TDM to Packet bridging devices. It provides a bridge between a WAN environment based on constant bit rate TDM streams and a packet domain based on Ethernet technology.

It is capable of assembling user-defined packets of TDM traffic from the WAN Access Interface and transmitting them from the Ethernet interfaces using a variety of protocols. If external processing is required (e.g. HDLC or modem termination) the traffic can be switched to a local interface using the internal TDM switch.

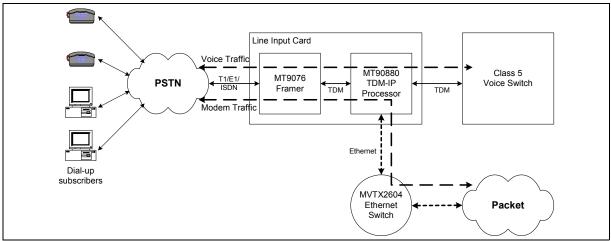

Figure 1 - MT90880 High Level Overview

# MT90880/1/2/3

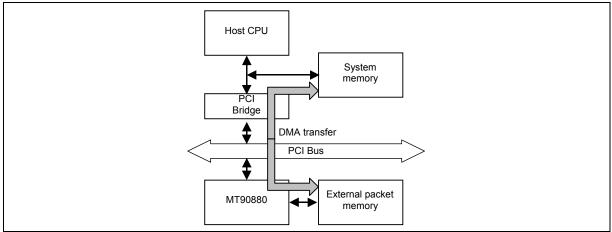

Packets received from the Ethernet interfaces are parsed to determine the egress destination, and are appropriately queued either to the WAN Access Interface or to the PCI interface. An integrated DMA controller is used to transfer packets to and from the PCI interface with a minimum of CPU intervention.

# Variants

There are four device variants in the MT9088x family:

- MT90880 1024 bi-directional channels, integral TDM switch

- MT90881 1024 bi-directional channels, no TDM switch

- MT90882 256 bi-directional channels, integral TDM switch

- MT90883 256 bi-directional channels, no TDM switch

| Feature                   | MT90880          | MT90881       | MT90882          | MT90883       |

|---------------------------|------------------|---------------|------------------|---------------|

| No. of WAN streams        | 32               | 32            | 8                | 8             |

| Local Port                | Yes              | No            | Yes              | No            |

| No. of Available Channels | 1024             | 1024          | 256              | 256           |

| TDM Switch Availability   | Master mode only | Not Available | Master mode only | Not Available |

| PCI Interface             | 33 / 66MHz       | 33 / 66MHz    | 33 / 66MHz       | 33 / 66MHz    |

| MII Interface             | Yes              | Yes           | Yes              | Yes           |

| RMII Interface            | Yes              | Yes           | Yes              | Yes           |

| JTAG                      | Yes              | Yes           | Yes              | Yes           |

**Table 1 - Variant Options**

# **Related Documents**

This data sheet should be read in conjunction with the following related documents and application notes:

| Title                                                                                   | Author  | Document<br>Number | Issue / Date    |

|-----------------------------------------------------------------------------------------|---------|--------------------|-----------------|

| 1. MT9088x Programmers Model                                                            | Zarlink | DM5708             | 1.0, Aug. 2002  |

| 2. MT9088x API User Guide                                                               | Zarlink | DM5805             | 1.0, Sept. 2002 |

| 3. MSAN-198 - Performing Clock Recovery for Circuit<br>Emulation when using the MT90880 | Zarlink | AN5789             | 1, Aug. 2002    |

| 4. MSAN-199 - Unstructured Circuit Emulation Using the<br>MT90880                       | Zarlink | AN5790             | 1, Aug. 2002    |

| 5. MSAN-200 - MT90880 TDM Replacement Packet<br>Backplane                               | Zarlink | AN5791             | 1, Aug. 2002.   |

**Table 2 - Related Documents**

The following external documents and standards are referenced in this data sheet:

|     | Title                                                                                                                                                                     | Author             | Document<br>Number | Issue / Date        |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|---------------------|

| 1.  | Local and Metropolitan Area Networks, Part 3: Carrier<br>sense multiple access with collision detection<br>(CSMA/CD) access method and physical layer specifi-<br>cations | IEEE               | IEEE 802.3u        | 1995                |

| 2.  | PCI Local Bus Specification                                                                                                                                               | PCI SIG            |                    | 2.2                 |

| 3.  | RMII <sup>TM</sup> Specification                                                                                                                                          | RMII<br>consortium |                    | Rev 1.2, March 1998 |

| 4.  | Test Access Port and Boundary Scan Architecture                                                                                                                           | IEEE               | IEEE 1149.1        | 1990                |

| 5.  | Circuit Emulation Service Interoperability Specification                                                                                                                  | ATM Forum          | af-vtoa-0078       | Ver 2.0, Jan. 1997  |

| 6.  | Specifications of (DBCES) Dynamic Bandwidth Utiliza-<br>tion - in 64KBPS Time Slot Trunking over ATM - Using<br>CES                                                       | ATM Forum          | af-vtoa-0085       | July 1997           |

| 7.  | ST-BUS Generic Device Specification                                                                                                                                       | Mitel              | MSAN-126           | Rev. B, June 1995   |

| 8.  | H.110 Hardware Compatibility Specification: CT Bus                                                                                                                        | ECTF               |                    | Rev. 1.0, 1997      |

| 9.  | H-MVIP Standard                                                                                                                                                           | GO-MVIP            |                    | Rel. 1.1a, Jan. '97 |

| 10. | Clocks for the Synchronized Network: Common Generic Cri-<br>teria                                                                                                         | Telcordia          | GR-1244-<br>CORE   | Iss. 2, Dec. 2000   |

|     | The Control of Jitter and Wander within digital networks which are based on the 2048 Kbit/s hierarchy                                                                     | ITU-T              | G.823              | 2000                |

| 12. | The Control of Jitter and Wander within digital networks which are based on the 1544 Kbit/s hierarchy                                                                     | ITU-T              | G.824              | 2000                |

**Table 3 - Referenced Documents**

# **Table of Contents**

| 1.0 Typical Applications                                               | 3        |

|------------------------------------------------------------------------|----------|

| 1.1 Packet Backplane Interconnection                                   |          |

| 1.2 Circuit Emulation Services                                         |          |

| 1.3 Internet Off-load                                                  |          |

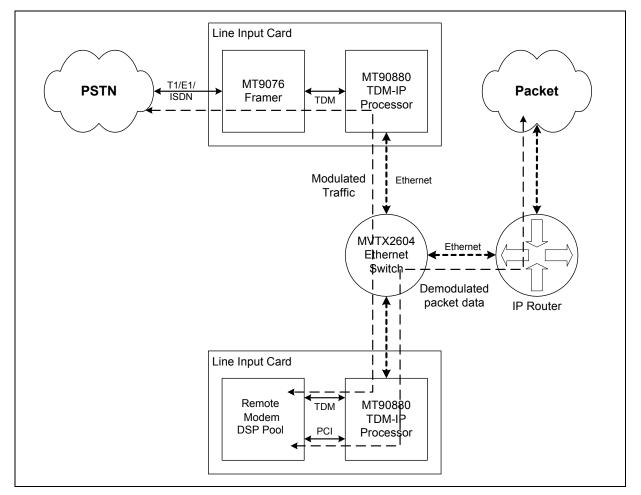

| 1.4 Remote Access Concentration                                        |          |

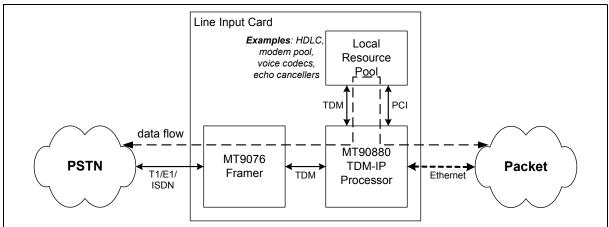

| 1.5 Local Resource Pool Example                                        |          |

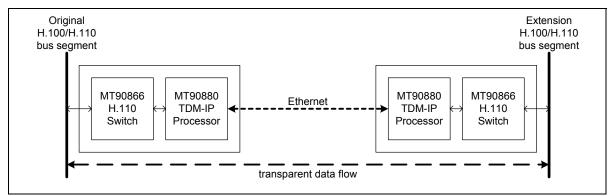

| 1.6 H.100/H.110 Extension                                              |          |

| 1.7 H.100/H.110 Expansion                                              |          |

| 2.0 Functional Operation                                               |          |

| 2.1 Overview                                                           |          |

| 2.2 Basic Operation                                                    |          |

| 2.2.1 WAN Access Interface                                             |          |

| 2.2.2 TDM Packet Assembly                                              |          |

| 2.2.3 Packet Transmission.                                             |          |

| 2.2.4 CPU Packet Generation                                            |          |

| 2.2.5 Packet Reception                                                 |          |

| 2.2.6 Call Setup and Control                                           | 10<br>10 |

| 2.3 Data and Control Flows                                             |          |

| 2.4 Packet Assembly                                                    |          |

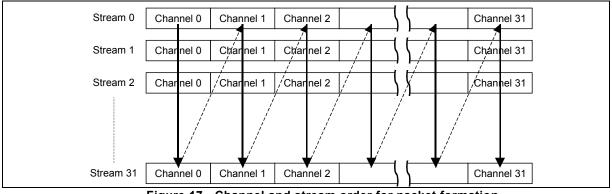

| 2.4.1 Payload Order                                                    |          |

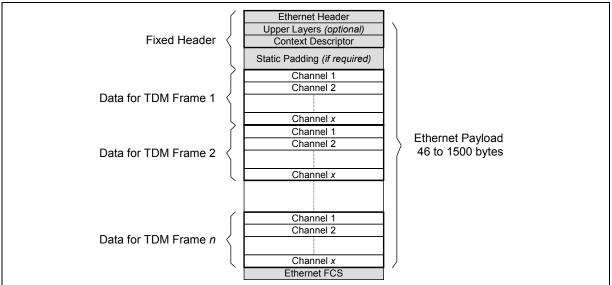

| 2.4.2 Packet Structure                                                 |          |

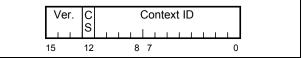

| 2.4.3 Context Descriptor Protocol                                      |          |

| 2.5 Context Negotiation and Establishment                              | 19       |

| 2.5.1 Overview                                                         |          |

| 2.5.2 New Context Establishment                                        |          |

| 2.5.3 Context Modification (Addition or deletion of physical channels) |          |

| 2.5.4 Context Removal                                                  |          |

| 2.5.5 Context Cleardown                                                |          |

| 3.0 Functional Block Descriptions                                      |          |

| 3.1 WAN Interface and Multiplexers                                     |          |

| 3.1.1 Port Data Formats                                                |          |

| 3.1.2 Operational Modes                                                |          |

| 3.2 TDM Cross-Connect Switch                                           |          |

| 3.2.1 Multiplexing and blocking                                        |          |

| 3.2.2 Re-ordering timeslots                                            |          |

| 3.2.3 Channel Broadcast                                                |          |

| 3.3 WAN Receive and Transmit Functions                                 |          |

| 3.4 Operation of the WAN Receive Block                                 |          |

| 3.4.1 Context Control in the WAN Receive/Transmit Controllers          |          |

| 3.4.2 Jitter buffer operation                                          |          |

| 3.5 Queue Manager                                                      |          |

| 3.5.1 Queues to the Packet Interface                                   |          |

| 3.5.2 Queues to PCI Interface                                          |          |

| 3.5.3 Queues to WAN Interface                                          |          |

| 3.6 Packet Transmit                                                    |          |

| 3.6.1 Protocol Stacks                                                  |          |

| 3.6.2 Shadow Headers                                                   |          |

| 3.7 Ethernet MAC                                                       |          |

| 3.8 Packet Classification                                              |          |

| 3.8.1 Example Classification Scheme                                    | 40       |

| 3.9 Memory Management Unit                                             |          |

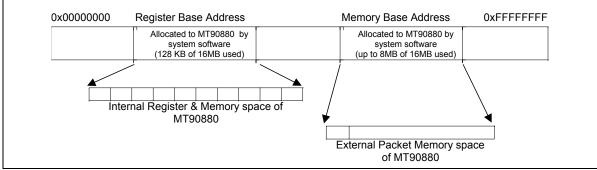

| 3.9.1 External Memory Requirements                                     | 45       |

| 3.9.2 Granule Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

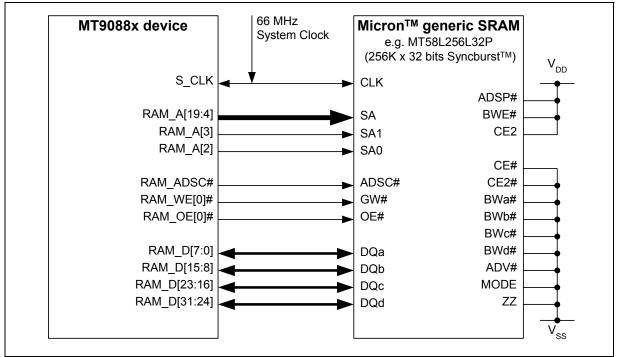

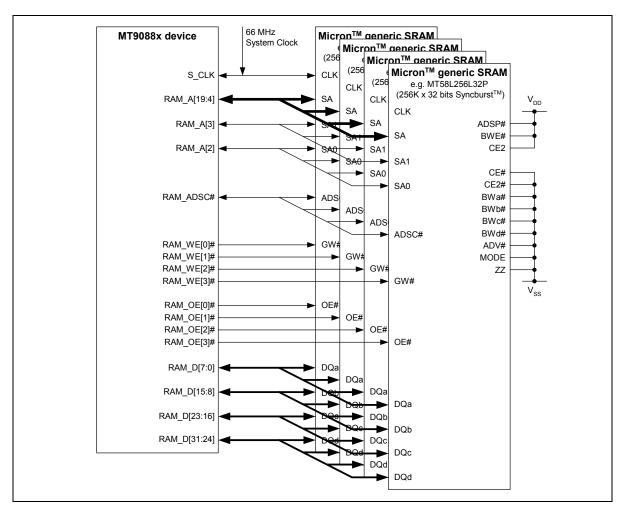

| 3.9.3 Connecting the MT9088x to external memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                        |

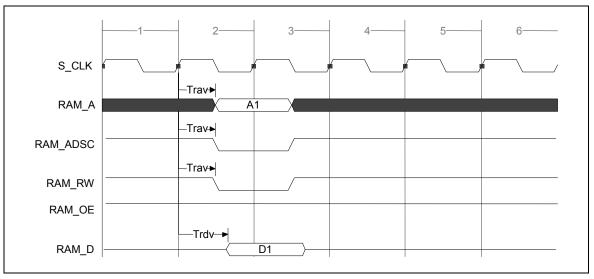

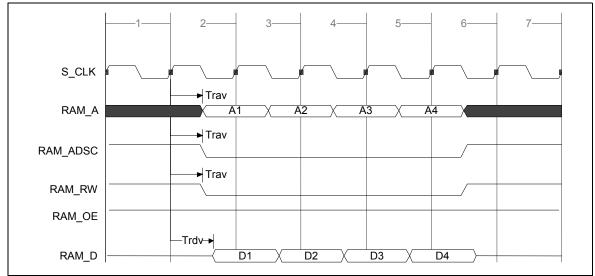

| 3.9.4 External Memory Interface Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                        |

| 3.10 PCI Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                        |

| 3.10.1 Address and Data Width support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                        |

| 3.10.2 Target Transaction Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                        |

| 3.10.3 Master Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                        |

| 3.10.4 Configuration and Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                        |

| 3.10.5 Signalling environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 51                                                                                                                                                                                                                                                                     |

| 3.11 DMA Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                        |

| 3.11.1 DMA Descriptor Rings and Lists                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                        |

| 3.11.2 Data Transfer from CPU to MT90880                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                        |

| 3.11.3 Data Transfer from MT90880 to CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                        |

| 3.12 Board Level Test Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                        |

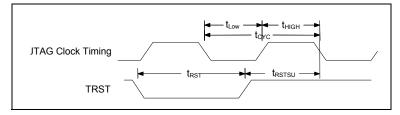

| 3.12.1 JTAG Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                        |

| 3.12.2 Test Access Port (TAP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                        |

| 3.12.3 Test Access Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                        |

| 3.13 DPLL Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                        |

| 3.13.1 Master Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                        |

| 3.13.2 Slave Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                        |

| 3.13.3 Free-run Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                        |

| 3.13.4 DPLL Performance Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                        |

| 4.0 Memory Map and Register definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 59                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                        |

| E O Cussial Note to Heave, MT0000, headling of reactived sorry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ipted Ethernet packets and                                                                                                                                                                                                                                             |

| 5.0 Special Note to Users: MT9088x handling of received corre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                        |

| 5.0 Special Note to Users: MT9088x handling of received corrodealing with the next valid packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                        |

| dealing with the next valid packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59                                                                                                                                                                                                                                                                     |

| dealing with the next valid packet<br>6.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 59<br>Physical Specification60                                                                                                                                                                                                                                         |

| <ul><li>dealing with the next valid packet</li><li>6.0</li><li>7.0 External Interface Description</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Physical Specification60<br>61                                                                                                                                                                                                                                         |

| <ul> <li>dealing with the next valid packet</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>Physical Specification60</b><br><b>61</b><br>                                                                                                                                                                                                                       |

| dealing with the next valid packet         6.0         7.0 External Interface Description         7.1 WAN Access Interface         7.2 Local TDM Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                        |

| dealing with the next valid packet         6.0         7.0 External Interface Description         7.1 WAN Access Interface         7.2 Local TDM Interface         7.3 Packet Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 59<br>Physical Specification60<br>61<br>61<br>                                                                                                                                                                                                                         |

| dealing with the next valid packet<br>6.0<br>7.0 External Interface Description<br>7.1 WAN Access Interface<br>7.2 Local TDM Interface<br>7.3 Packet Interfaces<br>7.3.1 MII Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 59<br>Physical Specification60<br>61<br>61<br>62<br>64<br>64                                                                                                                                                                                                           |

| dealing with the next valid packet<br>6.0<br>7.0 External Interface Description<br>7.1 WAN Access Interface<br>7.2 Local TDM Interface<br>7.3 Packet Interfaces<br>7.3.1 MII Interfaces<br>7.3.2 RMII Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 59<br>Physical Specification60<br>61<br>61<br>62<br>64<br>64<br>64<br>65                                                                                                                                                                                               |

| dealing with the next valid packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59<br>Physical Specification60<br>61<br>61<br>62<br>64<br>64<br>64<br>65<br>66                                                                                                                                                                                         |

| dealing with the next valid packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59<br>Physical Specification60<br>61<br>61<br>62<br>64<br>64<br>65<br>66<br>66<br>67                                                                                                                                                                                   |

| dealing with the next valid packet         6.0         7.0 External Interface Description         7.1 WAN Access Interface         7.2 Local TDM Interface         7.3 Packet Interfaces         7.3.1 MII Interfaces         7.3.2 RMII Interfaces         7.4 PCI Interface         7.5 External Memory Interface         7.6 System Control Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 59<br>Physical Specification60<br>61<br>61<br>62<br>64<br>64<br>64<br>65<br>66<br>66<br>67<br>67                                                                                                                                                                       |

| dealing with the next valid packet         6.0         7.0 External Interface Description         7.1 WAN Access Interface         7.2 Local TDM Interface         7.3 Packet Interfaces         7.3.1 MII Interfaces         7.3.2 RMII Interfaces         7.4 PCI Interface         7.5 External Memory Interface         7.6 System Control Interface         7.7 Test Facilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 59<br>Physical Specification60<br>61<br>61<br>62<br>64<br>64<br>64<br>65<br>66<br>67<br>67<br>67<br>68                                                                                                                                                                 |

| dealing with the next valid packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59<br>Physical Specification60<br>61<br>61<br>62<br>64<br>64<br>64<br>65<br>66<br>67<br>67<br>67<br>68<br>68<br>68                                                                                                                                                     |

| dealing with the next valid packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59<br>Physical Specification60<br>61<br>61<br>62<br>64<br>64<br>64<br>65<br>66<br>67<br>67<br>67<br>68<br>68<br>68<br>68<br>68                                                                                                                                         |

| dealing with the next valid packet         6.0         7.0 External Interface Description         7.1 WAN Access Interface         7.2 Local TDM Interface         7.3 Packet Interfaces         7.3.1 MII Interfaces         7.3.2 RMII Interfaces         7.4 PCI Interface         7.5 External Memory Interface         7.6 System Control Interface         7.7 Test Facilities.         7.7.1 JTAG Interface         7.7.2 Test Facility         7.7.3 Test Operating Modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59<br>Physical Specification60<br>61<br>61<br>62<br>64<br>64<br>65<br>66<br>67<br>67<br>67<br>68<br>68<br>68<br>68<br>68<br>68<br>68<br>68                                                                                                                             |

| dealing with the next valid packet         6.0         7.0 External Interface Description         7.1 WAN Access Interface         7.2 Local TDM Interface         7.3 Packet Interfaces         7.3.1 Mil Interfaces         7.3.2 RMII Interfaces         7.4 PCI Interface         7.5 External Memory Interface         7.6 System Control Interface         7.7.1 JTAG Interface         7.7.2 Test Facility         7.7.3 Test Operating Modes         7.8 Power and Ground Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 59<br>Physical Specification60<br>61<br>62<br>64<br>64<br>65<br>66<br>66<br>67<br>67<br>67<br>68<br>68<br>68<br>68<br>68<br>68<br>70                                                                                                                                   |

| dealing with the next valid packet         6.0         7.0 External Interface Description         7.1 WAN Access Interface         7.2 Local TDM Interface         7.3 Packet Interfaces         7.3.1 Mil Interfaces         7.3.2 RMII Interfaces         7.4 PCI Interface         7.5 External Memory Interface         7.6 System Control Interface         7.7.1 JTAG Interface         7.7.2 Test Facility         7.7.3 Test Operating Modes         7.8 Power and Ground Connections         8.0 DC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 59<br>Physical Specification60<br>61<br>62<br>64<br>64<br>65<br>66<br>66<br>67<br>67<br>67<br>67<br>67<br>67<br>67<br>67<br>67<br>67<br>67                                                                                                                             |

| dealing with the next valid packet         6.0         7.0 External Interface Description         7.1 WAN Access Interface         7.2 Local TDM Interface         7.3 Packet Interfaces         7.3.1 Mil Interfaces         7.3.2 RMII Interfaces         7.4 PCI Interface         7.5 External Memory Interface         7.6 System Control Interface         7.7.1 JTAG Interface         7.7.2 Test Facility         7.7.3 Test Operating Modes         7.8 Power and Ground Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 59<br>Physical Specification60<br>61<br>62<br>64<br>64<br>65<br>66<br>66<br>67<br>67<br>67<br>67<br>67<br>67<br>67<br>67<br>67<br>67<br>67                                                                                                                             |

| dealing with the next valid packet         6.0         7.0 External Interface Description         7.1 WAN Access Interface         7.2 Local TDM Interface         7.3 Packet Interfaces         7.3.1 Mil Interfaces         7.3.2 RMII Interfaces         7.4 PCI Interface         7.5 External Memory Interface         7.6 System Control Interface         7.7.1 JTAG Interface         7.7.2 Test Facility         7.7.3 Test Operating Modes         7.8 Power and Ground Connections         8.0 DC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 59<br>Physical Specification60<br>61<br>61<br>62<br>64<br>64<br>65<br>66<br>66<br>67<br>67<br>67<br>67<br>67<br>67<br>67<br>67<br>70<br>70<br>71                                                                                                                       |

| dealing with the next valid packet         6.0         7.0 External Interface Description         7.1 WAN Access Interface         7.2 Local TDM Interface         7.3 Packet Interfaces         7.3.1 MII Interfaces         7.3.2 RMII Interfaces         7.4 PCI Interface         7.5 External Memory Interface         7.6 System Control Interface         7.7 Test Facilities         7.7.1 JTAG Interface         7.7.2 Test Facility         7.7.3 Test Operating Modes         7.8 Power and Ground Connections         8.0 DC Characteristics         8.1 Recommended Operating Conditions - Voltage measurements are with                                                                                                                                                                                                                                                                                                                                                             | 59<br>Physical Specification60<br>61<br>61<br>62<br>64<br>64<br>65<br>66<br>67<br>67<br>67<br>67<br>67<br>67<br>67<br>67<br>67<br>70<br>70<br>70<br>70<br>71<br>respect to ground (VSS) unless                                                                         |

| dealing with the next valid packet         6.0         7.0 External Interface Description         7.1 WAN Access Interface         7.2 Local TDM Interface         7.3 Packet Interfaces.         7.3.1 MII Interfaces         7.3.2 RMII Interfaces         7.4 PCI Interface.         7.5 External Memory Interface         7.6 System Control Interface         7.7 Test Facilities.         7.7.1 JTAG Interface         7.7.2 Test Facility         7.7.3 Test Operating Modes.         7.8 Power and Ground Connections         8.0 DC Characteristics         8.1 Recommended Operating Conditions - Voltage measurements are with otherwise stated.71         8.2 DC Characteristics.         8.2.1 Input Levels.                                                                                                                                                                                                                                                                         | 59<br>Physical Specification60<br>61<br>61<br>62<br>64<br>64<br>65<br>66<br>67<br>67<br>67<br>68<br>68<br>68<br>68<br>68<br>70<br>70<br>70<br>71<br>respect to ground (VSS) unless<br>72<br>72                                                                         |

| dealing with the next valid packet         6.0         7.0 External Interface Description         7.1 WAN Access Interface         7.2 Local TDM Interface         7.3 Packet Interfaces         7.3.1 MII Interfaces         7.3.2 RMII Interfaces         7.4 PCI Interface         7.5 External Memory Interface         7.6 System Control Interface         7.7 Test Facilities         7.7.1 JTAG Interface         7.7.2 Test Facility         7.7.3 Test Operating Modes         7.8 Power and Ground Connections         8.0 DC Characteristics         8.1 Recommended Operating Conditions - Voltage measurements are with otherwise stated.71         8.2 DC Characteristics                                                                                                                                                                                                                                                                                                          | 59<br>Physical Specification60<br>61<br>61<br>62<br>64<br>64<br>65<br>66<br>67<br>67<br>67<br>68<br>68<br>68<br>68<br>68<br>70<br>70<br>70<br>71<br>respect to ground (VSS) unless<br>72<br>72                                                                         |

| dealing with the next valid packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59<br>Physical Specification60<br>61<br>61<br>62<br>64<br>64<br>65<br>66<br>67<br>67<br>67<br>68<br>68<br>68<br>68<br>68<br>68<br>70<br>70<br>71<br>respect to ground (VSS) unless<br>72<br>72<br>72                                                                   |

| dealing with the next valid packet         6.0         7.0 External Interface Description         7.1 WAN Access Interface         7.2 Local TDM Interface         7.3 Packet Interfaces         7.3.1 MII Interfaces         7.3.2 RMII Interfaces         7.4 PCI Interface         7.5 External Memory Interface         7.6 System Control Interface         7.7 Test Facilities         7.7.1 JTAG Interface         7.7.2 Test Facility         7.7.3 Test Operating Modes         7.8 Power and Ground Connections         8.0 DC Characteristics         8.1 Recommended Operating Conditions - Voltage measurements are with otherwise stated.71         8.2 DC Characteristics         8.2.1 Input Levels         8.2.2 Output Levels         8.0                                                                                                                                                                                                                                       | 59<br>Physical Specification60<br>61<br>61<br>62<br>64<br>64<br>65<br>66<br>67<br>67<br>67<br>68<br>68<br>68<br>68<br>68<br>68<br>70<br>70<br>71<br>respect to ground (VSS) unless<br>72<br>72<br>72<br>72<br>                                                         |

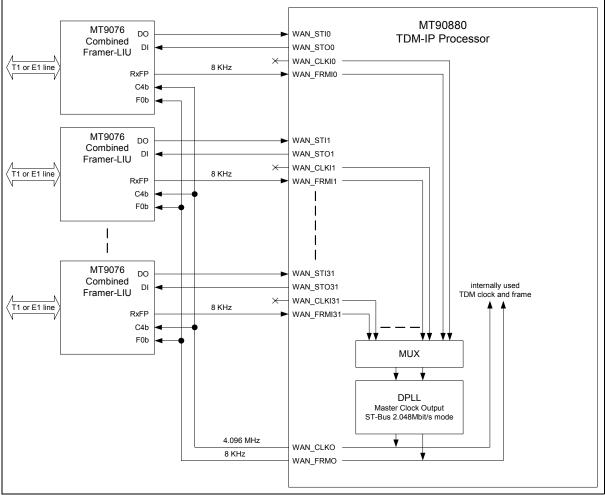

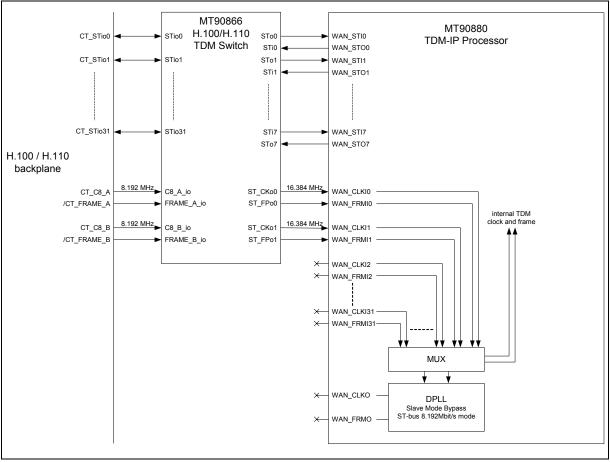

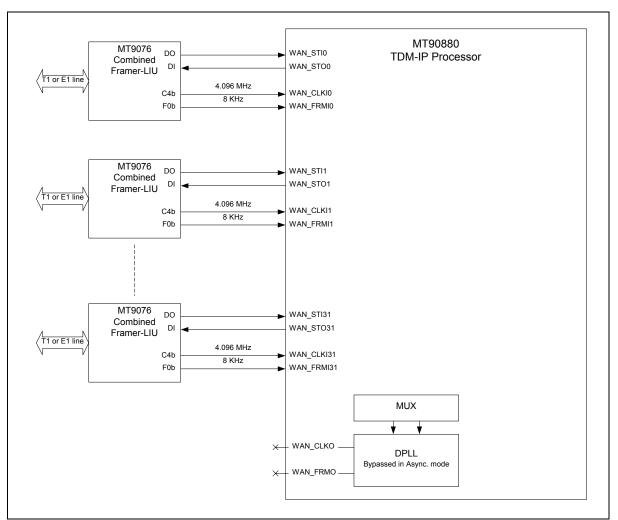

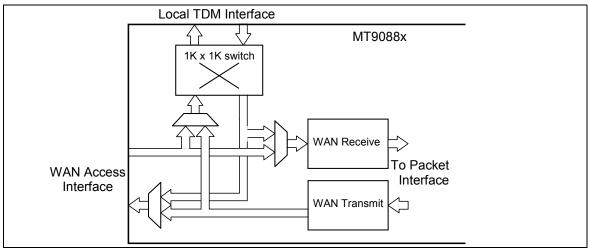

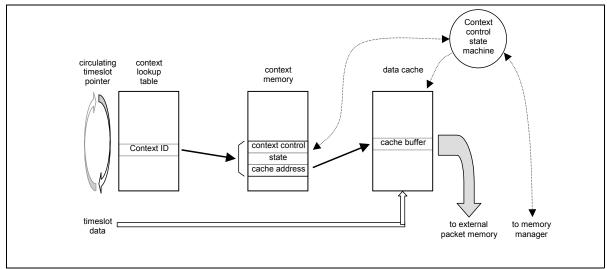

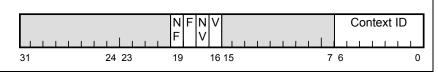

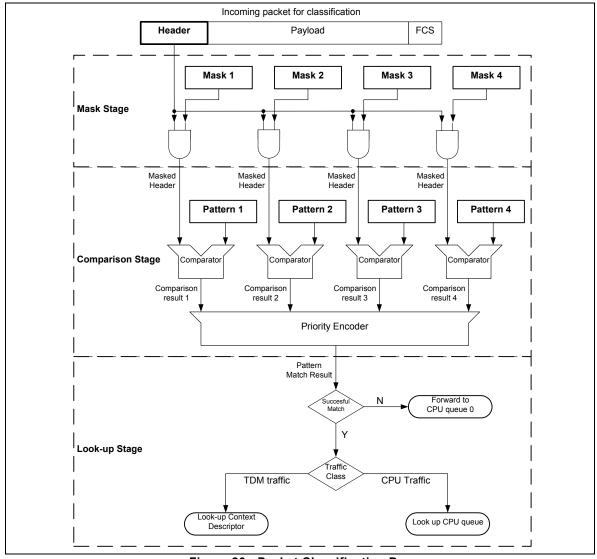

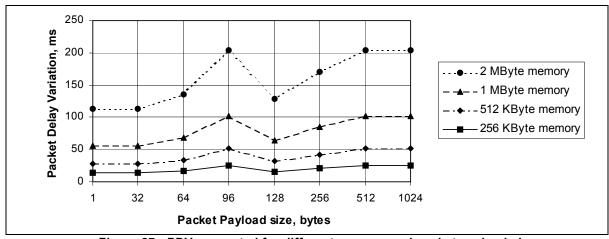

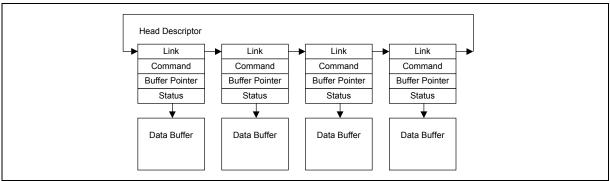

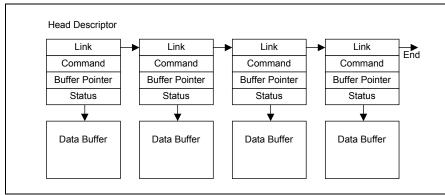

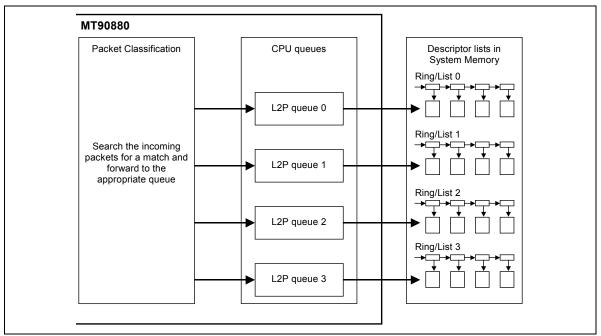

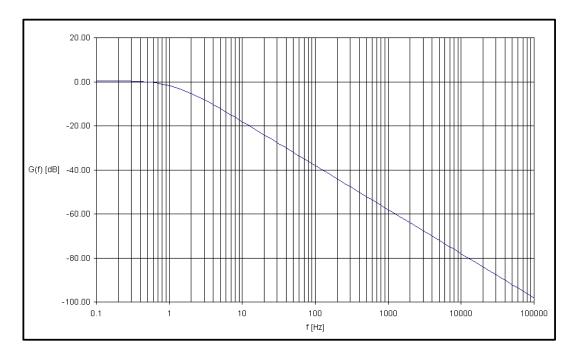

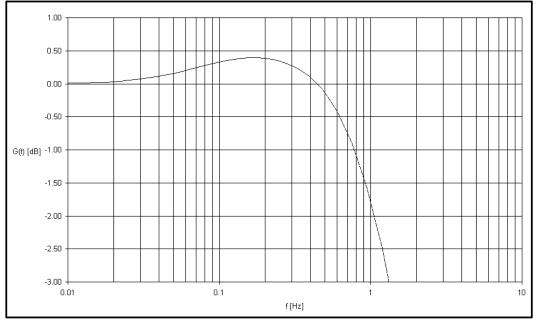

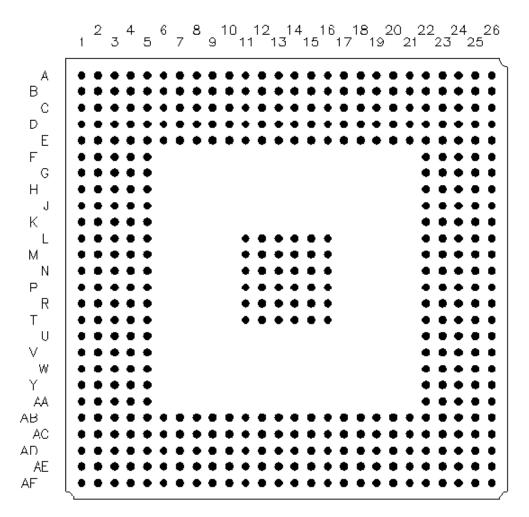

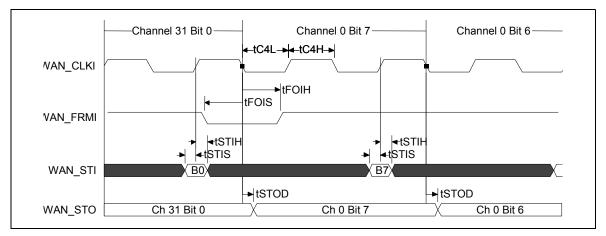

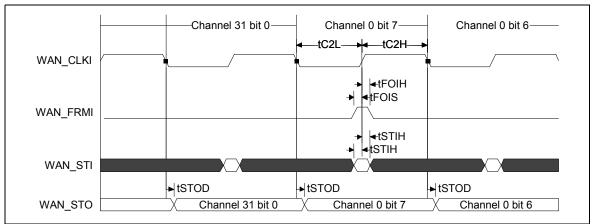

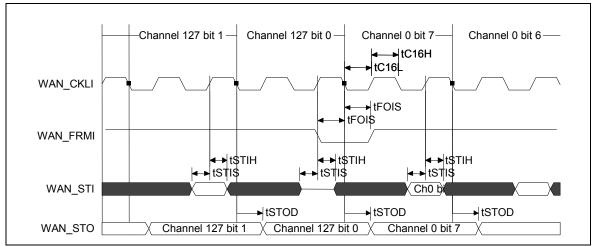

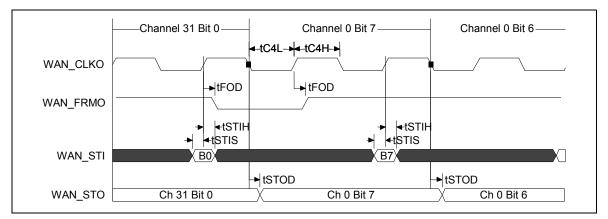

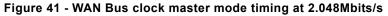

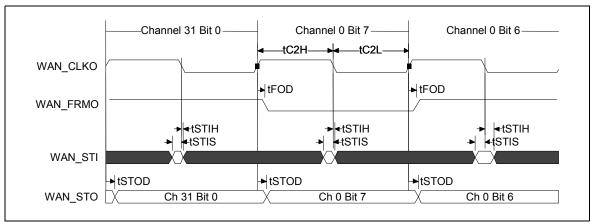

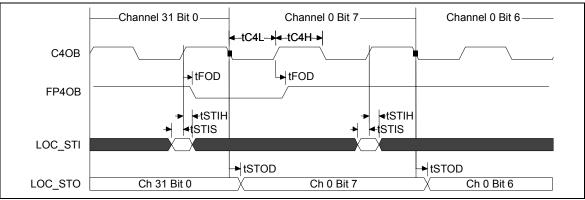

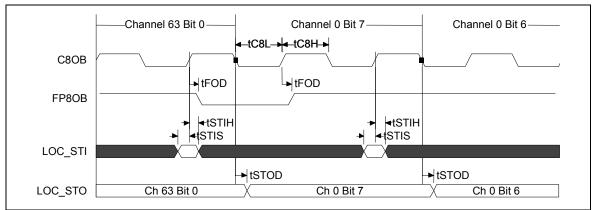

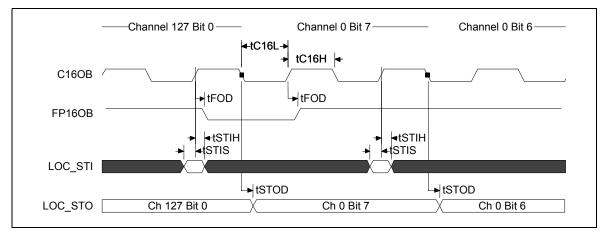

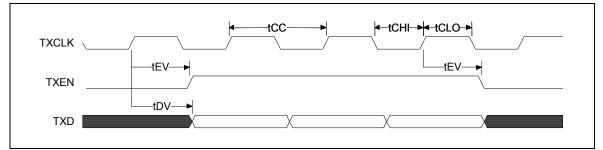

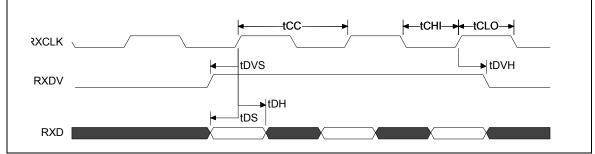

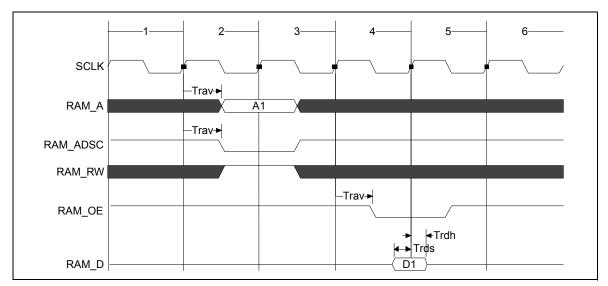

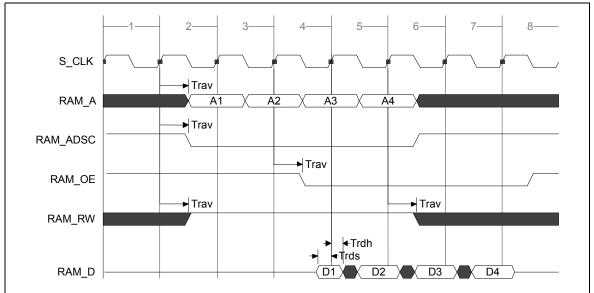

| dealing with the next valid packet         6.0         7.0 External Interface Description         7.1 WAN Access Interface         7.2 Local TDM Interface         7.3 Packet Interfaces         7.3.1 MII Interfaces         7.3.2 RMII Interfaces         7.3.2 RMII Interface         7.4 PCI Interface         7.5 External Memory Interface         7.6 System Control Interface         7.7.1 JTAG Interface         7.7.1 JTAG Interface         7.7.2 Test Facilities.         7.7.3 Test Operating Modes.         7.8 Power and Ground Connections         8.0 DC Characteristics         8.1 Recommended Operating Conditions - Voltage measurements are with otherwise stated.71         8.2 DC Characteristics.         8.2.1 Input Levels.         8.2.2 Output Levels.         8.2.2 Output Levels.         8.1 WAN Access Interface.                                                                                                                                               | 59<br>Physical Specification60<br>61<br>61<br>62<br>64<br>64<br>65<br>66<br>66<br>67<br>67<br>67<br>68<br>68<br>68<br>68<br>68<br>68<br>69<br>70<br>                                                                                                                   |