T-1 PCM Devices

## R8050 T-1 SERIAL TRANSMITTER

#### **DESCRIPTION**

The Rockwell T-1 Serial Transmitter formats data to be serially transmitted according to T-1 D2 or T-1 D3 specifications, inserting framing and signalling bits along with 24 channels of 8-bit channel data. The T-1 Serial Transmitter also provides for alarm reporting via the Bit 2 inhibit method or, with minimal external logic, via the multiframe alignment signal ( $F_{\rm S}$ ) modification method.

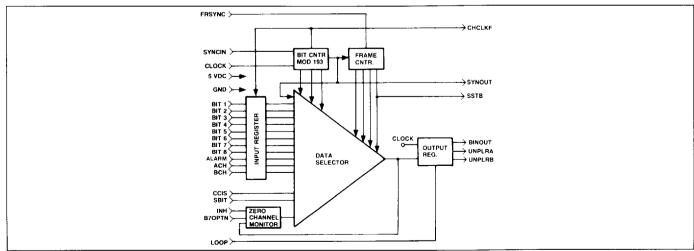

Figure 1 is a functional block diagram of the T-1 Serial Transmitter. The Mod 193 counter is driven by the clock at 1.544 MHz and is either synchronized to the driving system by input signal SYNCIN or provides synchronization via output signal SYNOUT. Input signal FRSYNC applies synchronization to a Mod 12 counter, which identifies the frame of the 12-frame multiframe being processed.

The input data register latches data during each bit period, when the 8th bit of a channel sample is being transmitted. The data selector outputs the proper sequence of bits, as controlled by a bit count and frame count.

The zero channel monitor function causes Bit 8 or Bit 7 to be transmitted as a "one" if the channel data sample is all "zeros." Input INH provides a means to inhibit the zero channel monitor function. Input B70PTN controls the particulars of the insertion method.

Two types of transmit formats are provided, a binary output and a paired unipolar output. The unipolar pair provides a means to externally create a single bipolar output with minimal logic.

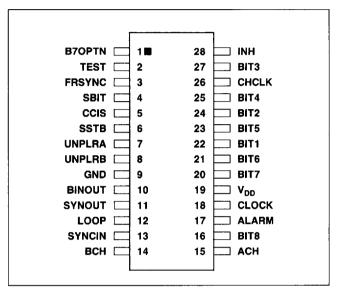

Pin Configuration

#### **FEATURES**

- Single 5V supply, low power Schottky TTL compatible.

- · Accepts 8 bits of parallel data as input.

- Generates output as 193 bit serial data stream in T-1, D2, D3 or D4 Mode 3 data format.

- Provides a channel and frame timing signal.

- Provides alternate control for alarm reporting and signalling.

- · Provides automatic bit insertion for all-zero channel samples.

Figure 1. T-1 Serial Transmitter

## T-1 Serial Transmitter

#### T-1 TRANSMITTER INPUTS

Any input  $\leq 0.8V = \log c 0$ , low. Any input  $\geq 2.0V = \log c 1$ , high. The transition from a low level to a high level is called a rising edge, while the converse is defined as a falling edge.

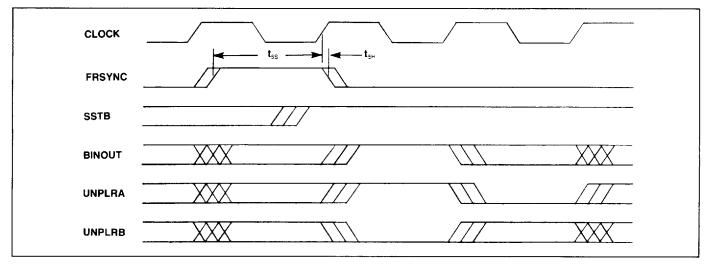

#### FRSYNC: FRAME SYNCHRONIZATION

Frame sync allows external synchronization of the transmitter's internal frame counter. When FRSYNC becomes high, the frame counter is directly set to frame 1, the first of the twelve frames. If FRYSYNC is held high and does not return to zero before a rising edge of CLOCK, the subsequent states of BINOUT. UNPLRA and UNPLRB are high, high and low, respectively, regardless of the states of any other inputs. The latter mechanism is useful for device and/or board testing only and will cause bit errors and/or bipolar violations if used during field operations. See Figures 6 and 7.

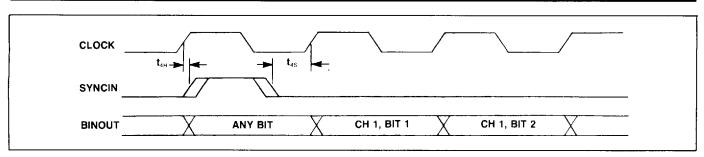

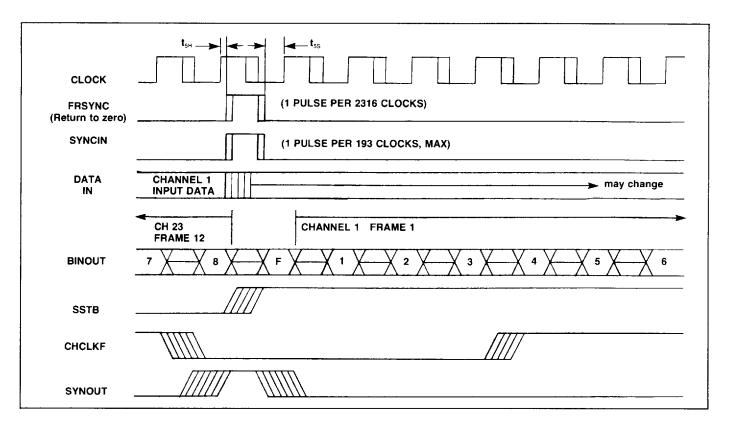

#### SYNCIN: SYNCHRONIZATION INPUT

SYNCIN allows external synchronization of the internal Modulo 193 bit/channel counter. When SYNCIN becomes high, the Modulo 193 counter is directly set to the state corresponding to the output of the framing (FT or FS) bit. The first bit of channel one will be output on BINOUT (and UNPLRA or UNPLRB) as a result of the first rising edge of CLOCK following the return of SYNCIN to logic 0. See Figures 5 and 7.

#### **TEST: ROCKWELL DEVICE TEST INPUT**

Used only for Rockwell device testing. Keep this input grounded.

#### CLOCK: T-1 CLOCK

Maximum frequency = 1.6 MHz Minimum pulse width = 275 ns

The T-1 bit period is bounded by the rising edges of this input.

#### **INH: INHIBIT ZERO CHANNEL MONITOR**

If INH is high, the zero channel monitor function is disabled, and Bits 7 and 8 are transmitted per corresponding inputs received. See Table 1.

For channels in signalling frames (6 or 12) in which the first six data bits and the signalling highway are all "zero," BIT 7 will be forced to one if INH is low. For any frame except a signalling frame Bit 8 or Bit 7 as selected by B7OPTN will be transmitted as a "one" if the channel input data is "zero" and INH is low.

#### BITS 1-8: PARALLEL CHANNEL DATA INPUTS

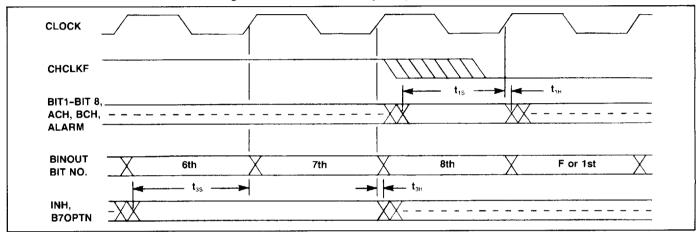

Bit 1, the sign bit, will be serially transmitted first, followed by Bits 2 through 8. The falling edge of CHCLKF indicates input channel data has been clocked into the input register and always occurs during the transmission of the final bit (Bit 8) of each channel data sample.

## ACH: "A" CHANNEL HIGHWAY SIGNALLING

ACH allows the user to transmit one bit of signalling per channel as Bit 8 of each channel data sample in Frame 6 only. ACH is clocked into the input register by the falling edge of CHCLKF. Refer to Table 1 and Figure 4.

#### BCH: "B" CHANNEL HIGHWAY SIGNALLING

BCH allows the user to transmit one bit of signalling per channel as Bit 8 of each channel data sample in Frame 12 only. BCH is clocked into the input register by the falling edge of CHCLKF. Refer to Table 1 and Figure 4.

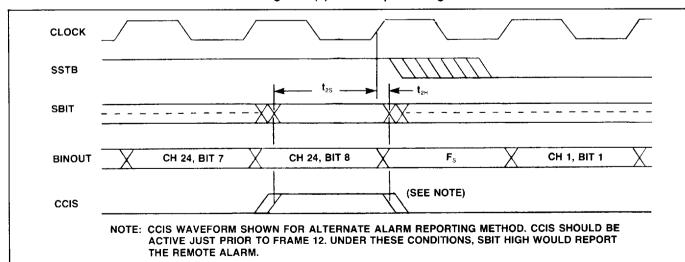

#### S-BIT: MULTIFRAME SIGNALLING BIT

SBIT, in conjunction with CCIS, provides an alternate way to control the multiframe signalling bit (Fs) transmission. The S-Bit input is transmitted as the multiframe signalling bit (Fs) if CCIS is held high. Refer to Table 2.

#### **ALARM: LOCAL ALARM**

Used for reporting alarm conditions. If the ALARM signal is high, Bit 2 (the most-significant bit) of every channel data sample of every frame is transmitting as a zero. This is commonly called remote alarm signalling. ALARM is clocked into the input register at the falling edge of CHCLKF. Refer to Table 1 and Figure 4.

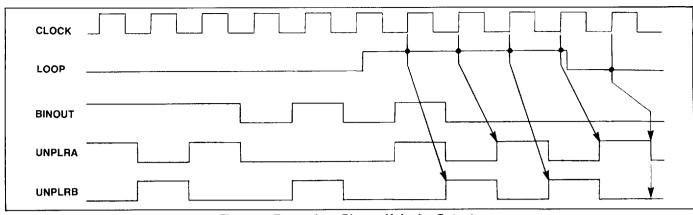

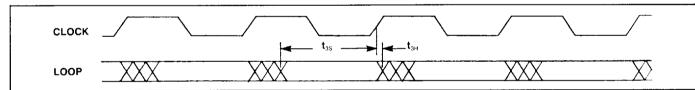

#### LOOP: LOOP STRAP

Provided to aid testing of user applications. When enabled to a high level, LOOP forces the unipolar outputs to transmit alternating ones and zeros, regardless of input conditions, while BINOUT continues to provide normal data outputs. Refer to Figure 3.

#### CCIS: COMMON CHANNEL INTEROFFICE SIGNALLING STRAP

Provides optional control for replacing the automatic F<sub>S</sub> pattern with a 4-kilobit common channel signalling path. When CCIS is high, the SBIT input replaces the FS pattern and the insertion of ACH and BCH is suspended. The CCIS input may also be used to provide the alternate method of alarm reporting. See Figure 4.

#### **B70PTN: BIT 7 OPTION**

Provides Bit 7 as an alternate bit position for "one" stuffing, as programmed by the zero channel monitor function. Refer to Table 1.

#### VSS, VDD: GROUND AND POWER

$V_{DD} = +5 \pm 0.25 \text{ Vdc}$  $V_{SS}$  = Ground, 0 Vdc

### **T-1 TRANSMITTER OUTPUTS**

Low power TTL Schottky compatible. "1" ≥ 2.4 Vdc, "0" ≤ 0.4 Vdc, CMOS —  $12K\Omega$  pullup to  $V_{DD}$  required.

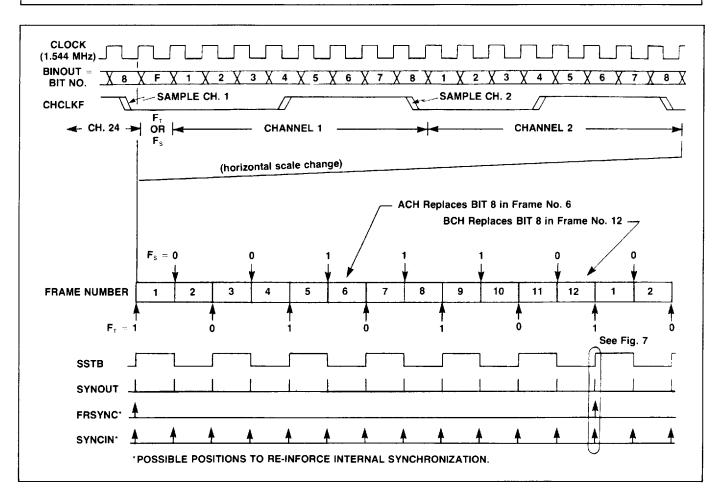

#### SSTB: 4 kHz SIGNALLING CHANNEL STROBE

SSTB is the least-significant bit of the frame counter. Unless it is directly set by FRSYNC, SSTB will go high as each framing bit (F<sub>T</sub>) is serially transmitted, and will return low as each multiframe alignment signal (FS) is transmitted. Refer to Figure 2.

#### SYNOUT: CHANNEL SYNC OUTPUT

SYNOUT provides a means to synchronize to the internal bit counter (Mod 193). SYNOUT is high for one bit time, beginning just prior to the first data bit of a frame being serially transmitted. Refer to Figure 7. SYNOUT is the only output determined by the falling edge of CLOCK.

## **T-1 Serial Transmitter**

#### **CHCLKF: CHANNEL CLOCK FALSE**

The falling edge of CHCLKF, occurring as Bit 8 of any channel is being serially transmitted, indicates input data has been clocked into the input register. With the exception of an extra bit period extending the low level duration at frame bit time, CHCLKF is a divide-by-eight of CLOCK. Refer to Figure 2.

## BINOUT: SERIAL DATA OUTPUT, BINARY FORMATTED

BINOUT is the binary formatted serial conversion of the parallel input data. The programmed format of BINOUT follows Tables 1 and 2

BINOUT is synchronously transmitted as a high level if FRSYNC remains high during the rising edge of CLOCK. Refer to Figures 6 and 7.

## UNPLRA, UNPLRB: T-1 SERIAL DATA UNIPOLAR OUTPUTS

Two paired unipolar outputs are provided for the purpose of creating a single serial data output transmission in bipolar format. The unipolar output register toggles for each "one" bit to be serially transmitted. UNPLRA and UNPLRB are transmitted as complements for "one" data bits and as low levels for "zero" data bits. See Figure 3.

The input signal LOOP, if high, forces the unipolar outputs to toggle every bit time, regardless of input data.

FRSYNC perturbs the current bits being transmitted by UNPLRA and UNPLRB. If FRSYNC remains high during the rising edge of CLOCK, UNPLRA will be transmitted as a high level and UNPLRB will be low. Refer to Figures 6 and 7.

Table 1. Serial Channel Sample Output Data Truth Table

|       | Inputs X = don't care |            |     |     |     |     | · · · · · · · · · · · · · · · · · · · | Binout |     |     |     |     |                            |                                      |   |   |   |   |       |   |   |     |

|-------|-----------------------|------------|-----|-----|-----|-----|---------------------------------------|--------|-----|-----|-----|-----|----------------------------|--------------------------------------|---|---|---|---|-------|---|---|-----|

| ALARM | <b>T</b>              | B70PTN     | T 1 | Т2  | Т 3 | T 4 | T 5                                   | т 6    | Т 7 | T 8 | АСН | 天   | Current<br>Frame<br>Number | Serial Output  Channel  Bit Position |   |   |   |   | Notes |   |   |     |

| AL    | H                     | <b>B</b> 7 | BIT | BIT | BIT | ВІТ | BIT                                   | BIT    | ш   | ВІТ | ¥   | BCH |                            | 1 2 3 4 5 6 7 8                      |   |   |   |   |       |   |   |     |

| 1     | х                     | Х          | Х   | ×   | Х   | X   | X                                     | ×      | X   | х   | Х   | Х   | Х                          | Х                                    | 0 | х | Х | Х | Х     | Х | х | 1   |

| Х     | Х                     | Х          | Х   | 0   | Х   | Х   | Х                                     | Х      | Х   | х   | Х   | Х   | Х                          | Х                                    | 0 | Х | Х | Х | Х     | Х | Х | 1   |

| 0     | Х                     | Х          | Р   | Q   | R   | S   | Т                                     | U      | ٧   | Х   | Α   | Х   | 6                          | P                                    | Q | R | S | Т | U     | V | Α | 2   |

| 0     | Х                     | Х          | Р   | Q   | R   | S   | Т                                     | υ      | ٧   | Х   | Х   | В   | 12                         | P                                    | Q | R | S | Т | U     | V | В | 2   |

| 0     | Х                     | Х          | Р   | Q   | R   | s   | Т                                     | U      | ٧   | w   | Х   | Х   | Υ                          | Р                                    | Q | R | S | T | U     | ٧ | w | 2,3 |

| 0     | 1                     | Х          | 0   | 0   | 0   | 0   | 0                                     | 0      | 0   | х   | Α   | х   | 6                          | 0                                    | 0 | 0 | 0 | 0 | 0     | 0 | Α |     |

| 0     | 1                     | Х          | 0   | 0   | 0   | 0   | 0                                     | 0      | 0   | х   | Х   | В   | 12                         | 0                                    | 0 | 0 | 0 | 0 | 0     | 0 | В |     |

| 0     | 1                     | Х          | 0   | 0   | 0   | 0   | 0                                     | 0      | 0   | W   | Х   | Х   | Υ                          | 0                                    | 0 | 0 | 0 | 0 | 0     | 0 | W | 3   |

| 0     | 0                     | Х          | 0   | 0   | 0   | 0   | 0                                     | 0      | 0   | Х   | 0   | Х   | 6                          | 0                                    | 0 | 0 | 0 | 0 | 0     | 1 | 0 |     |

| 0     | 0                     | х          | 0   | 0   | 0   | 0   | 0                                     | 0      | 0   | х   | Х   | 0   | 12                         | 0                                    | 0 | 0 | 0 | 0 | 0     | 1 | 0 |     |

| 0     | 0                     | 1          | 0   | 0   | 0   | 0   | 0                                     | 0      | 0   | 0   | х   | Х   | Y                          | 0                                    | 0 | 0 | 0 | 0 | 0     | 1 | 0 | 3   |

| 0     | 0                     | 0          | 0   | 0   | 0   | 0   | 0                                     | 0      | 0   | 0   | Х   | Х   | Y                          | 0                                    | 0 | 0 | 0 | 0 | 0     | 0 | 1 | 3   |

NOTES: (1) ALARM = 1 has the same effect as BIT 2 = 0

(2) P, Q, R, S, T, U and V may not simultaneously be zero, unles A, B or W is 1

(3) Y is any frame  $\neq$  6 and  $\neq$  12 with CCIS = 0, or all frames with CCIS = 1

## **T-1 Serial Transmitter**

Table 2. Framing Bit (F<sub>T</sub> & F<sub>S</sub>) Output Data

| Frame  | Processed      | Binout     |          |  |  |  |

|--------|----------------|------------|----------|--|--|--|

| Number | Bit            | CCIS = 0   | CCIS = 1 |  |  |  |

| 1      | F <sub>T</sub> | 1          | 1        |  |  |  |

| 2      | Fs             | 0          | SBIT     |  |  |  |

| 3      | F <sub>T</sub> | 0          | 0        |  |  |  |

| 4      | Fs             | 0          | SBIT     |  |  |  |

| 5      | F <sub>T</sub> | 1          | 1        |  |  |  |

| 6      | F <sub>s</sub> | 1          | SBIT     |  |  |  |

| 7      | F <sub>T</sub> | 0          | 0        |  |  |  |

| 8      | Fs             | 1          | SBIT     |  |  |  |

| 9      | F <sub>T</sub> | 1          | 1        |  |  |  |

| 10     | Fs             | 1          | SBIT     |  |  |  |

| 11     | F <sub>T</sub> | 0          | 0        |  |  |  |

| 12     | Fs             | 0 (NOTE 1) | SBIT     |  |  |  |

Notes: (1) Alternate remote alarm reporting may be accomplished by holding SBIT and CCIS both high just prior to initiation of Frame 12.

(2)  $F_T$  bit insertion is automatic and no optional control is provided.

Figure 2. Transmitter Input-Output Signal Relationships

## **T-1 Serial Transmitter**

Figure 3. Transmitter Binary, Unipolar Outputs

Figure 4 (a). Channel Input Timing

Figure 4 (b). LOOP Input Timing

Figure 4 (c). Control Input Timing

## **T-1 Serial Transmitter**

Figure 5. SYNCIN Timing Relationship

Figure 6. Non-return-to-zero FRSYNC Timing

Figure 7. Transmitter External Synchronization (Return-to-zero FRSYNC)

## **T-1 Serial Transmitter**

Table 3. Input Timing

| Symbol          | Parameter                                  | Min | Max | Unit |

|-----------------|--------------------------------------------|-----|-----|------|

| t <sub>1S</sub> | Buffered Data Setup Time                   | 450 |     | ns   |

| t <sub>1H</sub> | Buffered Data Hold Time                    | 0   |     | ns   |

| t <sub>2S</sub> | Control Input Setup Time                   | 400 |     | ns   |

| t <sub>2H</sub> | Control Input Hold Time                    | 20  |     | ns   |

| t <sub>3S</sub> | Asynchronous Control Input Setup Time      | 350 |     | ns   |

| t <sub>3H</sub> | Asynchronous Control Input Hold Time       | 20  |     | ns   |

| t <sub>4S</sub> | SYNCIN Setup Time                          | 200 |     | ns   |

| t <sub>4H</sub> | SYNCIN Hold Time                           | 20  |     | ns   |

|                 | SYNCIN Pulse Width                         | 100 |     | ns   |

| t <sub>5S</sub> | Frame Sync Setup Time (Return to Zero)     | 250 |     | ns   |

| t <sub>5H</sub> | Frame Sync Hold Time (Return to Zero)      | 20  |     | ns   |

|                 | Frame Sync Pulse Width                     | 200 |     | ns   |

| t <sub>5S</sub> | Frame Sync Setup Time (Non-Return to Zero) | 525 |     | ns   |

| t <sub>sH</sub> | Frame Sync Hold Time (Non-Return to Zero)  | 20  |     | ns   |

#### Table 4. Output Propagation Delay, Worst Case (Measured from Rising Edge of Clock Unless Stated Otherwise)

| Output           | Max Delay | Unit |

|------------------|-----------|------|

| SSTB             | 500       | ns   |

| SYNOUT           | 500       | ns   |

| Ref from Falling |           |      |

| Edge of Clock    |           |      |

| CHCLKF           | 500       | ns   |

| BINOUT           | 500       | ns   |

| UNPLRA           | 500       | ns   |

| UNPLRB           | 500       | ns   |

## **MAXIMUM RATINGS\***

| Parameter             | Symbol           | Value          | Unit |

|-----------------------|------------------|----------------|------|

| Supply Voltage        | V <sub>DD</sub>  | +4.75 to +5.25 | Vdc  |

| Operating Temperature | T <sub>OP</sub>  | 0 to 70        | °C   |

| Storage Temperature   | T <sub>STG</sub> | - 55 to + 150  | °C   |

\*NOTE: Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in other sections of this document is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 5.0 \pm 5\%)$

| Parameter                     | Symbol          | Min   | Max                   | Unit |

|-------------------------------|-----------------|-------|-----------------------|------|

| Logical "1" Input Voltage     | V <sub>OH</sub> | 2.0   | V <sub>DD</sub> + 0.3 | V    |

| Logicical "0" Input Voltage   | V <sub>IL</sub> | -0.3  | 0.8                   | V    |

| Logicical "1" Output Voltage  | V <sub>OH</sub> | 2.4   |                       | V    |

| Logic "0" Output Voltage      | V <sub>OL</sub> | _     | 0.4                   | V    |

| Output Source Current         | Гон             | - 100 | _                     | μΑ   |

| Output Sink Current           | loL             | 400   | -                     | μΑ   |

| Capacitance Load (any output) | С               | _     | 25                    | pF   |

| Input Capacitance (any input) | C <sub>IN</sub> | _     | 5                     | pF   |

| Clock Frequency               |                 | _     | 1.6                   | MHz  |

| Power Dissipation             | P <sub>D</sub>  | _     | 250                   | mW   |

## T-1 Serial Transmitter

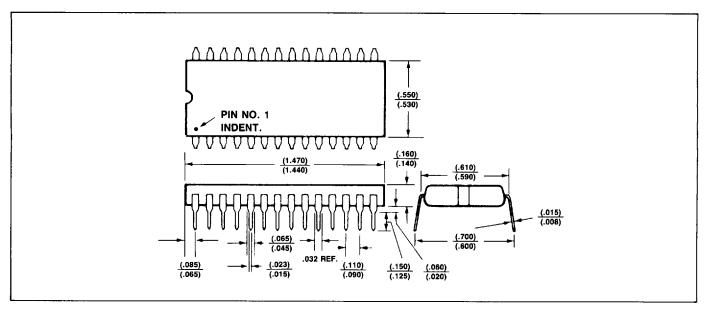

#### PACKAGE DIMENSIONS

Information furnished by Rockwell International Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Rockwell International for its use, nor any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of Rockwell International other than for circuitry embodied in Rockwell products. Rockwell International reserves the right to change circuitry at any time without notice. This document is subject to change without notice

#### **ROCKWELL COMMUNICATION SYSTEMS** DIGITAL COMMUNICATIONS REGIONAL SALES OFFICES

Headquarters Rockwell International (Physical Address) 4311 Jamboree Road Newport Beach, CA 92660-3095 (Malling Address) P.O. Box C Newport Beach, CA 92658-8902 (714) 833-4600 (800) 422-4230 (In CA) (800) 854-8099 (Outside CA) FAX: (714) 833-4078 or (714) 833-4391 TWX: (910) 591-1698 TLX: 170653

Rockwell International 2001 N. Collins Blvd. Suite 103 Richardson, TX 75080 (214) 996-6500 FAX: (214) 996-7812 TWX or TLX: (650) 227-9516

Rockwell International 1967 Lakeside Parkway

Tucker, GA 30084

(404) 270-8300 (404) 493-8300

Suite 420

**United States** Rockwell International Rockwell International 4311 Jamboree Road 2700 N. River Road Suite 501-301 Suite 315 Newport Beach, CA 92660-3095 (714) 833-4655 Des Plaines, IL 60018 (708) 297-8862 FAX: (714) 833-6898 FAX: (312) 297-3230

Rockwell International 3375 Scott Blvd. Suite 410 Santa Clara, CA 95054 (408) 980-1900 AX: (408) 980-0744 TWX: (650) 260-6750

**Rockwell International** 5001-B Greentree **Executive Campus** Marlton, NJ 08053 (609) 596-0090 FAX: (609) 596-5681

Rockwell International 239 Littleton Road Suite 1B Westford, MA 01886 (508) 692-7660 FAX: (508) 692-8185 TLX (MCI) 6502512464

Canada Rockwell International 60 Columbia Way Suite 300 Markham, Ontario Canada L3R OC9 (416) 940-2770 FAX: (416) 940-2779

Japan Rockwell International Japan Co., Ltd. Sogo Hanzomon Bldg., 8F 7, Kojimachi 1-chome, Chiyoda-ku Tokyo, Japan 102 (011-81-3) 265-8808 FAX: (011-81-3) 263-0639 TLX: J22198

Asia Pacific Rockwell International 3375 Scott Blvd. Suite 410 Santa Clara, CA 95054 (408) 980-1900 FAX: (408) 727-4643

Rockwell International 30-332 Rutland Road Box Hill, Victoria 3128 Australia (61-3) 890-6999 FAX: (61-3) 898-6437 TLX: AA30450

Rockwell International Rm. 608 Leema Bldg. 146-1 Soosong-Dong Chongro-Ku K.P.O. Box 527 Seoul, Korea (Dept. 553) (82-2) 736-9121 FAX: (82-2) 736-9124 TLX: RCIIK22710

Rockwell International Room 2808 International Trade Building 333 Keelung Road, Section 1 Taipei, Taiwan 10548, R.O.C. (886-2) 720-0282 FAX: (886-2) 757-6808 TLX: 26049 ENTTPE

Rockwell International GmbH Fraunhoferstrasse 11b D-8033 Muenchen-Martinsried Germany (49-89) 857-6016 FAX: (49-89) 857 57 93 TLX: 521-2650 rimd d

United Kingdom Rockwell International Ltd. Central House 3. Lampton Road Hounslow, Middlesex TW3 1HY England (44-1) 577-2800 FAX: (44-1) 577-2257 or (44-1) 570-0758

Rockwell International Tour GAN, 16 Place de l'Iris Certex 13 92082 Paris La Defense 2 France (33-1) 49-06-39-80 FAX: (33-1) 49-06-39-90

South/Central America Rockwell International 4311 Jamboree Road P.O. Box C, MS 501-315 Newport Beach, CA 92660-3095 (714) 833-4532 FAX: (714) 833-4078 TWX: (910) 591-1698

Rockwell International Southwest Sales Office 4311 Jamboree Road Suite 501-301 Newport Beach, CA 92660 (714) 833-4655 FAX: (714) 833-6898

110190