# **OKI** Semiconductor

# MSM60802

#### **PCMCIA Host Interface Controller**

#### DESCRIPTION

The MSM60802 is OKI's first single-chip, highly integrated PC Card (PCMCIA) HostSide™ interface controller, offering compliancy with the PCMCIA 2.1, JEIDA 4.1, and ATA 1.01 industry standards. This device is optimized for usage in notebook and hand-held computers that require low-cost, single-socket support with extremely low power consumption for enhancing battery life. For small-form-factor designs, OKI delivers a minimum board-area solution by eliminating external buffers.

The HostSide<sup>™</sup> controller is unique in several aspects, but most importantly regarding its register and software compatibility to the Intel 82365SL B step IC. Software compatibility significantly simplifies the design process and shortens time-to-market.

Plug-and-play compatibility is becoming more popular with PC Cards. The HostSide™ controller offers seamless transitions through full ExCA™ (QuickSwap) extensions. Another benefit of internal buffers is hot insertion capability.

All necessary registers, decoders, and buffers are integrated to reduce the system form factor and to eliminate discrete components. A comprehensive interface allows device configuration, software setup, and firmware parameter setup by a host (PC) system.

The MSM60802 is manufactured on OKI's high-quality CMOS process, providing unrivaled low-power performance with a 3-V or 5-V operating range. Power-management circuitry further reduces power consumption through active monitoring techniques. In an effort to further reduce board space usage, the HostSide<sup>TM IC</sup> is offered in a 176-pin TQFP package.

#### **FEATURES**

- Single-chip PCMCIA host controller for reduced board space.

- Register- and software-compatible with Intel 82365SL B step PCMCIA controller for simplified design

- Mixed-voltage (3-V and 5-V) support, providing easy transition path

- Direct connection between ISA bus and PCMCIA socket for enhanced performance

- Compliant with PCMCIA 2.1, JEIDA 4.1, and ATA 1.01, facilitating compatibility

- ExCA<sup>™</sup> compatible with hot-insertion compatibility

- Five independent, programmable memory windows per slot, meeting user requirements

- Two independent, programmable I/O windows per slot, simplifying partitioning

- Programmable access cycle timing, enhancing throughput

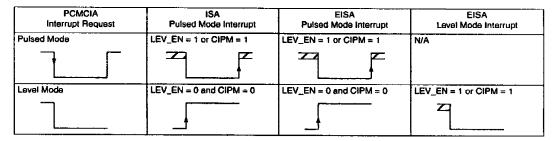

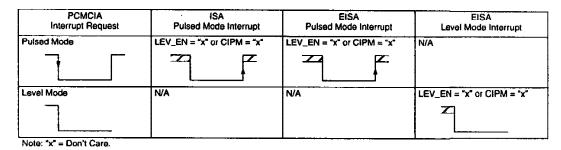

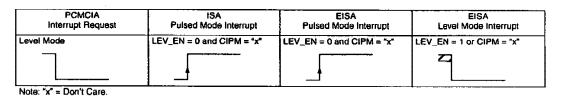

- Pulse- or level-mode interrupts, providing flexibility

- Execute-in-place (XIP) operation

- Programmable sleep modes for increased power savings

- 8-bit or 16-bit PCMCIA and CPU interface support for most architecture variations

- PCMCIA RESET compatibility, reducing design overhead

- 176-pin TQFP package, minimizing board space

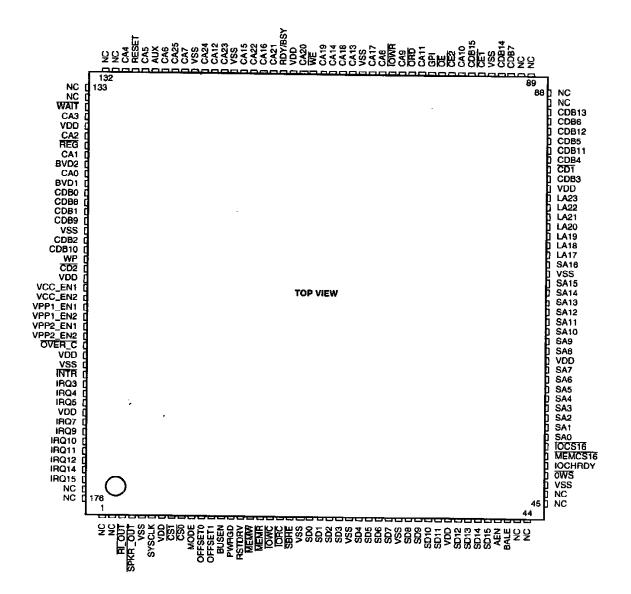

#### **PIN CONFIGURATION**

### **PIN LAYOUT**

| Pin | Pin Name |

|-----|----------|-----|----------|-----|----------|-----|----------|-----|----------|-----|----------|

| 1   | NC       | 31  | VSS      | 61  | SA8      | 91  | CDB7     | 121 | CA12     | 151 | WP       |

| 2   | NC       | 32  | SD8      | 62  | SA9      | 92  | CDB14    | 122 | CA24     | 152 | CD2      |

| 3   | RI_OUT   | 33  | SD9      | 63  | SA10     | 93  | VSS      | 123 | VSS      | 153 | VDD      |

| 4   | SPKR_OUT | 34  | SD10     | 64  | SA11     | 94  | CE1      | 124 | CA7      | 154 | VCC_EN1  |

| 5   | VSS      | 35  | SD11     | 65  | SA12     | 95  | CDB15    | 125 | CA25     | 155 | VCC_EN2  |

| 6   | SYSCLK   | 36  | VDD      | 66  | SA13     | 96  | CA10     | 126 | CA6      | 156 | VPP1_EN1 |

| 7   | VDD      | 37  | SD12     | 67  | SA14     | 97  | CE2      | 127 | AUX      | 157 | VPP1_EN2 |

| 8   | CS1      | 38  | SD13     | 68  | SA15     | 98  | ŌĒ       | 128 | CA5      | 158 | VPP2_EN1 |

| 9   | CS0      | 39  | SD14     | 69  | VSS      | 99  | GPI      | 129 | RESET    | 159 | VPP2_EN2 |

| 10  | MODE     | 40  | SD15     | 70  | SA16     | 100 | CA11     | 130 | CA4      | 160 | OVER_C   |

| 11  | OFFSET 0 | 41  | AEN      | 71  | LA17     | 101 | IORD     | 131 | NC       | 161 | VDD      |

| 12  | OFFSET 1 | 42  | BALE     | 72  | LA18     | 102 | CA9      | 132 | NC       | 162 | VSS      |

| 13  | BUSEN    | 43  | NC       | 73  | LA19     | 103 | TOWR     | 133 | NC       | 163 | INTR     |

| 14  | PWRGD    | 44  | NC       | 74  | LA20     | 104 | CA8      | 134 | NC       | 164 | IRQ3     |

| 15  | RSTDRV   | 45  | NC       | 75  | LA21     | 105 | CA17     | 135 | WAIT     | 165 | IRQ4     |

| 16  | MEMW     | 46  | NC       | 76  | LA22     | 106 | VSS      | 136 | CA3      | 166 | IRQ5     |

| 17  | MEMR     | 47  | VSS      | 77  | LA23     | 107 | CA13     | 137 | VDD      | 167 | VDD      |

| 18  | IOWC     | 48  | ows      | 78  | VDD      | 108 | CA18     | 138 | CA2      | 168 | IRQ7     |

| 19  | IORC     | 49  | IOCHRDY  | 79  | CBD3     | 109 | CA14     | 139 | REG      | 169 | IRQ9     |

| 20  | SBHE     | 50  | MEMCS16  | 80  | CD1      | 110 | CA19     | 140 | CA1      | 170 | IRQ10    |

| 21  | VSS      | 51  | 10CS16   | 81  | CDB4     | 111 | WE       | 141 | BVO2     | 171 | IRQ11    |

| 22  | SD0      | 52  | SA0      | 82  | CDB11    | 112 | CA20     | 142 | CA0      | 172 | IRQ12    |

| 23  | SD1      | 53  | SA1      | 83  | CDB5     | 113 | VDD      | 143 | BVD1     | 173 | IRQ14    |

| 24  | SD2      | 54  | SA2      | 84  | CDB12    | 114 | RDY/BSY  | 144 | CDB0     | 174 | IRQ15    |

| 25  | SD3      | 55  | SA3      | 85  | CDB6     | 115 | CA21     | 145 | CDB8     | 175 | NC       |

| 26  | VSS      | 56  | SA4      | 86  | CDB13    | 116 | CA16     | 146 | CDB1     | 176 | NC       |

| 27  | SD4      | 57  | SA5      | 87  | NC       | 117 | CA22     | 147 | CDB9     |     |          |

| 28  | SD5      | 58  | SA6      | 88  | NC       | 118 | CA15     | 148 | VSS      |     |          |

| 29  | SD6      | 59  | SA7      | 89  | NC       | 119 | VSS      | 149 | CDB2     |     |          |

| 30  | SD7      | 60  | VDD      | 90  | NC       | 120 | CA23     | 150 | CDB10    |     |          |

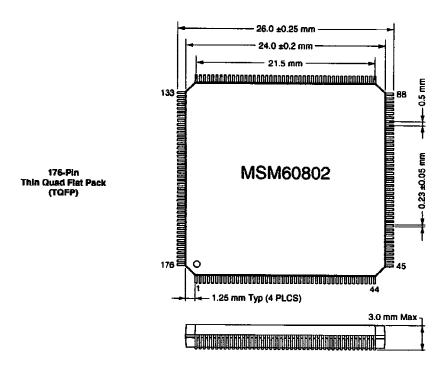

### **PACKAGE DIAGRAM**

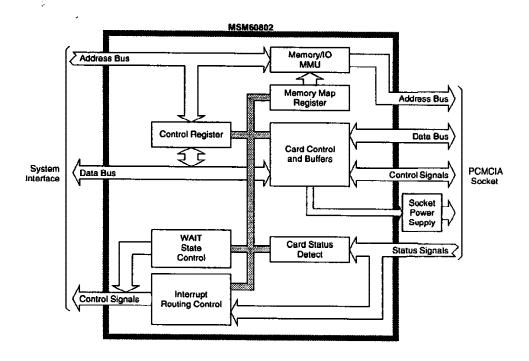

### **BLOCK DIAGRAM**

### **PIN DESCRIPTIONS**

| Pin Name      | Direction and<br>Strength                 |                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Descri                                                                                                                                                  | rtion                                                                                                                                                                                                                                                                                                                        |                       |  |  |

|---------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|

| AEN           | Input                                     | System Address Enable. This active-HIGH input signal should be connected to the AEN signal on the ISA bus. If the system asserts this signal HIGH, access to I/O and the internal MSM60802 registers is disabled, CE1 and CE2 are asserted LOW, and memory access is enabled. If the system deasserts this signal LOW, access to I/O and internal registers is also enabled. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                              |                       |  |  |

| AUX           | I/O<br>4 mA                               | Auxiliary.                                                                                                                                                                                                                                                                                                                                                                   | Auxiliary. This is a multi-purpose I/O pin for user applications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                              |                       |  |  |

| BALE          | Input                                     | bus. The s                                                                                                                                                                                                                                                                                                                                                                   | Bus Address Latch Enable. This active-HIGH input signal should be connected to the BALE signal on the ISA bus. The system asserts this signal HIGH at the beginning of every bus cycle to latch the address from the system address bus, SA[23:17].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                              |                       |  |  |

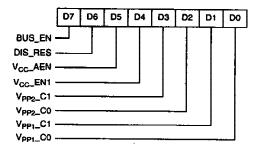

| BUSEN         | Output<br>4 mA                            | Bus Enable                                                                                                                                                                                                                                                                                                                                                                   | e. If the PCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CIA bus is enabled, the MSM608                                                                                                                          | 102 asserts this signal LOW.                                                                                                                                                                                                                                                                                                 |                       |  |  |

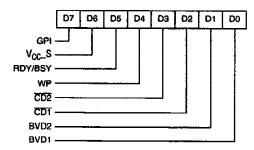

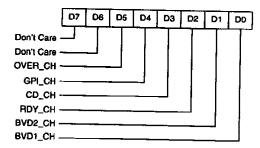

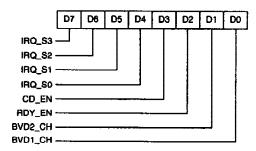

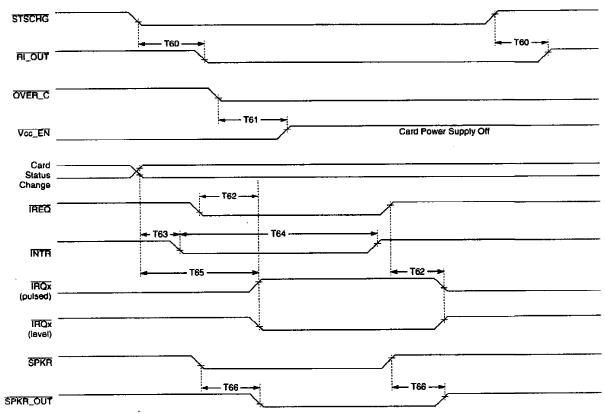

| BVD1 (STSCHG) | Input                                     | Battery Sta<br>Card Status<br>bit in this n<br>'1' on the fa<br>Status Cha<br>the BVD1 b<br>selected by                                                                                                                                                                                                                                                                      | This is a dual-function PCMCIA pin with different characteristics on memory and configured I/O cards. <b>Battery Status 1.</b> On memory cards, this signal indicates a low battery on the PC card. If the BVD1 bit in the Card Status Interrupt Configuration Register (see page 19) is set to '1' then the interrupt selected by the IRQ_SX bit in this register is requested. The BVD1_CH bit in the Card Status Flag Register (see page 18) is also set to '1' on the falling edge of BVD1. <b>Status Changed.</b> On configured I/O cards, the card signals a change of its status by setting this signal LOW. If the BVD1 bit in the Card Status Interrupt Configuration Register (see page 19) is set to '1' then the interrupt selected by the IRQ_Sx bit in this register is requested. The BVD1_CH bit in the Card Status Flag Register (see page 18) is also set to '1' on the falling edge of STSCHG, and the MSM60802 asserts the RI_OUT signal LOW |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                              |                       |  |  |

| BVD2 (SPKR)   | Input                                     | Battery Sta<br>Card Status<br>bit in this re<br>'1' on the fa<br>Digital Aud<br>When confi                                                                                                                                                                                                                                                                                   | tus 2. On me<br>Interrupt Co.<br>egister is requalling edge of<br>io. On I/O car<br>gured for I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | mory cards, this signal indicates<br>nfiguration Register (see page 19<br>uested. The BVD2_CH bit in the<br>BVD1.<br>rds, the PC card can use this sign | teristics on memory and configured I/O cards. a low battery on the PC card. If the BVD2 bit in ) is set to '1' then the interrupt selected by the IRC Card Status Flag Register (see page 18) is also so all to transmit digital audio signals to the host systemerated when the level of SPKR changes and the continuously. | Q_Sx<br>et to<br>tem. |  |  |

| CA[25:0]      | 3-state Output<br>4 mA                    | Card Addre                                                                                                                                                                                                                                                                                                                                                                   | ss Bus. This                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | signal directly connects to the P                                                                                                                       | CMCIA socket's A[25:0] signals.                                                                                                                                                                                                                                                                                              |                       |  |  |

| CDB[15:0]     | I/O<br>4 mA                               | Card Data i                                                                                                                                                                                                                                                                                                                                                                  | Bus. This sign                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nal directly connects to the PCM                                                                                                                        | CIA socket's D[15:0] signals.                                                                                                                                                                                                                                                                                                |                       |  |  |

| CD1, CD2      | Input<br>Schmitt Trigger<br>50 kΩ pull-up |                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ard is present, these signals are<br>er Index 04H and 05H for details                                                                                   | pulled HIGH. An inserted card pulls both of these                                                                                                                                                                                                                                                                            | e                     |  |  |

| CE1, CE2      | 3-state Output<br>4 mA                    | Card Enable. The MSM60802 asserts these signals LOW to enable the PC card for read and write accesses.                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                              |                       |  |  |

| CS1, CS0      | Input<br>50 kΩ pull-down                  | signals sele<br>Register. For<br>jumpers for                                                                                                                                                                                                                                                                                                                                 | ct the system<br>our addresses<br>selection of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | naddresses for the MSM60802 is are selectable via the CSO and (                                                                                         | signal input is not asserted HIGH, the CS1 and CS<br>Register Select Register and the Data Transfer<br>CS1 pins, allowing users to hard-wire or configuinate also the<br>hat avoid potential address conflicts. See also the                                                                                                 | re                    |  |  |

|               |                                           | CSO                                                                                                                                                                                                                                                                                                                                                                          | CS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Address                                                                                                                                                 | (Hex)                                                                                                                                                                                                                                                                                                                        |                       |  |  |

|               |                                           |                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Register Select Register                                                                                                                                | Data Transfer Register                                                                                                                                                                                                                                                                                                       |                       |  |  |

|               |                                           | 0                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3E0                                                                                                                                                     | 3E1                                                                                                                                                                                                                                                                                                                          |                       |  |  |

|               |                                           | 0                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3E2                                                                                                                                                     | 3E3                                                                                                                                                                                                                                                                                                                          |                       |  |  |

|               |                                           | 1                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 240                                                                                                                                                     | 241                                                                                                                                                                                                                                                                                                                          |                       |  |  |

|               |                                           | 1                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 100                                                                                                                                                     | 101                                                                                                                                                                                                                                                                                                                          |                       |  |  |

## PIN DESCRIPTIONS (Continued)

| Pin Name                                      | Direction and<br>Strength | _Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPI                                           | Input                     | General Purpose Input. The MSM60802 images the inverted state of this input pin in bit D7 of the Card Status Register (see page 15). If the GPI_EN bit in the Card Detect and General Control Register (see page 28) is set to '1,' then a transition on this input can generate a card status-change interrupt. The GPI_TC bit in the same register controls the direction of signal change that causes an interrupt.                                                                                     |

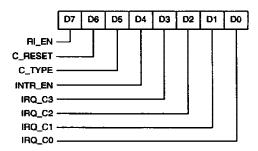

| INTR                                          | 3-state Output<br>8 mA    | Interrupt Request. This active-LOW output should be connected to a system interrupt signal, i.e., the system signal ETSMI. The INTR signal is used to require a maskable interrupt from the system CPU. If the MSM60802 asserts INTR LOW, all other status interrupt requests (IRO's) are disabled.                                                                                                                                                                                                        |

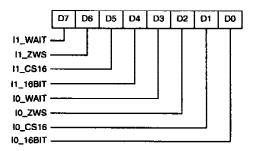

| IOCHRDY                                       | 3-state Output<br>16 mA   | I/O Channel Ready. This active-HIGH output should be connected to the host signal IOCHRDY. When asserted HIGH, this output indicates that the current I/O read or write cycle is completed. If the PCMCIA signal WAIT signal is active, or the MSM60802 is programmed to insert WAIT states, the MSM60802 will reflect this by deasserting the IOCHRDY signal LOW.                                                                                                                                         |

| IOCS16                                        | 3-state Output<br>16 mA   | I/O Chip Select.16. This active-LOW output signal should be connected to the host signal IOCS16. The IOCS16 signal is generated either by the MSM60802 or by the PC card. When asserted LOW, this signal indicates that 16-bit I/O cycles can be performed.                                                                                                                                                                                                                                                |

| TORC                                          | Input                     | I/O Read Cycle. This active-LOW input signal should be connected to the host signal IORC. If the accessed address is in the configured and enabled I/O window, the MSM60802 performs a PCMCIA I/O read cycle to the PC I/O card when this signal is asserted LOW.                                                                                                                                                                                                                                          |

| IORD                                          | 3-state Output<br>4 mA    | 1/O Read. This active-LOW signal indicates that the MSM60802 is performing an VO read access to the PC card.                                                                                                                                                                                                                                                                                                                                                                                               |

| IOWC                                          | Input                     | I/O Write Cycle. This input signal should be connected to the host signal $\overline{10WC}$ . If the accessed address is in the configured and enabled I/O window, the MSM60802 performs a PCMCIA I/O write cycle to the PC I/O card when this signal is asserted LOW.                                                                                                                                                                                                                                     |

| IOWR                                          | 3-state Output<br>4 mA    | I/O Write. This active-LOW signal indicates that the MSM60802 is performing an I/O write access to the PC card.                                                                                                                                                                                                                                                                                                                                                                                            |

| IREQ                                          | input                     | Interrupt Request. See the signal description for RDY/ BSY (IREQ).                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| IRQ[15:14]<br>IRQ[12:9]<br>IRQ[7]<br>IRQ[5:3] | 3-state Output<br>8 mA    | Interrupt Request. These output signals should be connected to the equivalent signals of the host system. The PCMCIA interrupt request is routed to one of these interrupt signals. The system can choose the interrupt signal by writing a configuration into IRQ_Cx bits in the Interrupt and General Control Register (see page 17). A status change of the PC card might also force a system interrupt, if this function is enabled in the Card Status Interrupt Configuration Register (see page 19). |

| LA[23:17]<br>SA[16:0]                         | Input                     | Local Address Bus and System Address Bus. These signals should be connected to the system address bus, SA[16:0] and LA[23:17]. LA23 is the most-significant and SA0 is the least-significant bit. If connected to an 8-bit ISA bus, LA[19:17] should be connected to SA[19:17] of the ISA bus and LA[23:20] must be pulled down.                                                                                                                                                                           |

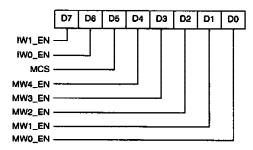

| MEMCS16                                       | 3-state Output<br>16 mA   | Memory Chip Select 16-Bit. This output signal should be connected to the host signal MEMCS16. The MSM60802 asserts this signal LOW to indicate that a 16-bit memory cycle can be performed. The signal is decoded from the system address and is controlled by the MCS bit in the Address Window Enable Register (see page 20).                                                                                                                                                                            |

| MEMR                                          | Input                     | System Memory Read. This input signal should be connected to the host signal MEMR. If the accessed address is in the configured and enabled memory window, the MSM60802 performs a PCMCIA memory read cycle to the PC card attribute or common memory when this signal is asserted LOW.                                                                                                                                                                                                                    |

| MEMW                                          | Input                     | System Memory Write. This input signal should be connected to the host signal MEMW. If the accessed address is in the configured and enabled memory window, the MSM60802 performs a PCMCIA memory write cycle to the PC card attribute or common memory when this signal is asserted LOW.                                                                                                                                                                                                                  |

## PIN DESCRIPTIONS (Continued)

| Pin Name        | Direction and<br>Strength                 |                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                           | Description                                                                                                                                          |                                                                                                              |                                                                                                      |  |

|-----------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|

| MODE            | Input<br>50 kΩ puil-up                    | Mode Select. When asserted HIGH, this input makes the $\overline{CSO}$ and $\overline{CSO}$ inputs select addresses for the Registe Select Register and Data Transfer Register. When deasserted LOW, the system addresses for the Register Select Register and the Data Transfer Register are decoded externally. For external decoding, the CS1 input must be tied LOW. See the table below. |                                                                                                                           |                                                                                                                                                      |                                                                                                              |                                                                                                      |  |

|                 |                                           | Mode (                                                                                                                                                                                                                                                                                                                                                                                        | CSO CS1                                                                                                                   | Register Select Re                                                                                                                                   | egister                                                                                                      | Data Transfer Register                                                                               |  |

|                 |                                           | 1                                                                                                                                                                                                                                                                                                                                                                                             | x x                                                                                                                       | See Sign                                                                                                                                             | nal Description                                                                                              | o for CSO and CS1                                                                                    |  |

|                 |                                           | 0                                                                                                                                                                                                                                                                                                                                                                                             | 0 1                                                                                                                       | A0 = 0                                                                                                                                               |                                                                                                              | A0 = 1                                                                                               |  |

| İ               |                                           | 0                                                                                                                                                                                                                                                                                                                                                                                             | 1 1                                                                                                                       | Not selected                                                                                                                                         |                                                                                                              | Not selected                                                                                         |  |

| ŌĒ              | 3-state Output<br>4 mA                    | Output Enable. T                                                                                                                                                                                                                                                                                                                                                                              | his active-LOW sign<br>nemory or attribute                                                                                | al indicates that the MSN memory.                                                                                                                    | /160802 is perf                                                                                              | orming a read access to the PC                                                                       |  |

| OFFSET [1:0]    | input<br>50 kΩ pull-down                  | Control Registers                                                                                                                                                                                                                                                                                                                                                                             | s. The table below sl                                                                                                     | nals allow four different a<br>nows available offset valu<br>sters' on page 12 for more                                                              | es for the regi                                                                                              | s for the MSM60802 Status and ster addresses. Refer to the                                           |  |

|                 |                                           | OFFSET1                                                                                                                                                                                                                                                                                                                                                                                       | OFFSETO                                                                                                                   | Offset                                                                                                                                               |                                                                                                              |                                                                                                      |  |

|                 |                                           | 0                                                                                                                                                                                                                                                                                                                                                                                             | Ö                                                                                                                         | 0                                                                                                                                                    |                                                                                                              |                                                                                                      |  |

|                 |                                           | 0                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                         | 40 Hex                                                                                                                                               |                                                                                                              |                                                                                                      |  |

|                 |                                           | 1                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                         | 80 Hex                                                                                                                                               |                                                                                                              |                                                                                                      |  |

|                 |                                           | 1                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                         | C0 Hex                                                                                                                                               |                                                                                                              |                                                                                                      |  |

| OVER_C          | Input<br>Schmitt Trigger<br>50 kΩ pull-up | page 28) are set<br>and forces a stat                                                                                                                                                                                                                                                                                                                                                         | to '1,' then a failing e<br>us change interrupt                                                                           | dge at this input switches                                                                                                                           | off the power                                                                                                | and General Control Register (see supply via the power control pins                                  |  |

| PWRGD           | Input<br>Schmitt Trigger<br>50 kΩ pull-up | supply voltage. It<br>Register (see pa                                                                                                                                                                                                                                                                                                                                                        | the system is asser<br>ge 16) is set to '1,' t                                                                            | ting PWRGD HIGH and the<br>hen the reset signal RSTE                                                                                                 | e bit DIS_RES i<br>DRV is ignored                                                                            |                                                                                                      |  |

| RDY/ BSY (IREQ) | Input                                     | Ready/Busy. On has been forced. When the RDY/B RDY/BSY bit is s Interrupt Reque:                                                                                                                                                                                                                                                                                                              | memory cards, the Putling the RDY/BS SY bit in the Card S tet to '1' continuous to On I/O cards, the in the Interrupt and | PC card pulls this signal<br>Y signal clears the RDY/Bi<br>atus Register is set to '1,'<br>by if the socket is configur<br>PC card can request a hos | LOW to indica<br>SY bit in the Ca<br>the PC card is<br>red for I/O ope<br>st system interi<br>see page 17) s | rupt by asserting this signal LOW<br>elect the generated interrupt level                             |  |

| REG             | 3-state Output<br>4 mA                    | operations and o<br>signal is general                                                                                                                                                                                                                                                                                                                                                         | Irives this signal act<br>ed by the MSM6080                                                                               | ve LOW for I/O and attrib                                                                                                                            | ute memory o<br>bute memory a                                                                                | t active) for common memory<br>perations. For I/O operations, thi<br>access, the REG bit in the Card |  |

| RESET           | 3-state Output<br>4 mA                    | Card Reset. The MSM60802 asserts this signal HIGH level to force a hardware reset on the PC card. If the C_RESET bit in the Interrupt and General Control Register (see page 17) is cleared to '0,' then the RESET output is asserted HIGH. Setting the C_RESET bit to '1' deasserts the RESET signal.                                                                                        |                                                                                                                           |                                                                                                                                                      |                                                                                                              |                                                                                                      |  |

| RI_OUT          | 3-state Output<br>8 mA                    | signal to the hos                                                                                                                                                                                                                                                                                                                                                                             | t system that it shou<br>SCHG signal receive                                                                              | ild switch from sleep mod<br>d from a configured I/O P                                                                                               | le to active mo<br>C card via the                                                                            |                                                                                                      |  |

| RSTDRV          | Input<br>Schmitt Trigger                  | the MSM60802                                                                                                                                                                                                                                                                                                                                                                                  | by asserting this sig                                                                                                     | nal HIGH. If the Power Go                                                                                                                            | od signal, PWI                                                                                               | al RSTDRV. The system can rese<br>RGD, is HIGH and the DIS_RES b<br>MSM60802 will ignore RSTDRV.     |  |

## PIN DESCRIPTIONS (Continued)

| Pin Name             | Direction and<br>Strength | Description                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SBHE                 | input                     | System Bus High Enable. This input signal should be connected to the host signal SBHE. The system drives this signal LOW to indicate that the upper byte of data on the data bus is valid. If this signal is deasserted HIGH, the MSM60802 will only perform 8-bit cycles to the PCMCIA socket.                                                                                          |

| SA[16:0]             | Input                     | System Address Bus. See the signal description for LA[23:17].                                                                                                                                                                                                                                                                                                                            |

| SD[15:0]             | I/O<br>8 mA               | System Data Bus. These bidirectional signals should be connected to the system data bus, SD[15:0].                                                                                                                                                                                                                                                                                       |

| SPKR                 | Input                     | Speaker In. See the signal description for BVD2 (SPKR).                                                                                                                                                                                                                                                                                                                                  |

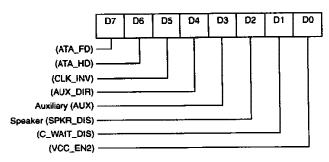

| SPKR_OUT             | 3-state Output<br>8 mA    | <b>Speaker Out.</b> To perform digital audio functions, this output passes through the signal received at the SPKR input from a configured PC I/O card. The output can be disabled with the D2 bit of the Extension Register (Index OFFH).                                                                                                                                               |

| STSCHG               | Input                     | Status Changed. For information, see the signal description for BVD1 (STSCHG).                                                                                                                                                                                                                                                                                                           |

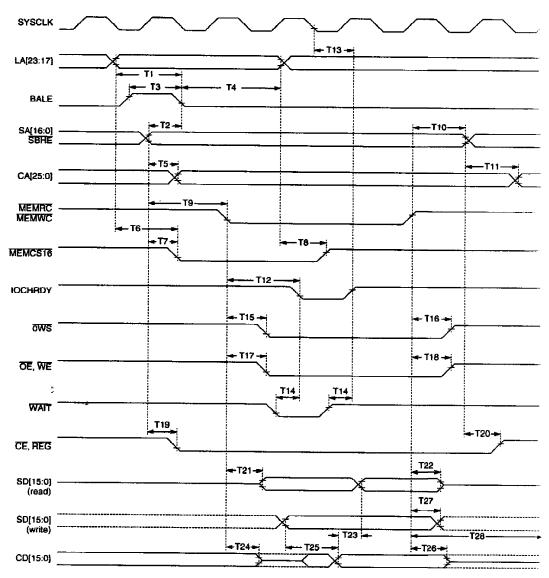

| SYSCLK               | Input                     | System Clock. This input signal should be connected to the host system's CLOCK signal. The MSM60802 supports clock frequencies in the 4.77-MHz to 8.33-MHz range. The clock frequency effects the timings by changing the pulse width of INTR (three SYSCLK cycles), and the delays for 16-bit MEMR and 16-bit MEMW operations.                                                          |

| VCC_EN1<br>VCC_EN2   | Output<br>8 mA            | V <sub>CC</sub> Power Enable. The MSM60802 asserts this LOW to activate PC card V <sub>CC</sub> power.                                                                                                                                                                                                                                                                                   |

| VPP1_EN1<br>VPP1_EN2 | Output<br>8 mA            | V <sub>PP1</sub> Power Enable. This signal is active HIGH.                                                                                                                                                                                                                                                                                                                               |

| VPP2_EN1<br>VPP2_EN2 | Output<br>8 mA            | V <sub>PP2</sub> Power Enable. This signal is active HIGH                                                                                                                                                                                                                                                                                                                                |

| WAIT                 | Input                     | Extend Bus Cycle. The PC card can activate this active-LOW signal to extend a memory or I/O cycle.                                                                                                                                                                                                                                                                                       |

| WE                   | 3-state Output<br>4 mA    | Write Enable. This active-low signal indicates a write access to the common memory or attribute memory of the PC card.                                                                                                                                                                                                                                                                   |

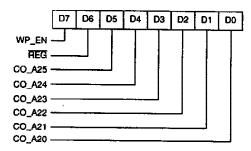

| WP<br>(IOIS16)       | Input                     | Write Protect. By pulling this signal high, the PC card indicates that the card is write protected. The MSM60802 will not qualify this signal. To prevent write access, the WP_EN bit in the Card Memory Offset Address High Byte Register has to be set.  I/O port is 16-bit. The PC card indicates if a addressed I/O port is capable of 16-bit accesses by asserting this signal LOW. |

| <u> </u>             | 3-state Output<br>16 mA   | Zero WAIT State. This signal (active low) should be connected to the host system signal OWS. It indicates that the system should execute cycles with no extra WAIT states. It is controlled by Ix_ZWS (I/O Control Register) and ZWS (Memory Window x Start Address High Byte Register).                                                                                                 |

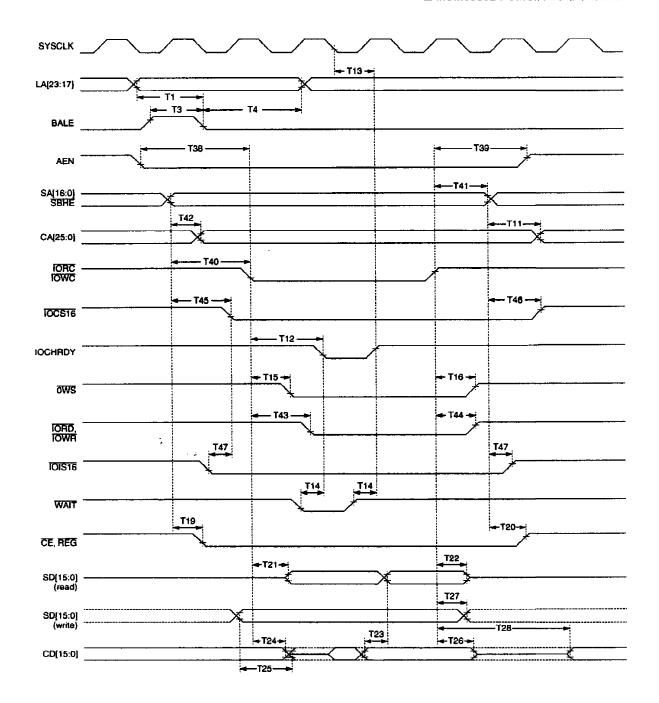

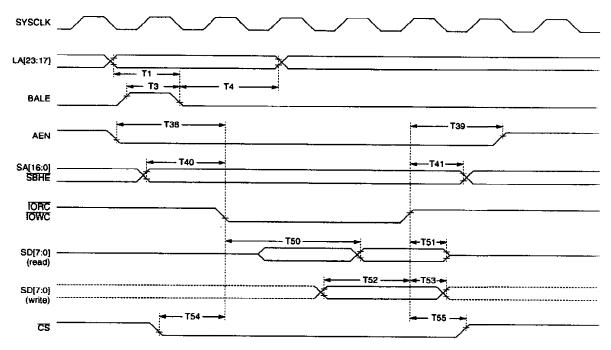

#### **FUNCTIONAL DESCRIPTION**

The following information describes the MSM60802 main function blocks.

#### **MEM/IO MMU**

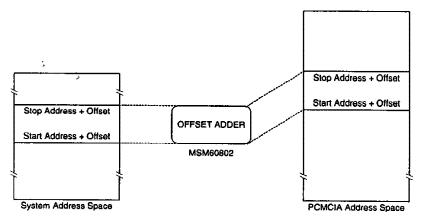

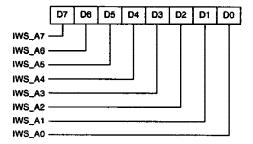

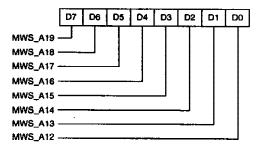

The Memory Management Unit (MMU) is controlled by the Memory Map Register and decodes the system addresses LA[23:17] and SA[16:0]. If addresses are accessed within a configured memory or I/O window, the memory management unit transfers the access to the PCMCIA socket. For memory address operations, the MMU adds the configured address offset to the system address.

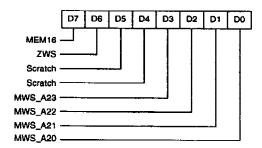

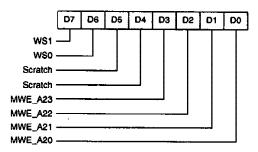

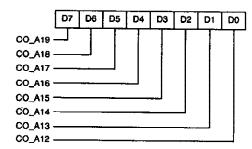

#### **Memory Map Register**

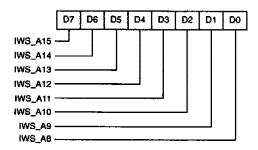

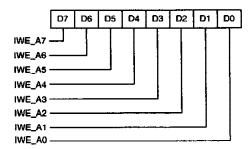

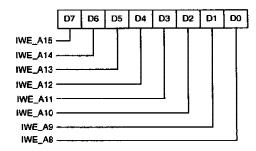

The Memory Map Registers control MEM/IO MMU. The system address windows must be defined by writing to these registers. Five memory windows and two I/O windows can be defined simultaneously.

#### **Control Registers**

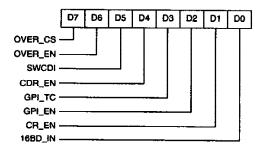

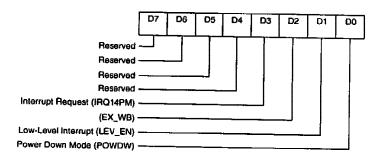

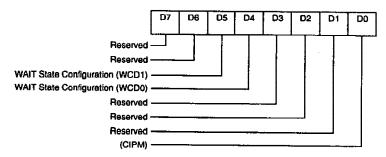

Control Registers interface between the internal function blocks of the MSM60802 and the host system. By reading or writing the Control Registers, the MSM60802 and the PCMCIA Interface can be configured.

To access a control register, the system must at first select this register by writing the register's index number into the Register Select Register. To read or write the selected register, the system must access the Data Transfer Register. Both system addresses of the Register Select Register and the Data Transfer Register are adjustable by two chip select signals.

#### **Card Control and Buffers**

If the MEM/IO MMU detects a valid memory or I/O cycle to the PC card, the card control and buffers function block generates all necessary control signals, such as card enables, and then connects the data bus to the PC card. This function block also drives signals for switching the PCMCIA socket power supply.

#### **Card Status Detect**