# **LXT970**

# Fast Ethernet Transceiver

# **General Description**

The LXT970 Fast Ethernet Transceiver supports IEEE 802.3 compliant Ethernet applications at both 10 and 100Mbps operation. It provides the active circuitry to interface 802.3 media independent interface (MII) compliant controllers to 10BASE-T and/or 100BASE-TX media. The LXT970 also provides an ECL-type interface for use with 100BASE-FX fiber networks.

The LXT970 supports full duplex operation at 10 and 100 Mbps. Its operating condition can be set using auto-negotiation, parallel detection or manual control. The encoder can be bypassed for symbol mode applications.

The LXT970 is fabricated with an advanced CMOS process and requires only a single 5 volt power supply. The MII may be operated independently with either a 5 volt supply or a 3.3 volt supply.

# **Applications**

- Combination 10BASE-T/100BASE-TX Network Interface Cards (NICs)

- 10/100 Switches, 10/100 Repeaters

- 100BASE-FX Network Interface Cards (NICs)

### **Features**

- IEEE 802.3 Compliant:

- 10BASE-T and 100BASE-TX using a single RJ45 connection

- Supports both auto-negotiation via Fast Link Pulse (FLP) exchange and parallel detection for legacy 10BASE-T and 100BASE-TX systems

- MII interface with extended register capability

- Baseline wander correction

- 100BASE-FX fiber optic capable

- Standard CSMA/CD or full duplex operation at 10 or 100 Mbps

- Configurable through MII serial port or via external control pins

- Configurable for DTE, repeater or switch applications

- CMOS process with single 5 volt supply operation with provision for interface to 3.3 V MII bus

- Integrated transmit and receive filtering for 10BASE-T and 100BASE-TX

- Integrated LED drivers

- Integrated supply monitor and line disconnect during low supply fault

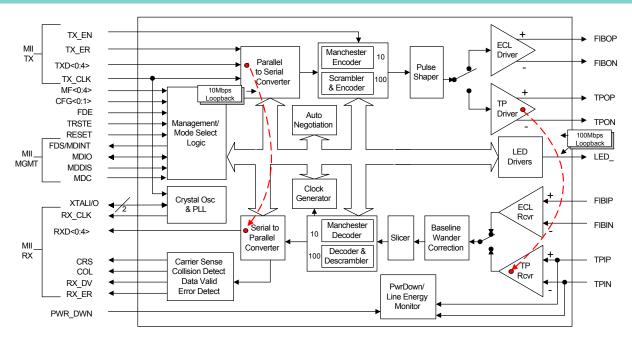

# **LXT970 Block Diagram**

# **TABLE OF CONTENTS**

| PIN AS | SSIGNMENTS AND SIGNAL DESCRIPTIONS | . 11-168 |

|--------|------------------------------------|----------|

| FUNC   | TIONAL DESCRIPTION                 | . 11-176 |

|        | Introduction                       | . 11-176 |

|        | Network Media/Protocol Support     | . 11-177 |

|        | 10/100 Mbps Twisted Pair Interface | . 11-177 |

|        | 100 Mbps Fiber Interface           | . 11-177 |

|        | MII Interface                      | . 11-177 |

|        | MII Data Interface                 | . 11-177 |

|        | MII Management Interface (MDIO)    | . 11-178 |

|        | Hardware Control Interface         | . 11-179 |

|        | Operating Configurations Tables    | . 11-179 |

|        | Initialization                     | . 11-181 |

|        | Link Configuration                 | . 11-181 |

|        | Auto-Negotiation                   | . 11-182 |

|        | 100 Mbps Operation                 | . 11-183 |

|        | 4B/5B Coding Table                 | . 11-184 |

|        | 5B Symbol Mode                     | . 11-185 |

|        | Scrambler Bypass                   | . 11-185 |

|        | Link Failure Criteria and Override | . 11-185 |

|        | Baseline Wander Correction         | . 11-185 |

|        | Errors and Collisions              | . 11-186 |

|        | 10 Mbps Operation                  | . 11-187 |

|        | Operating Requirements             | . 11-188 |

|        | Power Requirements                 | . 11-188 |

|        | Clock Requirements                 | . 11-188 |

| APPLI  | CATION INFORMATION                 | . 11-189 |

|        | Magnetics/Crystal Information      | . 11-189 |

|        | Layout Requirements                | . 11-190 |

|        | Twisted-Pair Interface             | . 11-190 |

|        | The RBIAS Pin                      | . 11-190 |

|        | Power Supply Decoupling            | . 11-190 |

|        | Typical Application                | . 11-191 |

|        |                                    |          |

| TEST SPECIFICATIONS                                        | 11-193 |

|------------------------------------------------------------|--------|

| Absolute Maximum Ratings                                   | 11-193 |

| Recommended Operating Conditions                           | 11-193 |

| Digital I/O Characteristics                                | 11-194 |

| Clock Characteristics                                      | 11-195 |

| Link Integrity Timing Characteristics                      | 11-195 |

| 100BASE-TX Transceiver Characteristics                     | 11-196 |

| 100BASE-FX Transceiver Characteristics                     | 11-196 |

| 10BASE-T Transceiver Characteristics                       | 11-197 |

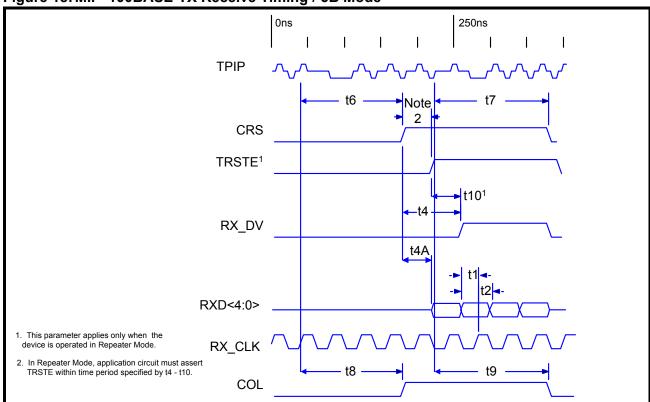

| 100BASE-TX Receive Timing 4B Mode                          | 11-198 |

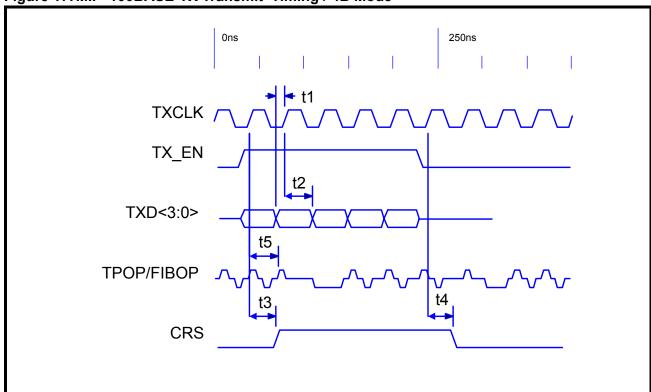

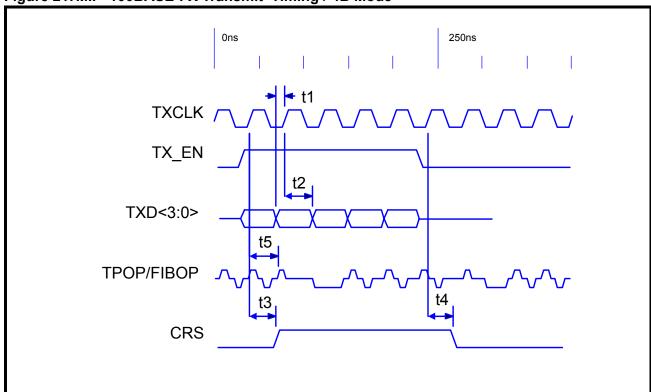

| 100BASE-TX Transmit Timing 4B Mode                         | 11-199 |

| 100BASE-TX Receive Timing 5B Mode                          | 11-200 |

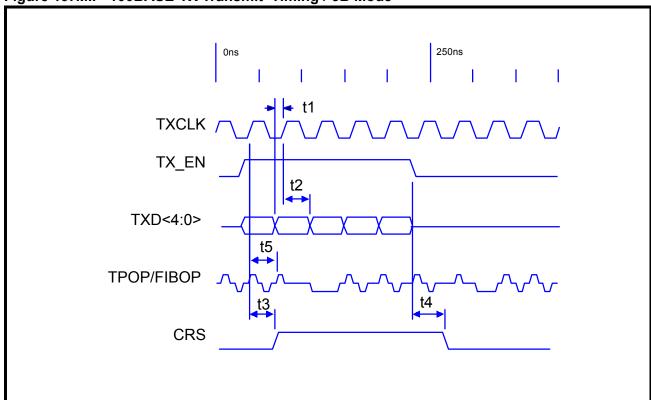

| 100BASE-TX Transmit Timing 5B Mode                         | 11-201 |

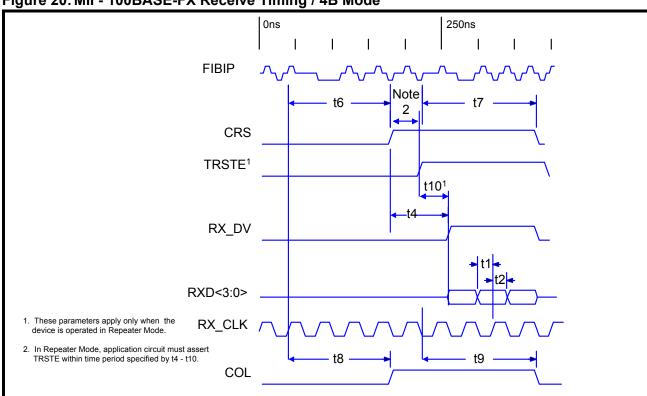

| 100BASE-FX Receive Timing 4B Mode                          | 11-202 |

| 100BASE-FX Transmit Timing 4B Mode                         | 11-203 |

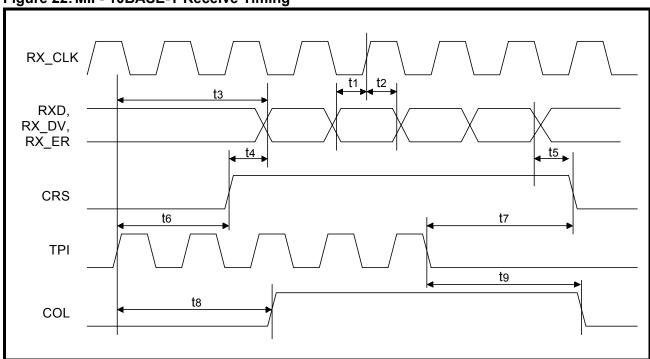

| 10BASE-T Receive Timing                                    | 11-204 |

| 10BASE-T Transmit Timing                                   | 11-205 |

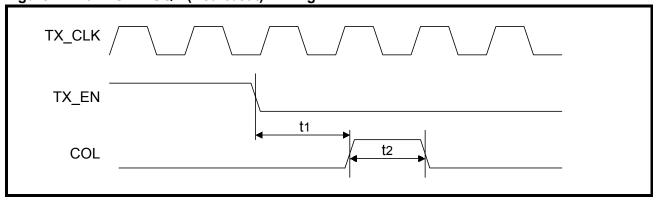

| 10BASE-T SQE (Heartbeat) TIming                            | 11-206 |

| Auto Negotiation and Fast Link Pulse TIming                | 11-207 |

| MDIO and MII Timing                                        | 11-208 |

| Miscellaneous Timing                                       | 11-209 |

| REGISTER DEFINITIONS                                       | 11-210 |

| Control Register (Address 0)                               | 11-211 |

| Status Register (Address 1)                                | 11-212 |

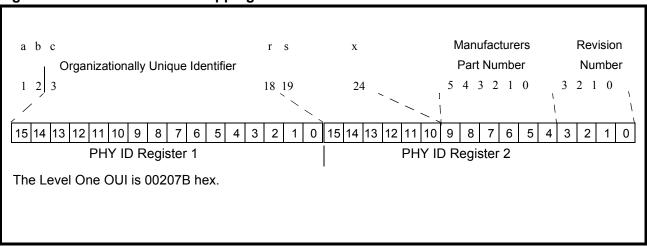

| PHY Identification Register (Address 2)                    | 11-213 |

| PHY Identification Register (Address 3)                    | 11-213 |

| Auto Negotiation Advertisement Register (Address 4)        | 11-214 |

| Auto Negotiation Link Partner Ability Register (Address 5) | 11-215 |

| Auto Negotiation Expansion (Address 6)                     | 11-216 |

| Mirror Register (Address 16)                               | 11-216 |

| Interrupt Enable Register (Address 17)                     | 11-216 |

| Interrupt Status Register (Address 18)                     | 11-217 |

| Configuration Register (Address 19)                        | 11-218 |

| Chip Status Register (Address 20)                          | 11-219 |

# PIN ASSIGNMENTS AND SIGNAL DESCRIPTIONS

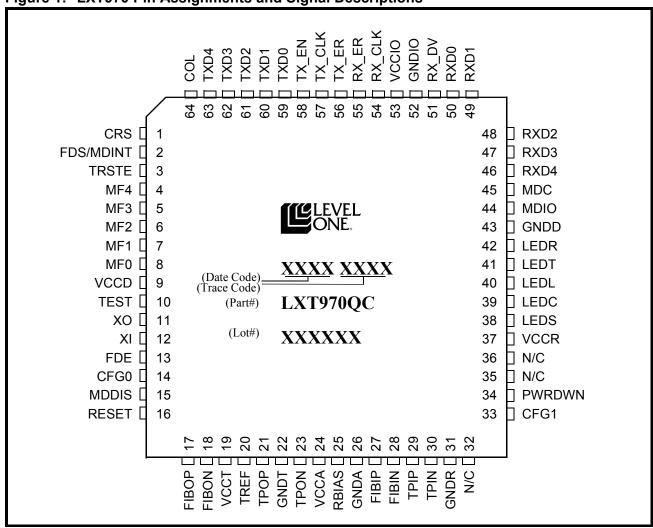

Figure 1: LXT970 Pin Assignments and Signal Descriptions

**Table 1: LXT970 Power Supply Signal Descriptions**

| Pin#     | Pin Name       | I/O | Pin Description                                 |

|----------|----------------|-----|-------------------------------------------------|

| 19<br>22 | VCCT<br>GNDT   | -   | Transmitter Supply (+5V) and Ground.            |

| 37<br>31 | VCCR<br>GNDR   | -   | Receiver Supply (+5V) and Ground.               |

| 24<br>26 | VCCA<br>GNDA   | -   | Analog Supply (+5V) and Ground.                 |

| 9<br>43  | VCCD<br>GNDD   | -   | <b>Digital Supply</b> (+5V) and <b>Ground</b> . |

| 53<br>52 | VCCIO<br>GNDIO | -   | MII Supply (+3.3V or +5V) and Ground.           |

Table 2: I XT970 MII Signal Descriptions

| Pin#                       | Pin Name                             | I/O <sup>1</sup> | Pin Description                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|----------------------------|--------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                            | MII Data Interface Pins              |                  |                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 63<br>62<br>61<br>60<br>59 | TXD4<br>TXD3<br>TXD2<br>TXD1<br>TXD0 | I                | <b>Transmit Data</b> . The MAC drives data to the LXT970 using these inputs. TXD4 is monitored only in Symbol (5B) Mode. These signals must be synchronized to the TX_CLK.                                                                                                                                                                                           |  |  |  |  |

| 58                         | TX_EN                                | I                | <b>Transmit Enable</b> . The MAC asserts this signal when it drives valid data on the TXD inputs. This signal must be synchronized to the TX_CLK.                                                                                                                                                                                                                    |  |  |  |  |

| 57                         | TX_CLK                               | I/O              | <b>Transmit Clock</b> . 25 MHz for 100 Mbps operation, 2.5 MHz for 10 Mbps operation. Refer to the Clock Requirements discussion in the Functional Description section.                                                                                                                                                                                              |  |  |  |  |

| 56                         | TX_ER                                | I                | <b>Transmit Coding Error</b> . The Media Access Controller (MAC) asserts this input when an error has occurred in the transmit data stream. When the LXT970 is operating at 100Mbps, the LXT970 responds by sending "Invalid Code Symbols" on the line.                                                                                                              |  |  |  |  |

| 46<br>47<br>48<br>49<br>50 | RXD4<br>RXD3<br>RXD2<br>RXD1<br>RXD0 | О                | Receive Data. The LXT970 drives received data on these outputs, synchronous to RX_CLK. RXD4 is driven only in Symbol (5B) Mode.                                                                                                                                                                                                                                      |  |  |  |  |

| 51                         | RX_DV                                | О                | Receive Data Valid. The LXT970 asserts this signal when it drives valid data on RXD. This output is synchronous to RX_CLK.                                                                                                                                                                                                                                           |  |  |  |  |

| 55                         | RX_ER                                | О                | <b>Receive Error</b> . The LXT970 asserts this output when it receives invalid symbols from the network. This signal is synchronous to RX_CLK.                                                                                                                                                                                                                       |  |  |  |  |

| 54                         | RX_CLK                               | О                | <b>Receive Clock</b> . 25 MHz for 100 Mbps operation, 2.5 MHz for 10 Mbps operation. Refer to the Clock Requirements discussion in the Functional Description section.                                                                                                                                                                                               |  |  |  |  |

| 64                         | COL                                  | О                | Collision Detected. The LXT970 asserts this output when a collision is detected. This output remains High for the duration of the collision. This signal is asynchronous and is inactive during full duplex operation.                                                                                                                                               |  |  |  |  |

| 1                          | CRS                                  | О                | <b>Carrier Sense</b> . During half-duplex operation (bit $0.8 = 0$ ) <sup>2</sup> , the LXT970 asserts this output when either transmit or receive medium is non-idle. During full-duplex operation (bit $0.8 = 1$ ) or repeater operation (bit $19.13 = 1$ ), CRS is asserted only when the receive medium is non-idle.                                             |  |  |  |  |

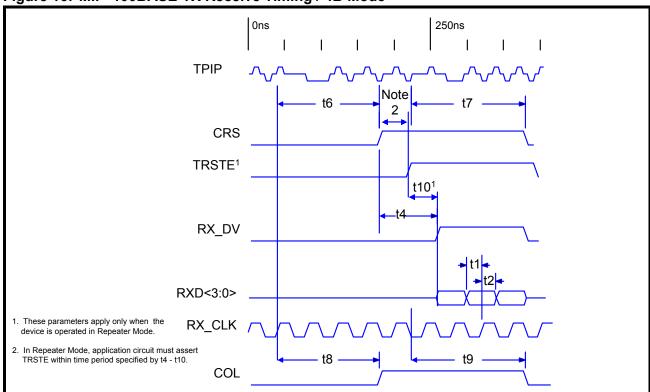

| 3                          | TRSTE                                | I                | <b>Tristate</b> . In DTE Mode (19.13 = 0), when TRSTE input is High, the LXT970 isolates itself from the MII Data Interface, and controls the MDIO register bit 0.10 (Isolate bit). When MDDIS is High, TRSTE provides continuous control over bit 0.10. When MDDIS is Low, TRSTE sets initial (default) values only and reverts control back to the MDIO interface. |  |  |  |  |

|                            |                                      |                  | In Repeater Mode (19.13 = 1), when TRSTE input is High, the LXT970 tri-states the receive outputs of the MII (RXD<4:0>, RX_DV, RX_ER, RX_CLK).                                                                                                                                                                                                                       |  |  |  |  |

I/O Column Coding: I = Input, O = Output, OD = Open Drain

The LXT970 supports the 802.3 MDIO register set. Specific bits in the registers are referenced using an "X.Y" notation, where X is the register number (0-31) and Y is the bit number (0-15).

Table 2: LXT970 MII Signal Descriptions - continued

| Pin# | Pin Name                                                                                                                                                                                                                                                                                                                                                                                                                               | I/O <sup>1</sup> | Pin Description                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|      | MII Control Interface Pins                                                                                                                                                                                                                                                                                                                                                                                                             |                  |                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 15   | MDDIS  I Management Disable. When MDDIS is High, the MDIO is restricted to Read Only and the MF<4:0>, CFG<1:0> and FDE pins provide continual control of their respective bits. When MDDIS is Low at power up or Reset, the MF<4:0>, CFG<1:0> and FDE pins control only the initial or "default" values of their respective register bits. After the power-up/reset cycle is complete, bit control reverts to the MDIO serial channel. |                  |                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 45   | MDC                                                                                                                                                                                                                                                                                                                                                                                                                                    | I                | <b>Management Data Clock</b> . Clock for the MDIO serial data channel. Maximum frequency is 2.5 MHz.                                                                                                                                                                                                                                                                                                     |  |  |  |

| 44   | MDIO                                                                                                                                                                                                                                                                                                                                                                                                                                   | I/O              | Management Data Input/Output. Bidirectional serial data channel for PHY/STA communication.                                                                                                                                                                                                                                                                                                               |  |  |  |

| 2    | FDS/MDINT                                                                                                                                                                                                                                                                                                                                                                                                                              | OD               | Full Duplex Status. When bit 17.1 = 0 (default), this pin indicates full duplex status. (High = Full Duplex, Low = Half Duplex) This pin can drive a high efficiency LED. (See Table 22 for detail specifications).  Management Data Interrupt. When bit 17.1 = 1, an active Low output on this pin indicates status change.  Interrupt is cleared by sequentially reading Register 1, then Register 18. |  |  |  |

<sup>1.</sup> I/O Column Coding: I = Input, O = Output, OD = Open Drain

**Table 3: LXT970 Fiber Interface Signal Descriptions**

| Pin#      | Pin Name                                    | I/O | Pin Description                                                                                                                             |  |  |

|-----------|---------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 17<br>18  | FIBOP<br>FIBON                              | О   | <b>Fiber Output, Positive and Negative</b> . Differential pseudo-ECL driver pair compatible with standard fiber transceiver for 100BASE-FX. |  |  |

| 27<br>28  | FIBIP<br>FIBIN                              | I   | <b>Fiber Input, Positive and Negative</b> . Differential pseudo-ECL receive pair compatible with standard fiber transceiver for 100BASE-FX. |  |  |

| 1. I/O Co | 1. I/O Column Coding: I = Input, O = Output |     |                                                                                                                                             |  |  |

**Table 4: LXT970 Twisted Pair Interface Signal Descriptions**

| Pin#      | Pin Name                                                | I/O | Pin Description                                                                                                                                              |  |  |

|-----------|---------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 21<br>23  | TPOP<br>TPON                                            | AO  | <b>Twisted Pair Output, Positive and Negative</b> . Differential driver pair produces 802.3-compliant pulses for either 100BASE-TX or 10BASE-T transmission. |  |  |

| 20        | TREF                                                    | AO  | Transmit Reference. Tie to center tap of output transformer.                                                                                                 |  |  |

| 29<br>30  | TPIP<br>TPIN                                            | AI  | Twisted Pair Input, Positive and Negative. Differential input pair for either 100BASE-TX or 10BASE-T reception.                                              |  |  |

| 1. I/O Co | 1. I/O Column Coding: I = Input, O = Output, A = Analog |     |                                                                                                                                                              |  |  |

<sup>2.</sup> The LXT970 supports the 802.3 MDIO register set. Specific bits in the registers are referenced using an "X.Y" notation, where X is the register number (0-31) and Y is the bit number (0-15).

**Table 5: LXT970 LED Indicator Signal Descriptions**

| Pin#                             | Pin Name                                               | I/O | Pin Description                                                                                                                |  |  |  |

|----------------------------------|--------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 38                               | LEDS                                                   | О   | Speed LED. Active Low output indicates 100 Mbps operation is selected.                                                         |  |  |  |

| 42                               | LEDR                                                   | О   | Receive LED. Active Low output indicates that receiver is active.                                                              |  |  |  |

| 41                               | LEDT                                                   | О   | ansmit LED. Active Low output indicates transmitter is active.                                                                 |  |  |  |

| 40                               | LEDL                                                   | О   | Link LED. Active Low output;                                                                                                   |  |  |  |

|                                  |                                                        |     | During 100 Mbps operation, indicates scrambler lock and receipt of valid Idle codes.                                           |  |  |  |

|                                  | During 10 Mbps operation, indicates Link Valid status. |     |                                                                                                                                |  |  |  |

| 39                               | LEDC                                                   | О   | Collision LED. In default mode, active Low output indicates collision. However,                                                |  |  |  |

|                                  |                                                        |     | LEDC is programmable and may be set for other indications. For programming options, see Configuration Register 19 in Table 53. |  |  |  |

| I. I/O Column Coding: O = Output |                                                        |     |                                                                                                                                |  |  |  |

Table 6: LXT970 Miscellaneous Signal Descriptions

| Pin#                                                    | Pin Name | I/O | Pin Description                                                                                                                                                          |  |  |

|---------------------------------------------------------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 10                                                      | TEST     | I   | Test. Must be tied Low.                                                                                                                                                  |  |  |

| 12                                                      | XI       | I   | Crystal Input and Output. A 25 MHz crystal oscillator circuit can be connected                                                                                           |  |  |

| 11                                                      | XO       | О   | across XI and XO. A clock can also be used at XI. Refer to Functional Description for detailed clock requirements.                                                       |  |  |

| 25                                                      | RBIAS    | AI  | <b>Bias Control</b> . Controls operating circuit bias via an external 22 k $\Omega$ , 1% resistor to ground.                                                             |  |  |

| 16                                                      | RESET    | I   | <b>Reset</b> . This active Low input is OR'ed with the control register Reset bit (0.15). The LXT970 reset cycle is extended 205ns (nominal) after Reset is de-asserted. |  |  |

| 34                                                      | PWRDWN   | I   | <b>Power Down</b> . When High, forces LXT970 into power down mode. This pin is OR'ed with the Power Down bit (0.11). Refer to Table 43 for more information.             |  |  |

| 32, 35,<br>36                                           | N/C      | -   | No Connection. Leave open.                                                                                                                                               |  |  |

| 1. I/O Column Coding: I = Input, O = Output, A = Analog |          |     |                                                                                                                                                                          |  |  |

**Table 7: LXT970 Hardware Control Interface Signal Descriptions**

| Pin#     | Pin Name           | I/O     | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|--------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | MF0 - MF4          | I       | <b>Multi-Function (MF)</b> . Each pin has two independent settings that are established by 4-level supply voltages. The first setting (ADD), determines the PHY address on the MDIO bus and the second setting (FUNC), determines configuration of the LXT970.                                                                                                                                                                                                                                                                                                                                        |

|          |                    |         | The MF inputs directly affect particular bits in the MDIO register set. The effect is mediated by the MDDIS pin. When MDDIS is High, these inputs continually affect the MDIO registers. When MDDIS is Low, they determine initial (default) values only.                                                                                                                                                                                                                                                                                                                                             |

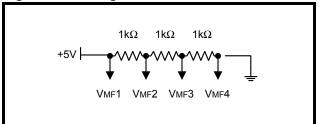

|          |                    |         | Table 21 shows the 4-level supply voltages (voltage levels referred to as VMF1, VMF2, VMF3 and VMF4) that establish the settings per pin. An external voltage divider, as shown in the Layout Requirement section, is required to establish mid-level (VMF2 and VMF3) settings. VMF1 and VMF4 (default) settings, can be established with the LXT970 standard power supply and do not require a voltage divider. Tables 8 and 9 show the selected MF pin function and address with respect to the applied input voltage level. The descriptions below detail the configuration of each of these pins. |

| 8        | MF0                | I       | Enables Auto-Negotiation (A/N) and directly affects MDIO register bit 0.12. When input value = VMF1 or VMF4, A/N is disabled and 0.12 = 0. When input value = VMF2 or VMF3, A/N is enabled and 0.12 = 1.                                                                                                                                                                                                                                                                                                                                                                                              |

| 7        | MF1                | I       | Selects Repeater Mode and directly affects MDIO register bit 19.13.  When input value = VMF1 or VMF4, DTE Mode is enabled and 19.13 = 0.  When input value = VMF2 or VMF3, Repeater Mode is enabled and 19.13 = 1.                                                                                                                                                                                                                                                                                                                                                                                    |

| 6        | MF2                | I       | In TX mode, selects 4B Nibble (normal) or 5B Symbol Mode and directly affects MDIO register bit 19.4.  When input value = VMF1 or VMF4, 4B Nibble Mode is selected and 19.4 = 0.  When input value = VMF2 or VMF3, 5B Symbol Mode is selected and 19.4 = 1.                                                                                                                                                                                                                                                                                                                                           |

| 5        | MF3                | I       | In TX mode, enables or bypasses Scrambler operation and directly affects MDIO register bit 19.3.  When input value = VMF1 or VMF4, Scrambler is enabled and 19.3 = 0.  When input value = VMF2 or VMF3, Scrambler is bypassed and 19.3 = 1.  In FX mode, the LXT970 <i>automatically</i> bypasses the Scrambler. <i>Selecting</i> Scrambler bypass in FX mode will cause the LXT970 to also bypass the 4B/5B encoder and enable Symbol mode MII operation.                                                                                                                                            |

| 4        | MF4                | Ι       | <b>When A/N is enabled</b> , MF4 determines operating speed advertisement capabilities in combination with CFG1. See Table 9 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          |                    |         | When A/N is disabled, this input selects either TX or FX interface. When FX interface is selected, the LXT970 will automatically disable the scrambler. For correct FX operation, 100Mbps operation must also be selected.  When input value = VMF1 or VMF4, TX is enabled and 19.2 = 0.  When input value = VMF2 or VMF3, FX is enabled and 19.2 = 1.                                                                                                                                                                                                                                                |

| 1. I/O ( | Column Coding: I = | = Input |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Table 7: LXT970 Hardware Control Interface Signal Descriptions – continued

| Pin#     | Pin Name           | I/O     | Pin Description                                                                                                                                                                                                                                                                                                                                                                      |

|----------|--------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13       | FDE                | I       | Full Duplex Enable. When A/N is enabled, FDE determines full duplex advertisement capability in combination with MF4 and CFG1. See Table 9 for details.  When A/N is disabled, FDE directly affects full duplex operation and determines the value of bit 0.8 (Duplex Mode).  When FDE is High, F/D is enabled and 0.8 = 1.  When FDE is Low, F/D is disabled and 0.8 = 0.           |

| 14       | CFG0               | I       | Configuration Control 0. When A/N is enabled, Low to High transition on CFG0 causes auto-negotiate to re-start and 0.9 = 1.  When A/N is disabled, this input selects operating speed and directly affects bit 0.13. When CFG0 is High, 100Mbps is selected and 0.13 = 1. When CFG0 is Low, 10Mbps is selected and 0.13 = 0.                                                         |

| 33       | CFG1               | Ι       | Configuration Control 1.  When A/N is enabled, CFG1 determines operating speed advertisement capabilities in combination with MF4. See Table 9 for details.  When A/N is disabled, CFG1 enables 10Mbps link test function and directly affects bit 19.8.  When CFG1 is High, 10Mbps link test is disabled and 19.8 = 1.  When CFG1 is Low, 10Mbps link test is enabled and 19.8 = 0. |

| 1. I/O ( | Column Coding: I = | = Input |                                                                                                                                                                                                                                                                                                                                                                                      |

Table 8: MF Pin Function Descriptions 1, 3

| Pin  | Address                                                                                                                                                               | Input Voltage Levels <sup>2</sup> |                           |                           |                           |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------|---------------------------|---------------------------|--|--|

| FIII | Function                                                                                                                                                              | VMF1                              | VmF2                      | VMF3                      | VmF4                      |  |  |

| MF0  | Address Bit 0                                                                                                                                                         | 1                                 | 1                         | 0                         | 0                         |  |  |

|      | Auto-Negotiation Sets the initial value of bit 0.12                                                                                                                   | Disabled (0.12 = 0)               | Enabled (0.12 = 1)        | Enabled (0.12 = 1)        | Disabled (0.12 = 0)       |  |  |

| MF1  | Address Bit 1                                                                                                                                                         | 1                                 | 1                         | 0                         | 0                         |  |  |

|      | Repeater / DTE Mode<br>Sets the initial value of bit 19.13                                                                                                            | DTE (19.13 = 0)                   | Repeater (19.13 = 1)      | Repeater (19.13 = 1)      | DTE (19.13 = 0)           |  |  |

| MF2  | Address Bit 2                                                                                                                                                         | 1                                 | 1                         | 0                         | 0                         |  |  |

|      | Nibble (4B) / Symbol (5B) Mode<br>Sets the initial value of bit 19.4                                                                                                  | Nibble (4B)<br>(19.4 = 0)         | Symbol (5B)<br>(19.4 = 1) | Symbol (5B)<br>(19.4 = 1) | Nibble (4B)<br>(19.4 = 0) |  |  |

| MF3  | Address Bit 3                                                                                                                                                         | 1                                 | 1                         | 0                         | 0                         |  |  |

|      | Scrambler Operation Sets the initial value of bit 19.3                                                                                                                | Enabled (19.3 = 0)                | Bypassed (19.3 = 1)       | Bypassed (19.3 = 1)       | Enabled (19.3 = 0)        |  |  |

| MF4  | Address Bit 4                                                                                                                                                         | 1                                 | 1                         | 0                         | 0                         |  |  |

|      | If Auto-Negotiate Enabled via MF0, MF4 works in combination with CFG1 to control of and duplex advertisement capabilities via bits 4.5 through 4.8. See Table 9 for d |                                   |                           |                           |                           |  |  |

|      | If Auto-Negotiate Disabled via MF0 Then TX/FX Mode Sets the initial value of bit 19.2                                                                                 | 100TX<br>(19.2 = 0)               | 100FX<br>(19.2 = 1)       | 100FX<br>(19.2 = 1)       | 100TX<br>(19.2 = 0)       |  |  |

<sup>1.</sup> In MDIO Control Mode, the MF pins control only the initial or default value for the respective register bits. In Manual Control mode, the MF pins provide continuous control of the respective register bits.

<sup>2.</sup> Input Voltage Levels (VMF1, VMF2, VMF3, VMF4) for MF pins.

<sup>3.</sup> See Tables 10 and 11 for operating configuration set-up.

| Table 9: LX1970 C                        | Table 9: LXT970 Operating Speed/Full Duplex Advertisement Settings |      |                                                      |                                              |  |  |  |  |  |  |

|------------------------------------------|--------------------------------------------------------------------|------|------------------------------------------------------|----------------------------------------------|--|--|--|--|--|--|

| MF4 Input<br>Voltage Levels <sup>2</sup> | CFG1                                                               | FDE  | MDIO Registers <sup>1</sup>                          | Function                                     |  |  |  |  |  |  |

| If Auto-Negotiate Enabled via MF0        |                                                                    |      |                                                      |                                              |  |  |  |  |  |  |

| VMF1, VMF4                               | Low                                                                | _    | Sets 4.5, 4.6, 4.7 and 4.8 = 1                       | Advertise all capabilities<br>Ignore FDE     |  |  |  |  |  |  |

| VMF1, VMF4                               | High                                                               | High | Sets 4.5 = 1<br>Sets 4.7 and 4.8 = 0<br>Sets 4.6 = 1 | Advertise 10 Mbps only<br>FD Advertised      |  |  |  |  |  |  |

|                                          |                                                                    | Low  | Sets 4.5 = 1<br>Sets 4.7 and 4.8 = 0<br>Sets 4.6 = 0 | Advertise 10 Mbps only<br>FD Not Advertised  |  |  |  |  |  |  |

| VMF2, VMF3                               | Low                                                                | High | Sets 4.7 = 1<br>Sets 4.5 and 4.6 = 0<br>Sets 4.8 = 1 | Advertise 100 Mbps only<br>FD Advertised     |  |  |  |  |  |  |

|                                          |                                                                    | Low  | Sets 4.7 = 1<br>Sets 4.5 and 4.6 = 0<br>Sets 4.8 = 0 | Advertise 100 Mbps only<br>FD Not Advertised |  |  |  |  |  |  |

| VMF2, VMF3                               | High                                                               | High | Sets 4.5 and 4.7 = 1<br>Sets 4.6 and 4.8 = 1         | Advertise 10/100 Mbps<br>FD Advertised       |  |  |  |  |  |  |

| _                                        |                                                                    | Low  | Sets 4.5 and 4.7 = 1<br>Sets 4.6 and 4.8 = 0         | Advertise 10/100 Mbps<br>FD Not Advertised   |  |  |  |  |  |  |

# **FUNCTIONAL DESCRIPTION**

### Introduction

The LXT970 Fast Ethernet Transceiver is a physical layer (PHY) device that supports 10 Mbps and 100 Mbps Ethernet networks. It provides all the functions necessary to build an IEEE 802.3 compliant solution. The LXT970 can directly drive a twisted-pair cable for up to 100 meters. The LXT970 also provides a pseudo-ECL interface for driving a 100BASE-FX fiber connection.

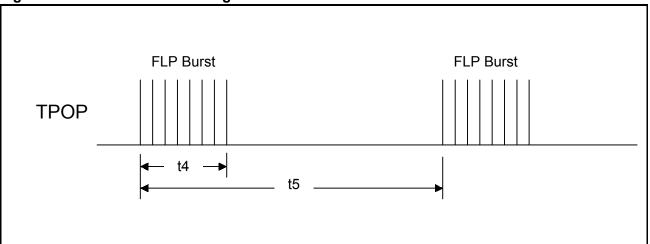

On power-up, the LXT970 can use auto-negotiation with parallel detection to automatically determine line operating conditions. If the PHY device on the other side of the link supports auto-negotiation, the LXT970 will auto-negotiate with it using Fast Link Pulse (FLP) Bursts. If the PHY partner does not support auto-negotiation, the LXT970 will automatically detect the presence of either link pulses (10 Mbps PHY) or Idle symbols (100 Mbps PHY) and set its operating speed accordingly. When the line speed selection is made via the parallel detection method, the duplex mode will be set to half. The user may later select full duplex operation by subsequent writes to the appropriate MDIO register. Line operation can also be set using the Hardware Control Interface.

The LXT970 interfaces to a 10/100 MAC through the MII interface. The LXT970 performs all functions of the Physical Coding Sublayer (PCS) and Physical Media Attachment (PMA) sublayer as defined in the IEEE 802.3 100BASE-X specification. It also performs all functions of the Physical Media Dependent (PMD) sublayer for 100BASE-TX connections. The MII speed is automatically set once line operating conditions have been determined.

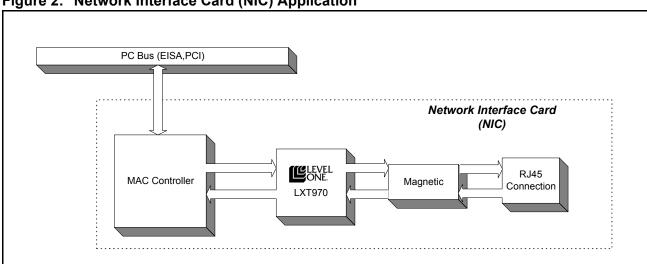

The LXT970 supports NIC, repeater and switch applications. It provides half- and full-duplex operation at 100Mbps and 10Mbps. See Figure 2 for a typical Network Interface Card (NIC).

#### NOTE

The LXT970 supports the 802.3 MDIO register set. Specific bits in the registers are referenced using an "X.Y" notation, where X is the register address (0-31) and Y is the bit number (0:15).

Figure 2: Network Interface Card (NIC) Application

# Network Media / Protocol Support

The LXT970 supports both 10BASE-T and 100BASE-TX Ethernet over twisted-pair, or 100 Mbps Ethernet over fiber media (100BASE-FX). A standard Media Independent Interface (MII) is used for communication with the Media Access Controller (MAC).

# 10/100 Mbps Twisted Pair Interface

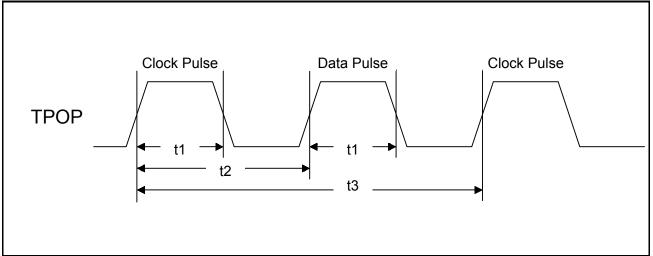

The twisted-pair interface consists of two differential pairs: the Twisted-Pair Input (TPIP/N) for receiving data, and the Twisted-Pair Output (TPOP/N) for transmitting data. This interface is used for both 10Mbps and 100Mbps operation. Auto-negotiation/parallel detection or manual control can be used to determine operation of the twisted-pair interface.

When operating at 100Mbps, MLT3 symbols are continuously transmitted and received. When not transmitting data, the LXT970 generates "IDLE" symbols.

During 10Mbps operation, Manchester encoded data is exchanged. During idle periods, the line is left in an idle voltage state.

In 100Mbps mode, the LXT970 is capable of driving a 100BASE-TX connection over  $100\Omega$ , Category 5, Unshielded Twisted Pair (UTP). A 10BASE-T connection can be supported using  $100\Omega$ , Category 3 or Category 5, UTP.

A transformer with 1:1 windings for transmit and receive, load resistors and bypass capacitors are all that is needed to complete this interface. The Transmit Reference (TREF) pin is used to supply +5V to the output transformer center tap. Using Level One's patented waveshaping technology, the transmitter pre-distorts the outgoing signal to reduce the need for external filters for EMI compliance.

When the twisted-pair interface is selected the FIBOP/N drivers are disabled. All data presented on the FIBIP/N input pins is ignored. In applications where the fiber interface is not used, the fiber I/O pins (FIBIP/N and FIBOP/N) may be left unconnected.

# 100 Mbps Fiber Interface

The LXT970 provides a pseudo-ECL interface that complies with the ANSI X3.166 specification. This interface is suitable for driving a fiber-optic coupler. This interface consists of four signals: FIBIP/N are the input pair and FIBOP/N are the output pair. The Fiber Port cannot be enabled via auto-negotiation, it must be enabled via the Hardware Control Interface or MDIO registers. When the

fiber interface is selected, the TPOP/N drivers are disabled and the TREF pin is tri-stated. All data presented on the TPIP/N input pins is ignored. In applications where the twisted pair interface is not used, the twisted pair I/O pins (TPIP/N, TPOP/N and TREF) may be left unconnected.

### MII Interface

The MII Interface is specified in IEEE 802.3. For this discussion, the MII is divided into two blocks; the MII Data Interface and the MII Management Interface.

### **MII Data Interface**

This interface is used to pass data between the LXT970 and a Media Access Controller (MAC). The MII operates at either 2.5 MHz or 25 MHz, depending on the network link speed.

Ten signals are used to pass received data to the MAC: RXD<4:0>, RX\_CLK, RX\_DV, RX\_ER, COL and CRS. Eight signals are used to transmit data from the MAC: TXD<4:0>, TX CLK, TX EN, and TX ER.

### Nibble (4B) vs. Symbol (5B) Mode

In nibble mode (19.4 = 0), 4-bit nibbles are passed across the MII data interface. RXD4 is set Low and TXD4 is ignored.

In symbol mode (19.4 = 1), 5-bit symbols are passed across the MII data interface. RXD4 and TXD4 are active.

#### DTE vs. Repeater Mode

In DTE mode (19.13 = 0), the LXT970 asserts RX\_DV, RXD, RX\_CLK and RX\_ER as soon as it receives a packet from the network. In repeater mode (19.13 = 1), when TRSTE input is High, these output signals are tri-stated. This allows multiple LXT970's to share a single MII Interface and an external arbiter to determine which LXT970 should drive the MII Data Interface.

### **Loopback Operation**

Loopback is determined by the operational state of the device and by bits 0.14 and 19.11. Bit 0.14 controls MII loopback test at both 10 and 100Mbps. Bit 19.11 controls normal twisted-pair loopback during 10Mbps, half-duplex operation. CRS is generated when the LXT970 is receiving data during all modes of operation.

Full Duplex - During full duplex mode loopback and collision detection are always disabled. CRS is not generated on transmission.

- Repeater Mode (bit 19.13 = 1) During repeater mode, loopback is disabled. CRS is not generated on transmit and collision detection is enabled.

- Half-Duplex/DTE Mode (10Mbps) If 19.11 = 0 (default), data is looped back. If 19.11 = 1, data is not looped back. In both cases CRS is generated on transmit and collision detection is enabled.

- Half-Duplex/DTE Mode (100Mbps) Data is not looped back. CRS is generated on transmit and collision detection is enabled.

- Loopback Test Register bit 0.14 controls the MII loopback function. This capability is provided for diagnostics. Setting bit 0.14 = 1, causes the LXT970 to disconnect from the media interface and any data transmitted will be looped back to the receiver. No data will be sent or received from the media when this mode is enabled. When this diagnostic loopback is enabled, bit 0.7 can be used to test the operation of the COL pin.

### **MII Management Interface**

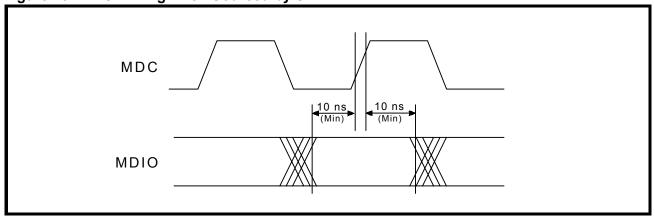

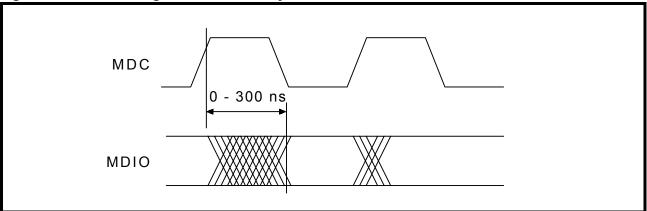

The LXT970 supports the IEEE 802.3 MII Management Interface also known as the Management Data Input/Output (MDIO) Interface. This interface allows upper-layer devices to monitor and control the state of the LXT970.

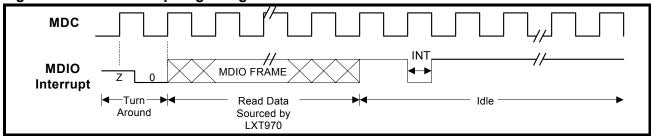

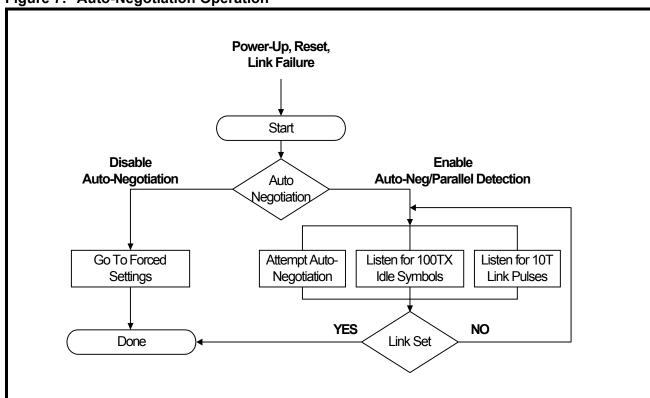

MDIO interface consists of a physical connection, a specific protocol which runs across the connection, and an internal set of addressable registers. The physical interface consists of a data line (MDIO) and clock line (MDC), a control line (MDDIS) and an optional interrupt line (MDINT). The LXT970 can signal an interrupt using the MDIO signal as shown in Figure 3. The user can also assign a separate pin for this function. If Bit 17.1 = 1, pin 2 (FDS/MDINT) will be used as an MDINT pin.

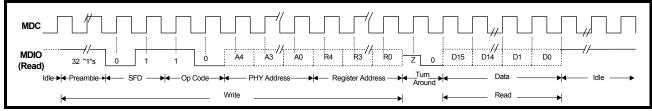

Operation of this interface is controlled by the MDDIS input pin. When MDDIS is High, the MDIO operates as a read-only interface. When MDDIS is Low, read and write are enabled. The timing for the MDIO Interface is shown in Table 40. Read and write operations are shown in Figures 4 and 5. The protocol allows one controller to communicate with multiple LXT970 devices; each LXT970 is assigned an address between 0 and 31.

The LXT970 supports twelve 16-bit MDIO registers. Registers 0-7 are required and their functions are specified by the IEEE 802.3 specification. Additional registers are included for expanded functionality. The MDIO Register set for the LXT970 is described in Tables 43 through 54. Specific bits in the registers are referenced using an "X.Y" notation, where X is the register number (0-31) and Y is the bit number (0-15).

Figure 3: MDIO Interrupt Signaling

Figure 4: Management Interface - Read Frame Structure

Figure 5: Management Interface - Write Frame Structure

# Hardware Control Interface

The Hardware Control Interface consists of MF<4:0>, CFG<1:0> and FDE input pins. This interface is used to configure operating characteristics of the LXT970 and to determine the MDIO Address. When MDDIS is Low, the Hardware Control Interface provides initial values for the MDIO registers, and then passes control to the MDIO Interface.

When MDDIS is High, the Hardware Control Interface provides continuous control over the LXT970. Individual chip addressing allows multiple LXT970 devices to share the MII in either mode. Tables 10, 11 and 12 show how to set-up the desired operating configurations using the Hardware Control Interface.

Table 10: Configuring the LXT970 via Hardware Control

| Desired Configuration                                          | Pin Name          | Input Value | MDIO Registers                        |

|----------------------------------------------------------------|-------------------|-------------|---------------------------------------|

| Auto-Negotiation Enabled <sup>1</sup>                          | MF0               | VMF2, VMF3  | 0.12 = 1                              |

| Auto-Negotiation Disabled <sup>2</sup>                         | MF0               | VMF1, VMF4  | 0.12 = 0                              |

| Normal Operation<br>(PHY Mode, Nibble Mode, Scrambler Enabled) | MF1<br>MF2<br>MF3 | VMF1, VMF4  | $ 19.13 = 0 \\ 19.4 = 0 \\ 19.3 = 0 $ |

| Repeater Mode                                                  | MF1               | VMF2, VMF3  | 19.13 = 1                             |

| Symbol Mode                                                    | MF2               | VMF2, VMF3  | 19.4 = 1                              |

| Scrambler Bypass Mode                                          | MF3               | VMF2, VMF3  | 19.3 = 1                              |

<sup>1.</sup> Refer to Table 11 for Hardware Control Interface functions available when auto-negotiation is enabled.

Table 11: LXT970 Operating Configurations / Auto-Negotiation Enabled

| Desired                      |            | MDIO Registers |        |     |     |     |     |

|------------------------------|------------|----------------|--------|-----|-----|-----|-----|

| Configuration <sup>1,2</sup> | MF4        | F4 CFG1 FDE    |        | 4.5 | 4.6 | 4.7 | 4.8 |

| Advertise All                | VMF1, VMF4 | Low            | Ignore | 1   | 1   | 1   | 1   |

| Advertise 100 HD             | VMF2, VMF3 | Low            | Low    | 0   | 0   | 1   | 0   |

| Advertise 100 HD/FD          | VMF2, VMF3 | Low            | High   | 0   | 0   | 1   | 1   |

| Advertise 10 HD              | VMF1, VMF4 | High           | Low    | 1   | 0   | 0   | 0   |

| Advertise 10 HD/FD           | VMF1, VMF4 | High           | High   | 1   | 1   | 0   | 0   |

| Advertise 10/100 HD          | VMF2, VMF3 | High           | Low    | 1   | 0   | 1   | 0   |

<sup>1.</sup> Refer to Table 10 for basic configurations.

<sup>2.</sup> Refer to Table 12 for Hardware Control Interface functions available when auto-negotiation is disabled.

<sup>2.</sup> Refer to Table 12 for Hardware Control Interface functions available when auto-negotiation is disabled.

Table 12: LXT970 Operating Configurations / Auto-Negotiation Disabled

| Desired Configuration <sup>1,2</sup> | Pin Name | Input Value | MDIO Registers |

|--------------------------------------|----------|-------------|----------------|

| Force 100FX Operation                | MF4      | VMF2, VMF3  | 19.2 = 1       |

| Force 100TX Operation                | MF4      | VMF1, VMF4  | 19.2 = 0       |

|                                      | CFG0     | High        | 0.13 = 1       |

| Force 10T Operation                  | MF4      | VMF1, VMF4  | 19.2 = 0       |

|                                      | CFG0     | Low         | 0.13 = 0       |

| Force Full Duplex Operation          | FDE      | High        | 0.8 = 1        |

| Disable 10T Link Test                | CFG1     | High        | 19.8 = 1       |

| Enable 10T Link Test                 | CFG1     | Low         | 19.8 = 0       |

<sup>1.</sup> Refer to Table 10 for basic configurations.

<sup>2.</sup> Refer to Table 11 for Hardware Control Interface functions available when auto-negotiation is enabled.

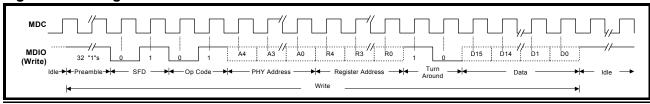

# Initialization

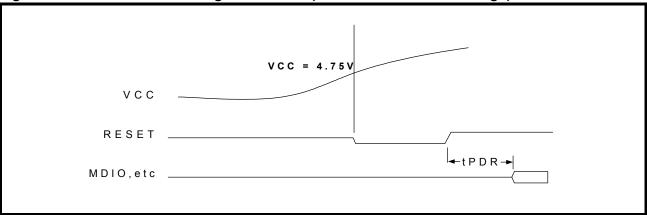

At power-up or reset, the LXT970 performs the initialization as shown in Figure 6. When pin 15 (MDDIS) is High, the LXT970 enters Manual Control Mode. When MDDIS is Low, MDIO Control Mode is enabled. Mode control selection is provided via the MDDIS pin as shown in Table

### **MDIO Control Mode**

In the MDIO Control mode, the LXT970 uses the Hardware Control Interface to set up initial (default) values of the MDIO registers. Once initial values are set, bit control reverts to the MDIO interface.

### **Manual Control Mode**

In the Manual Control Mode, LXT970 disables direct write operations to the MDIO registers on the MDIO interface. The Hardware Control Interface is continuously monitored and the MDIO registers are updated accordingly.

**Table 13: Mode Control Settings**

| MDDIS<br>Pin 15 | RESET<br>Pin 16 | PWRDWN<br>Pin 34 | Mode           |

|-----------------|-----------------|------------------|----------------|

| Low             | High            | Low              | MDIO Control   |

| High            | High            | Low              | Manual Control |

| -               | Low             | Low              | Reset          |

| -               | -               | High             | Power Down     |

# **Link Configuration**

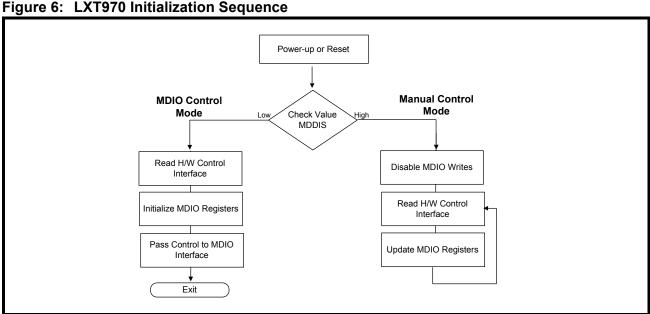

When the LXT970 is first powered on, reset, or encounters a link failure state, it must determine the line speed and operating conditions to use for the network link.

The LXT970 first checks the MDIO registers (initialized via the Hardware Control Interface or software) for operating instructions. Using these mechanisms, the user can command the LXT970 to do one of the following:

- Force 100FX (Fiber)

- Force twisted-pair link operation to:

100TX, Full Duplex 100TX, Half Duplex 10BASE-T, Full Duplex 10BASE-T, Half Duplex

• Allow auto-negotiation/parallel-detection.

In the first two cases, the LXT970 immediately begins operating the network interface as commanded. In the third case, the LXT970 begins the auto-negotiation/paralleldetection operation.

# **Auto-Negotiation**

At power-up or reset, with auto-negotiation enabled, the LXT970 attempts to establish link operating conditions with its partner by sending FLP (Fast Link Pulse) bursts. By exchanging FLP bursts, the LXT970 and its link partner communicate their capabilities to each other. Each side finds the highest common capabilities that both sides can support and then begins operating in that mode.

### **Parallel Detection**

In parallel with auto-negotiation, the LXT970 also checks for 10 Mbps Normal Link Pulses (NLP) or 100 Mbps Idle symbols. If either is detected, the device automatically configures to match the detected operating speed in half duplex mode. This ability allows the LXT970 to communicate with devices that do not support auto-negotiation.

### **Controlling Auto-Negotiation**

When auto-negotiation is controlled by software, the following steps are recommended:

- After power-up, power down, or reset, the power down recovery time, as specified in Table 41, must be exhausted before proceeding.

- Set MDIO Register 4 advertisement capabilities before enabling auto-negotiation by setting MDIO bit 0.12 = 1

# Monitoring Auto-Negotiation

When auto-negotiation is being monitored, the following apply:

- Bit 20.13 is set to 1 once the link is established

- Bits 20.12 and 20.11 can be used to determine the link operating conditions (speed and duplex)

- Operation can be forced by disabling auto-negotiation (bit 0.12 = 0) and setting bits 0.13, 0.8 and 19.2

Figure 7: Auto-Negotiation Operation

# 100 Mbps Operation

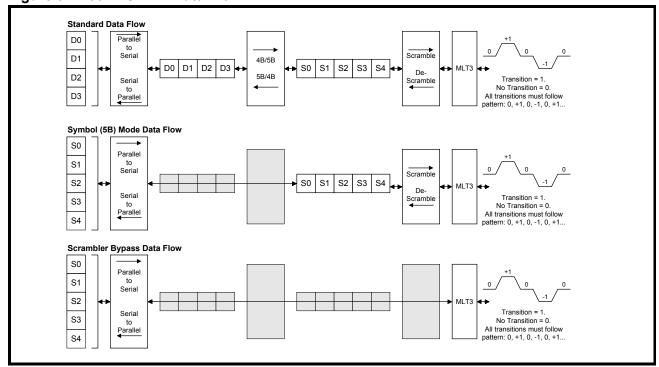

The MAC transmits data to the LXT970 over the MII. In 100BASE-TX mode, the LXT970 encodes and scrambles the data, then transmits it using MLT-3 signalling. The LXT970 descrambles and decodes MLT-3 data received from the network. In 100BASE-FX mode, the LXT970 transmits and receives data as NRZI signals.

When the MAC is not actively transmitting data, the LXT970 sends out Idle symbols on the line.

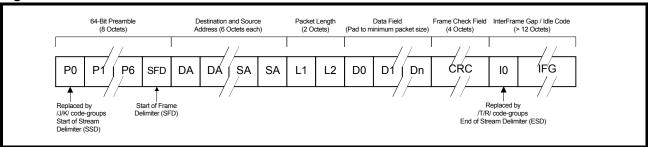

As shown in Figure 8, the MAC starts each transmission with a preamble pattern. When TX\_EN is asserted, the LXT970 transmits a J/K symbol to the network (Start of Stream Delimiter or SSD). It then encodes and transmits

the rest of the packet, including the balance of the preamble, the SFD (Start of Frame Delimiter), packet data, and CRC. Once the packet ends, the LXT970 transmits the T/R symbol (End of Stream Delimiter or ESD) and then returns to transmitting Idle symbols.

Normally, 4-bit wide nibble data is transmitted across the MII interface and RXD4/TXD4 are ignored. The encoder translates the 4-bit nibbles into 5-bit symbols which are sent over the 100BASE-X connection. In Symbol Mode, a fifth bit is provided (RXD4/TXD4) to allow a 5-bit symbol to be sent across the MII interface.

Figure 9 shows the data conversion flow from nibbles to symbols. Table 14 shows 4B/5B symbol coding. Note that some symbols are invalid.

Figure 8: 100BASE-TX Frame Structure

Figure 9: 100BASE-TX Data Flow

Table 14: 4B/5B Coding

| Code Type | 4B Code<br>3 2 1 0          | Name           | 5B Symbol<br>4 3 2 1 0 | Interpretation                                 |

|-----------|-----------------------------|----------------|------------------------|------------------------------------------------|

|           | 0 0 0 0                     | 0              | 11110                  | Data 0                                         |

|           | 0 0 0 1                     | 1              | 0 1 0 0 1              | Data 1                                         |

|           | 0 0 1 0                     | 2              | 10100                  | Data 2                                         |

|           | 0 0 1 1                     | 3              | 1 0 1 0 1              | Data 3                                         |

|           | 0 1 0 0                     | 4              | 01010                  | Data 4                                         |

|           | 0 1 0 1                     | 5              | 0 1 0 1 1              | Data 5                                         |

|           | 0 1 1 0                     | 6              | 01110                  | Data 6                                         |

| DATA      | 0 1 1 1                     | 7              | 01111                  | Data 7                                         |

|           | 1 0 0 0                     | 8              | 10010                  | Data 8                                         |

|           | 1 0 0 1                     | 9              | 10011                  | Data 9                                         |

|           | 1 0 1 0                     | A              | 10110                  | Data A                                         |

|           | 1 0 1 1                     | В              | 1 0 1 1 1              | Data B                                         |

|           | 1 1 0 0                     | С              | 1 1 0 1 0              | Data C                                         |

|           | 1 1 0 1                     | D              | 1 1 0 1 1              | Data D                                         |

|           | 1 1 1 0                     | Е              | 11100                  | Data E                                         |

|           | 1111                        | F              | 1 1 1 0 1              | Data F                                         |

| IDLE      | undefined                   | I 1            | 11111                  | Idle. Used as inter-stream fill code           |

|           | 0 1 0 1                     | J <sup>2</sup> | 1 1 0 0 0              | Start-of-Stream Delimiter (SSD), part 1 of 2   |

| CONTROL   | 0 1 0 1                     | K <sup>2</sup> | 1 0 0 0 1              | Start-of-Stream Delimiter (SSD), part 2 of 2   |

|           | undefined                   | T <sup>3</sup> | 0 1 1 0 1              | End-of-Stream Delimiter (SSD), part 1 of 2     |

|           | undefined                   | R <sup>3</sup> | 0 0 1 1 1              | End-of-Stream Delimiter (SSD), part 2 of 2     |

|           | undefined                   | H <sup>4</sup> | 0 0 1 0 0              | Transmit Error. Used to force signaling errors |

|           | undefined                   | Invalid        | 0 0 0 0 0              | Invalid                                        |

|           | undefined                   | Invalid        | 0 0 0 0 1              | Invalid                                        |

|           | undefined                   | Invalid        | 0 0 0 1 0              | Invalid                                        |

| INVALID   | undefined                   | Invalid        | 0 0 0 1 1              | Invalid                                        |

|           | undefined Invalid 0 0 1 0 1 |                | 0 0 1 0 1              | Invalid                                        |

|           | undefined                   | Invalid        | 0 0 1 1 0              | Invalid                                        |

|           | undefined                   | Invalid        | 0 1 0 0 0              | Invalid                                        |

|           | undefined                   | Invalid        | 01100                  | Invalid                                        |

|           | undefined                   | Invalid        | 10000                  | Invalid                                        |

|           | undefined                   | Invalid        | 1 1 0 0 1              | Invalid                                        |

<sup>1.</sup> The /I/ (Idle) code-group is sent continuously between frames.

<sup>3.</sup> The /T/ and /R/ (ESD) code-groups are always sent in pairs; /R/ follows /T/.

<sup>4.</sup> An /H/ (Error) code-group is used to signal an error condition.

### **5B Symbol Mode**

In Symbol Mode, raw 5-bit symbol data is passed directly across the MII interface and the encoder is bypassed. Symbol Mode is selected by setting bit 19.4 = 1 or by setting input pin MF2 = VMF2 or VMF3.

This mode reduces device latency for use in repeater applications. See Table 31 and 32 for timing parameters.

### **Scrambler Seeding**

Once the transmit data (or Idle symbols) are properly encoded, they are scrambled to further reduce EMI and to spread the power spectrum using an 11-bit scrambler seed. Ten seed bits are determined by MF<4:0> inputs and LED outputs, and one bit is randomly determined.

# **Scrambler Bypass**

The scrambler/descrambler can be bypassed by either setting bit 19.3 = 1 or setting input pin MF3 to VMF2/VMF3. The scrambler is automatically bypassed when the fiber port is enabled. Symbol Mode (5B) must also be enabled for the LXT970 to work properly while in Scrambler Bypass Mode. Scrambler Bypass is provided for diagnostic and test support.

### **Link Failure**

Link failure is declared when an excessive number (250 out of 1000) of invalid symbols are received. The LXT970 reports link failure via the MII status bits (1.2, 18.15 and 20.13) and interrupt functions. If auto-negotiation is enabled, link failure causes the LXT970 to re-negotiate.

### Link Failure Override

The LXT970 will normally transmit 100Mbps data packets only if it detects the link is up, and transmits only Idle symbols or FLP bursts if the link is not up. Setting bit 19.14 = 1 overrides this function, allowing the LXT970 to transmit data packets even when the link is down. This feature is provided as a diagnostic tool. Note that auto-negotiation

must be disabled to transmit data packets in the absence of link. If auto-negotiation is enabled, the LXT970 will auto-matically begin transmitting FLP bursts if the link goes down.

### **Baseline Wander Correction**

The LXT970 provides a baseline wander correction function which makes the device robust under all network operating conditions. The MLT3 coding scheme used in 100BASE-TX is by definition "unbalanced". This means that the DC average value of the signal voltage can "wander" significantly over short time intervals (tenths of seconds). This wander can cause receiver errors, particularly at long line lengths (100 meters). The exact characteristics of the wander are completely data dependent. "Killer Packets" have been created that exhibit worst case baseline wander characteristics. The LXT970 baseline wander correction characteristics allow the LXT970 to recover error-free data, even at long line lengths.

### **FX Operation**

To enable 100BASE-FX operation, auto-negotiation must be disabled and FX selected.

- To disable auto-negotiation, set 0.12 = 0, or set MF0 = VMF1 or VMF4.

- To select FX, set 19.2 = 1, or set MF4 = VMF2 or VMF3.

In FX mode, the following conditions apply:

- CFG0 / 0.13 still controls speed and must be set to 1 for 100 Mbps operation.

- · Scrambler is automatically disabled.

- 5-bit symbol mode may be selected by setting 19.4 = 1, or setting MF2 = VMF2 or VMF3.

- Duplex operation is controlled by pin FDE or by bit 0.8.

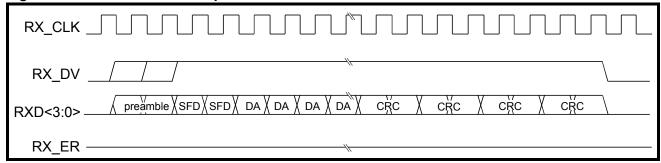

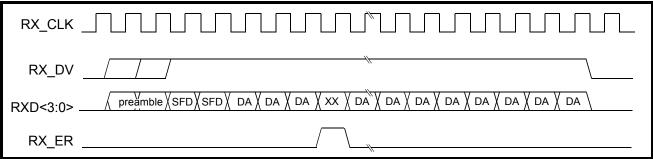

### **Data Errors**

Figure 10 shows normal reception. When the LXT970 receives invalid symbols from the line, it asserts RX\_ER, as shown in Figure 11.

### **Collision Indication**

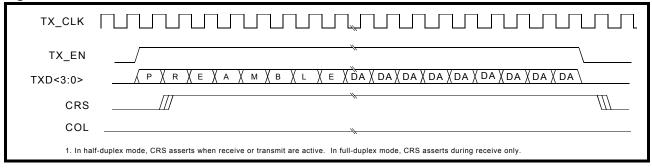

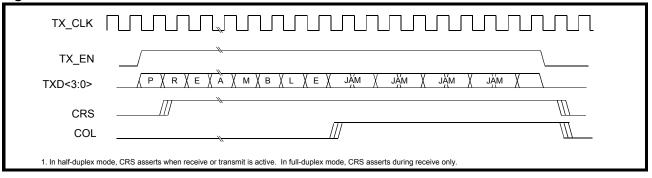

Figure 12 shows normal transmission. The LXT970 detects a collision if transmit and receive are active at the same time. As shown in Figure 13, upon detection of a collision, the COL output is asserted and remains asserted for the duration of the collision.

Figure 10: 100BASE-TX Reception with No Errors

Figure 11: 100BASE-TX Reception with Invalid Symbol

Figure 12: 100BASE-TX Transmission with No Errors

Figure 13: 100BASE-TX Transmission with Collision

# 10 Mbps Operation

The LXT970 will operate as a standard 10 Mbps transceiver. Data transmitted by the MAC as 4-bit nibbles is serialized, Manchester-encoded, and transmitted on the TPOP/N outputs. Received data is decoded, de-serialized into 4-bit nibbles and passed to the MAC across the MII. The LXT970 supports all the standard 10Mbps functions.

### **Link Test**

In 10 Mbps mode, the LXT970 always transmits link pulses. If the Link Test Function is enabled, it monitors the connection for link pulses. Once it detects 2 to 7 link pulses, data transmission will be enabled and will remain enabled as long as the link pulses or data transmission continues. If the link pulses stop, the data transmission will be disabled.

If the Link Test function is disabled, the LXT970 will transmit to the connection regardless of detected link pulses. The Link Test function can be disabled by setting Bit 19.8 = 1 or by setting MF0 to disable auto-negotiation and setting CFG1 input High.

### **SQE** (Heartbeat)

By default, the SQE (heartbeat) function is disabled on the LXT970. To enable this function, set bit 19.10 = 1. When this function is enabled, the LXT970 will assert its COL output for 5-15 BT after each packet. See Figure 24 for SQE timing parameters.

### **Jabber**

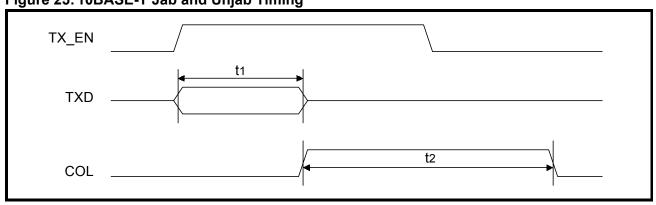

If the MAC begins a transmission that exceeds the jabber timer, the LXT970 disables the transmit and loopback functions and enables the COL pin. The LXT970 automatically exits jabber mode after 250-750ms. This function can be disabled by setting Bit 19.9 = 1. See Figure 25 for Jabber timing parameters.

### **Polarity Correction**

The LXT970 automatically detects and corrects for the condition where the receive signal (TPIP/N) is inverted. Reversed polarity is detected if 8 inverted link pulses, or 4 inverted end-of-frame markers, are received consecutively. If link pulses or data are not received for 96-128 ms, the polarity state is reset to a non-inverted state.

### Link Failure

Link failure occurs if Link Test is enabled and link pulses stop being received. If this condition occurs, the LXT970 returns to the auto-negotiation phase if auto-negotiation is enabled.

# **Operating Requirements Power Requirements**

The LXT970 requires four +5V supply inputs (VCCA, VCCD, VCCR and VCCT). These inputs may be supplied from a single source although decoupling is required to each respective ground. As a matter of good practice, these supplies should be as clean as possible. Typical filtering and decoupling are shown in the Application Information section, Figure 15. An additional supply is required for the MII (VCCIO). The MII supply may be either +5V or +3.3V. Power for the MII should be supplied from the same power source used for the controller on the other side of the MII interface.

### Low Voltage Fault Detect

The LXT970 has a low voltage fault detection function that prevents transmission of invalid symbols when VCC goes below normal operating levels. This function disables the transmit outputs when a low voltage fault on VCC occurs. If this condition happens, the LXT970 sets 20.2 = 1. Operation is automatically restored when VCC returns to normal. Table 24 indicates voltage levels used to detect and clear the low voltage fault condition.

#### **Power Down Mode**

The LXT970 goes into Power Down Mode when PWRDWN is asserted. In this mode, all functions are disabled except the MDIO. The power supply current is significantly reduced. Refer to Table 19 for power down specifications. This mode can be used for energy-efficient applications or for redundant applications where there are two devices and one is left as a stand-by. When the LXT970 is returned to normal operation, configuration settings of the MDIO registers are maintained.

# **Clock Requirements**

The LXT970 requires a constant clock that must be enabled at all times. Depending on the mode of operation, the clock may be supplied at the crystal oscillator pins (XI, XO), or at the Transmit Clock pin (TX\_CLK). There are two clock modes, master clock mode and slave clock mode. See Table 23 for input clock requirements.

#### **Master Clock Mode**

The Master Clock mode is recommended in most Network Interface Cards (NICs) and switch applications. In the Master Clock mode the LXT970 is the master clock source for data transmission, and requires a 25 MHz reference signal at XI.