### Features

- Eight fully independent, T1/E1/J1 framers

- 3.3V supply with 5V tolerant inputs

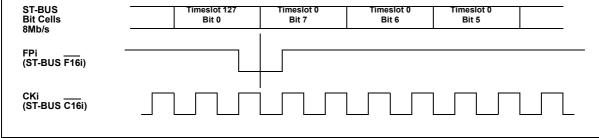

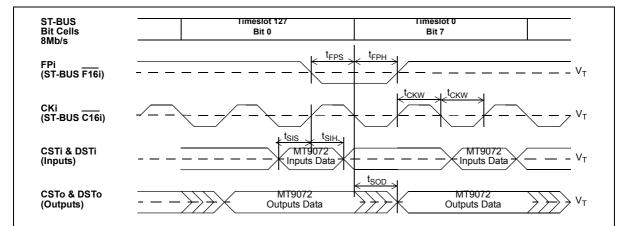

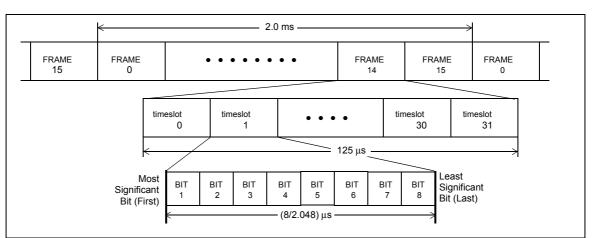

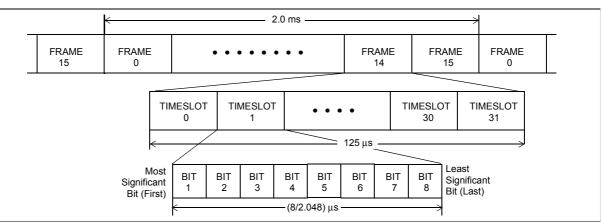

- Selectable 2.048 Mbit/s or 8.192 Mbit/s serial buses for both data and signaling

- Framing Modes:

- T1: D4, ESF, T1DM

- E1: Basic Framing, CRC4 multiframing and Signaling Multiframing

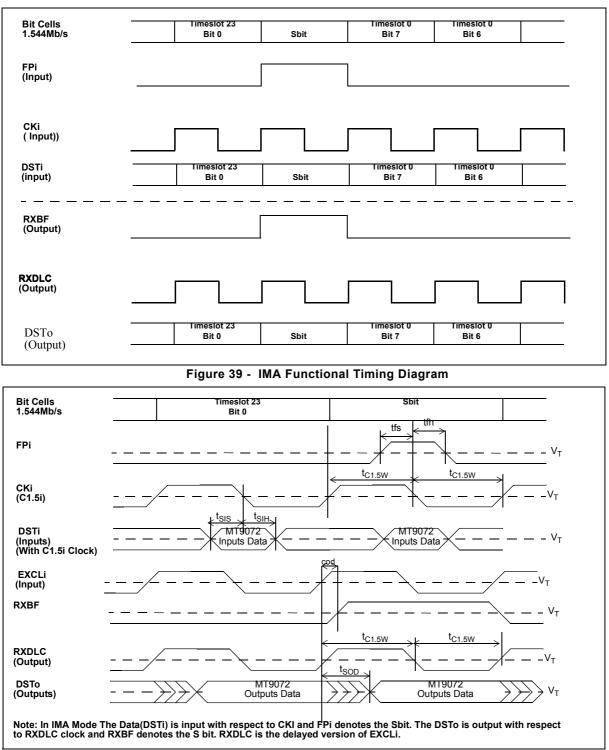

- Supports Inverse Mux for ATM

- Timeslot assignable HDLC

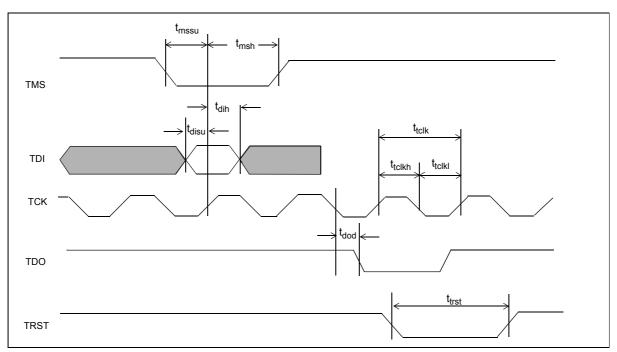

- IEEE-1149.1 (JTAG) test port

### **Applications**

- T1/E1/J1 add/drop multiplexers

- V5.1 and V5.2 access network interfaces

- CO and PBX equipment interfaces

- Primary rate IDSN nodes

- Digital Cross-connect Systems (DCS)

- Wireless base stations

Issue 4 September 2002

Ordering Information

MT9072AB208 Pin LQFP MT9072AV220 Pin LBGA

-40 to +85 <sup>0</sup>C

### Description

DS5063

The MT9072 is a multi-port T1/E1/J1 framing device that integrates eight fully independent, feature rich framers. The device is software selectable between T1, E1 or J1 modes and meets the latest relevant recommendations and standards from Telcordia, ANSI, ETSI and ITU-T. An extensive suite of features make the MT9072 very flexible and suitable for a wide variety of applications around the globe.

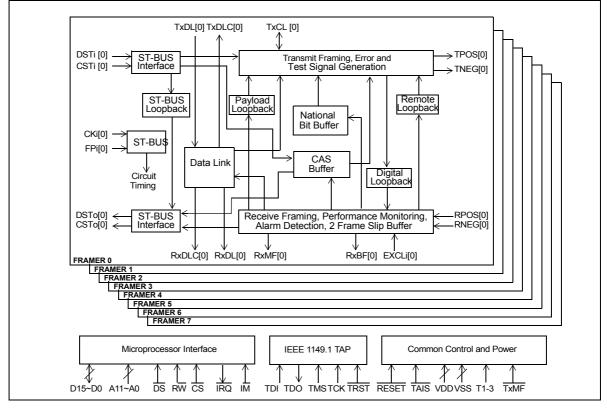

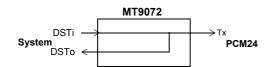

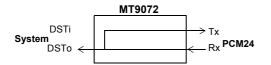

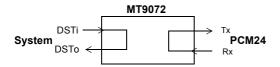

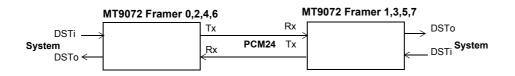

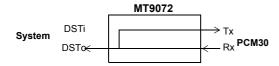

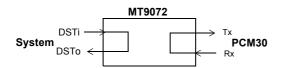

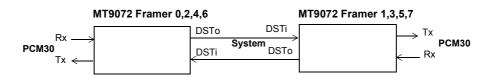

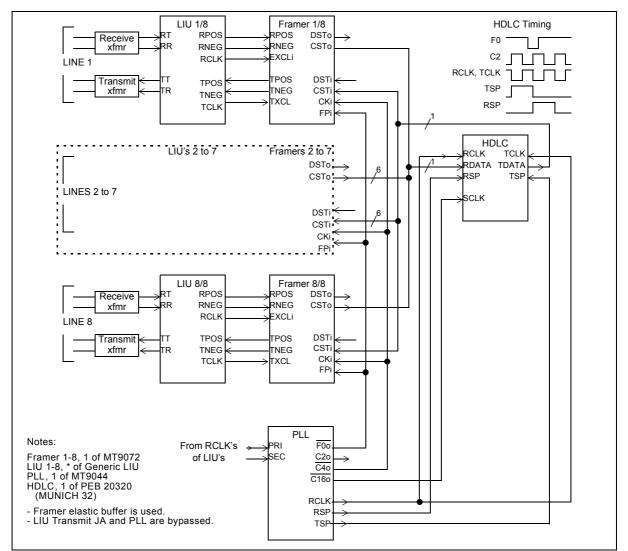

Figure 1 - Block Diagram

### **MT9072 Detailed Feature Summary Standards Compliance and Support** T1/J1 Mode E1 Mode ANSI: ETSI: T1.102, T1.231 TBR4, TBR13 T1.403, T1.408 ETS 300 233, ETS 300 347 (V5.2) AT&T: TR 62411, PUB43801 ITU-T: **Telcordia:** G.703, G.704, G.706, G.711, G.732 GR-303-CORE G.775, G.796, G.823, I.431 ITU-T: G.965 (V5.2) G.802

### TTC:

JT-G703, JT-G704

JT-G706

### Access and Control

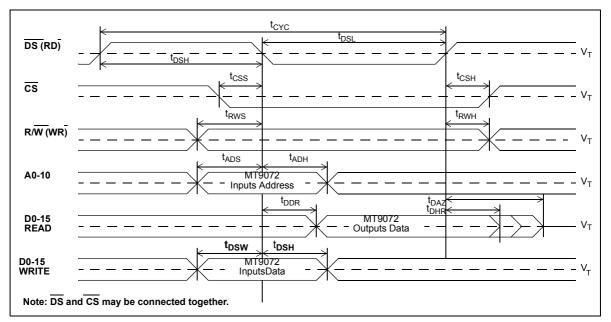

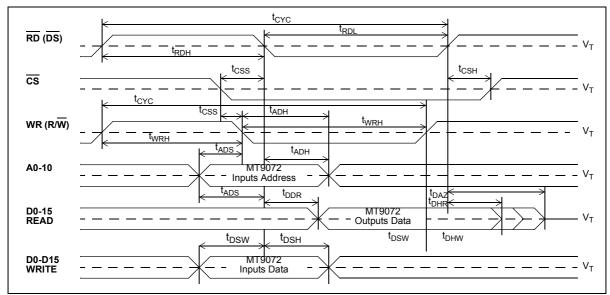

A 16-bit parallel Motorola or Intel non-multiplexed microprocessor interface is used to access the control and status registers.

### **Backplane Interfaces**

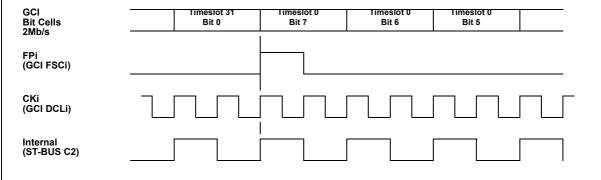

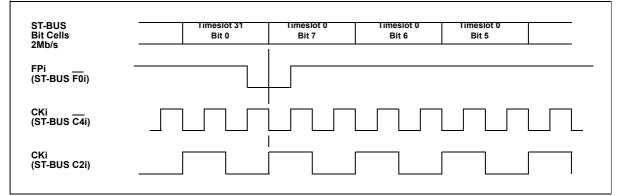

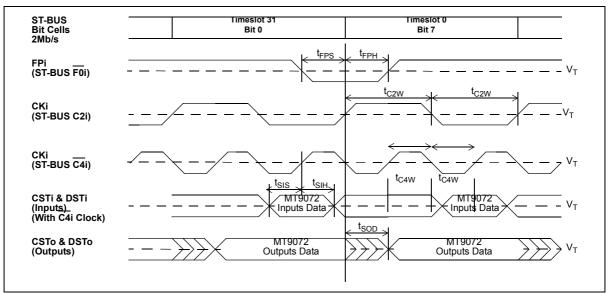

- 2.048Mbit/s or 8.192Mbit/s ST-BUS

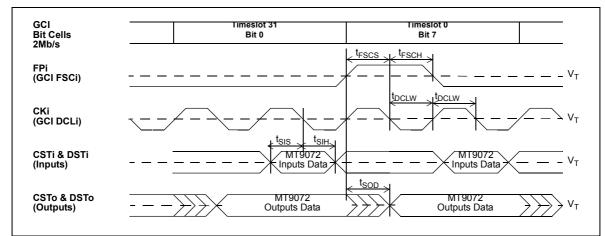

- 2.048Mbit/s GCI bus

- IMA (Inverse Mux for ATM) mode, 1.544Mbit/s (T1) or 2.048Mbit/s (E1) serial bus with asynchronous transmit and receive timing for Inverse MUX for ATM applications.

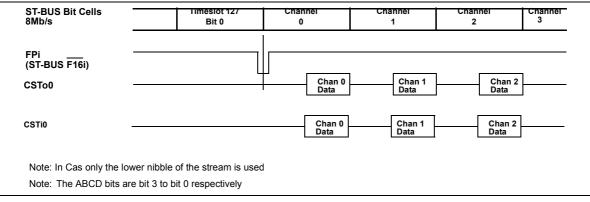

- · CSTo/CSTi pins can be used to access the receive/transmit signaling data

- RxDL pin can be used to access the entire B8ZS/HDB3 decoded receive stream including framing bits

- TxDL pin can be used to transmit data on the FDL (T1) or the Sa bits (E1)

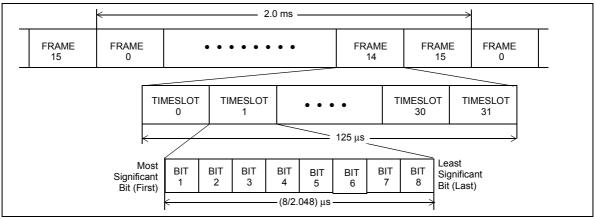

### T1/J1 Mode

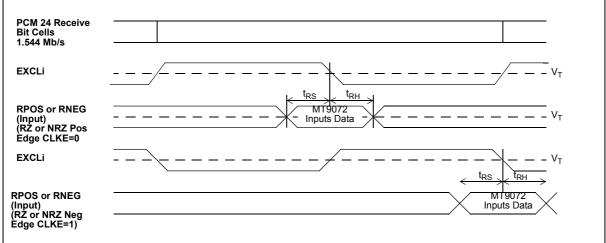

- PCM24 channels 1-24 are mapped to ST-BUS channels 0-23 respectively

- The framing-bit is mapped to ST-BUS channel 31

### E1 Mode

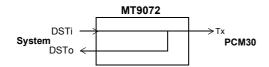

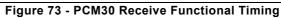

PCM30 timeslots 0-31 are mapped to ST-BUS channels 0-31 respectively

#### Data Link

#### T1/J1 Mode

- Three methods are provided to access the datalink:

- 1. TxDL and RxDL pins support transmit and receive datalinks

- 2. Bit Oriented Messages are supported via internal registers

- 3. An internal HDLC can be assigned to transmit/receive over the FDL in ESF mode

### E1 Mode

- Two methods are provided to access the datalink:

- 1. TxDL and RxDL pins support transmit and receive datalinks over the Sa4~Sa8 bits

- 2. An internal HDLC can be assigned to transmit/receive data via the Sa4~Sa8 bits

- In transparent mode, if the Sa4 bit is used for an intermediate datalink, the CRC-4 remainder can be updated to reflect changes to the Sa4 bit

#### One Embedded Floating HDLC per Framer

- Flag generation and Frame Check Sequence (FCS) generation and detection, zero insertion and deletion

- · Continuous flags, or continuous 1s are transmitted between frames

- Transmit frame-abort

- Invalid frame handling:

Frames yielding an incorrect FCS are tagged as bad packets

Frames with fewer than 25 bits are ignored

Frames with fewer than 32 bits between flags are tagged as bad packets

Frames interrupted by a Frame-Abort sequence remain in the FIFO and an interrupt is generated

- · Access is provided to the receive FCS

- · FCS generation can be inhibited for terminal adaptation

- · Recognizes single byte, dual byte and all call addresses

- · Independent, 32 byte deep transmit and receive FIFOs

- · Receive FIFO maskable interrupts for nearly full and overflow conditions

- · Transmit FIFO maskable interrupts for nearly empty and underflow conditions

- Maskable interrupts for transmit end-of-packet and receive end-of-packet

- Maskable interrupts for receive bad-frame (includes frame abort)

- · Transmit-to-receive and receive-to-transmit loopbacks are provided

- · Transmit and receive bit rates and enables are independent

- Frame aborts can be sent under software control and they are automatically transmitted in the event of a transmit FIFO underrun

### T1/J1 Mode

- Assignable to the ESF Facility Data Link or any other channel

- Operates at 4 kbit/s (FDL), 56 kbit/s or 64 kbit/s

### E1 Mode

- Assignable to timeslot-0, bits Sa4~Sa8 or any other timeslot

- Operates at 4, 8, 12, 16 or 20 kbit/s (Sa bits) or 64 kbit/s

# MT9072

### **Common Channel Signaling Timeslot Assigner**

Selected 64 Kbit/s CCS channels (for V5.2 and GR-303) can be routed to/from an external multichannel HDLC, using the CSTi/0 pins

#### Access and Monitoring for National (Sa) Bits (E1 mode only)

In addition to the datalink functions, the Sa bits can be accessed using:

- Single byte register

- •Five byte transmit and receive national bit buffers

- •A maskable interrupt is generated on the change of state of any Sa bit

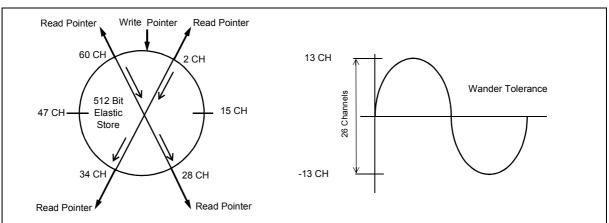

#### Slip Buffers

#### T1/J1 Mode

Transmit Slip Buffer

- Two-frame slip buffer capable of performing a controlled slip. Intended for rate conversion in the transmit direction

- Programmable delay

- Transmit slips are independent of receive slips

- Indication of slip •

- Indication of slip direction

#### Receive Slip Buffer

- Two-frame slip buffer capable of performing a controlled slip

- Wander tolerance of 142 UI (92 µs) peak

- Indication of slip

- Indication of slip direction

### Interface to the Physical Layer Device

- Single rail NRZ

- Dual rail (AMI) RZ or NRZ

- Transmits/samples data on the rising or falling edge of the line clock

### T1/J1 Mode

- Optional B8ZS line coding

- Pulse density enforcement •

- Forced ones stuffing (bit 7 of a DS0)

- GTE zero suppression code

- Bell zero suppression code

- DDS zero suppression code

### Receive Slip Buffer

- controlled slip

- Two-frame slip buffer capable of performing a

E1 Mode

- Wander tolerance of 208 UI peak-to-peak

- Indication of slip

- Indication of slip direction

### E1 Mode

Optional HDB3 line coding

### Framing Algorithm

### T1/J1 Mode

- · Synchronizes with D4 or ESF protocols

- Supports T1DM synchronization with the D4 pattern and timeslot 24 T1DM Sychronization bytes

- Framing circuit is off-line

- Transparent transmit and receive mode

- In D4 mode Fs bits can be optionally cross checked with the Ft bits

- The start of the ESF multiframe can be determined by the following methods: Free-run

### Software reset

Synchronized to the incoming multiframe

- An automatic reframe is initiated if the framing bit error density exceeds the programmed threshold

- In transparent mode no reframing is forced by the device

- · Software can force a reframe at any time

- In ESF mode the CRC-6 bits can be optionally confirmed before forcing a new frame alignment

- During a reframe the signaling bits are frozen, and error counting for Ft, Fs, ESF framing pattern and CRC-6 bits is suspended

- If J1 CRC-6 is selected the Fs bits are included in the CRC-6 calculation

- J1-CRC-6 and J1-Yellow Alarm can be independently selected

- Supports Robbed Bit Signaling

- Optional forced ones insertion

### Channel Associated Signaling

- ABCD or AB bits can be automatically inserted and extracted

- Transmit ABCD or AB bits can be passed via the microport or via the CSTi pin

- Receive ABCD or AB bits are accessible via the microport or via the CSTo pin

- Unused nibble positions in the CSTi/CSTo bandwidth are tri-stated

- An interrupt is provided in the event of changes in any of the signaling bits

- · Receive signaling bits are frozen if digital loss of signal or loss of multiframe alignment is declared

### T1/J1 Mode

- Signaling bits can be debounced by 6 ms

- Robbed bit or clear channel signaling are selected on a channel by channel basis

- Signaling interrupts period can be selected: 1, 4 or 8 msec

### E1 Mode

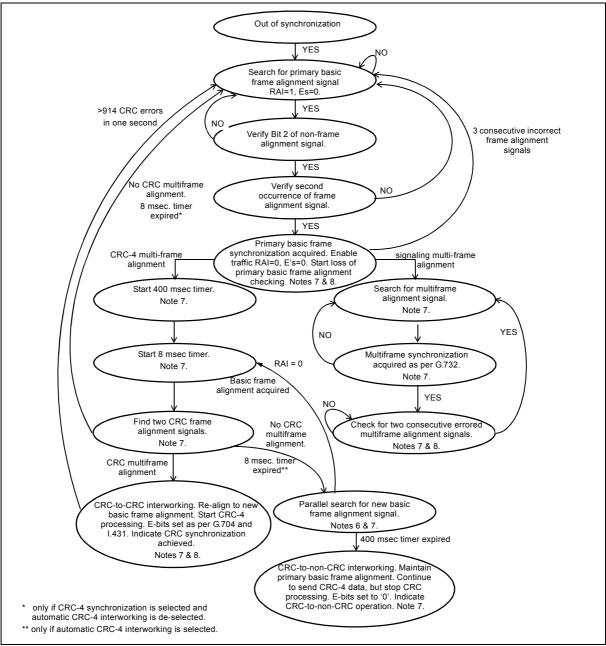

- Three distinct and independent E1 framing algorithms

- 1. Basic frame alignment

- 2. Signaling multiframe alignment

- 3. CRC-4 multiframe alignment

- Transparent receive mode

- Transparent transmit mode

- Optional automatic interworking between interfaces with and without CRC-4 processing capabilities is supported

- An automatic reframe is forced if 3 consecutive frame alignment patterns or three consecutive non-frame alignment bits are received in error

- In receive transparent mode no reframing is forced by the device

- Software can force a reframe at any time

- Software can force a multiframe reframe at any time

- E-bits can optionally be set to zero or one until CRC synchronization is achieved

- Optional automatic RAI

- Supports CAS multiframing

- Optional automatic Y-bit to indicate CAS multiframe alignment

### E1 Mode

- Signaling bits can be debounced by 14 ms

- Signaling interupt period can be selected 1, 4 or 8 msec

# MT9072

### Alarms

T1/J1 Mode

Yellow Alarm

D4 mode, two types:

- 1. Bit position 2 is zero for virtually every DS0 over 48ms

- 2. Two consecutive ones in the S-bit position of the twelfth frame

ESF mode, two types:

- 3. Reception of 000000011111111 in eight or more codewords out of ten (T1)

- 4. Reception of 11111111111111111 in eight or more codewords out of ten (J1)

T1DM mode :

Bit 2 of the T1DM synchronization byte is 0

Alarm Indication Signal (AIS)

• Declared if fewer than six zeros are detected during a 3 ms interval

Loss Of Signal (LOS)

Loss Of Signal is declared if 192 or 32 consecutive zeros are received

## E1 Mode

Remote Alarm Indication (RAI)

Bit 3 of the receive NFAS

Alarm Indication Signal (AIS)

• Unframed all ones signal for at least a double frame or two double frames

Timeslot 16 Alarm Indication Signal

• All ones signal in timeslot 16

Loss Of Signal (LOS)

Loss Of Signal is declared if 192 or 32 consecutive zeros are received

Remote Signaling Multiframe Alarm

• Y-bit of the multiframe alignment signal

### **Performance Monitoring**

#### Error Counters

- · All counters can be cleared or preset by writing to the appropriate locations

- Maskable occurrence interrupt

- Maskable overflow interrupt

- · Counters can be latched on one second intervals

#### T1/J1 Mode

- CRC-6 Multiframe Counter (8-bit)

- PRBS Error Counter (8-bit)

- Multiframes Out of Sync Counter (16-bit)

- Framing Bit Error Counter (16-bit)

- Bipolar Violation Counter (16-bit)

- CRC-6 Error Counter (16-bit)

- Out of Frame Alignment Counter (8-bit)

- Change of Frame Alignment Counter (8-bit)

- Excessive Zeros Counter (8-bit)

#### **Error Insertion**

#### T1/J1 Mode

- Bipolar Violations

- CRC-6 errors

- Ft errors

- Fs errors

- · Payload errors

- Loss of Signal error

#### Loopbacks

- Digital loopback

- Remote loopback

- ST-BUS loopback

- Payload loopback

- Local timeslot loopback

- Remote timeslot loopback

- Framer to framer loopback

### Per Timeslot Control

The following features can be controlled on a per timeslot basis:

- Clear Channel Capability (only used in T1/J1)

- · Choice of sourcing transmit signaling bits from microport or CSTi pin

- Remote timeslot loopback

- Local timeslot loopback

- PRBS insertion and reception

- · Digital milliwatt pattern insertion

- · Per channel inversion for transmit and receive

- · Transmit and receive idle code

#### E1 Mode

- CRC-4 Multiframe Counter (8-bit)

- PRBS Error Counter (8-bit)

- Loss of Basic Frame Sync (16-bit)

- E-bit Error Counter (16-bit)

- Bipolar Violation Counter (16-bit)

- CRC-4 Error Counter (16-bit)

- FAS Bit Error Counter (8-bit)

- FAS Error Counter (8-bit)

### E1 Mode

- E-bit

- Bipolar Violations

- CRC-4 Errors

- FAS Errors

- NFAS Errors

- · Payload Errors

- · Loss of Signal Error

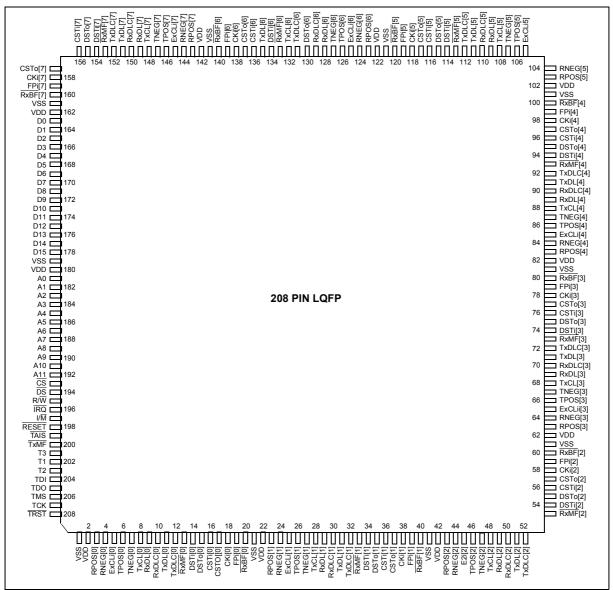

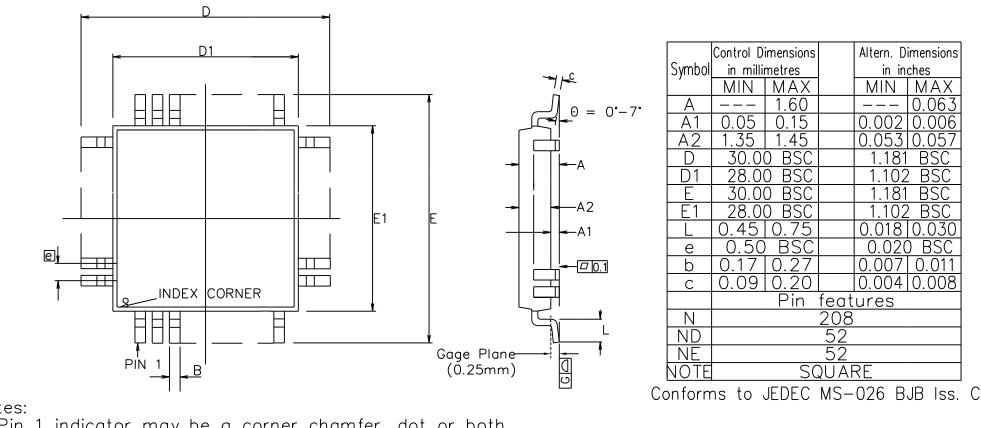

Figure 2 - Pin Connections (Jedec MS-026)

| MT9072 |

|--------|

|--------|

|   | 1        | 2        | 3        | 4        | 5       | 6        | 7         | 8           | 9         | 10       | 11        | 12      | 13       | 14       | 15        | 16       |

|---|----------|----------|----------|----------|---------|----------|-----------|-------------|-----------|----------|-----------|---------|----------|----------|-----------|----------|

| A | (NC)     | (205)    | (204)    | (201)    | (199)   | (193)    | (192)     | (187)       | (182)     | (178)    | (171)     | (168)   | (163)    | (164)    | (165)     | (166)    |

|   | 0        | TDO      | TDI      | T3       | TAIS    | CS       | A11       | A6          | A1        | D15      | D8        | D5      | D0       | D1       | D2        | D3       |

| В | 209      | 207      | 206      | 202      | 200     | (195)    | (190)     | (185)       | (181)     | (177)    | (172)     | (167)   | (157)    | (158)    | (159)     | (160)    |

|   | IDDq     | тск      | TMS      | T1       | TXMF    | RW       | A9        | A4          | A0        | D14      | D9        | D4      | CSTO[7]  | CKI[7]   | FPI[7]    | RXBF[7]  |

| С | NC       | NC       | 208      | 203      | (198)   | (196)    | (191)     | (186)       | (183)     | (175)    | (173)     | (169)   | (153)    | (154)    | (155)     | (156)    |

|   | ~        | ~        | TRST     | T2       | RESET   | IRQ      | A10       | A5          | A2        | D12      | D10       | D6      | RXMF[7]  | DSTI[7]  | DSTo[7]   | CSTI[7]  |

| D | 3        | 4        | 5        | 6        | (197)   | (194)    | (189)     | (188)       | (184)     | (176)    | (174)     | (170)   | (149)    | (150)    | (151)     | (152)    |

|   | RPOS[0]  | RNEG[0]  | EXCLi[0] | TPOS[0]  | IM      | DS       | A8        | A7          | A3        | D13      | D11       | D7      | RXDL[7]  | RXDLC[7  | ] TXDL[7] | TXDLC[7] |

| Е | (7)      | (8)      | 9        | (10)     | (NC)    | (NC)     | (101)     | (121)       | (141)     | (161)    | (179)     | (NC)    | (145)    | (146)    | (147)     | (148)    |

|   | TNEG[0]  | TXCL[0]  | RXDL[0]  | RXDLC[0] | ~       |          | VSS       | VSS         | VSS       | VSS      | VSS       | $\sim$  | EXCLi[7] | TPOS[7]  | TNEG[7]   | TXCL[7]  |

| F | (11)     | (12)     | (13)     | (14)     | (NC)    |          |           |             |           |          |           | (NC)    | (139)    | (140)    | (143)     | (144)    |

|   | TXDL[0]  | TXDLC[0] | RXMF[0]  | DSTI[0]  | _       |          |           |             |           |          |           | _       | FPI[6]   | RXBF[6]  | RPOS[7]   | RNEG[7]  |

| G | 15       | (16)     | (17)     | (18)     | 2       |          |           |             |           |          |           | (102)   | (130)    | (136)    | (137)     | (138)    |

|   | DSTo[0]  | CSTI[0]  | CSTO[0]  | CKI[0]   | VDD     |          |           |             |           |          |           | VDD     | DSTo[6]  | CSTI[6]  | CSTO[6]   | CKI[6]   |

| Н | (19)     | 20       | 23       | 24       | 22      |          |           | To          | Ŋ         |          |           | (122)   | (135)    | (131)    | (133)     | (134)    |

|   | FPi[0]   | RXBF[0]  | RPOS[1]  | RNEG[1]  | VDD     |          |           | <b>X</b> 7• | L-        |          |           | VDD     | TXDL6]   | TXDLC[6] | RXMF[6]   | DSTI[6]  |

| J | 25       | 26       | 27       | 28       | (42)    |          |           | Vi          | ew        |          |           | (142)   | (127)    | (132)    | (128)     | (129)    |

|   | EXCLi[1] | TPOS[1]  | TNEG[1]  | TXCL[1]  | VDD     |          |           |             |           |          |           | VDD     | TNEG[6]  | TXCL6]   | RXDL[6]   | RXDLC[6] |

| К | 29       | (30)     | (31)     | (32)     | 62      |          |           |             |           |          |           | (162)   | (123)    | (124)    | (125)     | (126)    |

|   | RXDL[1]  | RXDLC[1] | TXDL[1]  | TXDLC[1] | VDD     |          |           |             |           |          |           | VDD     | RPOS6]   | RNEGI6]  | EXCLi[6]  | TPOS[6]  |

| L | (33)     | (34)     | (35)     | (36)     | (82)    |          |           |             |           |          |           | (180)   | (117)    | (118)    | (119)     | (120)    |

|   | RXMF[1]  | DSTI[1]  | DSTo[1]  | CSTI[1]  | VDD     |          |           |             |           |          |           | VDD     | CSTO[5]  | CKI5]    | FPI[5]    | RXBF[5]  |

| М | (37)     | (38)     | (39)     | (40)     | NC      | NG       | (1)       | (21)        | (41)      | 61       | (81)      | NG      | (113)    | (114)    | (115)     | (116)    |

|   | CSTOI1]  | CKI[1]   | FPi[1]   | RXBF[1]  | 0       | 0        | VSS       | VSS         | VSS       | VSS      | VSS       | 0       | RXMF[5]  | DSTI[5]  | DSTo[5]   | CSTI[5]  |

| N | (43)     | (44)     | (45)     | (46)     | 59      | 60       | 63        | 64          | (77)      | (78)     | (79)      | 80      | (109)    | (110)    | (111)     | (112)    |

|   | RPOS[2]  | RNEG[2]  | EXCLi[2] | TPOS[2]  | FPI[2]  | RXBF[2]  | RPOS[3]   | RNEG[3]     | CSTO[3]   | CKI[3]   | FPI[3]    | RXBF[3] | RXDL[5]  | RXDLC[5  | ] TXDL[5] | TXDLC[5] |

| Р | (47)     | (48)     | (49)     | (50)     | 65      | 66       | 67        | 68          | (83)      | (84)     | (85)      | (86)    | (105)    | (106)    | (107)     | (108)    |

|   | TNEG[2]  | TXCL[2]  | RXDL[2]  | RXDLC[2] | EXCLi[3 | JTPOS[3] | TNEG[3]   | TXCL[3]     | RPOS[4]   | RNEG[4]  | EXCLi[4]  | TPOS[4] | EXCLi[5] | TPOS[5]  | TNEG[5]   | TXCL[5]  |

| R | (51)     | (52)     | (53)     | (54)     | (69)    | (70)     | (71)      | (72)        | (87)      | (88)     | (89)      | (90)    | (99)     | (100)    | (103)     | (104)    |

| - | TXDL[2]  | TXDLC[2] | RXMF[2]  | DSTI[2]  | RXDL[3  | RXDLC[3  | ] TXDL[3] | TXDLC[3]    | ] TNEG[4] | TXCL[4]  | RXDL[4] I | RXDLC[4 | ] FPi[4] | RXBF[4]  | RPOS[5]   | RNEG[5]  |

| т | (55)     | (56)     | (57)     | (58)     | (73)    | (74)     | (75)      | (76)        | (91)      | (92)     | (93)      | (94)    | (95)     | (96)     | (97)      | (98)     |

|   | DSTo[2]  | CSTI[2]  | CSTO[2]  | CKI[2]   | RXMF[3] | ]DSTI[3] | DSTo[3]   | CSTI[3]     | TXDL[4]   | TXDLC[4] | RXMF[ 4]  | DSTI[4] | DSTo[4]  | CSTI[4]  | CSTO[4]   | CKI[4]   |

|   |          |          |          |          |         |          |           |             |           |          |           |         |          |          |           |          |

|   |          |          |          |          |         |          |           |             |           |          |           |         |          |          |           |          |

|   |          |          |          |          |         |          |           |             |           |          |           |         |          |          |           |          |

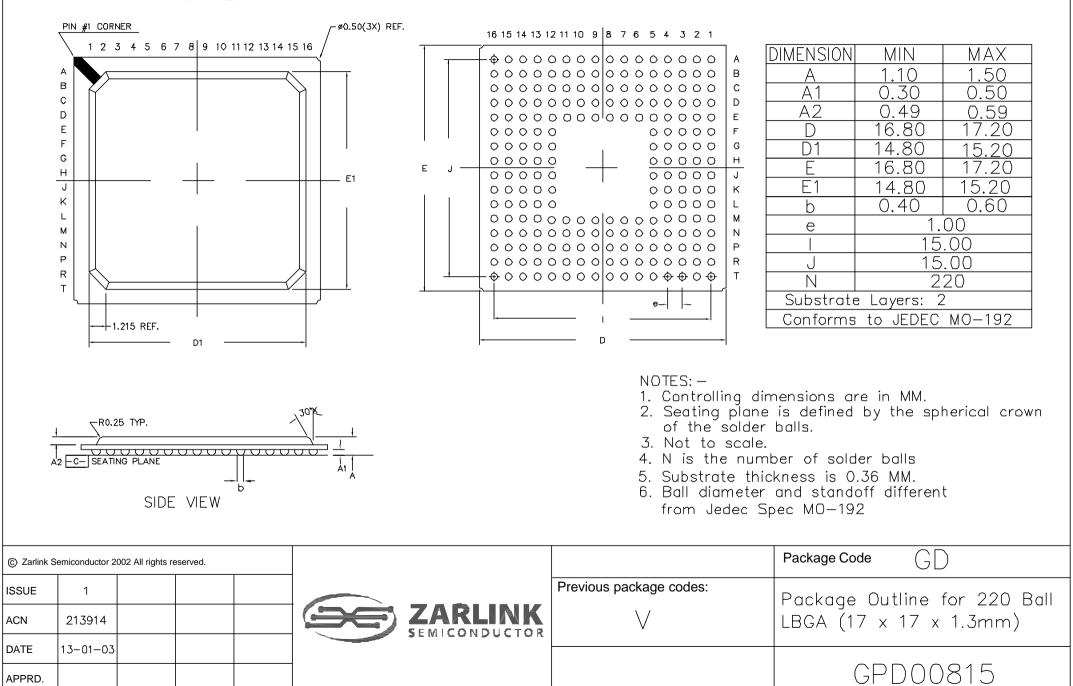

### Figure 3 - 220 PIN LBGA (Jedec MO-192)

Note: The pin numbers inside the balls for the LBGA package correspond to the pin numbers on the device in the Pin Description Table.

# **Pin Description**

| Pin #                                          |                                                  | Nome                                                                                         | Turce | Description (ass Notes 4 to 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP                                           | LBGA                                             | Name                                                                                         | Туре  | Description (see Notes 1 to 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1,21,41,61,<br>81,101,121,<br>141,161,<br>179  | E7,E8,E9,<br>E10,E11,<br>M7,M8,M9,<br>M10,M11    | V <sub>SS</sub>                                                                              | Р     | Ground. 0V <sub>DC</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2,22,42,62,<br>82,102,122,<br>142,162,18<br>0  | G5,H5,J5,<br>K5,L5,G12,<br>H12J12,K1<br>2,L12    | V <sub>DD</sub>                                                                              | Р     | Supply Voltage. +3.3V <sub>DC</sub> nominal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

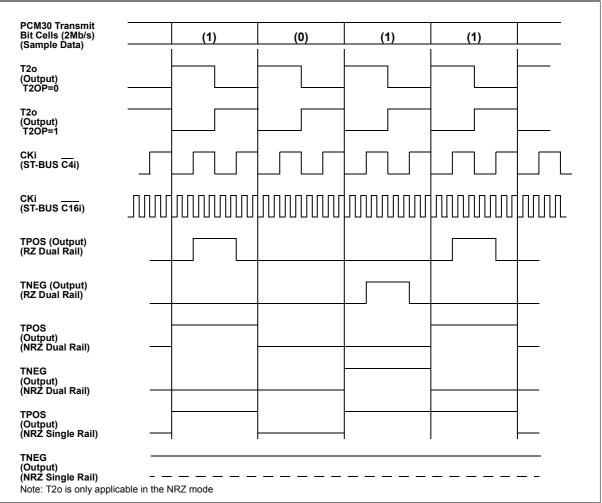

| 3<br>23<br>43<br>63<br>83<br>103<br>123<br>143 | D1<br>H3<br>N7<br>P9<br>R15<br>K13<br>F15        | RPOS[0]<br>RPOS[1]<br>RPOS[2]<br>RPOS[3]<br>RPOS[4]<br>RPOS[5]<br>RPOS[6]<br>RPOS[7]         | I     | <ul> <li>Receive Positive. This pin is an input for the receive side of the framer; it typically interfaces to an LIU. If used by itself it can accept single rail NRZ (Non Return to Zero) data. If RPOS is used in conjunction with RNEG it can accept dual rail NRZ data or dual rail RZ (Return to Zero) data. The clock at the EXCLi pin is used to clock data into the RPOS pin. Pins RPOS[0-7] are used for Framers[0-7] respectively.</li> <li>In T1 mode, transmit line codes are selected with control bits: RZCS1-0, RXB8ZS, RZNRZ and UNIBI (Address Y01). T1 mode is selected if the T1E0 bit (Address 900) is 1.</li> <li>In E1 mode, line codes are selected with control bits: COD0-1 and RHDB3 at (Address Y02). E1 mode is selected if the T1E0 bit</li> </ul> |

| 4<br>24<br>44<br>64<br>84<br>104<br>124<br>144 | D2<br>H4<br>N2<br>P10<br>R16<br>K14<br>F16       | RNEG[0]<br>RNEG[1]<br>RNEG[2]<br>RNEG[3]<br>RNEG[4]<br>RNEG[5]<br>RNEG[6]<br>RNEG[7]         | I     | <ul> <li>(Address 900) is 0.</li> <li><b>Receive Negative.</b> This pin is an input for the receive side of the framer; it typically interfaces to an LIU. RNEG is used in conjunction with RPOS to accept dual rail NRZ (Non Return to Zero) data or dual rail RZ (Return to Zero) data. The clock at the EXCLi pin is used to clock data into the RNEG pin. Pins RNEG[0-7] are used for Framers[0-7] respectively.</li> <li>In T1 mode, receive line codes are selected with control bits: RZCS1-0, RXB8ZS, RZNRZ and UNIBI at (Address Y01). T1 mode is selected if the T1E0 bit (Address 900) is 1.</li> <li>In E1 mode, line codes are selected with control bits: COD0-1 and RHDB3 at (Address Y02). E1 mode is selected if the T1E0 bit (Address 900) is 0.</li> </ul>    |

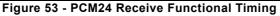

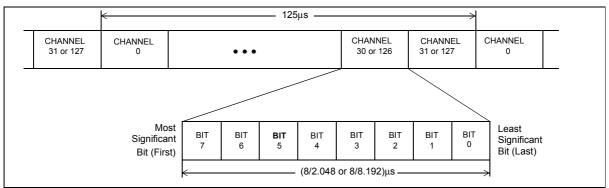

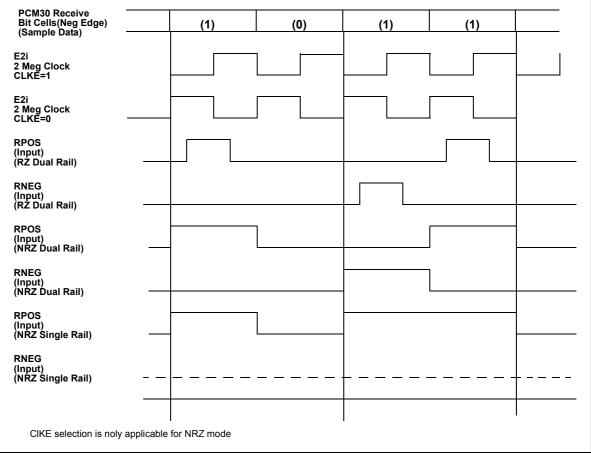

| 5<br>25<br>45<br>65<br>85<br>105<br>125<br>145 | D3<br>J1<br>N3<br>P5<br>P11<br>P13<br>K15<br>E13 | EXCLi(0)<br>EXCLi(1)<br>EXCLi(2)<br>EXCLi(3)<br>EXCLi(4)<br>EXCLi(5)<br>EXCLi(6)<br>EXCLi(7) | I     | <ul> <li>1.544/2.048 MHz Extracted Clock. The rising edge of the clock applied at this input is used to clock RZ data into the receive side of the framer on pins RPOS and RNEG. If RPOS/RNEG are configured for NRZ input then either a rising or falling edge on the EXCLi clock can be selected to clock RPOS/RNEG data. Pins EXCLi[0-7] are used for Framers[0-7] respectively.</li> <li>In T1 mode, this pin accepts a 1.544MHz extracted clock. An active rising or falling edge is selected with the CLKE bit (Address Y01). See Figure 53.</li> <li>In E1 mode, this pin accepts a 2.048MHz extracted clock. An active rising or falling edge is selected with the CLKE bit (Address Y02). See Figure 73.</li> </ul>                                                     |

| Pir                                            | Pin #                                            |                                                                                      | Trune |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP                                           | LBGA                                             | Name                                                                                 | Туре  | Description (see Notes 1 to 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

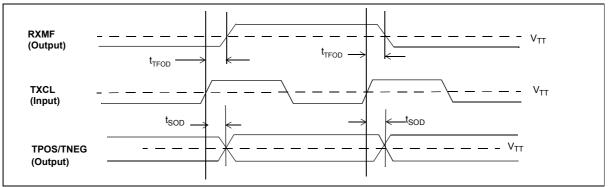

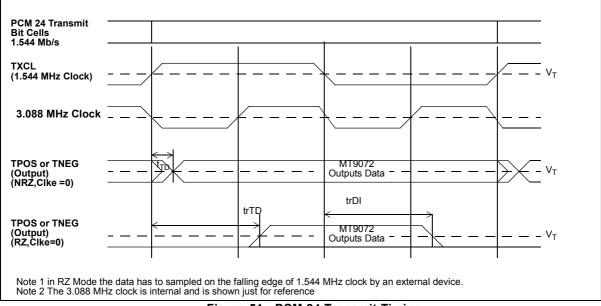

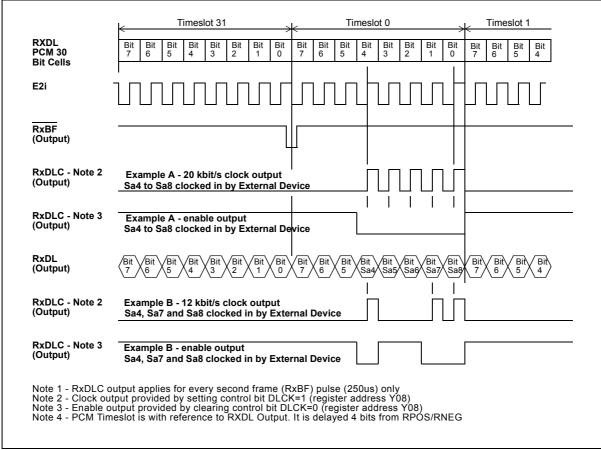

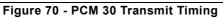

| 6<br>26<br>46<br>66<br>86<br>106<br>126<br>146 | D4<br>J2<br>N4<br>P6<br>P12<br>P14<br>K16<br>E14 | TPOS[0]<br>TPOS[1]<br>TPOS[2]<br>TPOS[3]<br>TPOS[4]<br>TPOS[5]<br>TPOS[6]<br>TPOS[7] | 0     | <ul> <li>Transmit Positive. This pin is an output for the transmit side of the framer; it typically interfaces to an LIU. If used by itself it can provide single rail NRZ (Non Return to Zero) data. If TPOS is used in conjunction with TNEG it can provide dual rail NRZ data or dual rail RZ (Return to Zero) data. The clock at the TXCL pin is used to clock data out of the TPOS pin. Pins TPOS[0-7] are used for Framers[0-7] respectively.</li> <li>In T1 mode, line codes are selected with control bits: TZCS2-0, TPDV, TXB8ZS, RZNRZ and UNIBI (Address Y01). T1 mode is selected if the T1E0 bit (Address 900) is 1.</li> <li>In E1 mode, line codes are selected with control bits: COD0-1 and THDB3 (Address Y02). E1 mode is selected if the T1E0 bit (Address 900) is 0.</li> </ul>                                                                                                                                                      |

| 7<br>27<br>47<br>67<br>87<br>107<br>127<br>147 | E1<br>J3<br>P1<br>R9<br>P15<br>J13<br>E15        | TNEG[0]<br>TNEG[1]<br>TNEG[2]<br>TNEG[3]<br>TNEG[4]<br>TNEG[5]<br>TNEG[6]<br>TNEG[7] | 0     | <ul> <li>Transmit Negative. This pin is an output for the transmit side of the framer; it typically interfaces to an LIU. TNEG is used in conjunction with TPOS to provide dual rail NRZ (Non Return to Zero) data or dual rail RZ (Return to Zero) data. The clock at the TXCL pin is used to clock data out of the TNEG pin. Pins TNEG[0-7] are used for Framers[0-7] respectively.</li> <li>In T1 mode, line codes are selected with control bits: TZCS2-0, TPDV, TXB8ZS, RZNRZ and UNIBI (Address Y01). T1 mode is selected if the T1E0 bit (Address 900) is 1.</li> <li>In E1 mode, line codes are selected with control bits: COD0-1 and THDB3 (Address Y02). E1 mode is selected if the T1E0 bit (Address 900) is 0.</li> </ul>                                                                                                                                                                                                                    |

| 8<br>28<br>48<br>68<br>88<br>108<br>132<br>148 | E2<br>J4<br>P2<br>R10<br>P16<br>J14<br>E16       | TXCL[0]<br>TXCL[1]<br>TXCL[2]<br>TXCL[3]<br>TXCL[4]<br>TXCL[5]<br>TXCL[6]<br>TXCL[7] | IO    | <ul> <li>1.544/2.048 MHz Transmit Clock. This pin accepts/outputs a clock that is used to clock data out of the transmit side of the framer on pins TPOS and TNEG. If TPOS/TNEG are configured for RZ output then the rising edge of the clock is used to clock TPOS/TNEG data. If TPOS/TNEG are configured for NRZ output then either a rising or falling TxCL edge can be selected to clock TPOS/TNEG data. Pins TxCL[0-7] are used for Framers[0-7] respectively.</li> <li>In T1 mode this pin is an input. The 1.544MHz transmit clock is typically provided by an external PLL (Phase Lock Loop) or LIU. An active rising or falling edge is selected with the CLKE bit (Address Y01). See Figure 52.</li> <li>In E1 mode this pin is an output. The 2.048MHz transmit clock is synchronous with the 4.096MHz ST-BUS clock input to pin CKi. An active rising or falling edge is selected with the T2OP bit (Address Y02). See Figure 71.</li> </ul> |

| Pin #                                           |                                                  | Nama                                                                                         | <b>T</b>                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP                                            | LBGA                                             | Name Type                                                                                    | Description (see Notes 1 to 7) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

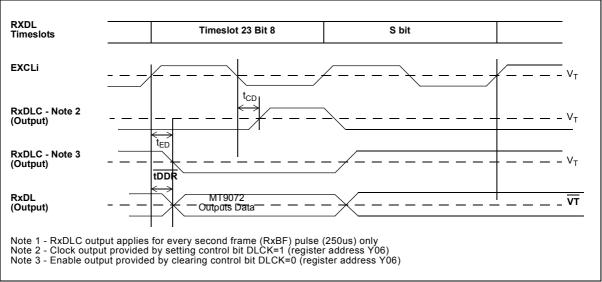

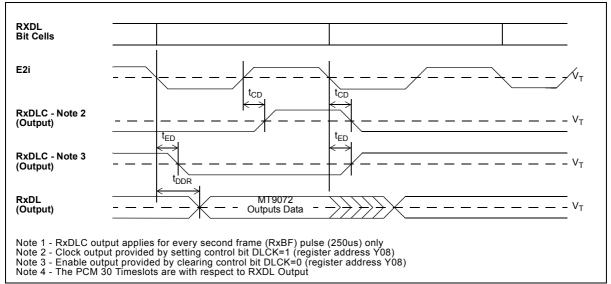

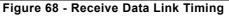

| 9<br>29<br>49<br>69<br>89<br>109<br>128<br>149  | E3<br>K1<br>P3<br>R5<br>R11<br>N13<br>J15<br>D13 | RxDL[0]<br>RxDL[1]<br>RxDL[2]<br>RxDL[3]<br>RxDL[4]<br>RxDL[5]<br>RxDL[6]<br>RxDL[7]         | 0                              | <b>Receive Data Link.</b> The entire received data stream including framing bits, after B8ZS/HDB3 decoding, is clocked out of the RxDL pin by the clock at the EXCLi pin. RxDL data does not pass through the receive slip buffer. The embedded data link is flagged by RxDLC. Pins RxDL[0-7] are used for Framers[0-7] respectively.<br>In T1 mode this is a 1.544Mbit/s data stream clocked out with the rising edge of the clock at the EXCLi pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                 |                                                  |                                                                                              |                                | In E1 mode this is a 2.048 Mbit/s data stream clocked out with the falling edge of the clock at the EXCLi pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

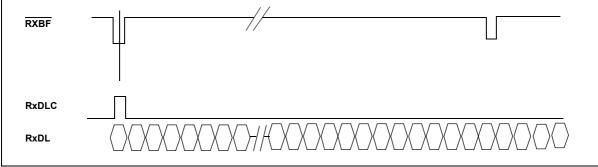

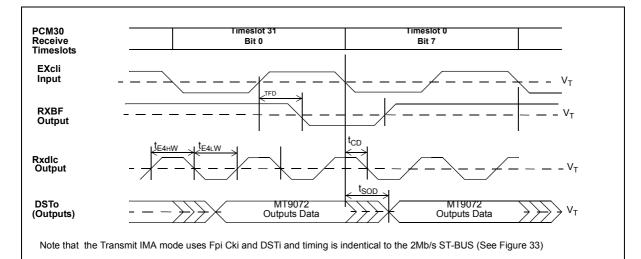

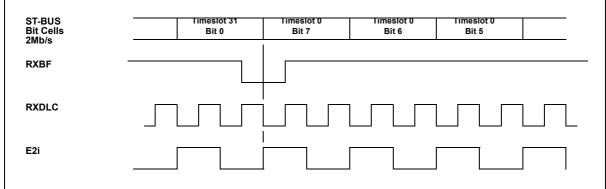

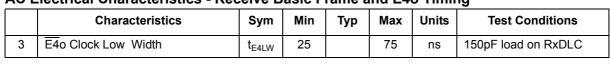

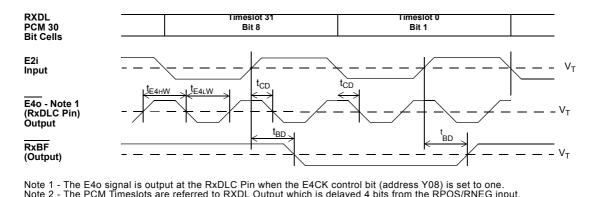

| 10<br>30<br>50<br>70<br>90<br>110<br>129<br>150 | E4<br>K2<br>P4<br>R6<br>R12<br>N14<br>J16<br>D14 | RxDLC[0]<br>RxDLC[1]<br>RxDLC[2]<br>RxDLC[3]<br>RxDLC[4]<br>RxDLC[5]<br>RxDLC[6]<br>RxDLC[7] | 0                              | <ul> <li>Receive Data Link Clock. This pin outputs a clock that can be used to clock selected bits from the RxDL data stream into an external device. The RxDLC pin can also be configured as an enable signal. Pins RxDLC[0-7] are used for Framers[0-7] respectively.</li> <li>In T1 mode the FDL (Facility Data Link) bits embedded in the RxDL data stream can be clocked into an external device with the rising edge of this 4kHz clock. The rising edge of the clock is centered on the S-bit position and it is coincident with the falling edge of the clock provided to the EXCLi pin. The RxDLC pin can be configured as a clock or an enable signal with the DLCK bit (Address Y06). See Figure 49.</li> <li>In T1 IMA (Inverse Mux for ATM) mode the RxDLC pin outputs the same 1.544MHz clock that is input to the EXCLi pin. In IMA mode the DSTo data stream will be synchronous with this 1.544MHz clock. IMA mode is selected by setting the IMA bit (Address Y00) to 1. See Figure 39.</li> <li>In E1 mode the selected data link national bits (timeslot 0, bits 4-8 of the NFAS (Non-Frame Alignment Signal) frames) can be clocked into an external device with the rising edge of this clock. The Receive Data Link clock is a gapped 4, 8, 12, 16 or 20 kHz, clock as programmed by the Datalink Control Register (Address Y08), derived by gating the 2.048MHz clock provided to the EXCLi pin. The RxDLC pin can be configured as a clock or an enable signal with the DLCK bit (Address Y08). See Figure 68.</li> <li>In E1 IMA (Inverse Mux for ATM) mode the RxDLC pin provides an ST-BUS type 4.096MHz clock derived by doubling the 2.048MHz clock provided to the EXCLi pin. In IMA mode is selected by setting the IMA bit (Address Y00) to 1. See Figure 58.</li> </ul> |

| Pir                                             | Pin #                                            |                                                                                              | Turna | Description (see Notes 1 to 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP                                            | LBGA                                             | Name Type                                                                                    | Туре  | Description (see Notes 1 to 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

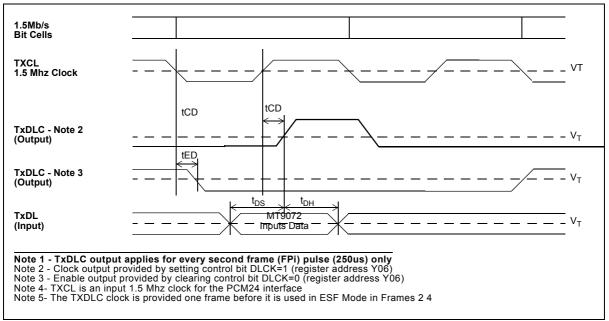

| 11<br>31<br>51<br>71<br>91<br>111<br>135<br>151 | F1<br>K3<br>R1<br>R7<br>T9<br>N15<br>H13<br>D15  | TxDL[0]<br>TxDL[1]<br>TxDL[2]<br>TxDL[3]<br>TxDL[4]<br>TxDL[5]<br>TxDL[6]<br>TxDL[7]         | I     | Transmit Data Link. This pin accepts data from an external device for the Transmit Data Link. Pins TxDL[0-7] are used for Framers[0-7] respectively.<br>In T1 mode this pin accepts a 4kbit/s serial input stream that contains the ESF FDL (Facility Data Link) bits that are to be embedded in the transmit data stream. The data is clocked in by the rising edge of the clock provided at the TxDLC pin. TxDL data does not pass through the transmit slip buffer.<br>In E1 mode this pin accepts a 4,8,12,16 or 20 kbit/s, as programmed by the Datalink Control Register (Address Y08), data stream which contains the data link national bits (timeslot 0, bits 4-8 of the NFAS (Non-Frame Alignment Signal) frames) for transmission. The selected data link national bits are clocked into the framer by the falling edge of the clock provided at the TxDLC pin.                                                                        |

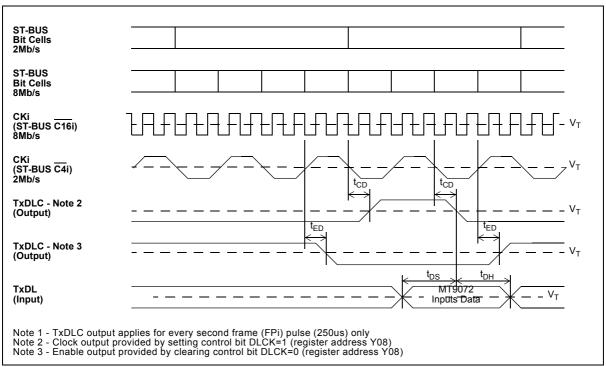

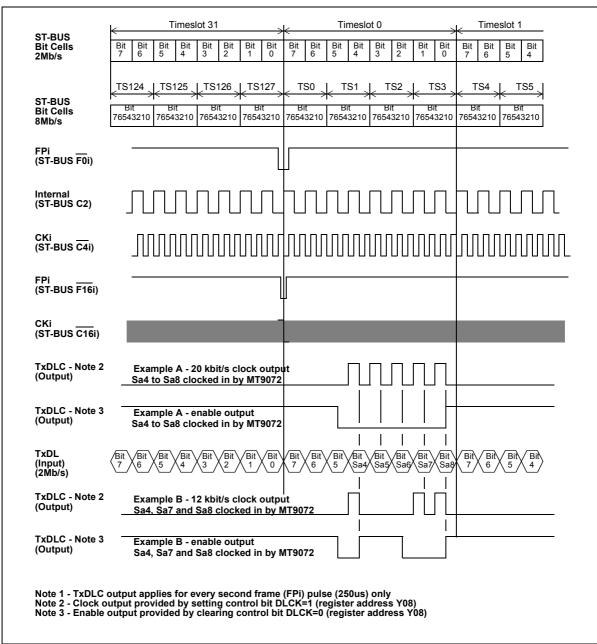

| 12<br>32<br>52<br>72<br>92<br>112<br>131<br>152 | F2<br>K4<br>R2<br>R8<br>T10<br>N16<br>H14<br>D16 | TxDLC[0]<br>TxDLC[1]<br>TxDLC[2]<br>TxDLC[3]<br>TxDLC[4]<br>TxDLC[5]<br>TxDLC[6]<br>TxDLC[7] |       | <ul> <li>Transmit Data Link Clock. This pin provides a clock that is used to clock transmit data link data out of an external device into the TxDL pin. The TxDLC pin can also be configured as an enable signal. Pins TxDLC[0-7] are used for Framers[0-7] respectively.</li> <li>In T1 mode, this pin provides either a 4kHz clock derived by gating the 1.544MHz clock provided to the TxCL pin, or it provides an enable signal. The TxDLC pin can be configured as a clock or an enable signal with the DLCK bit (Address Y06). Transmit data link data does not pass through the transmit slip buffer. See Figure 47.</li> <li>In E1 mode, this pin provides either a gapped 4,8,12,16 or 20 kHz clock, as programmed by the Datalink Control Register (Address Y08), derived by gating the 2.048MHz clock provided to the TxCL pin, or it provides an enable signal. The TxDLC pin can be configured as a clock or an enable 6.</li> </ul> |

| Pir                                             | Pin #                                            |                                                                                      | Trune                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP                                            | LBGA                                             | Name Type                                                                            | Description (see Notes 1 to 7) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

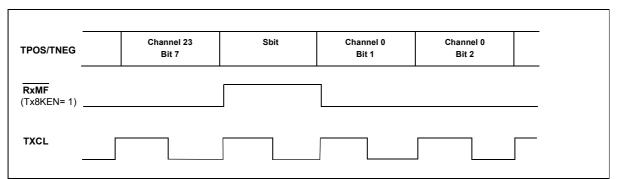

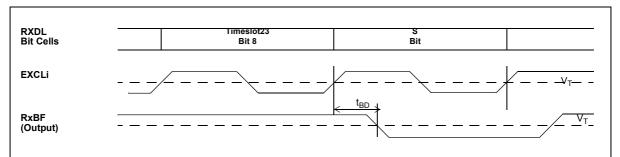

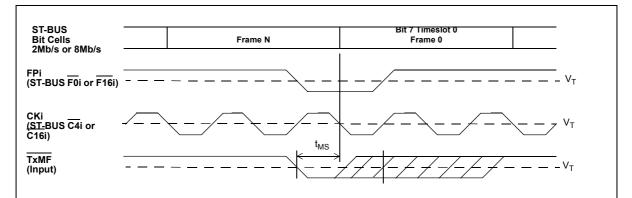

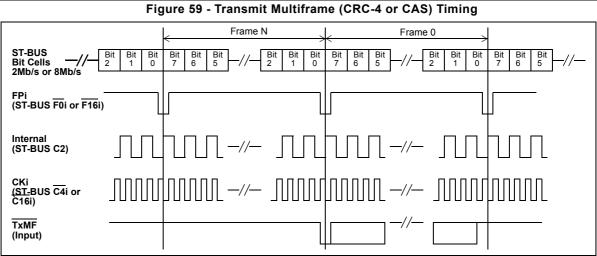

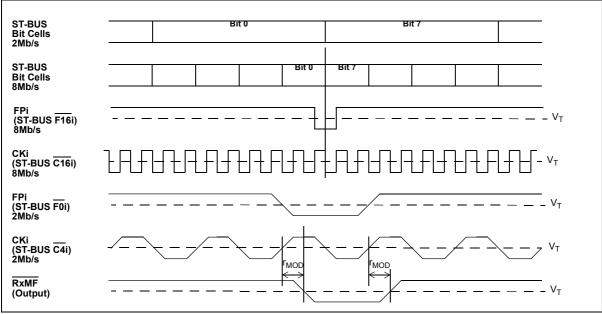

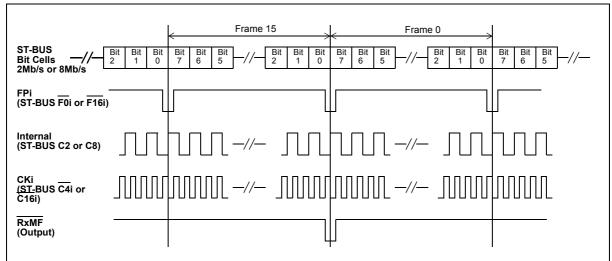

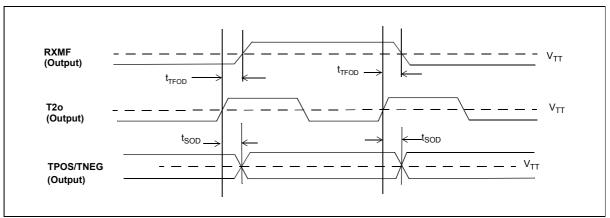

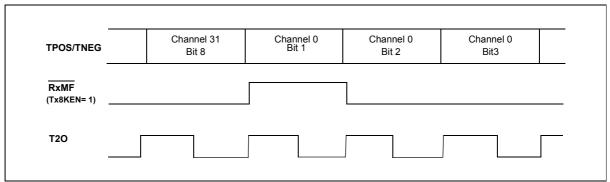

| 13<br>33<br>53<br>73<br>93<br>113<br>133<br>153 | F3<br>L1<br>R3<br>T5<br>T11<br>M13<br>H15<br>C13 | RxMF[0]<br>RxMF[1]<br>RxMF[2]<br>RxMF[3]<br>RxMF[4]<br>RxMF[5]<br>RxMF[6]<br>RxMF[7] | 0                              | <b>Receive Multiframe Boundary.</b> This pin provides a pulse that<br>identifies basic frame 0 (the start of bit cell 7 of channel 0) of each<br>received multiframe on the ST-BUS data stream (DSTo). The RxMF<br>pin operates the same way in 2.048Mbit/s and 8.196Mbit/s modes.<br>Pins RxMF[0-7] are used for Framers[0-7] respectively.<br>In T1 mode, the RxMF pulse is 244ns wide and its center identifies<br>basic frame 0 of the received multiframe. If the Tx8KEN control bit<br>(Address YF1) is 1 then the RxMF pin outputs an 8kHz frame pulse<br>synchronous with the data stream on TPOS/TNEG. See Figure 43 and<br>Figure 45<br>In T1 IMA mode, the frame pulse duration is 648ns.<br>In E1 mode, (and E1 IMA mode) the RxMF pulse is 244ns wide and its<br>center identifies basic frame 0 of the received CAS (Channel<br>Associated Signaling) multiframe boundary or the received CRC-4<br>multiframe boundary as determined by the MFSEL control bit<br>(Address Y02). If the Tx8KEN control bit (Address Y02) is 1 then the<br>RxMF pin outputs and 8kHz frame pulse synchronous with the data<br>stream on TPOS/TNEG. See Figure 64. |

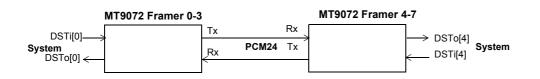

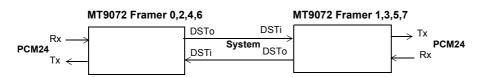

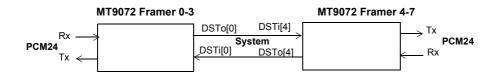

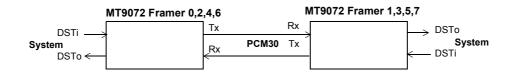

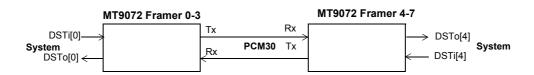

| 14<br>94                                        | F4<br>T12                                        | DSTi[0]<br>DSTi[4]                                                                   | I                              | Data ST-BUS. This pin is an input for the transmit side of the framer.<br>In 2.048Mbit/s ST-BUS mode and IMA mode it operates the same as<br>DSTi(1-3), it can also operate in 8.192Mbit/s ST-BUS mode. IMA<br>mode is not available at 8.192Mbit/s. The DSTi data stream is clocked<br>into the framer by the clock input to pin CKi.<br>When operated in 8.192Mbit/s ST-BUS mode this pin accepts a data<br>stream containing 128 8-bit channels accommodating four framers.<br>See Table 2 and Table 5. The frame boundary is indicated by the FPi<br>inputs. Pin DSTi[0] is used by Framers[0-3] and pin DSTi[4] is used by<br>Framers[4-7].<br>In 8.192Mbit/s mode, the 32 ST-BUS channels mapped to each framer<br>are treated as described for DSTi(1-3) operating at 2.048Mbit/s.                                                                                                                                                                                                                                                                                                                                                                     |

| Pir                                 | Pin #                               |                                                                | Turne                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------|-------------------------------------|----------------------------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP                                | LBGA                                | Name Type                                                      | Description (see Notes 1 to 7) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 34<br>54<br>74<br>114<br>134<br>154 | L2<br>R4<br>T6<br>M14<br>H16<br>C14 | DSTi[1]<br>DSTi[2]<br>DSTi[3]<br>DSTi[5]<br>DSTi[6]<br>DSTi[7] | I                              | <ul> <li>Data ST-BUS. In 2.048Mbit/s ST-BUS mode and IMA mode this pin is an input for the transmit side of the framer. This pin is not used in 8.192Mbit/s ST-BUS mode. The DSTi data stream is clocked into the framer by the clock input to pin CKi. Pins DSTi[0-7] are used by Framers[0-7] respectively.</li> <li>In T1 mode, this pin accepts a 2.048Mbit/s ST-BUS stream. The first 24 ST-BUS channels contain the data to be transmitted on the PCM24 interface. See Table 1.</li> <li>In T1 IMA mode, this pin accepts a 1.544Mbit/s serial stream that contains a framing bit followed by the 24 8-bit channels to be transmitted on the PCM24 interface, see Table 3. The framing bit is ignored and an internally generated framing bit is used. IMA mode is selected by setting the IMA bit (Address Y00) to 1.</li> <li>In E1 IMA mode, this pin accepts a 2.048Mbit/s ST-BUS stream that contains the data to be transmitted on the PCM30 interface. See Table 4 and Table 6.</li> </ul> |

| 15<br>95                            | G1<br>T13                           | DSTo[0]<br>DSTo[4]                                             | 0                              | <ul> <li>Data ST-BUS. This pin is an output for the receive side of the framer.<br/>In 2.048Mbit/s ST-BUS mode and IMA mode it operates the same as<br/>DSTo(1-3), it can also operate in 8.192Mbit/s ST-BUS mode. IMA<br/>mode is not available at 8.192Mbit/s. The DSTo data stream is<br/>clocked out of the framer by the clock input to pin CKi.</li> <li>When operated in 8.192Mbit/s ST-BUS mode this pin outputs a data<br/>stream containing 128 8-bit channels accommodating four framers.<br/>See Table 2 and Table 5. The frame boundary is indicated by the FPi<br/>inputs. Pin DSTo[0] is used by Framers[0-3] and pin DSTo[4] is used<br/>by Framers[4-7].</li> <li>The 32 ST-BUS channels mapped to each framer are treated as<br/>described for DSTi(1-3) operating at 2.048Mbit/s.</li> </ul>                                                                                                                                                                                         |

| Pir                                 | Pin #                               |                                                                | т    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------|-------------------------------------|----------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP                                | LBGA                                | Name                                                           | Туре | Description (see Notes 1 to 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 35<br>55<br>75<br>115<br>130<br>155 | L3<br>T1<br>T7<br>M15<br>G13<br>C15 | DSTo[1]<br>DSTo[2]<br>DSTo[3]<br>DSTo[5]<br>DSTo[6]<br>DSTo[7] | 0    | <ul> <li>Data ST-BUS. In 2.048Mbit/s ST-BUS mode and IMA mode this pin is an output for the receive side of the framer. This pin is not used in 8.192Mbit/s ST-BUS mode. Pins DSTo[0-7] are used by Framers[0-7] respectively.</li> <li>In T1 mode, this pin outputs 2.048Mbit/s ST-BUS data. The first 24 channels contain the 24 8-bit channels received on the PCM24 interface. Channel 31 bit 0 contains the received S-bit in D4 and ESF modes. See Table 1.The DSTo data stream is clocked out of the framer by the clock input to pin CKi. The DSTo pin is enabled if the DSToEN control bit (Address YF1) is set to 1.</li> <li>In T1 IMA mode, this pin outputs the 1.544Mbit/s received serial stream. The serial stream contains the framing bit followed by the 24 8-bit channels received on the PCM24 interface. See Table 3. In IMA mode the DSTo data stream is clocked out of the framer by the clock output by the RxDLC pin. The DSto pin is enabled if the DSToEN control bit (Address YF1) is set to 1.</li> <li>In E1 mode, this pin outputs 2.048Mbit/s ST-BUS data. The 32 channels contain the 32 channels of data stream is clocked out the PCM30 interface. See Table 4 and Table 6. The DSTo data stream is clocked out of the framer by the clock out of the framer by the clock input to pin CKi. The DSTo pin is enabled if the DSToEN control bit (Address Y00) to 1.</li> </ul> |

|                                     |                                     |                                                                |      | In E1 IMA mode, this pin outputs the 2.048Mbit/s received serial stream. See Table 4 and Table 6. In IMA mode the DSTo data stream is clocked out of the framer by the clock output by the RxDLC pin. The DSTo pin is enabled if the DSToE control bit (Address Y02) is set to 1. IMA mode is selected by setting the IMA bit (Address Y00) to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 16<br>96                            | G2<br>T14                           | CSTi[0]<br>CSTi[4]                                             | I    | <b>Control ST-BUS.</b> This pin is the signaling input for the transmit side of the framer. In 2.048 Mbit/s ST-BUS mode it operates the same as CSTi(1-3), it can also operate in 8.192Mbit/s ST-BUS mode. The CSTi data stream is clocked into the framer by the clock input to pin CKi. This pin has no function in IMA mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                     |                                     |                                                                |      | When operated in 8.192Mbit/s ST-BUS mode this pin accepts a data stream containing 128 8-bit channels accommodating four framers. See Table 2 and Table 5. The frame boundary is indicated by the FPi inputs. Pin CSTi[0] is used by Framers[0-3] and pin CSTi[4] is used by Framers[4-7].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                     |                                     |                                                                |      | The 32 ST-BUS channels mapped to each framer are treated as described for CSTi(1-3) operating at 2.048Mbit/s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Pin #                               |                                     | Nome                                                | Trues |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |