# EPSON

# SED1565 Series

# **Dot Matrix LCD Driver**

## DESCRIPTION

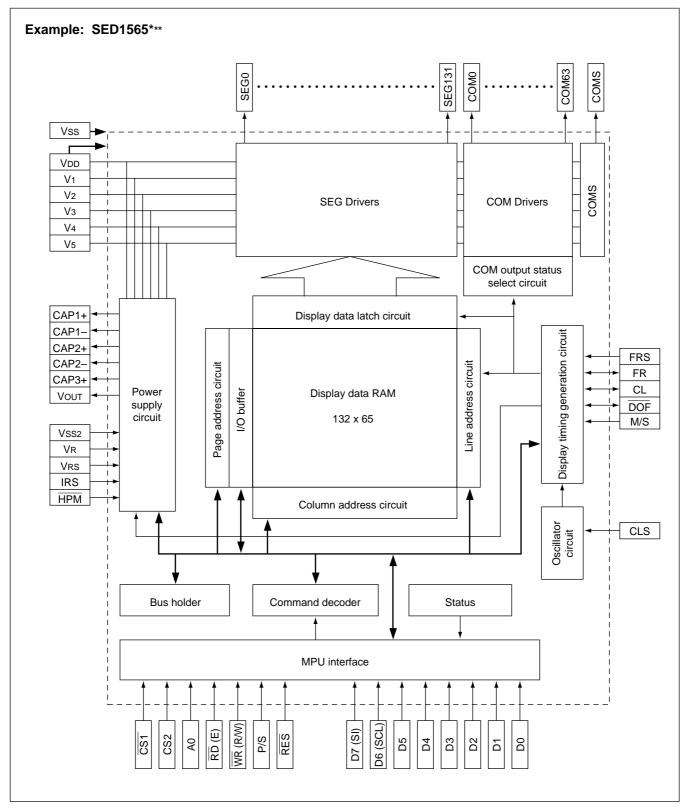

The SED1565 Series is a series of single-chip dot matrix liquid crystal display drivers that can be connected directly to a microprocessor bus. 8-bit parallel or serial display data sent from the microprocessor is stored in the internal display data RAM and the chip generates a liquid crystal drive signal independent of the microprocessor. Because the chips in the SED1565 Series contain  $65 \times 132$  bits of display data RAM and there is a 1-to-1 correspondence between the liquid crystal panel pixels and the internal RAM bits, these chips enable displays with a high degree of freedom.

The SED1565 Series chips contain 65 common output circuits and 132 segment output circuits, so that a single chip can drive a  $65 \times 132$  dot display (capable of displaying 8 columns  $\times$  4 rows of a  $16 \times 16$  dot kanji font). The SED1567 Series chips contain 33 common output circuits and 132 segment output circuits, so that a single chip can drive  $33 \times 132$  dot display (capable of displaying 8 columns  $\times 2$  rows of  $16 \times 16$  dot kanji fonts). Moreover, the capacity of the display can be extended through the use of master/slave structures between chips.

The chips are able to minimize power consumption because no external operating clock is necessary for the display data RAM read/write operation. Furthermore, because each chip is equipped internally with a low-power liquid crystal driver power supply, resistors for liquid crystal driver power voltage adjustment and a display clock CR oscillator circuit, the SED1565 Series chips can be used to create the lowest power display system with the fewest components for high-performance portable devices.

## ■ FEATURES

- Direct display of RAM data through the display data RAM.

- RAM bit data: "1" Non-illuminated "0" Illuminated

(during normal display)

- RAM capacity

RAM capacity

- 65 × 132 = 8580 bits ● Display driver circuits

- SED1565\*\*\*: 65 common output and 132 segment outputs

- SED1566\*\*\*: 49 common output and 132 segment outputs

- SED1567\*\*\*: 33 common outputs and 132 segment outputs

- SED1568\*\*\*: 55 common outputs and 132 segment outputs

- SED1569\*\*\*: 53 common outputs and 132 segment outputs

- High-speed 8-bit MPU interface (The chip can be connected directly to the both the 80×86 series MPUs and the 68000 series MPUs) /Serial interfaces are supported.

- Abundant command functions

- Abundant command functions

Display data Read/Write, display ON/OFF, Normal/ Reverse display mode, page address set, display start line set, column address set, status read, display all points ON/OFF, LCD bias set, electronic volume, read/modify/write, segment driver direction select, power saver, static indicator, common output status select, V5 voltage regulation internal resistor ratio set.

- Static drive circuit equipped internally for indicators.

(1 system, with variable flashing speed.)

- Low-power liquid crystal display power supply circuit equipped internally.

Booster circuit (with Boost ratios of Double/Triple/Quad, where the step-up voltage reference power supply can be input externally)

High-accuracy voltage adjustment circuit (Thermal gradient –0.05%/°C or –0.2%/°C or external input)

V5 voltage regulator resistors equipped internally,

V1 to V4 voltage divider resistors equipped internally, electronic volume function equipped internally, voltage follower.

- CR oscillator circuit equipped internally (external clock can also be input)

| Operating powe                | power consumption<br>er when the built-in power supply is              |

|-------------------------------|------------------------------------------------------------------------|

| used (an exam                 |                                                                        |

| SED1565D0B                    | $81 \mu\text{A} (\text{VDD} - \text{VSS} = \text{VDD} - \text{VSS2} =$ |

| /SED1565DBB                   | $3.0 \text{ V}$ , Quad voltage, $V_5 - V_{DD} = -11.0 \text{ V}$ )     |

| SED1566D0B                    | $43 \mu\text{A} (\text{VDD} - \text{VSS} = \text{VDD} - \text{VSS2} =$ |

| /SED1566Dвв                   | 3.0 V, Triple voltage, $V_5 - V_{DD} = -8.0 V$ )                       |

| SED1567Dob                    | $29 \mu\text{A}$ (VDD – VSS = VDD – VSS2 =                             |

| /SED1567Dвв                   | 3.0 V, Triple voltage, $V_5 - V_{DD} = -8.0 V$ )                       |

| SED1568D0B                    | $46 \mu\text{A}$ (VDD – VSS = VDD – VSS2 =                             |

| /SED1568Dbb                   | $3.0 \text{ V}$ , Triple voltage, $V_5 - V_{DD} =$                     |

| /SED1569D0B                   | -8.0 V)                                                                |

| /SED1569DBB                   | ,                                                                      |

| Conditions: Wh normal mode is | en all displays are in white and the selected.                         |

Power supply

Operable on the low 1.8 voltage Logic power supply VDD – VSS = 1.8 V to –5.5 V

Boost reference voltage: VDD - VSS2 = 1.8 V to -6.0 V

Liquid crystal drive power supply: VDD – V5 = –4.5 V to –16.0 V

- Wide range of operating temperatures: -40 to 85°C

- CMOS process

- Shipping forms include bare chip and TCP.

- These chips not designed for resistance to light or resistance to radiation.

| Product Name | Duty | Bias     | SED Dr | COM Dr | VREG Temperature<br>Gradient | Shipping Forms |

|--------------|------|----------|--------|--------|------------------------------|----------------|

| SED1565Dob   | 1/65 | 1/9, 1/7 | 132    | 65     | -0.05%/°C                    | Bare Chip      |

| /SED1565Dвв  | 1/05 | 1/3, 1/1 | 152    | 00     | -0.0378/ 0                   | Dare Onip      |

| SED1565T0*   | 1/65 | 1/9, 1/7 | 132    | 65     | −0.05%/°C                    | TCP            |

| * SED1565D1в | 1/65 | 1/9, 1/7 | 132    | 65     | −0.2%/°C                     | Bare Chip      |

| * SED1565T1* | 1/65 | 1/9, 1/7 | 132    | 65     | −0.2%/°C                     | TCP            |

| SED1565D2B   | 1/65 | 1/9, 1/7 | 132    | 65     | External Input               | Bare Chip      |

| SED1565T2*   | 1/65 | 1/9, 1/7 | 132    | 65     | External Input               | TCP            |

| SED1566D0B   | 1/49 | 1/0 1/0  | 132    | 49     | 0.050/ /00                   | Bara Chin      |

| /SED1566Dвв  | 1/49 | 1/8, 1/6 | 132    | 49     | −0.05%/°C                    | Bare Chip      |

| SED1566T0*   | 1/49 | 1/8, 1/6 | 132    | 49     | −0.05%/°C                    | TCP            |

| SED1566D1B   | 1/49 | 1/8, 1/6 | 132    | 49     | −0.2%/°C                     | Bare Chip      |

| * SED1566T1* | 1/49 | 1/8, 1/6 | 132    | 49     | −0.2%/°C                     | TCP            |

| SED1566D2B   | 1/49 | 1/8, 1/6 | 132    | 49     | External Input               | Bare Chip      |

| * SED1566T2* | 1/49 | 1/8, 1/6 | 132    | 49     | External Input               | TCP            |

| SED1567Dob   | 1/33 | 1/6, 1/5 | 132    | 33     | -0.05%/°C                    | Bare Chip      |

| /SED1567Dвв  | 1/33 | 1/0, 1/5 | 152    | 33     | -0.03%/ C                    | Dare Onip      |

| SED1567T0*   | 1/33 | 1/6, 1/5 | 132    | 33     | −0.05%/°C                    | TCP            |

| SED1567D1B   | 1/33 | 1/6, 1/5 | 132    | 33     | −0.2%/°C                     | Bare Chip      |

| * SED1567T1* | 1/33 | 1/6, 1/5 | 132    | 33     | −0.2%/°C                     | TCP            |

| SED1567D2B   | 1/33 | 1/6, 1/5 | 132    | 33     | External Input               | Bare Chip      |

| * SED1567T2* | 1/33 | 1/6, 1/5 | 132    | 33     | External Input               | TCP            |

| SED1568Dob   | 1/55 | 1/0 1/0  | 100    | FF     |                              | Bara Chin      |

| /SED1568Dвв  | 1/55 | 1/8, 1/6 | 132    | 55     | -0.05%/°C                    | Bare Chip      |

| SED1569Dob   | 1/52 | 1/9 1/6  | 122    | 52     | 0.05%//00                    | Poro Chin      |

| /SED1569Dвв  | 1/53 | 1/8, 1/6 | 132    | 53     | −0.05%/°C                    | Bare Chip      |

| SED1569T0*   | 1/53 | 1/8, 1/6 | 132    | 53     | −0.05%/°C                    | TCP            |

■ SERIES SPECIFICATIONS

Note: The circuit for the VREG temperature gradient -0.2%/°C and the external input is under preparation.

\* : Under development

## SED1565 Series

## BLOCK DIAGRAM

## SED1565 Series

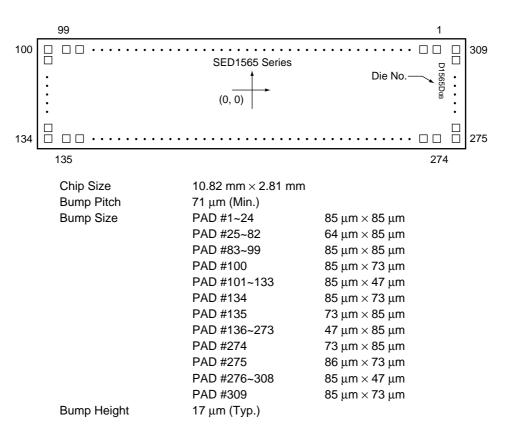

## ■ PAD LAYOUT

## ■ PIN DESCRIPTIONS

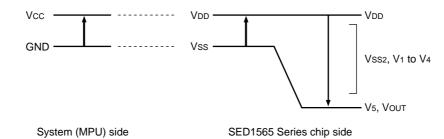

## • Power Supply Pins

| Pin Name              | I/O             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | # of<br>Pins |

|-----------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Vdd                   | Power<br>Supply | Shared with the MPU power supply terminal Vcc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13           |

| Vss                   | Power<br>Supply | This is a 0 V terminal connected to the system GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9            |

| VSS2                  | Power<br>Supply | This is the reference power supply for the step-up voltage circuit for the liquid crystal drive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4            |

| Vrs                   | Power<br>Supply | This is the externally-input VREG power supply for the LCD power supply voltage regulator.<br>These are only enabled for the models with the VREG external input option.                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2            |

| V1, V2, V3,<br>V4, V5 | Power<br>Supply | This is a multi-level power supply for the liquid crystal drive. The voltage applied is determined by the liquid crystal cell, and is changed through the use of a resistive voltage divided or through changing the impedance using an op. amp. Voltage levels are determined based on VDD, and must maintain the relative magnitudes shown below.<br>$V_{DD} (= V_0) \ge V_1 \ge V_2 \ge V_3 \ge V_4 \ge V_5$<br>Master operation: When the power supply turns ON, the internal power supply circuits produce the V1 to V4 voltages shown below. The voltage settings are selected using the LCD bias set command. | 10           |

|                       |                 | SED1565*** SED1566*** SED1567*** SED1569***                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

|                       |                 | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

## • LCD Power Supply Circuit Pins

| Pin Name | I/O | Function                                                                                                                                                                                                                                                                                                            | # of<br>Pins |

|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| CAP1+    | 0   | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1-terminal.                                                                                                                                                                                                                           | 2            |

| CAP1-    | 0   | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.                                                                                                                                                                                                                          | 2            |

| CAP2+    | 0   | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP2-terminal.                                                                                                                                                                                                                           | 2            |

| CAP2-    | 0   | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP2+ terminal.                                                                                                                                                                                                                          | 2            |

| CAP3-    | 0   | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.                                                                                                                                                                                                                          | 2            |

| Vout     | 0   | DC/DC voltage converter. Connect a capacitor between this terminal and Vss.                                                                                                                                                                                                                                         | 2            |

| VR       | I   | Output voltage regulator terminal. Provides the voltage between VDD and V5 through a resistive voltage divider.<br>These are only enabled when the V5 voltage regulator internal resistors are not used (IRS = "L").<br>These cannot be used when the V5 voltage regulator internal resistors are used (IRS = "H"). | 2            |

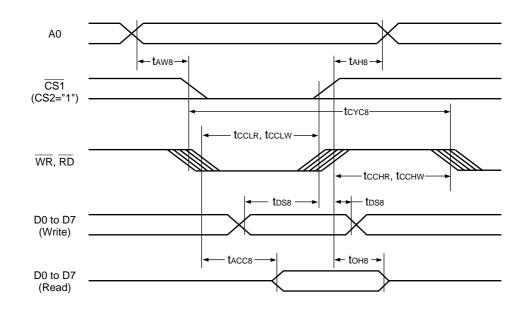

## • System Bus Connection Terminals

| Pin Name                  | I/O |                                                                                                                                                                                                                                       | Fun                                                                                                                                                                                                                                                                                                                                                                                                | ction                                                  |                     |             | # of<br>Pins |  |  |

|---------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------|-------------|--------------|--|--|

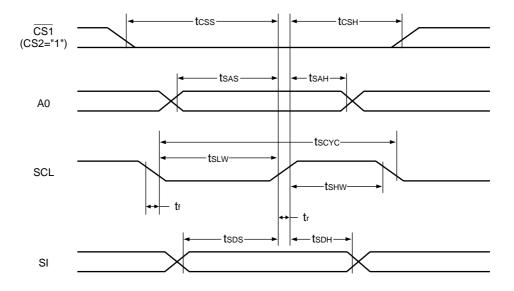

| D7 to D0<br>(SI)<br>(SCL) | I/O | data bus.<br>When the serial interface is set<br>terminal (SI) and D6 serves as<br>D5 are set to high impedance.                                                                                                                      | This is an 8-bit bi-directional data bus that connects to an 8-bit or 16-bit standard MPU data bus.<br>When the serial interface is selected (P/S = "L"), then D7 serves as the serial data input terminal (SI) and D6 serves as the serial clock input terminal (SCL). At this time, D0 to D5 are set to high impedance.<br>When the chip select is inactive, D0 to D7 are set to high impedance. |                                                        |                     |             |              |  |  |

| A0                        | I   | This is connect to the least sign<br>determines whether the data be<br>A0 = "H": Indicates that D0 to<br>A0 = "L": Indicates that D0 to I                                                                                             | oits are data o<br>D7 are displa                                                                                                                                                                                                                                                                                                                                                                   | or a command.<br>ly data.                              | J address bus, ar   | nd it       | 1            |  |  |

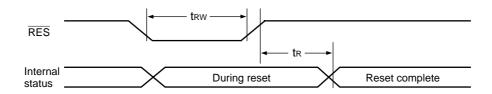

| RES                       | I   | When RES is set to "L," the se<br>The reset operation is perform                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                    |                                                        |                     |             | 1            |  |  |

| CS1<br>CS2                | I   | This is the chip select signal. becomes active, and data/con                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                    |                                                        | I," then the chip s | select      | 2            |  |  |

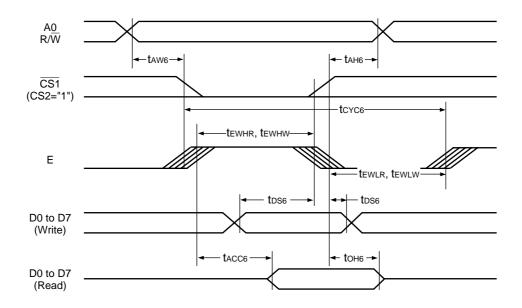

| RD<br>(E)                 | I   | <ul> <li>When connected to an 808<br/>This pin is connected to the<br/>data bus is in an output sta</li> <li>When connected to a 6800<br/>This is the 68000 Series M</li> </ul>                                                       | e RD signal o<br>tus when this<br>Series MPU                                                                                                                                                                                                                                                                                                                                                       | f the 8080 MPU,<br>signal is "L".<br>this is active HI | GH.                 | 5 series    | 1            |  |  |

| WR<br>(R/W)               | I   | <ul> <li>When connected to an 808<br/>This terminal connects to the<br/>latched at the rising edge or<br/>When connected to a 6800<br/>This is the read/write control<br/>When R/W = "H": Read.<br/>When R/W = "L": Write.</li> </ul> | ne 8080 MPU<br>f the WR sign<br>Series MPU                                                                                                                                                                                                                                                                                                                                                         | WR signal. The nal.                                    | signals on the da   | ata bus are | 1            |  |  |

| C86                       | I   | This is the MPU interface swit<br>C86 = "H": 6800 Series MP<br>C86 = "L": 8080 MPU interf                                                                                                                                             | U interface.                                                                                                                                                                                                                                                                                                                                                                                       |                                                        |                     |             | 1            |  |  |

| P/S                       | Ι   | This is the parallel data input/s<br>P/S = "H": Parallel data input.<br>P/S = "L": Serial data input.<br>The following applies dependi                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                    |                                                        | al.                 | _           | 1            |  |  |

|                           |     | P/S Data/Command                                                                                                                                                                                                                      | Data                                                                                                                                                                                                                                                                                                                                                                                               | Read/Write                                             | Serial Clock        | -           |              |  |  |

|                           |     | "H" A0<br>"L" A0                                                                                                                                                                                                                      | D0 to D7<br>SI (D7)                                                                                                                                                                                                                                                                                                                                                                                | RD, WR<br>Write only                                   | SCL (D6)            |             |              |  |  |

|                           |     | $\overline{RD}$ (E) and $\overline{WR}$ (P/W) are fixe                                                                                                                                                                                | When P/S = "L", D0 to D5 are HZ. D0 to D5 may be "H", "L" or Open.<br>$\overline{RD}$ (E) and $\overline{WR}$ (P/ $\overline{W}$ ) are fixed to either "H" or "L".<br>With serial data input, RAM display data reading is not supported.                                                                                                                                                           |                                                        |                     |             |              |  |  |

| CLS                       | Ι   | circuit.<br>CLS = "H": Internal oscillato<br>CLS = "L": Internal oscillato                                                                                                                                                            | Ferminal to select whether or enable or disable the display clock internal oscillator                                                                                                                                                                                                                                                                                                              |                                                        |                     |             |              |  |  |

# SED1565 Series

| Pin Name | I/O                                                                                                   |                                            | Function                                                 |                                                                                             |                                                                                                                  |                                           |                                        |                      |                  |   |

|----------|-------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------|----------------------|------------------|---|

| M/S      | I                                                                                                     | operat<br>operat<br>the liqu<br>M/S<br>M/S | ion outp<br>ion inpu<br>uid crys<br>S = "H":<br>S = "L": | outs the timing<br>uts the timing s<br>tal display sys<br>Master operatio<br>Slave operatio | ion                                                                                                              | e required for the liqu                   | or the LCD<br>id crystal d             | display, wh          | nile slave       | 1 |

|          |                                                                                                       | M/S                                        | CLS                                                      | Oscillator<br>Circuit                                                                       | Power<br>Supply<br>Circuit                                                                                       | CL                                        | FR                                     | FRS                  | DOF              |   |

|          |                                                                                                       | "H"                                        | "H"<br>"L"                                               | Enabled<br>Disabled                                                                         | Enabled<br>Enabled                                                                                               | Output<br>Input                           | Output<br>Output                       | Output<br>Output     | Output<br>Output |   |

|          |                                                                                                       | "L"                                        | "H"<br>"L"                                               | Disabled<br>Disabled                                                                        | Disabled<br>Disabled                                                                                             | Input<br>Input                            | Input<br>Input                         | Output<br>Output     | Input<br>Input   |   |

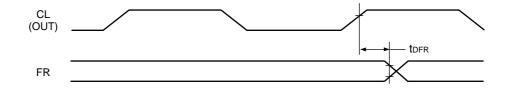

| CL       | I/O                                                                                                   | This is<br>The fo                          | the dis<br>llowing                                       | play clock inpu<br>is true depend                                                           | ut terminal<br>ling on the M/S                                                                                   | and CLS s                                 | tatus.                                 |                      |                  | 1 |

|          |                                                                                                       | M/S                                        | CL                                                       |                                                                                             | -                                                                                                                |                                           |                                        |                      |                  |   |

|          |                                                                                                       | "H"                                        | "H"<br>"L"                                               |                                                                                             |                                                                                                                  |                                           |                                        |                      |                  |   |

|          |                                                                                                       | "L"                                        | "H'<br>"L'                                               | ' Input                                                                                     | _                                                                                                                |                                           |                                        |                      |                  |   |

|          | When the SED1565 Series chips are used in master/slave mode, the various terminals must be connected. |                                            |                                                          |                                                                                             |                                                                                                                  |                                           |                                        | s CL                 |                  |   |

| FR       | I/O                                                                                                   | M/S<br>M/S<br>When                         | 5 = "H":<br>5 = "L":                                     | Output<br>Input<br>D1565 Series o                                                           | rnating current                                                                                                  | -                                         |                                        | e various F          | R terminals      | 1 |

| DOF      | I/O                                                                                                   | M/S<br>M/S<br>When                         | 5 = "H":<br>5 = "L":<br>the SEI                          | Output<br>Input                                                                             | lay blanking co<br>chip is used in i<br>d.                                                                       |                                           |                                        | e various D          | OF               | 1 |

| FRS      | 0                                                                                                     | This te                                    | erminal                                                  | is only enabled                                                                             | or the static driv<br>d when the stat<br>d in conjunction                                                        | ic indicator                              |                                        | ON when in           | master           | 1 |

| IRS      | I                                                                                                     | IRS<br>IRS<br>extern<br>This pi            | = "H":<br>= "L": I<br>al resis<br>n is ena               | Use the interna<br>Do not use the<br>tive voltage div<br>abled only whe                     | istors for the Va<br>al resistors<br>internal resistor<br>vider attached to<br>en the master o<br>when the slave | ors. The V5<br>o the VR te<br>peration mo | voltage lev<br>rminal.<br>ode is selec | el is regula<br>ted. | ted by an        | 1 |

| HPM      | Ι                                                                                                     | HPI<br>HPI<br>This pi                      | ∏ = "H"<br>∏ = "L":<br>n is ena                          | : Normal mode<br>High power m<br>abled only whe                                             |                                                                                                                  | peration mo                               | ode is selec                           | ted.                 | al drive.        | 1 |

## Liquid Crystal Drive Pins

| Pin Name             | I/O |                            | Function  |                                                                    |                 |          |          |     |

|----------------------|-----|----------------------------|-----------|--------------------------------------------------------------------|-----------------|----------|----------|-----|

| SEG0<br>to<br>SEG131 | 0   |                            |           | stal segment drive ou<br>RAM and with the FR                       |                 |          |          | 132 |

|                      |     | RAM DATA                   | FR        | Output                                                             | Voltage         |          |          |     |

|                      |     |                            |           | Normal Display                                                     | Reverse Display | /        |          |     |

|                      |     | Н                          | Н         | Vdd                                                                | V2              |          |          |     |

|                      |     | Н                          | L         | V5                                                                 | V3              |          |          |     |

|                      |     | L                          | Н         | V2                                                                 | Vdd             |          |          |     |

|                      |     | L                          | L         | V3                                                                 | V5              |          |          |     |

|                      |     | Power save                 | _         | V                                                                  | DD              |          |          |     |

| COM0                 | 0   | These are the lic          | uid cry   | stal common drive ou                                               | itputs.         |          |          |     |

| to                   |     | Part No.                   |           | СОМ                                                                | Part No.        |          |          |     |

| COM31                |     | SED1565***                 | CO        | M 0 to COM 63                                                      | SED1565***      | 64       |          |     |

|                      |     | SED1566***                 | CO        | M 0 to COM 47                                                      | SED1566***      | 48       |          |     |

|                      |     | SED1567***                 | CO        | M 0 to COM 31                                                      | SED1567***      | 32       |          |     |

|                      |     | SED1568***                 | CO        | M 0 to COM 53                                                      | SED1568***      | 54       |          |     |

|                      |     | SED1569***                 | CO        | M 0 to COM 51                                                      | SED1569***      | 52       |          |     |

|                      |     |                            |           | of the contents of the<br>rom VDD, V1, V4, and<br>Output Voltage   |                 | the FR s | ignal, a | 64  |

|                      |     | Н                          | Н         | V5                                                                 |                 |          |          |     |

|                      |     | Н                          | L         | Vdd                                                                |                 |          |          |     |

|                      |     | L                          | Н         | V1                                                                 |                 |          |          |     |

|                      |     | L                          | L         | V4                                                                 |                 |          |          |     |

|                      |     | Power Save                 | —         | Vdd                                                                |                 |          |          |     |

| COMS                 | 0   | signal.<br>Leave these ope | en if the | put terminals for the i<br>y are not used.<br>node, the same signa |                 |          |          | 2   |

#### • Test Terminals

| Pin Name      | I/O | Function                                                          | No. of<br>Pins |

|---------------|-----|-------------------------------------------------------------------|----------------|

| TEST0<br>to 9 | I/O | These are terminals for IC chip testing.<br>They are set to OPEN. | 14             |

|               |     | Total: 288 pins for the SE                                        | D1565***       |

Total:

288 pins for the SED1565\*\*\*.

272 pins for the SED1566\*\*\*.

256 pins for the SED1567\*\*\*.

276 pins for the SED1569\*\*\*.

276 pins for the SED1569\*\*\*.

## ■ ABSOLUTE MAXIMUM RATINGS

Unless otherwise noted, VSS = 0 V

| Parame                                                                                 | ter         | Symbol         | Conditions                                   | Unit |

|----------------------------------------------------------------------------------------|-------------|----------------|----------------------------------------------|------|

| Power Supply Voltage                                                                   |             | Vdd            | -0.3 to +7.0                                 | V    |

| Power supply voltage (2)<br>(VDD standard)<br>With Triple step-up<br>With Quad step-up |             | VSS2           | -7.0 to +0.3<br>-6.0 to +0.3<br>-4.5 to +0.3 | V    |

| Power supply voltage (3) (VI                                                           | D standard) | V5, Vout       | -18.0 to +0.3                                | V    |

| Power supply voltage (4) (V                                                            | D standard) | V1, V2, V3, V4 | V5 to +0.3                                   | V    |

| Input voltage                                                                          |             | Vin            | -0.3 to VDD + 0.3                            | V    |

| Output voltage                                                                         |             | Vo             | -0.3 to VDD + 0.3                            | V    |

| Operating temperature                                                                  |             | Topr           | -40 to +85                                   |      |

| Storage temperature TCP<br>Bare chip                                                   |             | Tstr           | -55 to +100<br>-55 to +125                   | °C   |

Notes and Cautions

- 1. The Vss2, V1 to V5 and VOUT are relative to the VDD = 0V reference.

- 2. Insure that the voltage levels of V1, V2, V3, and V4 are always such that  $VDD \ge V1 \ge V2 \ge V3 \ge V4 \ge V5$ .

- 3. Permanent damage to the LSI may result if the LSI is used outside of the absolute maximum ratings. Moreover, it is recommended that in normal operation the chip be used at the electrical characteristic conditions, and use of the LSI outside of these conditions may not only result in malfunctions of the LSI, but may have a negative impact on the LSI reliability as well.

## ■ DC CHARACTERISTICS

Unless otherwise specified, VSS = 0 V, VDD = 3.0 V  $\pm$  10%, Ta = –40 to 85°C

|           |                                               | tem                                                                  | Symbol           | Condit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ion                                |                                                                    | Rating        |                                                   | Units    | Applicable       |

|-----------|-----------------------------------------------|----------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------|---------------|---------------------------------------------------|----------|------------------|

|           |                                               | tem                                                                  | Symbol           | Condit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Condition                          |                                                                    | Тур.          | Max.                                              | Units    | Pin              |

|           | erating<br>Itage (1)                          | Recommended<br>Voltage<br>Possible<br>Operating<br>Voltage           | Vdd              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    | 2.7<br>1.8                                                         |               | 3.3<br>5.5                                        | V<br>V   | Vdd*1<br>Vdd*1   |

|           | erating                                       | Recommended                                                          | Vss2             | (Relative to VDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                    | -3.3                                                               | _             | -2.7                                              | V        | VSS2             |

| Vo        | ltage (2)                                     | Voltage<br>Possible<br>Operating<br>Voltage                          | Vss2             | (Relative to VDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                    | -6.0                                                               | _             | -1.8                                              | V        | VSS2             |

|           | erating<br>Itage (3)                          | Possible<br>Operating<br>Voltage                                     | V5               | (Relative to VDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                    | -16.0                                                              | _             | -4.5                                              | V        | V5 *2            |

|           |                                               | Possible<br>Operating<br>Voltage<br>Possible<br>Operating<br>Voltage | V1, V2<br>V3, V4 | (Relative to VDD)<br>(Relative to VDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                    | 0.4 × V5<br>V5                                                     | _             | VDD<br>0.6 × V5                                   | V        | V1, V2<br>V3, V4 |

|           |                                               | put Voltage<br>out Voltage                                           | Vihc<br>Vilc     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    | $\begin{array}{c} 0.8 \times \text{VDD} \\ \text{Vss} \end{array}$ |               | VDD<br>$0.2 \times VDD$                           | V<br>V   | *3<br>*3         |

|           |                                               | utput Voltage<br>Itput Voltage                                       | Vонс<br>Volc     | IOH = -0.5 mA<br>IOL = 0.5 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                    | $\begin{array}{c} 0.8 \times \text{VDD} \\ \text{Vss} \end{array}$ |               | $\begin{array}{c} VDD\\ 0.2\timesVDD \end{array}$ | V<br>V   | *4<br>*4         |

|           | out leakage<br>Itput leaka                    | e current<br>ge current                                              | Ili<br>Ilo       | VIN = VDD or VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    | -1.0<br>-3.0                                                       |               | 1.0<br>3.0                                        | μΑ<br>μΑ | *5<br>*6         |

|           | luid Crysta<br>I Resistan                     |                                                                      | Ron              | Ta = 25°C<br>(Relative To VDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V5 = -14.0 V<br>V5 = -8.0 V        | —                                                                  | 2.0<br>3.2    | 3.5<br>5.4                                        | ΚΩ<br>ΚΩ | SEGn<br>COMn *7  |

|           |                                               | mption Current<br>age Current                                        | ISSQ<br>I5Q      | V5 = -18.0 V (Rela                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ative To Vdd)                      |                                                                    | 0.01<br>0.01  | 5<br>15                                           | μΑ<br>μΑ | Vss, Vss2<br>V5  |

| Inp       | out Termin                                    | al Capacitance                                                       | CIN              | Ta = 25°C f = 1 Mł                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Hz                                 | _                                                                  | 5.0           | 8.0                                               | pF       |                  |