# **SPT8000**

## 14-BIT, 20 MSPS, CMOS A/D CONVERTER

## PRELIMINARY INFORMATION

### **FEATURES**

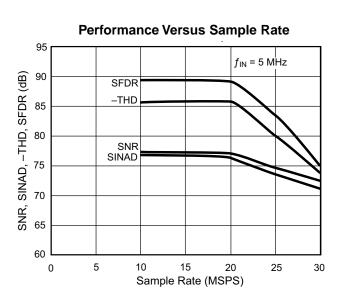

- 14-bit, 20 MSPS CMOS analog-to-digital converter

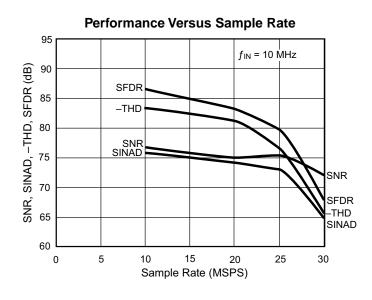

- Excellent performance:

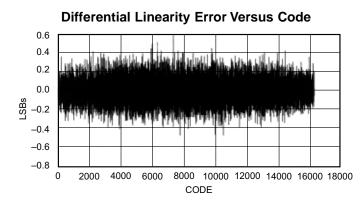

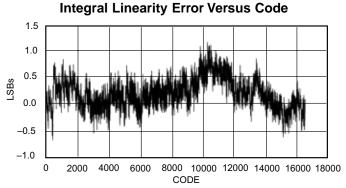

DLE: ±0.5 LSB, ILE: ±1.2 LSB

12.1 Effective Number of Bits @ f<sub>IN</sub> = 5 MHz

SFDR = 87 dB @ f<sub>IN</sub> = 5 MHz

- Internal sample-and-hold and voltage reference

- Power dissipation: 725 mW at 20 MSPS

- +5 V analog supply and +3.3/5 V digital output supply

- Out-of-range indicator

- 44-lead TQFP plastic package

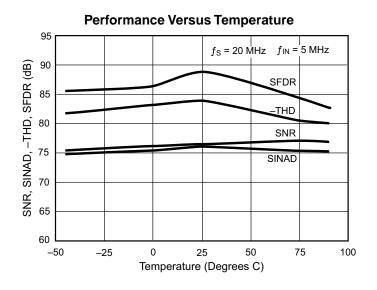

- -40 °C to +85 °C temperature range

## **APPLICATIONS**

- OCTOBER 12, 2001

- · Wireless communications

- IR imaging

- · Scanners and digital copiers

- High-end CCD cameras

- Medical imaging

- · Automatic test equipment

- Data acquisition systems

- · Lab and test equipment

## **DESCRIPTION**

This high-performance, 14-bit analog-to-digital converter operates at a sample rate of up to 20 MSPS. It utilizes a digitally calibrated, pipelined CMOS architecture to achieve excellent dynamic performance and linearity. Incorporated on chip are a high-performance sample-and-hold amplifier and internal reference for minimal external circuitry.

The excellent linearity and superb dynamic performance of this device make it ideal for image processing and in-

strumentation applications, as well as communications applications.

The device operates from a single +5 V supply. A separate digital output supply pin is provided for +3/5 V logic output levels. Total power dissipation, including internal reference, is 725 mW. It is in a 44-lead TQFP package over the industrial temperature range of -40 °C to +85 °C.

## ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur) 25 °C

| Supply Voltages  |                                   | Digital Outputs                                  |

|------------------|-----------------------------------|--------------------------------------------------|

| AV <sub>DD</sub> | +6 V                              | Output Current±10 mA                             |

| OV <sub>DD</sub> | +6 V                              | Temperature                                      |

| Input Voltages   |                                   | Operating Temperature40 to +85 °C                |

| Analog Inputs    | –0.3 V to AV <sub>DD</sub> +0.3 V | Junction Temperature+175 °C                      |

| CLK Input        | –0.3 V to AV <sub>DD</sub> +0.3 V | Lead Temperature, (soldering 10 seconds) +300 °C |

| Digital Inputs   | –0.3 V to AV <sub>DD</sub> +0.3 V | Storage Temperature –65 to +150 °C               |

**Note:** Operation at any Absolute Maximum Rating is not implied. See Electrical Specifications for proper nominal applied conditions in typical applications.

## **ELECTRICAL SPECIFICATIONS**

$T_A$ =25 °C,  $AV_{DD}$ =+5.0 V,  $OV_{DD}$ =3.3 V,  $f_S$ =20 MSPS, Internal References, unless otherwise specified.

| PARAMETERS                                                                                                                                                                                         | TEST<br>CONDITIONS                                                                                                | TEST<br>LEVEL    | SPT8000<br>MIN TYP                                          | MAX               | UNITS                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------|-------------------|----------------------------------------------|

| Resolution                                                                                                                                                                                         |                                                                                                                   |                  | 14                                                          |                   | Bits                                         |

| DC Performance Differential Linearity Error (DLE) Integral Linearity Error (ILE) No Missing Codes Offset (Mid Scale) Error Gain Error Offset Error Temperature Drift¹ Gain Error Temperature Drift | External V <sub>RT</sub> & V <sub>RC</sub> -40 to +85 °C External V <sub>RT</sub> & V <sub>RC</sub> -40 to +85 °C | V<br>V<br>V<br>V | ±0.5<br>±1.2<br>Guaranteed<br>±1.0<br>±0.05<br>±2.4<br>±3.5 |                   | LSB<br>LSB<br>% FS<br>ppm FS/°C<br>ppm FS/°C |

| Analog Input Input Voltage Span <sup>2</sup> : V <sub>IN</sub> +, V <sub>IN</sub> - Input Capacitance Input Full-Power Bandwidth                                                                   | Common Mode=+2.25 V                                                                                               | V<br>V           | ±1<br>10<br>82                                              |                   | V<br>pF<br>MHz                               |

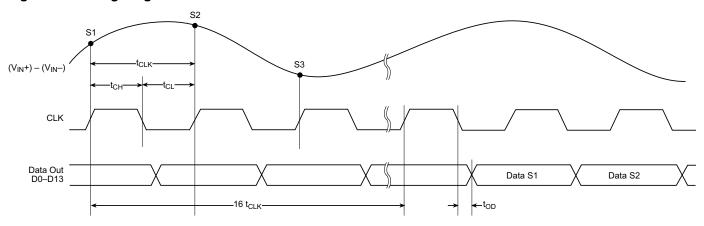

| Timing Characteristics Conversion Rate Pipeline Delay (Latency) Clock Duty Cycle Clock Period (t <sub>CLK</sub> ) Output Delay (t <sub>OD</sub> )                                                  | C <sub>L</sub> =3.5 pF                                                                                            | V<br>V<br>V<br>V | 20<br>16.5<br>40 50<br>50<br>8                              | 25<br>60          | MSPS<br>Clock Cycles<br>%<br>ns<br>ns        |

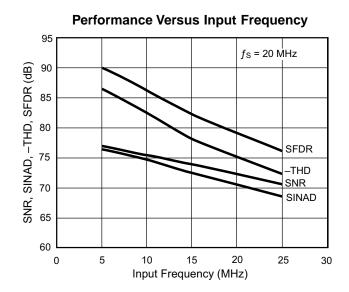

| Dynamic Performance  Effective Number of Bits (ENOBs)  Signal-to-Noise and Distortion (SINAD)  Signal-to-Noise Ratio (SNR)  Total Harmonic Distortion (THD)  Spurious Free Dynamic Range (SFDR)    | $f_{IN} = 5 \text{ MHz}$<br>$f_{IN} = 5 \text{ MHz}$                                                              | V<br>V<br>V      | 12.1<br>74.5<br>75<br>–84<br>87                             |                   | Bits<br>dB<br>dB<br>dB<br>dB                 |

| Digital Inputs (CAL, RESETB) Logic 1 Voltage Logic 0 Voltage Logic 1 Input Current Logic 0 Input Current Input Capacitance                                                                         |                                                                                                                   | V<br>V<br>V<br>V | 2.4<br>-10<br>-10                                           | 0.8<br>+10<br>+10 | V<br>V<br>µA<br>µA<br>pF                     |

<sup>&</sup>lt;sup>1</sup> After one-time calibration at 25 °C.

$<sup>^2</sup>$  Each of  $V_{IN}+$  and  $V_{IN}-$  ranges from +1.25 V to +3.25 V, making the span of differential input,  $(V_{IN}+)-(V_{IN}-)$ , to be -2.0 V to +2.0 V.

## **ELECTRICAL SPECIFICATIONS**

$T_A$ =25 °C, AV<sub>DD</sub>=+5.0 V, OV<sub>DD</sub>=3.3 V,  $f_S$ =20 MSPS, Internal References, unless otherwise specified.

| PARAMETERS                                                                                                                                                                                           | TEST<br>CONDITIONS                                                                                                                                                                                                                                                                | TEST<br>LEVEL    | MIN         | SPT8000<br>TYP                                                                               | MAX          | UNITS                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------|----------------------------------------------------------------------------------------------|--------------|--------------------------|

| Clock Input (CLK) Logic 1 Voltage Logic 0 Voltage Logic 1 Input Current Logic 0 Input Current Input Capacitance                                                                                      |                                                                                                                                                                                                                                                                                   | V<br>V           | -10<br>-10  | TBD<br>TBD                                                                                   | +10<br>+10   | V<br>V<br>µA<br>µA<br>pF |

| Digital Outputs (D0-D13, OTR, BUSY) Logic 1 Voltage  Logic 0 Voltage                                                                                                                                 | $\begin{array}{c} I_{OH}\!\!=\!\!4.5~\text{mA, OV}_{DD}\!\!=\!\!5~\text{V} \\ I_{OH}\!\!=\!\!2.5~\text{mA, OV}_{DD}\!\!=\!\!3.3~\text{V} \\ I_{OL}\!\!=\!\!-4.5~\text{mA, OV}_{DD}\!\!=\!\!5~\text{V} \\ I_{OL}\!\!=\!\!-2.5~\text{mA, OV}_{DD}\!\!=\!\!3.3~\text{V} \end{array}$ | V<br>V<br>V      |             | 90% OV <sub>DD</sub><br>90% OV <sub>DD</sub><br>10% OV <sub>DD</sub><br>10% OV <sub>DD</sub> |              | V<br>V<br>V              |

| Voltage Reference Output Voltage (V <sub>REF</sub> ) Reference Temperature Coefficient Top Reference Voltage (V <sub>RT</sub> ) Bottom Reference Voltage (V <sub>RC</sub> ) Common Mode Voltage (CM) |                                                                                                                                                                                                                                                                                   | V<br>V<br>V<br>V |             | 1.0<br>100<br>3.25<br>1.25<br>2.25                                                           |              | V<br>ppm/°C<br>V<br>V    |

| Power Supply Requirements  AV <sub>DD</sub> Supply Voltage  OV <sub>DD</sub> Supply Voltage  AV <sub>DD</sub> Supply Current  OV <sub>DD</sub> Supply Current  Power Dissipation                     | Full Scale 5 MHz Input<br>Full Scale 5 MHz Input<br>Full Scale 5 MHz Input                                                                                                                                                                                                        | V<br>V<br>V<br>V | 4.75<br>3.3 | 5.0<br>145<br>0.07<br>725                                                                    | 5.25<br>5.25 | V<br>V<br>mA<br>mA<br>mW |

### **TEST LEVEL CODES**

All electrical characteristics are subject to the following conditions:

All parameters having min/max specifications are guaranteed. The Test Level column indicates the specific device testing actually performed during production and Quality Assurance inspection. Any blank section in the data column indicates that the specification is not tested at the specified condition.

## LEVEL TEST PROCEDURE

I

100% production tested at the specified temperature.

II 100% production tested at  $T_A$  = +25 °C, and sample tested at the specified temperatures.

III QA sample tested only at the specified temperatures.

IV Parameter is guaranteed (but not tested) by design and characterization data.

V Parameter is a typical value for information purposes only.

VI 100% production tested at  $T_A = +25$  °C. Parameter is guaranteed over specified temperature range.

3

#### SPECIFICATION DEFINITIONS

# DIFFERENTIAL LINEARITY ERROR (DLE) OR DIFFERENTIAL NONLINEARITY (DNL)

In an ideal ADC, code transitions are 1 LSB apart. Differential Linearity Error is the maximum deviation, expressed in LSBs, from this ideal value.

# INTEGRAL LINEARITY ERROR (ILE) OR INTEGRAL NONLINEARITY (INL)

The ideal transfer for an ADC is a straight line drawn between "zero" and "full scale." The point used as "zero" occurs 0.5 LSB before the first code transition. "Full scale" is defined as a level 1.5 LSB beyond the last code transition. ILE is the worst-case deviation of a code from the straight line. The deviation of each code is measured from the middle of that code.

#### MISSING CODE

A code with zero width is missing. A code that is missing will have a DLE of -1. For example, as the input voltage is increasing, the output will jump between the adjacent codes, from 11...001 to 11...011, skipping 11...010. A specification that guarantees no missing codes requires that every code combination appear in a monotonically increasing sequence as the analog input is increased.

## OFFSET ERROR, BIPOLAR

In the differential mode, the major carry transition (0111...1 to 1000...0) should occur for an analog value 0.5 LSB below mid scale (0 V differential input). The Offset Error specifies the deviation of the actual transition from that point.

### **GAIN ERROR**

The last transition should occur at an analog value 1.5 LSB below the nominal full scale. The first transition is 0.5 LSB above the low end of the scale (–FS in bipolar converters). The gain error is the deviation of the actual difference between the first and last code transitions from the ideal difference between the first and last transitions.

#### INPUT FULL-POWER BANDWIDTH

The frequency at which the amplitude of the reconstructed fundamental signal is reduced by 3 dB for a full-scale input.

## **CLOCK DUTY CYCLE**

Ratio of clock pulse high ( $t_{CH}$ ) to total clock period ( $t_{CLK}$ ) times 100%.

Duty Cycle =

$$\frac{t_{CH}}{t_{CLK}}$$

X 100%

## SIGNAL-TO-NOISE RATIO (SNR)

The ratio of the power of the desired signal (fundamental) to the sum of the power of noise signals at a given point in time. The first 9 harmonics are excluded from the noise signals. Usually expressed in dB.

#### **HARMONIC**

- 1.Of a sinusoidal wave, an integral multiple of the frequency of the wave. Note: The frequency of the sine wave is called the *fundamental frequency* or the first harmonic, the second harmonic is twice the fundamental frequency, the third harmonic is thrice the fundamental frequency, etc.

- 2. Of a periodic signal or other periodic phenomenon, such as an electromagnetic wave or a sound wave, a component frequency of the signal that is an integral multiple of the fundamental frequency. Note: The fundamental frequency is the reciprocal of the period of the periodic phenomenon. Contrast with fundamental overtone.

## TOTAL HARMONIC DISTORTION (THD)

The ratio of the sum of the power of first 9 harmonics above the fundamental frequency to the power of the fundamental frequency. Usually expressed in dB.

# SIGNAL-TO-NOISE AND DISTORTION RATIO (SINAD)

The ratio of the power of the desired signal (fundamental) to the sum of the power of all spectral components below Nyquist Frequency, including noise and distortion. Usually expressed in dB.

## **EFFECTIVE NUMBER OF BITS (ENOB)**

SINAD = 6.02N + 1.76, where N is equal to the effective number of bits.

$$N = \frac{SINAD - 1.76}{6.02}$$

#### SPURIOUS FREE DYNAMIC RANGE (SFDR)

The ratio of the fundamental sinusoidal power to the power of the single largest harmonic or spurious signal.

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 1 - Timing Diagram

## **FUNCTIONAL DESCRIPTION**

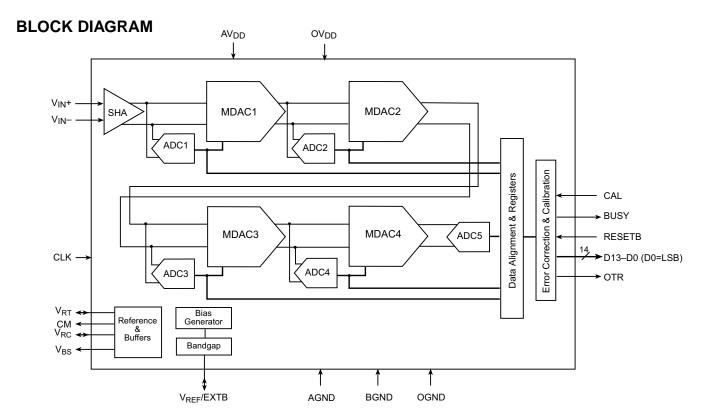

The SPT8000 is a five-stage, pipeline analog-to-digital converter (ADC) implemented in a fine-line CMOS process. The block diagram on page one illustrates the device's functional block-level implementation. The input sample-and-hold amplifier (SHA) guarantees its specified performance for the input signal frequencies up to the Nyquist frequency. It samples the differential analog input signal at the rising edge of CLK input and holds it for the next half-clock cycle. The SHA starts acquiring the input signal once CLK input goes low and acquires the next sample at the next rising edge of CLK.

Each of the first four pipeline stages consists of a flash ADC (ADCn) and a multiplying digital-to-analog converter (MDACn), where n=1, 2, 3 or 4. The first stage flash ADC (ADC1) digitizes the output of the SHA and produces a lower-resolution digital code corresponding to the SHA output. The first stage MDAC1 subtracts from the SHA output the ideal voltage corresponding to the ADC1 code to generate the residue voltage, then amplifies the residue and passes it to the second stage. The subsequent stages 2 through 4 repeat the same operation, and ADC5 gives the last digital code corresponding to the output of MDAC4. The digital codes from ADC1 to ADC5 are time aligned and stored inside the "Data Alignment & Registers" block.

The SPT8000 incorporates one bit of overlap between two subsequent pipeline stages and uses this redundancy to digitally correct for errors in ADC1 through ADC4. In addition, the SPT8000 employs an internal digital calibration circuitry to eliminate errors of the SHA and MDACs. Its function is controlled by an internal microcontroller. When in calibration mode, the SPT8000 configures itself such that errors of each stage can be measured by the ADC made of subsequent stages. The measured errors are stored in on-chip digital memory (RAM). During subsequent normal conversions, the microcontroller looks up

the RAM contents and makes digital corrections of the errors, to produce the final 14-bit digital output free of the errors. The 14-bit digital output along with OTR (out-of-range flag) are latched and buffered to drive the output pins. These output buffers have their own power supply and ground (OV $_{DD}$  and OGND), and can interface +5 V or +3.3 V external logic circuitry.

The SPT8000 has an internal bandgap voltage reference that produces a temperature-stable 1 V output at  $V_{REF}/EXTB$  pin. This voltage sets the input span of the SPT8000 about CM of 2.25 V. Therefore, the input span nominally is set to 1.25 V ( $V_{RC}$ ) to 3.25 V ( $V_{RT}$ ). Internal buffers provide low-impedance outputs for CM,  $V_{RT}$  and  $V_{RC}$  that are used throughout the pipeline stages. The output impedance of the  $V_{REF}/EXTB$  pin is set relatively high (approximately 4.7 k $\Omega$ ), allowing the user to override the internal 1 V reference and change the input span. The user can also drive  $V_{RT}$  and  $V_{RC}$  directly with external buffers. To do this,  $V_{REF}/EXTB$  must be shorted to AGND. Shorting this pin to AGND disables the internal buffers driving  $V_{RT}$  and  $V_{RC}$ .

## INTERNAL DIGITAL CALIBRATION

The SPT8000 achieves the specified performance by internal digital calibration, eliminating the need for external adjustments or trimming by the user.

The calibration takes advantage of the fact that the accuracy requirement for a pipeline stage is progressively reduced. For example, the SHA and MDAC1 must be accurate to 14 bits in order to achieve 14 bits of overall ADC accuracy. If we assume that ADC1's resolution is N and that there is a one-bit overlap between the first and second stages, the accuracy requirement for MDAC2 is reduced to (14–N+1) bits (note: N>1). The obtainable accuracy of a stage is set by the circuit's non-idealities such as device mismatches, finite bandwidth, finite gain, etc. For the specific implementation of the SPT8000, the

process warrants the required accuracy of stage 4 and stage 5 without calibration.

The calibration sequence starts with the ADC made of stage 4 and 5 measuring errors in MDAC3 and storing the digital representation of each of the errors (calibration coefficient) in RAM. The stage 3 calibration coefficients are used to make the ADC composed of stage 3, 4 and 5 accurate to its required specifications. The next sequence measures errors in MDAC2 by the ADC made of stages 3, 4 and 5, and stores the calibration coefficients in RAM. This is repeated until all relevant errors of SHA and MDACs are measured and stored in RAM.

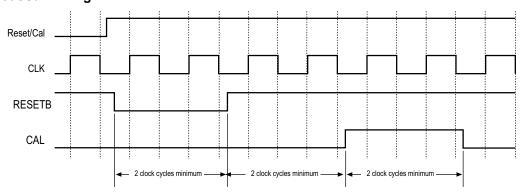

The user can initiate the calibration by driving the CAL pin high for more than two falling edges of CLK while holding RESETB high. The internal microcontroller then outputs high to the BUSY pin, indicating that the SPT8000 is in calibration mode. BUSY will remain high until all the calibration coefficients have been successfully measured and stored in RAM. Once BUSY returns to low, the SPT8000 is ready for normal conversions of analog input at V<sub>IN</sub>+ and V<sub>IN</sub>-. The number of clock cycles it takes to complete the digital calibration is about 1.49 million, which translates to 74.5 ms for a 20 MHz clock. By driving low the asynchronous reset pin, RESETB, the user can interrupt the calibration in progress. When the SPT8000 detects RESETB low, it clears all the calibration coefficients in RAM and sits in the initial idle state. In order to start new conversions to the specifications, the user must drive RESETB high again and drive CAL high to restart calibration.

It is important to note that both  $V_{IN}+$  and  $V_{IN}-$  pins are shorted to CM through a pair of internal switches. Therefore, the user must either leave  $V_{IN}+$  and  $V_{IN}-$  open or drive both to CM during the calibration mode. The digital ouputs during the calibration are controlled by the internal calibration machine and should be disregarded. It is the user's responsibility to establish stable power supplies and references (when external references are used) prior to issuing CAL high, and to maintain their integrity during the calibration.

# POWER-ON SEQUENCE AND INITIALIZATION

Power supplies  $AV_{DD}$  and  $OV_{DD}$  may be turned on in any sequence. Inputs  $V_{IN}+$ ,  $V_{IN}-$ , and CLK may be driven only after all the supplies have been established. If external references are used to drive  $V_{RT}$  and  $V_{RC}$  pins, they can be applied only after all supplies are in their normal range.

Once all supplies have been provided, CLK input may be driven with a frequency up to 20 MHz. The user must then initialize the SPT8000 in order to obtain the specified performance. To do this, the user must first drive RESETB pin to logic low for at least one full clock cycle and subsequently drive CAL high to initiate the internal calibration (see Internal Digital Calibration and Typical Interface Circuit sections).

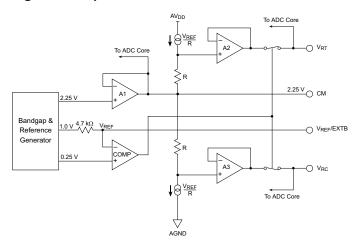

#### REFERENCE CIRCUIT

Figure 2, Equivalent Reference Circuit, shows the equivalent circuit that produces  $V_{RT},\,V_{RC},\,$  CM and  $V_{REF}/EXTB.$  The on-chip bandgap circuit creates temperature-stable reference voltages of 2.25 V and 1.0 V. The op amp A1 provides a buffer for 2.25 V and drives the CM pin, as well as the internal ADC core circuitry. The 1.0 V output from the bandgap has about 4.7 k $\Omega$  output impedance to the  $V_{REF}/EXTB$  pin. The span of the ADC is set to +V\_{REF} and –V\_REF about CM as shown in Figure 2, where V\_REF is the voltage at pin V\_REF/EXTB. A2 and A3 provide low impedance outputs at V\_RT and V\_RC. It should be noted that all three op amps in figure 2 (A1, A2, and A3) require an external capacitor of 4.7  $\mu F$  or larger from each output pin (V\_RT, V\_RC, or CM) to AGND for compensation as well as noise reduction.

The finite output impedance of the V<sub>REF</sub>/RSTB pin allows the user to use an external reference circuit to overdrive this pin. The user may do so in order to set a different ADC span voltage or to obtain a span voltage that has less drift over temperature than the internal reference. Note that the specified performance is guaranteed only for V<sub>REF</sub>=1.0 V. The user can also drive V<sub>RT</sub> and V<sub>RC</sub> directly with external buffers by shorting the V<sub>REF</sub>/RSTB pin to AGND externally. The internal comparator COMP detects this and disables both A2 and A3, making V<sub>RT</sub> and V<sub>RC</sub> pins high impedance.

Figure 2 – Equivalent Reference Circuit

7 10/12/01

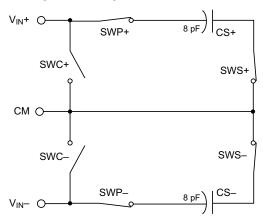

#### **EQUVALENT INPUT CIRCUIT**

Figure 3 shows a simplified, equivalent input circuit when the input is being sampled. The inputs,  $V_{IN}$ + and  $V_{IN}$ –, drive the bottom plates of the sampling capacitors, CS+ and CS–, respectively. The top plates of the sampling capacitors are shorted to CM through sampling switches SWS+ and SWS–. A sampling of the input is accomplished by simultaneously opening SWS+ and SWS–. An internal clock driver circuit generates this control signal so that the sampling instance is defined at the rising edge of CLK input.

The SPT8000 incorporates two switches that connect  $V_{IN}+$  and  $V_{IN}-$  to CM during calibration. These switches are shown as SWC+ and SWC- in Figure 3. The typical onresistance of the switches is about 900  $\Omega$  each. This configuration enables the internal calibration to calibrate out the offset error of SHA and to achieve the superb specification for mid-scale error of the ADC. The user must ensure that both  $V_{IN}+$  and  $V_{IN}-$  are left open or driven to CM during calibration.

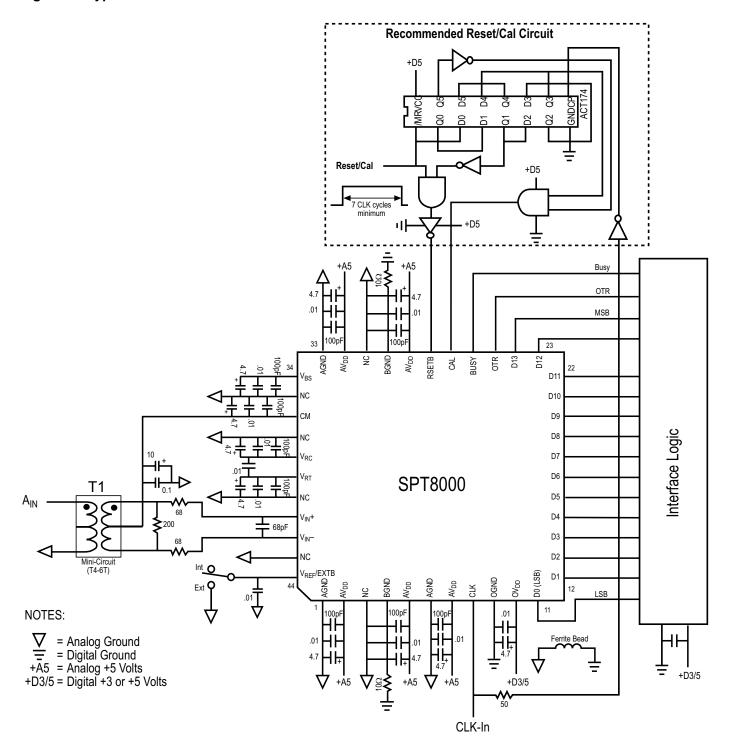

## TYPICAL INTERFACE CIRCUIT

Figure 5 shows a typical interface circuit reflecting the grounding and bypassing scheme used in the evaluation board. All bypass capacitors must be located as close to the package pins as possible. It is also important to keep a minimum lead distance between the input pins,  $V_{IN}$ + and  $V_{IN}$ –, and the transformer.

It is recommended that the user follow the timing requirements for RESETB and CAL indicated in Figure 4. In this example, RESETB stays logic low for two full clock cycles. CAL must remain logic high for two or more clock cycles, and the time from RESETB returning high to the rising edge of CAL must be at least two clock cycles, based on the internal operation of the SPT8000. It has been verified that the timing specified in Figure 4 functions properly with the evaluation board. However, it should be noted that this time between RESETB going high and CAL going high

Figure 3 - Equivalent Input Circuit

also depends on the external system design and configuration. Once RESETB goes low for two clock cycles, the SPT8000 initializes its internal bias condition. The internal initialization takes place instantaneously. However, the amount of time it takes for the voltages at  $V_{RT},\,V_{RC},\,CM,\,V_{BS},\,$  and  $V_{REF}/EXTB,\,$  to stabilize will vary depending on the external bypassing circuits at these pins. The user must ensure that the SPT8000 has reached a stable operation condition before initiating a calibration by driving CAL high. It is also a user's responsibility to make sure that all the power supplies have reached a stable condition before initiating the Reset/Cal sequence.

As in the case with any high-speed, high-resolution ADCs, the quality of clock input to the SPT8000 significantly affects its performance. A SHA with a sample clock jitter of  $t_J$ , sampling a full-scale input of frequency  $f_{IN}$ , has the SNR due only to the clock jitter given by:

$$SNR = -20 \bullet log_{10}(2\pi \bullet f_{IN} \bullet t_{J})$$

For a 10 MHz input with a 3 ps clock jitter, SNR is limited to 74.5 dB. It is therefore extremely important to drive the device with a clock signal having the lowest possible jitter.

Figure 4 - Reset/Cal Timing

8 10/12/01

Figure 5 - Typical Interface Circuit

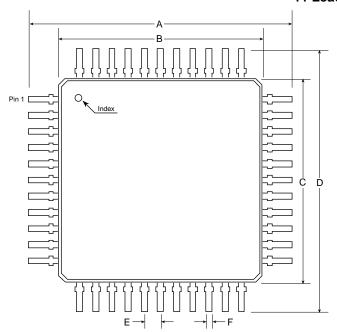

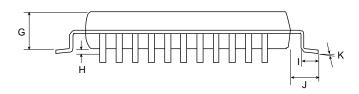

## **PACKAGE OUTLINE**

## 44-Lead TQFP

|        | INCHES |        | MILLIMETERS |       |

|--------|--------|--------|-------------|-------|

| SYMBOL | MIN T  | YP MAX | MIN TY      | P MAX |

| Α      | 0.630  |        | 16.00       |       |

| В      | 0.551  |        | 14.00       |       |

| С      | 0.551  |        | 14.00       |       |

| D      | 0.630  |        | 16.00       |       |

| E      | 0.0    | )39    | 1.0         | 00    |

| F      | 0.012  | 0.016  | 0.30        | 0.40  |

| G      | 0.053  | 0.057  | 1.35        | 1.45  |

| Н      | 0.002  | 0.006  | 0.05        | 0.15  |

| Į      | 0.020  | 0.030  | 0.50        | 0.75  |

| J      | 0.039  |        | 1.00        |       |

| K      | 0-7°   |        | 0-          | 7°    |

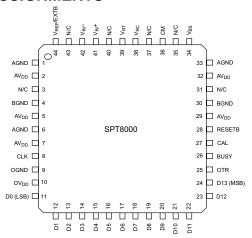

### **PIN ASSIGNMENTS**

### PIN FUNCTIONS

| Name             | Description                                                                                                                                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGND             | Ground                                                                                                                                                                                                        |

| $AV_{DD}$        | +5 V Supply                                                                                                                                                                                                   |

| N/C              | No Connect. Leave the pin open or tie it to AGND.                                                                                                                                                             |

| BGND             | Ground                                                                                                                                                                                                        |

| CLK              | Clock Input                                                                                                                                                                                                   |

| OGND             | Ground for BUSY, OTR, and Data Bit Outputs                                                                                                                                                                    |

| OV <sub>DD</sub> | +3.3 V to +5 V Supply for BUSY, OTR, and Data Bit Outputs                                                                                                                                                     |

| D0-D13           | Data Bit Outputs. D0=LSB, D13=MSB                                                                                                                                                                             |

| OTR              | Out of Range Output. OTR goes High for the Analog input above (overrange) or below (underrange) the full-scale range. The corresponding Data Bit Outputs are all 1s for overrange, and all 0s for underrange. |

| BUSY             | Busy Output. BUSY goes High when the SPT8000 goes into its internal calibration routine and                                                                                                                   |

|                        | remains High until it completes the calibration. The internal calibration routine takes approximately 74.5 ms for 20 MHz clock input. The SPT8000 ignores the Analog Input when BUSY is High. When BUSY is Low, it is ready to convert the Analog Input.                                                                                                                     |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAL                    | Calibration Start Input. Holding CAL High for more than two falling edges of CLK, while RESETB is High, initiates the SPT8000's internal calibration routine.                                                                                                                                                                                                                |

| RESETB                 | Reset Input (active Low). Logic 0 on this asynchronous reset pin will set the internal digital state machine to its initial state and clear all internal calibration coefficients.                                                                                                                                                                                           |

| V <sub>BS</sub>        | Noise Reduction Pin. Connect a noise reduction capacitor of 4.7 $\mu F$ or larger from this pin to AGND.                                                                                                                                                                                                                                                                     |

| СМ                     | Common Mode Level Output. +2.25 V nominal. Connect a noise reduction capacitor of 4.7 $\mu F$ or larger from this pin to AGND.                                                                                                                                                                                                                                               |

| V <sub>RC</sub>        | Lower Reference. +1.25 V nominal. This voltage sets the lower bound of analog input span. Connect a noise reduction capacitor of 4.7 µF or larger from this pin to AGND.                                                                                                                                                                                                     |

| V <sub>RT</sub>        | Upper Reference. +3.25 V nominal. This voltage sets the upper bound of analog input span. Connect a noise reduction capacitor of 4.7 $\mu F$ or larger from this pin to AGND.                                                                                                                                                                                                |

| V <sub>IN</sub> +      | Analog Input Pin (+). The nominal span at this pin is +1.25 V to +3.25 V.                                                                                                                                                                                                                                                                                                    |

| V <sub>IN</sub> –      | Analog Input Pin (–). The nominal span at this pin is $+3.25$ V to $+1.25$ V.                                                                                                                                                                                                                                                                                                |

| V <sub>REF</sub> /EXTB | Voltage Reference I/O Pin. +1.00 V nominal. The voltage at this pin sets the span above and below CM for each analog input pin. Driving $V_{REF}/EXTB$ to 0 V will disable internal buffers driving $V_{RT}$ and $V_{RC}$ , allowing the user to drive $V_{RT}$ and $V_{RC}$ externally. Connect a noise reduction capacitor of 4.7 $\mu F$ or larger from this pin to AGND. |

remains High until it completes the calibration. The

## ORDERING INFORMATION

| PART NUMBER | TEMPERATURE RANGE | PACKAGE  |

|-------------|-------------------|----------|

| SPT8000SIT  | −40 to +85 °C     | 44L TQFP |

## **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

## LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

© Copyright 2002 Fairchild Semiconductor Corporation