# HT27C4096 CMOS 256K×16-Bit OTP EPROM

#### **Features**

- · Operating voltage: +5.0V

- · Programming voltage

- V<sub>PP</sub>=12.5V±0.2V

- V<sub>CC</sub>=6.0V±0.2V

- · High-reliability CMOS technology

- Latch-up immunity to 100mA from -1.0V to V<sub>CC</sub>+1.0V

- · CMOS and TTL compatible I/O

- · Low power consumption

- Active: 30mA max.

- Standby: 1μA typ.

- 256K×16-bits organization

- Fast read access time: 70ns

- · Fast programming algorithm

- Programming time 75µs typ.

- Two line controls (OE and CE)

- · Standard product identification code

- Commercial temperature range (0°C to +70°C)

- 40-pin plastic DIP, 44-pin PLCC package

#### **General Description**

The HT27C4096 chip family is a low-power, 4096K (4,194,304) bits, +5V electrically one-time programmable (OTP) read-only memories (EPROM). Organized into 256K words with 16 bits per word, it features a fast single address location programming, typically at  $75\mu s$  per word. Any word can be accessed in less than 70ns

with respect to spec. This eliminates the need for WAIT states in high-performance microprocessor systems. The HT27C4096 has separate Output Enable  $(\overline{\text{OE}})$  and Chip Enable  $(\overline{\text{CE}})$  controls which eliminate bus contention issues.

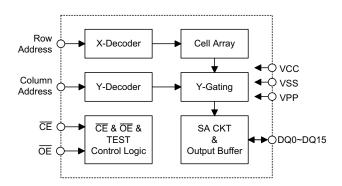

# **Block Diagram**

Rev. 1.10 1 November 21, 2002

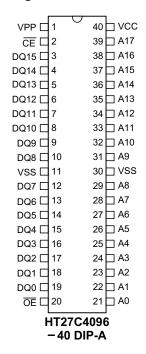

# **Pin Assignment**

## **Pin Description**

| Pin Name | I/O/P | Description                   |

|----------|-------|-------------------------------|

| VPP      | Р     | Program voltage supply        |

| CE       | I     | Chip enable                   |

| DQ0~DQ15 | I/O   | Data inputs/outputs           |

| VSS      | _     | Negative power supply, ground |

| ŌĒ       | I     | Output enable                 |

| A0~A17   | I     | Address inputs                |

| VCC      | _     | Positive power supply         |

# **Absolute Maximum Rating**

| Operation Temperature Commercial                                        | 0°C to +70°C                  |

|-------------------------------------------------------------------------|-------------------------------|

| Storage Temperature                                                     | 65℃ to 125°C                  |

| Applied V <sub>CC</sub> Voltage with Respect to VSS                     | 0.6V to 7.0V                  |

| Applied Voltage on Input Pin with Respect to VSS                        | 0.6V to 7.0V                  |

| Applied Voltage on Output Pin with Respect to VSS                       | 0.6V to V <sub>CC</sub> +0.5V |

| Applied Voltage on A9 Pin with Respect to VSS                           | 0.6V to 13.5V                 |

| Applied V <sub>PP</sub> Voltage with Respect to VSS                     | 0.6V to 13.5V                 |

| Applied READ Voltage (Functionality is guaranteed between these limits) | +4.5V to +5.5V                |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

# **D.C. Characteristics**

| Comple at        | Damana atau              | Т   | est Conditions                                              | Min.               | _    |                      |      |  |

|------------------|--------------------------|-----|-------------------------------------------------------------|--------------------|------|----------------------|------|--|

| Symbol           | Parameter                | Vcc | Conditions                                                  | Wiin.              | Тур. | Max.                 | Unit |  |

| Read ope         | ration                   | •   |                                                             |                    |      |                      |      |  |

| V <sub>OH</sub>  | Output High Level        | 5V  | I <sub>OH</sub> =-0.4mA                                     | 2.4                | _    | _                    | V    |  |

| V <sub>OL</sub>  | Output Low Level         | 5V  | I <sub>OL</sub> =2.1mA                                      | _                  | _    | 0.45                 | V    |  |

| V <sub>IH</sub>  | Input High Level         | 5V  | _                                                           | 2                  | _    | V <sub>CC</sub> +0.5 | V    |  |

| V <sub>IL</sub>  | Input Low Level          | 5V  | _                                                           | -0.3               | _    | 0.8                  | V    |  |

| ILI              | Input Leakage Current    | 5V  | V <sub>IN</sub> =0 to 5.5V                                  | -5                 | _    | 5                    | μΑ   |  |

| ILO              | Output Leakage Current   | 5V  | V <sub>OUT</sub> =0 to 5.5V                                 | -10                | _    | 10                   | μА   |  |

| I <sub>CC</sub>  | VCC Active Current       | 5V  | CE=V <sub>IL</sub> , f=5MHz,<br>I <sub>OUT</sub> =0mA       | _                  | _    | 30                   | mA   |  |

| I <sub>SB1</sub> | Standby Current (CMOS)   | 5V  | CE=V <sub>CC</sub> ±0.3V                                    | _                  | 1    | 10                   | μΑ   |  |

| I <sub>SB2</sub> | Standby Current (TTL)    | 5V  | CE=V <sub>IH</sub>                                          | _                  | _    | 1                    | mA   |  |

| Ірр              | VPP Read/Standby Current | 5V  | CE=OE=V <sub>IL</sub> ,<br>V <sub>PP</sub> =V <sub>CC</sub> | _                  | _    | 100                  | μΑ   |  |

| Program          | ning operation           | •   |                                                             |                    |      |                      |      |  |

| $V_{OH}$         | Output High Level        | 6V  | I <sub>OH</sub> =-0.4mA                                     | 2.4                | _    | _                    | V    |  |

| V <sub>OL</sub>  | Output Low Level         | 6V  | I <sub>OL</sub> =2.1mA                                      | _                  | _    | 0.45                 | V    |  |

| V <sub>IH</sub>  | Input High Level         | 6V  | _                                                           | 0.7V <sub>CC</sub> | _    | V <sub>CC</sub> +0.5 | V    |  |

| V <sub>IL</sub>  | Input Low Level          | 6V  | _                                                           | -0.5               | _    | 0.8                  | V    |  |

| ILI              | Input Load Current       | 6V  | V <sub>IN</sub> =V <sub>IL</sub> , V <sub>IH</sub>          | _                  | _    | 5                    | μΑ   |  |

| V <sub>H</sub>   | A9 Product ID Voltage    | 6V  | _                                                           | 11.5               | _    | 12.5                 | V    |  |

| Icc              | VCC Supply Current       | 6V  | _                                                           | _                  | _    | 40                   | mA   |  |

| I <sub>PP</sub>  | VPP Supply Current       | 6V  | CE=V <sub>IL</sub>                                          | _                  | _    | 10                   | mA   |  |

| Capacitaı        | nce                      | '   |                                                             | -                  |      |                      |      |  |

| C <sub>IN</sub>  | Input Capacitance        | 5V  | V <sub>IN</sub> =0V                                         | _                  | 8    | 12                   | pF   |  |

| C <sub>OUT</sub> | Output Capacitance       | 5V  | V <sub>OUT</sub> =0V                                        | _                  | 8    | 12                   | pF   |  |

| C <sub>VPP</sub> | VPP Capacitance          | 5V  | V <sub>PP</sub> =0V                                         | _                  | 18   | 25                   | pF   |  |

# A.C. Characteristics

Ta=+25°C±5°C

| Ch al            | Parameter                                                                               | Test Conditions |                       | Min.    | T    | Mari | 11:4 |

|------------------|-----------------------------------------------------------------------------------------|-----------------|-----------------------|---------|------|------|------|

| Symbol           | Parameter                                                                               | Vcc             | Conditions            | IVIIII. | Тур. | Max. | Unit |

| Read operation   |                                                                                         |                 |                       |         |      |      |      |

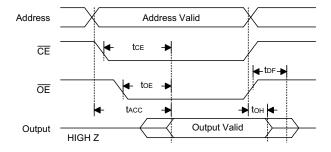

| t <sub>ACC</sub> | Address to Output Delay                                                                 | 5V              | CE=OE=V <sub>IL</sub> | _       | _    | 70   | ns   |

| t <sub>CE</sub>  | Chip Enable to Output Delay                                                             | 5V              | OE=V <sub>IL</sub>    | _       | _    | 70   | ns   |

| toE              | Output Enable to Output Delay                                                           | 5V              | CE=V <sub>IL</sub>    | _       |      | 30   | ns   |

| t <sub>DF</sub>  | CE or OE High to Output Float, Whichever Occurred First                                 | 5V              | _                     | _       | _    | 25   | ns   |

| tон              | Output Hold from Address, $\overline{CE}$ or $\overline{OE}$ , Whichever Occurred First | 5V              | _                     | 0       | _    | _    | ns   |

| Cumbal           | Damamatan                              | Т   | est Conditions | Min  | _    |      | Unit |  |

|------------------|----------------------------------------|-----|----------------|------|------|------|------|--|

| Symbol           | Parameter                              | Vcc | Conditions     | Min. | Тур. | Max. |      |  |

| Program          | Programming operation                  |     |                |      |      |      |      |  |

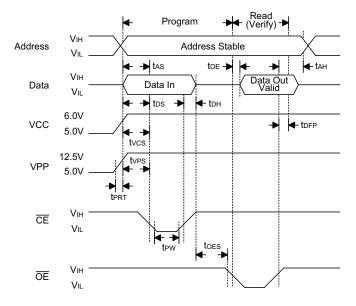

| t <sub>AS</sub>  | Address Setup Time                     | 6V  | _              | 2    | _    | _    | μS   |  |

| toes             | OE Setup Time                          | 6V  | _              | 2    | _    | _    | μS   |  |

| t <sub>DS</sub>  | Data Setup Time                        | 6V  | _              | 2    | _    | _    | μS   |  |

| t <sub>AH</sub>  | Address Hold Time                      | 6V  | _              | 0    | _    | _    | μS   |  |

| t <sub>DH</sub>  | Data Hold Time                         | 6V  | _              | 2    | _    | _    | μS   |  |

| t <sub>DFP</sub> | Output Enable to Output Float Delay    | 6V  | _              | 0    | _    | 130  | ns   |  |

| t <sub>VPS</sub> | VPP Setup Time                         | 6V  | _              | 2    | _    | _    | μS   |  |

| t <sub>PW</sub>  | CE Program Pulse Width                 | 6V  | _              | 50   | 75   | 105  | μS   |  |

| t <sub>VCS</sub> | VCC Setup Time                         | 6V  | _              | 2    | _    | _    | μS   |  |

| t <sub>CES</sub> | CE Setup Time                          | 6V  | _              | 2    | _    | _    | μS   |  |

| toE              | Data Valid from OE                     | 6V  | _              | _    | _    | 150  | ns   |  |

| t <sub>PRT</sub> | VPP Pulse Rise Time During Programming | 6V  | _              | 2    | _    | _    | μS   |  |

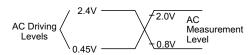

# Test waveforms and measurements

$t_{R}$ ,  $t_{F}$ < 20ns (10% to 90%)

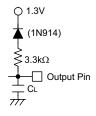

# **Output test load**

Note:  $C_L$ =100pF including jig capacitance.

# **Functional Description**

#### Programming of the HT27C4096

When the HT27C4096 is delivered, the chip has all 4096K bits in the "ONE", or HIGH state. "ZEROs" are loaded into the HT27C4096 through programming.

The programming mode is entered when 12.5 $\pm$ 0.2V is applied to the VPP pin,  $\overline{OE}$  is at V<sub>IH</sub>, and  $\overline{CE}$  is V<sub>IL</sub>. For programming, the data to be programmed is applied with 16 bits in parallel to the data pins.

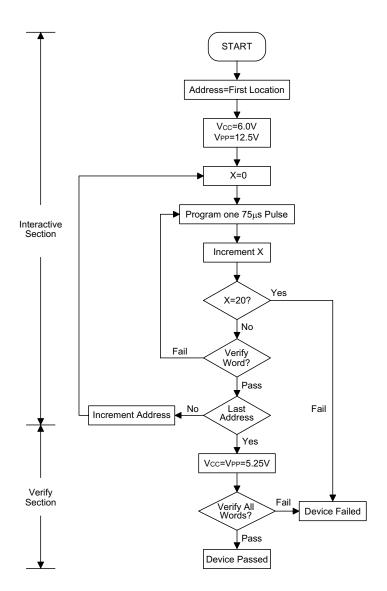

The programming flowchart in Figure 3 shows the fast interactive programming algorithm. The interactive algorithm reduces programming time by using 50 µs to 105μs programming pulses and giving each address only as many pulses as is necessary in order to reliably program the data. After each pulse is applied to a given address, the data in that address is verified. If the data is not verified, additional pulses are given until it is verified or until the maximum number of pulses is reached while sequencing through each address of the HT27C4096. This process is repeated while sequencing through each address of the HT27C4096. This part of the programming algorithm is done at V<sub>CC</sub>=6.0V to assure that each EPROM bit is programmed to a sufficiently high threshold voltage. This ensures that all bits have sufficient margin. After the final address is completed, the entire EPROM memory is read at  $V_{CC}=V_{PP}=5.25\pm0.25V$  to verify the entire memory.

#### Program inhibit mode

Programming of multiple HT27C4096 in parallel with different data is also easily accomplished by using the Program Inhibit Mode. Except for  $\overline{\text{CE}}$ , all like inputs of the parallel HT27C4096 may be common. A TTL low-level program pulse applied to an HT27C4096  $\overline{\text{CE}}$  input with Vpp=12.5±0.2V, and  $\overline{\text{OE}}$  HIGH will program that HT27C4096. A high-level  $\overline{\text{CE}}$  input inhibits the HT27C4096 from being programmed.

#### Program verify mode

Verification should be performed on the programmed bits to determine whether they were correctly programmed. The verification should be performed with  $\overline{\text{OE}}$  at  $V_{\text{IL}}$ , and  $\overline{\text{CE}}$  at  $V_{\text{IH}}$ , and VPP at its programming voltage.

#### Auto product identification

The Auto Product Identification mode allows the reading out of a binary code from an EPROM that will identify its manufacturer and the type. This mode is intended for programming to automatically match the device to be programmed with its corresponding programming algorithm. This mode is functional in the 25°C±5°C ambient temperature range that is required when programming the HT27C4096.

To activate this mode, the programming equipment must force  $12.0\pm0.5V$  on the address line A9 of the HT27C4096. Two identifier bytes may then be sequenced from the device outputs by toggling address line A0 from  $V_{IL}$  to  $V_{IH}$ , when A1= $V_{IH}$ . All other address lines must be held at  $V_{IH}$  during Auto Product Identification mode.

Byte 0 (A0= $V_{IL}$ ) represents the manufacturer code, and byte 1 (A0= $V_{IH}$ ), the device code. For HT27C4096, these two identifier bytes are given in the Operation mode truth table. When A1= $V_{IL}$ , the HT27C4096 will read out the binary code of 7F, continuation code, to signify the unavailability of manufacturer ID codes.

#### Read mode

The HT27C4096 has two control functions, both of which must be logically satisfied in order to obtain data at outputs. Chip Enable  $(\overline{CE})$  is the power control and should be used for device selection. Output Enable  $(\overline{OE})$  is the output control and should be used to gate data to the output pins, independent of device selection. Assuming that addresses are stable, address access time  $(t_{ACC})$  is equal to the delay from  $\overline{CE}$  to output  $(t_{CE})$ . Data is available at the outputs  $(t_{OE})$  after the falling edge of  $\overline{OE}$ , assuming the  $\overline{CE}$  has been LOW and addresses have been stable for at least  $t_{ACC}$ -to-E.

#### Standby mode

The HT27C4096 has CMOS standby mode which reduces the maximum  $V_{CC}$  current to  $10\mu A.$  It is placed in CMOS standby when  $\overline{CE}$  is at  $V_{CC}\pm 0.3V.$  The HT27C4096 also has a TTL-standby mode which reduces the maximum  $V_{CC}$  current to 1.0mA. It is placed in TTL-standby when  $\overline{CE}$  is at  $V_{IH}.$  When in standby mode, the outputs are in a high-impedance state, independent of the  $\overline{OE}$  input.

#### Two-line output control function

To accommodate multiple memory connections, a two-line control function is provided to allow for:

- Low memory power dissipation

- Assurance that output bus contention will not occur

It is recommended that  $\overline{CE}$  be decoded and used as the primary device-selection function, while  $\overline{OE}$  be made a common connection to the READ line from the system control bus. This assures that all deselected memory devices are in their low-power standby mode and that the output pins are only active when data is desired from a particular memory device.

#### System considerations

During the switch between active and standby conditions, transient current peaks are produced on the rising and falling edges of Chip Enable. The magnitude of

Rev. 1.10 5 November 21, 2002

these transient current peaks is dependent on the output capacitance loading of the device. At a minimum, a 0.1  $\mu F$  ceramic capacitor (high frequency, low inherent inductance) should be used on each device between VCC and VPP to minimize transient effects. In addition, to overcome the voltage drop caused by the inductive

effects of the printed circuit board traces on EPROM arrays, a  $4.7\mu\text{F}$  bulk electrolytic capacitor should be used between VCC and VPP for each eight devices. The location of the capacitor should be close to where the power supply is connected to the array.

#### Operation mode truth table

All the operation modes are shown in the table following.

| Mode                  | CE                     | OE              | A0              | A1              | A9                 | VPP             | Output           |

|-----------------------|------------------------|-----------------|-----------------|-----------------|--------------------|-----------------|------------------|

| Read                  | V <sub>IL</sub>        | V <sub>IL</sub> | Х               | Х               | Х                  | V <sub>CC</sub> | Dout             |

| Output Disable        | V <sub>IL</sub>        | V <sub>IH</sub> | Х               | Х               | Х                  | V <sub>CC</sub> | High Z           |

| Standby (TTL)         | V <sub>IH</sub>        | Х               | Х               | Х               | Х                  | V <sub>CC</sub> | High Z           |

| Standby (CMOS)        | V <sub>CC</sub> ± 0.3V | X               | X               | X               | X                  | V <sub>CC</sub> | High Z           |

| Program               | V <sub>IL</sub>        | V <sub>IH</sub> | Х               | Х               | Х                  | $V_{PP}$        | D <sub>IN</sub>  |

| Program Verify        | X                      | V <sub>IL</sub> | Х               | Х               | Х                  | $V_{PP}$        | D <sub>OUT</sub> |

| Product Inhibit       | V <sub>IH</sub>        | X               | Х               | X               | Х                  | V <sub>PP</sub> | High Z           |

| Manufacturer Code (3) | V <sub>IL</sub>        | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>H</sub> (1) | V <sub>CC</sub> | 1C               |

| Device Type Code (3)  | V <sub>IL</sub>        | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>H</sub> (1) | V <sub>CC</sub> | 05               |

Note: (1)  $V_H = 12.0V \pm 0.5V$

(2) X=Either  $V_{IH}$  or  $V_{IL}$

(3) For Manufacturer Code and Device Code, A1=V<sub>IH</sub>, When A1=V<sub>IL</sub>, both codes will read 7F

#### **Product Identification Code**

| Code                | Pins |            |     |     |     |     |     |     |     | Hex |      |

|---------------------|------|------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| Code                | A0   | <b>A</b> 1 | DQ7 | DQ6 | DQ5 | DQ4 | DQ3 | DQ2 | DQ1 | DQ0 | Data |

| Manufacturer        | 0    | 1          | 0   | 0   | 0   | 1   | 1   | 1   | 0   | 0   | 1C   |

| Device Type         | 1    | 1          | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 1   | 05   |

| O and in a set in a | 0    | 0          | 0   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 7F   |

| Continuation        | 1    | 0          | 0   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 7F   |

Figure 1. A.C. waveforms for read operation

Rev. 1.10 6 November 21, 2002

Figure 2. Programming waveforms

Rev. 1.10 7 November 21, 2002

Figure 3. Fast programming flowchart

Rev. 1.10 8 November 21, 2002

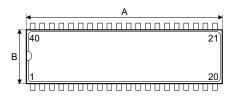

# **Package Information**

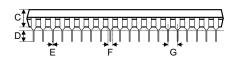

40-pin DIP (600mil) outline dimensions

| Symbol | Dimensions in mil |      |      |  |  |  |

|--------|-------------------|------|------|--|--|--|

| Symbol | Min.              | Nom. | Max. |  |  |  |

| А      | 2045              | _    | 2065 |  |  |  |

| В      | 535               | _    | 555  |  |  |  |

| С      | 145               | _    | 155  |  |  |  |

| D      | 125               | _    | 145  |  |  |  |

| E      | 16                | _    | 20   |  |  |  |

| F      | 50                | _    | 70   |  |  |  |

| G      | _                 | 100  | _    |  |  |  |

| Н      | 595               | _    | 615  |  |  |  |

| 1      | 635               | _    | 670  |  |  |  |

| α      | 0°                | _    | 15°  |  |  |  |

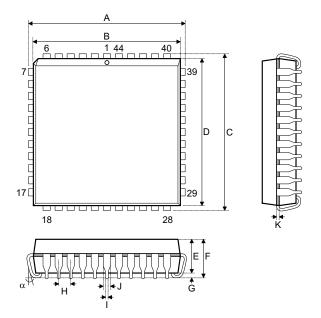

# 44-pin PLCC outline dimensions

| Combal | Dimensions in mil |      |      |  |  |  |  |

|--------|-------------------|------|------|--|--|--|--|

| Symbol | Min.              | Nom. | Max. |  |  |  |  |

| Α      | 680               | _    | 700  |  |  |  |  |

| В      | 648               | _    | 658  |  |  |  |  |

| С      | 680               | _    | 700  |  |  |  |  |

| D      | 648               | _    | 658  |  |  |  |  |

| E      | 145               | _    | 155  |  |  |  |  |

| F      | _                 | _    | 190  |  |  |  |  |

| G      | 20                | _    | _    |  |  |  |  |

| Н      | _                 | 50   | _    |  |  |  |  |

| I      | 16                | _    | 22   |  |  |  |  |

| J      | 24                | _    | 32   |  |  |  |  |

| K      | 8                 | _    | 12   |  |  |  |  |

| α      | 0°                | _    | 10°  |  |  |  |  |

# **Product Tape and Reel Specifications**

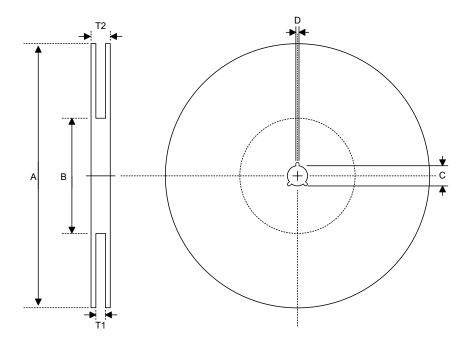

# Reel dimensions

PLCC 44

| Symbol | Description           | Dimensions in mm |

|--------|-----------------------|------------------|

| Α      | Reel Outer Diameter   | 330±1.0          |

| В      | Reel Inner Diameter   | 100±0.1          |

| С      | Spindle Hole Diameter | 13.0+0.5<br>-0.2 |

| D      | Key Slit Width        | 2.0±0.5          |

| T1     | Space Between Flange  | 32.8+0.3<br>-0.2 |

| T2     | Reel Thickness        | 38.2±0.2         |

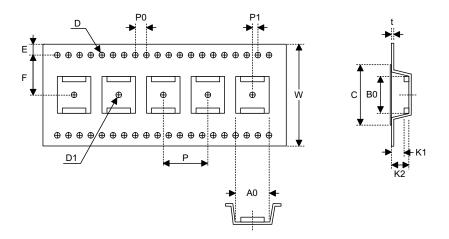

# Carrier tape dimensions

PLCC 44

| Symbol | Description                              | Dimensions in mm |

|--------|------------------------------------------|------------------|

| W      | Carrier Tape Width                       | 32.0±0.3         |

| Р      | Cavity Pitch                             | 24.0±0.1         |

| Е      | Perforation Position                     | 1.75±0.1         |

| F      | Cavity to Perforation (Width Direction)  | 14.2±0.1         |

| D      | Perforation Diameter                     | 1.5+0.1          |

| D1     | Cavity Hole Diameter                     | 2.0 Min.         |

| P0     | Perforation Pitch                        | 4.0±0.1          |

| P1     | Cavity to Perforation (Length Direction) | 2.0±0.1          |

| A0     | Cavity Length                            | 18.0±0.1         |

| В0     | Cavity Width                             | 18.0±0.1         |

| K1     | Cavity Depth                             | NA               |

| K2     | Cavity Depth                             | 4.9±0.1          |

| t      | Carrier Tape Thickness                   | 0.33±0.05        |

| С      | Cover Tape Width                         | 21.3             |

#### Holtek Semiconductor Inc. (Headquarters)

No.3, Creation Rd. II, Science-based Industrial Park, Hsinchu, Taiwan

Tel: 886-3-563-1999 Fax: 886-3-563-1189 http://www.holtek.com.tw

# Holtek Semiconductor Inc. (Sales Office)

11F, No.576, Sec.7 Chung Hsiao E. Rd., Taipei, Taiwan

Tel: 886-2-2782-9635 Fax: 886-2-2782-9636

Fax: 886-2-2782-7128 (International sales hotline)

#### Holtek Semiconductor (Shanghai) Inc.

7th Floor, Building 2, No.889, Yi Shan Rd., Shanghai, China

Tel: 021-6485-5560 Fax: 021-6485-0313 http://www.holtek.com.cn

#### Holtek Semiconductor (Hong Kong) Ltd.

Block A, 3/F, Tin On Industrial Building, 777-779 Cheung Sha Wan Rd., Kowloon, Hong Kong Tel: 852-2-745-8288

Tel: 852-2-745-8288 Fax: 852-2-742-8657

#### Holmate Semiconductor, Inc.

46712 Fremont Blvd., Fremont, CA 94538

Tel: 510-252-9880 Fax: 510-252-9885 http://www.holmate.com

#### Copyright © 2002 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek's products are not authorized for use as critical components in life support devices or systems. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at http://www.holtek.com.tw.

Rev. 1.10 13 November 21, 2002