APPLICATION NOTE PMC-990639 PMC-Sierra, Inc.

PM7381 FREEDM-32A672

ISSUE 1

PROGRAMMER'S GUIDE

PM7381

# FREEDM<sup>TM</sup>-32A672

# FRAME ENGINE AND DATALINK MANAGER 32A672

# **PROGRAMMER'S GUIDE**

PROPRIETARY AND CONFIDENTIAL ADVANCE ISSUE 1: JUNE 1999

APPLICATION NOTE PMC-990639 PMC-Sierra, Inc.

PM7381 FREEDM-32A672

ISSUE 1

PROGRAMMER'S GUIDE

# **CONTENTS**

| 1 | INTR | INTRODUCTION1                                                 |  |  |  |  |

|---|------|---------------------------------------------------------------|--|--|--|--|

|   | 1.1  | SCOPE1                                                        |  |  |  |  |

|   | 1.2  | TARGET AUDIENCE1                                              |  |  |  |  |

|   | 1.3  | NUMBERING CONVENTIONS1                                        |  |  |  |  |

|   | 1.4  | REGISTER DESCRIPTION1                                         |  |  |  |  |

|   |      | 1.4.1 NORMAL MODE REGISTERS2                                  |  |  |  |  |

| 2 | REF  | ERENCES                                                       |  |  |  |  |

| 3 | FRE  | EDM-32A672 OVERVIEW4                                          |  |  |  |  |

|   | 3.1  | FREEDM-32A672 SUMMARY4                                        |  |  |  |  |

|   | 3.2  | ANY-PHY PACKET INTERFACE6                                     |  |  |  |  |

| 4 | INTE | RRUPT ARCHITECTURE8                                           |  |  |  |  |

| 5 | CON  | FIGURING THE SERIAL LINKS9                                    |  |  |  |  |

|   | 5.1  | CHANNELISED T1/J1 LINKS9                                      |  |  |  |  |

|   | 5.2  | CHANNELISED E1 LINKS11                                        |  |  |  |  |

|   | 5.3  | UNCHANNELISED LINKS WITH BYTE SYNCHRONIZATION 12              |  |  |  |  |

|   | 5.4  | UNCHANNELISED LINKS WITHOUT SYNCHRONIZATION14                 |  |  |  |  |

|   | 5.5  | 8.192 MBPS H-MVIP LINKS16                                     |  |  |  |  |

|   | 5.6  | 2.048 MBPS H-MVIP LINKS18                                     |  |  |  |  |

| 6 | CON  | FIGURING THE ANY-PHY PACKET INTERFACE                         |  |  |  |  |

|   | 6.1  | CONFIGURING THE RECEIVE ANY-PHY PACKET INTERFACE (RAPI672)    |  |  |  |  |

|   | 6.2  | CONFIGURING THE TRANSMIT ANY-PHY PACKET INTERFACE (TAPI672)23 |  |  |  |  |

PM7381 FREEDM-32A672

| APPLICATION NOTE<br>PMC-990639 |      | ISSUE 1                                                          | PROGRAMMER'S GUIDE |

|--------------------------------|------|------------------------------------------------------------------|--------------------|

| 7                              | HDLC | AND CHANNEL FIFO CONFIGURATION                                   |                    |

|                                | 7.1  | CONFIGURING THE RHDL672                                          | 26                 |

|                                | 7.2  | CONFIGURING THE THDL672                                          | 27                 |

|                                | 7.3  | PROGRAMMING A CHANNEL FIFO                                       | 28                 |

|                                |      | 7.3.1 RECEIVE CHANNEL FIFO                                       | 29                 |

|                                |      | 7.3.2 TRANSMIT CHANNEL FIFO                                      |                    |

|                                | 7.4  | RHDL672 CHANNEL CONFIGURATION                                    | 31                 |

|                                | 7.5  | THDL672 CHANNEL CONFIGURATION                                    | 34                 |

| 8                              | FREE | DM-32A672 OPERATIONAL PROCEDURES                                 | 40                 |

|                                | 8.1  | DEVICE IDENTIFICATION, LOCATION AND SYSTE<br>RESOURCE ASSIGNMENT |                    |

|                                | 8.2  | RESET                                                            | 40                 |

|                                | 8.3  | INITIALIZATION                                                   | 41                 |

|                                | 8.4  | ACTIVATION PROCEDURE                                             | 41                 |

|                                | 8.5  | DEACTIVATION PROCEDURE                                           | 42                 |

|                                | 8.6  | PROVISIONING A CHANNEL                                           | 43                 |

|                                |      | 8.6.1 RECEIVE CHANNEL PROVISIONING                               | 43                 |

|                                |      | 8.6.2 TRANSMIT CHANNEL PROVISIONING                              | 45                 |

|                                | 8.7  | UNPROVISIONING A CHANNEL                                         | 48                 |

|                                |      | 8.7.1 RECEIVE CHANNEL UNPROVISIONING                             | 48                 |

|                                |      | 8.7.2 TRANSMIT CHANNEL UNPROVISIONING                            | 50                 |

|                                | 8.8  | RECEIVE SEQUENCE                                                 | 53                 |

|                                | 8.9  | TRANSMIT SEQUENCE                                                | 53                 |

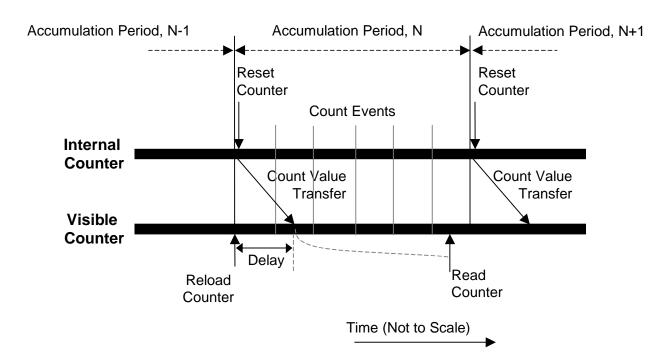

|                                | 8.10 | PERFORMANCE COUNTERS                                             | 54                 |

APPLICATION NOTE PMC-990639

ISSUE 1

| PROGRAMMER'S C | SUIDE |

|----------------|-------|

| 8.11       | LINE LOOPBACK                          | 56 |

|------------|----------------------------------------|----|

| 8.12       | DIAGNOSTIC LOOPBACK                    | 57 |

| 8.13       | BERT PORT                              | 57 |

| APPENDIX A | - REGISTER LEVEL CHANGES               | 59 |

| APPENDIX B | - NEW NORMAL MODE REGISTERS            | 66 |

| APPENDIX C | - NON-APPLICABLE NORMAL MODE REGISTERS | 67 |

| APPENDIX D | - NORMAL MODE REGISTER BIT CHANGES     | 39 |

APPLICATION NOTE PMC-990639 PMC-Sierra, Inc.

PM7381 FREEDM-32A672

ISSUE 1

PROGRAMMER'S GUIDE

# LIST OF FIGURES

| FIGURE 1 – FREEDM-32A672 BLOCK DIAGRAM                                     | 5    |

|----------------------------------------------------------------------------|------|

| FIGURE 2 – CHANNELISED T1/J1 RECEIVE LINK TIMING                           | 9    |

| FIGURE 3 – CHANNELISED T1/J1 TRANSMIT LINK TIMING                          | .10  |

| FIGURE 4 – CHANNELISED E1 RECEIVE LINK TIMING                              | .11  |

| FIGURE 5 – CHANNELISED E1 TRANSMIT LINK TIMING                             | . 11 |

| FIGURE 6 – UNCHANNELISED RECEIVE LINK TIMING WITH BYTE<br>SYNCHRONIZATION  | .13  |

| FIGURE 7 – UNCHANNELISED TRANSMIT LINK TIMING WITH BYTE<br>SYNCHRONIZATION | .13  |

| FIGURE 8 – UNCHANNELISED RECEIVE LINK TIMING WITHOUT<br>SYNCHRONIZATION    | .14  |

| FIGURE 9 – UNCHANNELISED TRANSMIT LINK TIMING WITHOUT<br>SYNCHRONIZATION   | . 15 |

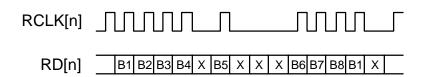

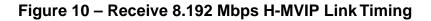

| FIGURE 10 – RECEIVE 8.192 MBPS H-MVIP LINK TIMING                          | .16  |

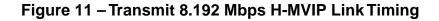

| FIGURE 11 – TRANSMIT 8.192 MBPS H-MVIP LINK TIMING                         | .17  |

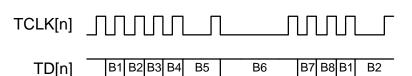

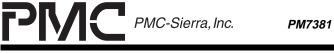

| FIGURE 12 – RECEIVE 2.048 MBPS H-MVIP LINK TIMING                          | .19  |

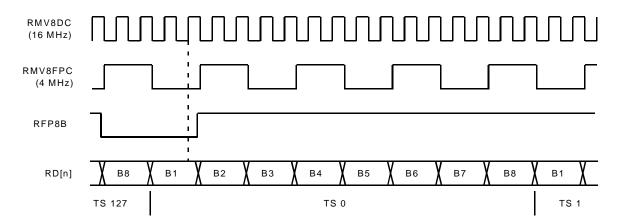

| FIGURE 13 – TRANSMIT 2.048 MBPS H-MVIP LINK TIMING                         | .19  |

| FIGURE 14 – SPECIFYING A CHANNEL FIFO                                      | .29  |

| FIGURE 15 – EVENT SEQUENCE FOR POLLING OF COUNTERS                         | .54  |

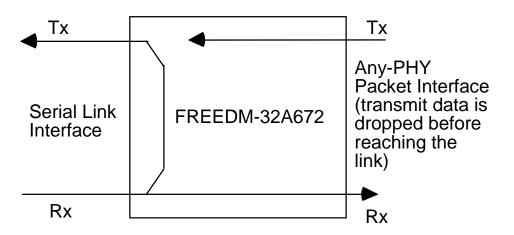

| FIGURE 16 – LINE LOOPBACK                                                  | .56  |

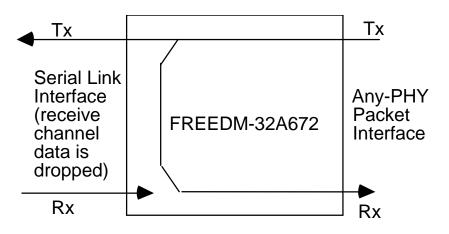

| FIGURE 17 – DIAGNOSTIC LOOPBACK                                            | .57  |

PMC PMC-Sierra, Inc.

ra, inc. **PN**

PM7381 FREEDM-32A672

ISSUE 1

PROGRAMMER'S GUIDE

#### 1 INTRODUCTION

#### 1.1 Scope

The FREEDM-32A672 Programmer's Guide is intended to describe the configurable features and operation of a FREEDM-32A672 from a programmer's perspective. This document may not cover all applications of the FREEDM-32A672. Please contact a PMC-Sierra Applications Engineer for specific uses not covered in this document.

This document is a supplement to the FREEDM-32A672 Longform Datasheet[1]. Both documents should be studied together to interface the FREEDM-32A672 to an embedded processor. In case of a discrepancy between the Programmer's Guide and the Longform Datasheet, the Longform Datasheet shall always be considered correct.

#### 1.2 Target Audience

The target audience for this document is programmers who will be writing software to configure and control the FREEDM-32A672.

This document has been prepared for readers with some prior knowledge of the HDLC protocol.

#### **<u>1.3 Numbering Conventions</u>**

The following numbering conventions are used throughout this document:

| binary      | 011 1010B, 011 |

|-------------|----------------|

| decimal     | 129, 6, 12     |

| hexadecimal | 0x1FE2, 09FH   |

#### 1.4 Register Description

Unless specified otherwise, FREEDM-32A672 registers are described using the convention **REGISTER\_NAME** (address in FREEDM-32A672). There is only one register space that can be addressed on a FREEDM-32A672, and it consists of the normal mode microprocessor accessible registers.

APPLICATION NOTE PMC-990639

PROGRAMMER'S GUIDE

## 1.4.1 Normal Mode Registers

ISSUE 1

Normal mode registers are used to configure, monitor and control the operation of the FREEDM-32A672. Registers must be accessed as 16-bit values with a DWORD aligned address. For all register descriptions, the hexadecimal register number indicates the address in the FREEDM-32A672 when accesses are made using the external microprocessor. A register value is accessed through an external microprocessor, and has the following characteristics:

- Writing values into unused register bits has no effect. However, to ensure software compatibility with future versions of the product, unused register bits should be written with logic zero. Reading back unused bits can produce either a logic one or a logic zero; hence, unused register bits should be masked off by software when read.

- Except where noted, all configuration bits that can be written into can also be read back. This allows the processor controlling the FREEDM-32A672 to determine the programming state of the block.

- Writable normal mode registers are cleared to logic zero upon reset unless otherwise noted.

- Writing into read-only normal mode register bit locations does not affect FREEDM-32A672 operation unless otherwise noted.

- Certain register bits are reserved. These bits are associated with megacell functions that are unused in this application. To ensure that the FREEDM-32A672 operates as intended, reserved register bits must only be written with their default values. Similarly, writing to reserved registers should be avoided.

APPLICATION NOTE PMC-990639 PMC PMC-Sierra, Inc.

PM7381 FREEDM-32A672

ISSUE 1

PROGRAMMER'S GUIDE

#### 2 REFERENCES

- 1. PMC-990263, PMC-Sierra, Inc., "Frame Engine and Data Link Manager 32A672" Longform Datasheet, February 1999, Issue 1.

- 2. PMC-990262, PMC-Sierra, Inc., "Frame Engine and Data Link Manager 32P672" Longform Datasheet, February 1999, Issue 1.

- 3. PMC-960758, PMC-Sierra, Inc., "Frame Engine and Data Link Manager" Longform Datasheet, May 1998, Issue 5.

APPLICATION NOTE PMC-990639

PM7381 FREEDM-32A672

ISSUE 1

PROGRAMMER'S GUIDE

## 3 FREEDM-32A672 OVERVIEW

#### 3.1 FREEDM-32A672 Summary

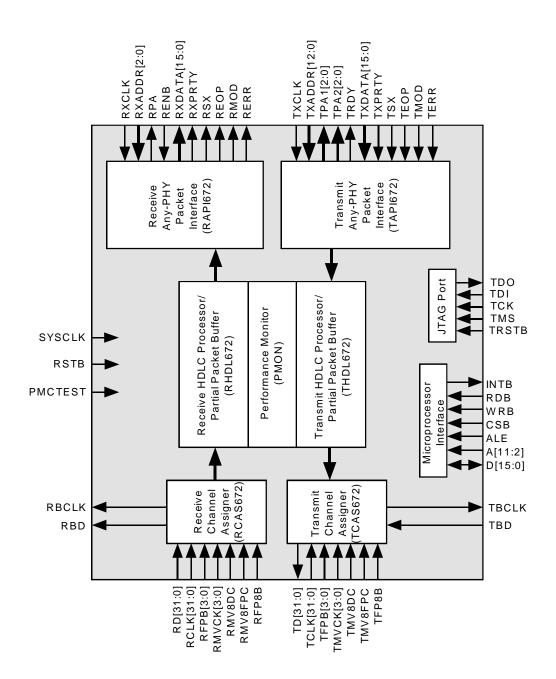

The PM7381 FREEDM-32A672 Frame Engine and Datalink Manager is an advanced data link layer processor that is ideal for applications such as IETF PPP interfaces for routers, TDM switches, Frame Relay switches and multiplexors, ATM switches and multiplexors, Internet/Intranet access equipment, packet-based DSLAM equipment, and Packet over SONET. The FREEDM-32A672 implements HDLC processing for a maximum of 672 bi-directional channels. The functional blocks of the FREEDM-32A672 are illustrated in Figure 1.

As many as 32 bi-directional serial links can be connected to the FREEDM-32A672. These are processed by the Receive Channel Assigner (RCAS672) and Transmit Channel Assigner (TCAS672) blocks. The RCAS672 and TCAS672 can be interfaced to H-MVIP, channelised T1/J1/E1, or unchannelised links.

The data stream at each serial port can be assigned to one or more of the FREEDM-32A672 channels. There are as many as 672 receive channels and 672 transmit channels available for assignment to unchannelised links, or to time-slots within a channelised T1/J1/E1 or H-MVIP link.

When configured for 2.048 Mbps H-MVIP operation, the FREEDM-32A672 partitions the 32 physical links into 4 logical groups of 8 links. Links in each logical group share a common clock and a common type 0 frame pulse in each direction.

When configured for 8.192 Mbps H-MVIP operation, the FREEDM-32A672 partitions the 32 physical links into 8 logical groups of 4 links. All links configured for 8.192 Mbps H-MVIP operation will share a common type 0 frame pulse, a common frame pulse clock and a common data clock.

For channelised T1/J1/E1 links, the FREEDM-32A672 allows up to 672 bidirectional HDLC channels to be assigned to individual time-slots within a maximum of 32 independently timed T1/J1/E1 links.

For unchannelised links, the FREEDM-32A672 processes up to 32 bi-directional HDLC channels within 32 independently timed links.

Each data stream can be HDLC processed on a channelised basis within the Receive HDLC Processor / Partial Packet Buffer (RHDL672) and Transmit HDLC Processor / Partial Packet Buffer (THDL672). There is a 32 Kbyte buffer in the

ISSUE 1

PROGRAMMER'S GUIDE

RHDL672 and another 32 Kbyte buffer in the THDL672 that must be assigned to FREEDM-32A672 channels to serve as channel FIFO's. Each buffer is a group of 2048 blocks with 16 bytes per block, and a minimum of 3 blocks must be assigned to a channel during provisioning. This allows for flexible assignment of a channel FIFO based on the expected data rate for the channel.

## Figure 1 – FREEDM-32A672 Block Diagram

APPLICATION NOTE PMC-990639

PM7381 FREEDM-32A672

ISSUE 1

PROGRAMMER'S GUIDE

Alternatively, the RHDL672 and THDL672 can provision a channel as transparent, in which case, the raw data stream is transferred without HDLC processing.

The Receive Any-PHY Interface (RAPI672) provides a low latency path for transferring data out of the partial packet buffer in the RHDL672 and onto the Receive Any-PHY Packet Interface (Rx APPI). The RAPI672 contains a FIFO block for latency control as well as to segregate the APPI timing domain from the SYSCLK timing domain. The RAPI672 contains the necessary logic to manage and respond to device polling from an upper layer device. The RAPI672 also provides the upper layer device with status information on a per packet basis.

The Transmit Any-PHY Interface (TAPI672) provides a low latency path for transferring data from the Transmit Any-PHY Packet Interface (Tx APPI) into the partial packet buffer in the THDL672. The TAPI672 contains a FIFO block for latency control as well as to segregate the APPI timing domain from the SYSCLK timing domain. The TAPI672 contains the necessary logic to manage and respond to channel polling from an upper layer device.

The PMON block provides performance monitor counts for a number of events. These counters can be read via the microprocessor interface and provides a means for the host software to accumulate performance statistics.

Channelised T1/J1/E1 and unchannelised links can be individually placed in line loopback. In addition to the line loopback capability, the FREEDM-32A672 provides a BERT port for attachment to BERT hardware. Under software control this port can be connected to any one of the 32 bi-directional links for additional diagnostic testing. The line loopback and BERT features are not supported for H-MVIP links. Finally, there is an internal diagnostic loopback configuration for each channel which can be used to diagnose FREEDM-32A672 operation on a per channel basis.

### 3.2 Any-PHY Packet Interface

The FREEDM-32A672 provides a low latency "Any-PHY" Packet Interface (APPI) to allow an external controller direct access into the 32 Kbyte partial packet buffers. Up to seven FREEDM-32A672 devices may share a single APPI. For each of the transmit and receive APPI, the external controller is the master of each FREEDM-32A672 device sharing the APPI from the point of view of device selection. The external controller is also the master for channel selection in the transmit direction. In the receive direction, however, each FREEDM-32A672 device retains control over selection of its respective channels. The transmit and receive APPI is made up of three groups of functional signals – polling, selection

APPLICATION NOTE PMC-990639

PM7381 FREEDM-32A672

ISSUE 1

PROGRAMMER'S GUIDE

and data transfer. The polling signals are used by the external controller to interrogate the status of the transmit and receive 32 Kbyte partial packet buffers. The selection signals are used by the external controller to select a FREEDM-32A672 device, or a channel within a FREEDM-32A672 device, for data transfer. The data transfer signals provide a means of transferring data across the APPI between the external controller and a FREEDM-32A672 device.

In the receive direction, polling and selection are done at the device level. Polling is not decoupled from selection, as the receive address pins serve as both a device poll address and to select a FREEDM-32A672 device. In response to a positive poll, the external controller may select that FREEDM-32A672 device for data transfer. Once selected, the FREEDM-32A672 prepends an in-band channel address to each partial packet transfer across the receive APPI to associate the data with a channel. A FREEDM-32A672 must not be selected after a negative poll response.

In the transmit direction, polling is done at the channel level. Polling is completely decoupled from selection. To increase the polling bandwidth, up to two channels may be polled simultaneously. The polling engine in the external controller runs independently of other activity on the transmit APPI. In response to a positive poll, the external controller may commence partial packet data transfer across the transmit APPI for the successfully polled channel of a FREEDM-32A672 device. The external controller must prepend an in-band channel address to each partial packet transfer across the transmit APPI to associate the data with a channel.

Detailed information on configuring the RAPI672 and the TAPI672 can be found in section 6 of this document.

PM7381 FREEDM-32A672

ISSUE 1

PROGRAMMER'S GUIDE

## 4 INTERRUPT ARCHITECTURE

This section provides an overview of the FREEDM-32A672 interrupt architecture. Detailed information on the individual interrupts is available in the Longform Datasheet[1].

The FREEDM-32A672 provides a number of individual interrupts which are identified as 'I' bits within the **FREEDM-32A672 Master Interrupt Status** (0x008) register. When an interrupt source becomes active, the 'I' bit is set and remains set until the **FREEDM-32A672 Master Interrupt Status** (0x008) register is read.

The FREEDM-32A672 provides interrupts to the microprocessor via the INTB pin of the FREEDM-32A672. The INTB pin is gated by the **FREEDM-32A672 Master Interrupt Enable** (0x004) register. This register contains 'E' bits which can mask the 'I' bit from causing an interrupt on the INTB pin of the FREEDM-32A672. When the 'E' and 'I' bits of an interrupt source are both high, then the INTB pin is active. When the 'E' bit is low, the interrupt source will not activate the INTB pin, regardless of the 'I' bit status. However, the 'I' bit remains valid when interrupts are disabled and may be polled to detect the various events.

| 'E' Bit | ʻl' Bit | Description                   |

|---------|---------|-------------------------------|

| RFCSEE  | RFCSEI  | Receive FCS Error             |

| RABRTE  | RABRTI  | Receive Abort                 |

| RPFEE   | RPFEI   | Receive Packet Format Error   |

| RFOVRE  | RFOVRI  | Receive FIFO Overrun Error    |

| TPRTYE  | TPRTYI  | Transmit Parity Error         |

| TUNPVE  | TUNPVI  | Transmit Unprovisioned Error  |

| TFOVRE  | TFOVRI  | Transmit FIFO Overflow Error  |

| TFUDRE  | TFUDRI  | Transmit FIFO Underflow Error |

The complete list of 'I' bits and 'E' bits is shown below:

APPLICATION NOTE PMC-990639

PM7381 FREEDM-32A672

ISSUE 1

PROGRAMMER'S GUIDE

## 5 CONFIGURING THE SERIAL LINKS

Each of the 32-bidirectional links is controlled via the RCAS672 and the TCAS672 blocks of the FREEDM-32A672. The RCAS672 controls the receive data stream while the TCAS672 controls the transmit data stream.

The RCAS672 extracts data bits from each of 32 receive links, based on the link configuration specified in the Normal Mode Register Space. The RCAS672 can align data to a link's gapped clock in channelised mode, extract unaligned data in unchannelised mode, or extract byte synchronized data in unchannelised mode.

The TCAS672 sources data bits onto each of 32 transmit links, based on the link configuration specified in the Normal Mode Register Space. The TCAS672 can provide data aligned to a link's gapped clock in channelised mode, provide unaligned data in unchannelised mode, or provide byte synchronized data in unchannelised mode.

Each of the serial link configurations is discussed separately in the following sections.

### 5.1 Channelised T1/J1 Links

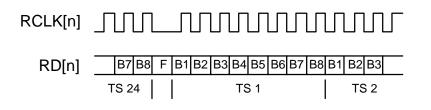

The receive bit stream is input on RD[n], and the RCLK[n] input is a 1.544 MHz clock that provides bit timing. The clock is gapped to align time-slot 1 of the channelised T1/J1 receive link (see Figure 2).

The transmit bit stream is output on TD[n], and the TCLK[n] input is a 1.544 MHz clock that provides bit timing. The clock is gapped to align time-slot 1 of the channelised T1/J1 transmit link (see Figure 3).

In each direction, transmit or receive, a T1/J1 frame consists of 24 time-slots or bytes which are mapped to one or more channels of the FREEDM-32A672. The data stream of each direction is processed and clocked independently.

### Figure 2 – Channelised T1/J1 Receive Link Timing

APPLICATION NOTE PMC-990639 PMC PMC-Sierra, Inc.

PM7381 FREEDM-32A672

ISSUE 1

PROGRAMMER'S GUIDE

## Figure 3 – Channelised T1/J1 Transmit Link Timing

To configure the RCAS672 and TCAS672 to interface to channelised T1/J1 links, the following bits are written:

| Bit         | Register                                   | Value |

|-------------|--------------------------------------------|-------|

| MODE[2:0]   | RCAS Link #n Configuration (0x180 – 0x1FC) | 001   |

| BSYNC       | RCAS Link #n Configuration (0x180 – 0x188) | Х     |

| FTHRES[6:0] | RCAS Framing Bit Threshold (0x108)         | 0x25  |

| MODE[2:0]   | TCAS Link #n Configuration (0x480 – 0x4FC) | 001   |

| BSYNC       | TCAS Link #n Configuration (0x480 – 0x488) | Х     |

| FTHRES[6:0] | TCAS Framing Bit Threshold (0x408)         | 0x25  |

| FDATA[7:0]  | TCAS Idle Time-slot Fill Data (0x40C)      | 0xFF  |

#### Notes:

- The **RCAS Link #n Configuration** register must be chosen from the range 0x180 through 0x1FC corresponding to the link being configured for channelised T1/J1 operation. The BSYNC bit is present only in registers with  $0 \le n \le 2$ . The BSYNC value is ignored for the channelised mode of operation.

- The **TCAS Link #n Configuration** register must be chosen from the range 0x480 through 0x4FC corresponding to the link being configured for channelised T1/J1 operation. The BSYNC bit is present only in registers with  $0 \le n \le 2$ . The BSYNC value is ignored for the channelised mode of operation.

- The FTHRES[6:0] value assumes a SYSCLK of 40Mhz. For other values of SYSCLK the framing threshold value is  $1.5 * f_{_{SYSCLK}} / 1.544$  MHz. (This value ensures that the threshold is suitable for T1/J1 and E1 links).

- The FDATA[7:0] bits of the TCAS Idle Time-slot Fill Data (0x40C) register, and the FTHRES[6:0] bits of the RCAS Framing Bit Threshold (0x108) / TCAS Framing Bit Threshold (0x408) registers, affect all links of a

ISSUE 1

PROGRAMMER'S GUIDE

FREEDM-32A672. The programmer should ensure that these values are suitable for all links attached to a FREEDM-32A672.

## 5.2 Channelised E1 Links

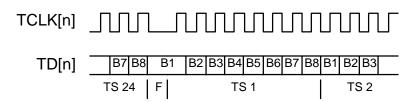

The receive bit stream is input on RD[n], and the RCLK[n] input is a 2.048 MHz clock that provides bit timing. The clock is gapped to align time-slot 1 of the channelised E1 receive link (see Figure 4).

The transmit bit stream is output on TD[n], and the TCLK[n] input is a 2.048 MHz clock that provides bit timing. The clock is gapped to align time-slot 1 of the channelised E1 transmit link (see Figure 5).

In each direction, transmit or receive, an E1 frame consists of 31 time-slots or bytes which are mapped to one or more channels of the FREEDM-32A672. The data stream of each direction is processed and clocked independently.

## Figure 4 – Channelised E1 Receive Link Timing

# Figure 5 – Channelised E1 Transmit Link Timing

| TCLK[n] |          |            |                                  |  |  |  |  |

|---------|----------|------------|----------------------------------|--|--|--|--|

| TD[n]   | B6 B7 B8 | B1         | B2 B3 B4 B5 B6 B7 B8 B1 B2 B3 B4 |  |  |  |  |

|         | TS 31    | FAS / NFAS | TS 1 TS 2                        |  |  |  |  |

To configure the RCAS672 and TCAS672 to interface to channelised E1 links, the following bits are written:

| Bit         | Register                                   | Value |

|-------------|--------------------------------------------|-------|

| MODE[2:0]   | RCAS Link #n Configuration (0x180 – 0x1FC) | 010   |

| BSYNC       | RCAS Link #n Configuration (0x180 – 0x188) | Х     |

| FTHRES[6:0] | RCAS Framing Bit Threshold (0x108)         | 0x25  |

APPLICATION NOTE PMC-990639

15

PM7381 FREEDM-32A672

PROGRAMMER'S GUIDE

| Bit         | Register                                   | Value |

|-------------|--------------------------------------------|-------|

| MODE[2:0]   | TCAS Link #n Configuration (0x480 – 0x4FC) | 010   |

| BSYNC       | TCAS Link #n Configuration (0x480 – 0x488) | Х     |

| FTHRES[6:0] | TCAS Framing Bit Threshold (0x408)         | 0x25  |

| FDATA[7:0]  | TCAS Idle Time-slot Fill Data (0x40C)      | 0xFF  |

PMC-Sierra, Inc.

#### Notes:

- The RCAS Link #n Configuration register must be chosen from the range 0x180 through 0x1FC corresponding to the link being configured for channelised E1 operation. The BSYNC bit is present only in registers with 0 ≤ n ≤ 2. The BSYNC value is ignored for the channelised mode of operation.

- The **TCAS Link #n Configuration** register must be chosen from the range 0x480 through 0x4FC corresponding to the link being configured for channelised E1 operation. The BSYNC bit is present only in registers with  $0 \le n \le 2$ . The BSYNC value is ignored for the channelised mode of operation.

- Since channelised E1 links have a framing byte, its gap will always be longer than the gap for the T1/J1 framing bit. Therefore, the same FTHRES[6:0] value of 0x25 can be used. The FTHRES[6:0] value assumes a SYSCLK of 40Mhz. For other values of SYSCLK the framing threshold value is 1.5 \* f<sub>SYSCLK</sub> / 1.544 MHz. (This value ensures the threshold is suitable for T1/J1 and E1 links).

- The FDATA[7:0] bits of the TCAS Idle Time-slot Fill Data (0x40C) register, and the FTHRES[6:0] bits of the RCAS Framing Bit Threshold (0x108) / TCAS Framing Bit Threshold (0x408) registers, affect all links of a FREEDM-32A672. The programmer should ensure that these values are suitable for all links attached to a FREEDM-32A672.

### 5.3 Unchannelised Links with Byte Synchronization

The bit stream of the unchannelised receive link that is attached to the RD[n] input is sampled on rising edges of the RCLK[n] input (see Figure 6). The receive data is byte aligned to the gapped RCLK[n] input, with the most significant bit of the byte clocked in following the gap.

The unchannelised transmit link is attached to the TD[n] output and is driven on falling edges of the TCLK[n] input (see Figure 7). The transmit data is byte

ISSUE 1

PROGRAMMER'S GUIDE

aligned to the gapped TCLK[n] input, with the most significant bit of the byte clocked out during the gap.

This mode of operation is only available for links 0 through 2 of a FREEDM-32A672.

In each direction, transmit or receive, the data stream is processed and clocked independently.

## Figure 6 – Unchannelised Receive Link Timing with Byte Synchronization

| o`ihxåz= |             |  | <br> |                                               | ՄՄ      |          |          |

|----------|-------------|--|------|-----------------------------------------------|---------|----------|----------|

| 0        |             |  | <br> | , <u>, , , , , , , , , , , , , , , , , , </u> |         |          |          |

| oaxaz=   | B5 B6 B7 B8 |  |      | B1 B2 B3 B                                    | 4 B5 B6 | B7 B8 B1 | B2 B3 B4 |

## Figure 7 – Unchannelised Transmit Link Timing with Byte Synchronization

| TCLK[n] |       |      | Γ     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | [ ] |    |    |

|---------|-------|------|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|----|----|

| TD[n]   | B5 B6 | B7 E | 38 B1 | B2 | B3 | B4 | B5 | B6 | B7 | B8 | B1 | B2  | B3 | B4 |

To configure the RCAS672 and TCAS672 to interface to byte synchronized unchannelised links, the following bits are written:

| Bit         | Register                                   | Value    |  |

|-------------|--------------------------------------------|----------|--|

| MODE[2:0]   | RCAS Link #n Configuration (0x180 – 0x1FC) | 000      |  |

| BSYNC       | RCAS Link #n Configuration (0x180 – 0x188) | 1        |  |

| FTHRES[6:0] | RCAS Framing Bit Threshold (0x108)         | see note |  |

| MODE[2:0]   | TCAS Link #n Configuration (0x480 – 0x4FC) | 000      |  |

| BSYNC       | TCAS Link #n Configuration (0x480 – 0x488) | 1        |  |

| FTHRES[6:0] | TCAS Framing Bit Threshold (0x408)         | see note |  |

| FDATA[7:0]  | TCAS Idle Time-slot Fill Data (0x40C)      | 0xFF     |  |

### Notes:

• The **RCAS Link #n Configuration** register must be chosen from the range 0x180 through 0x1FC corresponding to the link being configured. The

APPLICATION NOTE PMC-990639

ISSUE 1

PROGRAMMER'S GUIDE

unchannelised link with byte synchronization is only supported in registers with  $0 \le n \le 2$ .

- The **TCAS Link #n Configuration** register must be chosen from the range 0x480 through 0x4FC corresponding to the link being configured. The unchannelised link with byte synchronization is only supported in registers with  $0 \le n \le 2$ .

- The FTHRES[6:0] must be set based on the expected gap width of RCLK[n] or TCLK[n]. The reader should refer to the Longform Datasheet[1] on how to set this value.

- The FDATA[7:0] bits of the TCAS Idle Time-slot Fill Data (0x40C) register, and the FTHRES[6:0] bits of the RCAS Framing Bit Threshold (0x108) / TCAS Framing Bit Threshold (0x408) registers, affect all links of a FREEDM-32A672. The programmer should ensure that these values are suitable for all links attached to a FREEDM-32A672.

## 5.4 Unchannelised Links without Synchronization

The bit stream of the unchannelised receive link that is attached to the RD[n] input is sampled on rising edges of the RCLK[n] input (see Figure 8). The receive data is not aligned to the RCLK[n] input.

The unchannelised transmit link is attached to the TD[n] output and is driven on falling edges of the TCLK[n] input (see Figure 9). The transmit data is not aligned to the TCLK[n] input.

In each direction, transmit or receive, the data stream is processed and clocked independently.

# Figure 8 – Unchannelised Receive Link Timing without Synchronization

APPLICATION NOTE PMC-990639 PM7381 FREEDM-32A672

PROGRAMMER'S GUIDE

## Figure 9 – Unchannelised Transmit Link Timing without Synchronization

**ISSUE 1**

To configure the RCAS672 and TCAS672 to interface to unchannelised links without synchronization, the following bits are written:

| Bit         | Register                                   | Value |

|-------------|--------------------------------------------|-------|

| MODE[2:0]   | RCAS Link #n Configuration (0x180 – 0x1FC) | 000   |

| BSYNC       | RCAS Link #n Configuration (0x180 – 0x188) | 0     |

| FTHRES[6:0] | RCAS Framing Bit Threshold (0x108)         | ХХН   |

| MODE[2:0]   | TCAS Link #n Configuration (0x480 – 0x4FC) | 000   |

| BSYNC       | TCAS Link #n Configuration (0x480 – 0x488) | 0     |

| FTHRES[6:0] | TCAS Framing Bit Threshold (0x408)         | XXH   |

| FDATA[7:0]  | TCAS Idle Time-slot Fill Data (0x40C)      | 0xFF  |

### Notes:

- The **RCAS Link #n Configuration** register must be chosen from the range 0x180 through 0x1FC corresponding to the link being configured for unchannelised operation.

- The **TCAS Link #n Configuration** register must be chosen from the range 0x480 through 0x4FC corresponding to the link being configured for unchannelised operation.

- The BSYNC bit must only be programmed for links where  $0 \le n \le 2$ . For other links, there is no BSYNC bit.

- The FTHRES[6:0] bits of the RCAS Framing Bit Threshold (0x108) / TCAS Framing Bit Threshold (0x408) registers have no effect on the operation of an unchannelised link with BSYNC low, or on unchannelised links with no BSYNC bit.

- The FDATA[7:0] bits of the TCAS Idle Time-slot Fill Data (0x40C) register, and the FTHRES[6:0] bits of the RCAS Framing Bit Threshold (0x108) / TCAS Framing Bit Threshold (0x408) registers, affect all links of a

APPLICATION NOTE PMC-990639

PM7381 FREEDM-32A672

ISSUE 1

PROGRAMMER'S GUIDE

FREEDM-32A672. The programmer should ensure that these values are suitable for all links attached to a FREEDM-32A672.

## 5.5 8.192 Mbps H-MVIP Links

The timing relationship of the receive data clock (RMV8DC), frame pulse clock (RMV8FPC), data (RD[n]) and frame pulse (RFP8B[n]) signals of a link configured for 8.192 Mbps H-MVIP operation with a type 0 frame pulse is shown in Figure 10. The falling edges of each RMV8FPC are aligned to a falling edge of the corresponding RMV8DC for 8.192 Mbps H-MVIP operation. The FREEDM-32A672 samples RFP8B low on the falling edge of RMV8FPC and references this point as the start of the next frame. The FREEDM-32A672 samples the data provided on RD[n] at the <sup>3</sup>/<sub>4</sub> point of the data bit using the rising edge of RMV8DC as indicated for bit 1 (B1) of time-slot 0 (TS 0) in Figure 10. B1 is the most significant bit and B8 is the least significant bit of each octet. Time-slots can be ignored by setting the PROV bit in the corresponding word of the receive channel provision RAM in the RCAS672 block to low.

The timing relationship of the transmit data clock (TMV8DC), frame pulse clock (TMV8FPC), data (TD[n]) and frame pulse (TFP8B) signals of a link configured for 8.192 Mbps H-MVIP operation with a type 0 frame pulse is shown in Figure 11. The falling edges of each TMV8FPC are aligned to a falling edge of the corresponding TMV8DC for 8.192 Mbps H-MVIP operation. The FREEDM-32A672 samples TFP8B low on the falling edge of TMV8FPC and references this point as the start of the next frame. The FREEDM-32A672 updates the data provided on TD[n] on every second falling edge of TMV8DC as indicated for bit 2 (B2) of time-slot 0 (TS 0) in Figure 11. The first bit of the next frame is updated on TD[n] on the falling TMV8DC clock edge for which TFP8B is also sampled low. B1 is the most significant bit and B8 is the least significant bit of each octet.

PM7381 FREEDM-32A672

ISSUE 1

PROGRAMMER'S GUIDE

Time-slots that are not provisioned to belong to any channel (PROV bit in the corresponding word of the transmit channel provision RAM in the TCAS672 block set low) transmits the contents of the **TCAS Idle Time-slot Fill Data** (0x40C) register.

To configure the RCAS672 and TCAS672 to interface to 8.192 Mbps H-MVIP links, the following bits are written:

| Bit         | Register                                   | Value |

|-------------|--------------------------------------------|-------|

| MODE[2:0]   | RCAS Link #n Configuration (0x180 – 0x1FC) | 111   |

| BSYNC       | RCAS Link #n Configuration (0x180 – 0x188) | Х     |

| FTHRES[6:0] | RCAS Framing Bit Threshold (0x108)         | XXH   |

| MODE[2:0]   | TCAS Link #n Configuration (0x480 – 0x4FC) | 111   |

| BSYNC       | TCAS Link #n Configuration (0x480 – 0x488) | Х     |

| FTHRES[6:0] | TCAS Framing Bit Threshold (0x408)         | XXH   |

| FDATA[7:0]  | TCAS Idle Time-slot Fill Data (0x40C)      | 0xFF  |

### Notes:

When link 4m (0≤m≤7) is configured for operation in 8.192 Mbps H-MVIP mode (MODE[2:0]="111"), data cannot be received on links 4m+1, 4m+2 and 4m+3. However, links 4m+1, 4m+2 and 4m+3 must be configured for 8.192 Mbps H-MVIP mode for correct operation of the RCAS672. From a channel assignment point of view in the RCAS672 (Registers 0x100, 0x104), timeslots 0 through 31 of the H-MVIP link are treated as time-slots 0 through 31 of

APPLICATION NOTE PMC-990639 PMC PMC-Sierra, Inc.

PM7381 FREEDM-32A672

ISSUE 1

PROGRAMMER'S GUIDE

link 4m, time-slots 32 through 63 of the H-MVIP link are treated as time-slots 0 through 31 of link 4m+1, time-slots 64 through 95 of the H-MVIP link are treated as time-slots 0 through 31 of link 4m+2 and time-slots 96 through 127 of the H-MVIP link are treated as time-slots 0 through 31 of link 4m+3.

- When link 4m (0≤m≤7) is configured for operation in 8.192 Mbps H-MVIP mode, links 4m+1, 4m+2 and 4m+3 are driven with constant ones. However, links 4m+1, 4m+2 and 4m+3 must be configured for 8.192 Mbps H-MVIP mode for correct operation of the TCAS672. From a channel assignment point of view in the TCAS672 (Registers 0x40, 0x404), time-slots 0 through 31 of link 4m are mapped to time-slots 0 through 31 of the H-MVIP link, time-slots 0 through 31 of link 4m+1 are mapped to time-slots 32 through 63 of the H-MVIP link, time-slots 0 through 31 of link 4m+2 are mapped to time-slots 64 through 95 of the H-MVIP link and time-slots 0 through 31 of link 4m+3 are mapped to time-slots 96 through 127 of the H-MVIP link.

- The BSYNC value is ignored for links configured for H-MVIP.

- The FTHRES[6:0] bits of the RCAS Framing Bit Threshold (0x108) / TCAS Framing Bit Threshold (0x408) registers have no effect on the operation of H-MVIP links.

- The FDATA[7:0] bits of the TCAS Idle Time-slot Fill Data (0x40C) register, and the FTHRES[6:0] bits of the RCAS Framing Bit Threshold (0x108) / TCAS Framing Bit Threshold (0x408) registers, affect all links of a FREEDM-32A672. The programmer should ensure that these values are suitable for all links attached to a FREEDM-32A672.

## 5.6 2.048 Mbps H-MVIP Links

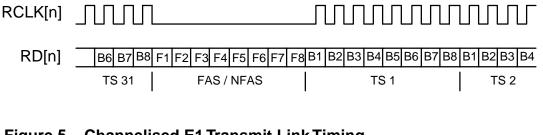

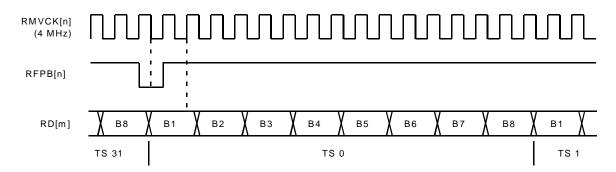

The timing relationship of the receive data clock (RMVCK[n]), data (RD[m], where 8n≤m≤8n+7) and frame pulse (RFPB[n]) signals of a link configured for 2.048 Mbps H-MVIP operation with a type 0 frame pulse is shown in Figure 12. The FREEDM-32A672 samples RFPB[n] low on the falling edge of the corresponding RMVCK[n] and references this point as the start of the next frame. The FREEDM-32A672 samples the data provided on RD[m] at the ¾ point of the data bit using the rising edge of the corresponding RMVCK[n] as indicated for bit 1 (B1) of time-slot 0 (TS 0) in Figure 12. B1 is the most significant bit and B8 is the least significant bit of each octet. Time-slots can be ignored by setting the PROV bit in the corresponding word of the receive channel provision RAM in the RCAS672 block to low.

APPLICATION NOTE PMC-990639

PM7381 FREEDM-32A672

ISSUE 1

PROGRAMMER'S GUIDE

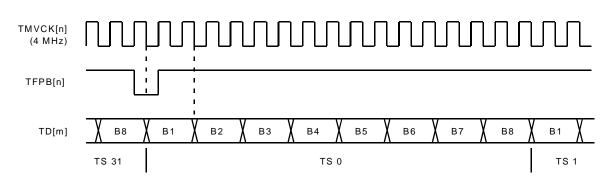

The timing relationship of the transmit data clock (TMVCK[n]), data (TD[m], where 8n≤m≤8n+7) and frame pulse (TFPB[n]) signals of a link configured for 2.048 Mbps H-MVIP operation with a type 0 frame pulse is shown in Figure 13. The FREEDM-32A672 samples TFPB[n] low on the falling edge of the corresponding TMVCK[n] and references this point as the start of the next frame. The FREEDM-32A672 updates the data provided on TD[m] on every second falling edge of the corresponding TMVCK[n] as indicated for bit 2 (B2) of time-slot 0 (TS 0) in Figure 13. The first bit of the next frame is updated on TD[n] on the falling TMVCK[n] clock edge for which TFPB[n] is also sampled low. B1 is the most significant bit and B8 is the least significant bit of each octet. Time-slots that are not provisioned to belong to any channel (PROV bit in the corresponding word of the transmit channel provision RAM in the TCAS672 block set low) transmits the contents of the **TCAS Idle Time-slot Fill Data** (0x40C) register.

## Figure 13 – Transmit 2.048 Mbps H-MVIP Link Timing

To configure the RCAS672 and TCAS672 to interface to 2.048 Mbps H-MVIP links, the following bits are written:

| Bit       | Register                                   | Value |

|-----------|--------------------------------------------|-------|

| MODE[2:0] | RCAS Link #n Configuration (0x180 – 0x1FC) | 011   |

APPLICATION NOTE PMC-990639

ISSUE 1

PROGRAMMER'S GUIDE

| Bit         | Register                                   | Value |

|-------------|--------------------------------------------|-------|

| BSYNC       | RCAS Link #n Configuration (0x180 – 0x188) | Х     |

| FTHRES[6:0] | RCAS Framing Bit Threshold (0x108)         | ХХН   |

| MODE[2:0]   | TCAS Link #n Configuration (0x480 – 0x4FC) | 011   |

| BSYNC       | TCAS Link #n Configuration (0x480 – 0x488) | Х     |

| FTHRES[6:0] | TCAS Framing Bit Threshold (0x408)         | ХХН   |

| FDATA[7:0]  | TCAS Idle Time-slot Fill Data (0x40C)      | 0xFF  |

PMC-Sierra, Inc.

#### Notes:

- The RCAS Link #n Configuration register must be chosen from the range • 0x180 through 0x1FC corresponding to the link being configured for 2.048 Mbps H-MVIP operation.

- The TCAS Link #n Configuration register must be chosen from the range 0x480 through 0x4FC corresponding to the link being configured for 2.048 Mbps H-MVIP operation.

- The BSYNC value is ignored for links configured for H-MVIP. •

- The FTHRES[6:0] bits of the RCAS Framing Bit Threshold (0x108) / TCAS • Framing Bit Threshold (0x408) registers have no effect on the operation of H-MVIP links.

- The FDATA[7:0] bits of the TCAS Idle Time-slot Fill Data (0x40C) register, • and the FTHRES[6:0] bits of the RCAS Framing Bit Threshold (0x108) / TCAS Framing Bit Threshold (0x408) registers, affect all links of a FREEDM-32A672. The programmer should ensure that these values are suitable for all links attached to a FREEDM-32A672.

PM7381 FREEDM-32A672

PROGRAMMER'S GUIDE

## 6 CONFIGURING THE ANY-PHY PACKET INTERFACE

ISSUE 1

The RAPI672 and TAPI672 blocks must be configured via the normal mode registers in order to enable the transferring of data between the partial packet buffers and the receive and transmit APPI.

## 6.1 Configuring the Receive Any-PHY Packet Interface (RAPI672)

The RAPI672 is configured by programming bits within the **RAPI Control** (0x580) register. The values programmed affect all receive channels. The default configuration is as follows:

| Bit        | Register             | Value |

|------------|----------------------|-------|

| BADDR[2:0] | RAPI Control (0x580) | 111   |

| ALL1ENB    | RAPI Control (0x580) | 1     |

| Reserved   | RAPI Control (0x580) | 0     |

| STATEN     | RAPI Control (0x580) | 0     |

| ENABLE     | RAPI Control (0x580) | 0     |

The default indicates that the RAPI672 is disabled from responding to device selection.

### Activation of the RAPI672

By default, the RAPI672 is disabled from responding to device selection. The ENABLE bit must be set to enable normal operation of the RAPI672. The encoding of this bit is:

| ENABLE | Function                                                             |

|--------|----------------------------------------------------------------------|

| 0      | The RAPI672 will not respond to device selection.                    |

| 1      | The RAPI672 operates normally, and will respond to device selection. |

## Base Address of the Receive APPI

The base address bits (BADDR[2:0]) configure the address space occupied by the FREEDM-32A672 device for purposes of responding to receive polling and receive device selection. During polling, the BADDR[2:0] bits are used to respond to polling via the RXADDR[2:0] pins. During device selection, the

PM7381 FREEDM-32A672

ISSUE 1

PROGRAMMER'S GUIDE

BADDR[2:0] are used to select a FREEDM-32A672 device, enabling it to accept data on the receive APPI. During data transfer, the RXDATA[15:13] pins of the prepended channel address reflect the BADDR[2:0] bits.

## All Ones Enable

The All Ones Enable bit (ALL1ENB) permits the FREEDM-32A672 to respond to receive polling and device selection when BADDR[2:0] = '111'. The encoding of this bit is:

| ALL1ENB | Function                                                                                                                                                                                       |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | The FREEDM-32A672 responds to receive polling and device selection when BADDR[2:0] = RXADDR[2:0] = '111'.                                                                                      |

| 1       | The FREEDM-32A672 regards the all-ones address as a null address and does not respond to receive polling and device selection when BADDR[2:0] = '111', regardless of the value of RXADDR[2:0]. |

## Status Enable

The FREEDM-32A672 can be programmed to overwrite the receive data signal pins, RXDATA[7:0], of the final word of each packet transfer (REOP pin is high) with the status of packet reception when that packet is errored (RERR pin is high). The RAPI672 Status Enable bit enables this feature as follows:

| STATEN | Function                                                                                                           |

|--------|--------------------------------------------------------------------------------------------------------------------|

| 0      | The RAPI672 does not report detailed status information for an errored packet.                                     |

| 1      | The RAPI672 overwrites RXDATA[7:0] of the final word of an errored packet with status information for that packet. |

When STATEN = 1 and the REOP and RERR pins are both high, the status information is bit mapped on RXDATA[7:0] as follows:

| Bit           | Status                          |

|---------------|---------------------------------|

| RXDATA[0] = 1 | Channel FIFO overrun            |

| RXDATA[1] = 1 | Maximum packet length violation |

| RXDATA[2] = 1 | FCS error                       |

| RXDATA[3] = 1 | Non-octet aligned               |

PMC PMC-Sierra, Inc.

PM7381 FREEDM-32A672

APPLICATION NOTE PMC-990639

ISSUE 1

PROGRAMMER'S GUIDE

| Bit                 | Status            |

|---------------------|-------------------|

| RXDATA[4] = 1       | HDLC packet abort |

| RXDATA[7:5] =<br>XH | Reserved          |

# 6.2 Configuring the Transmit Any-PHY Packet Interface (TAPI672)

The TAPI672 is configured by programming bits within the **TAPI Control** (0x600) register. The values programmed affect all transmit channels. The default configuration is as follows:

| Bit           | Register                                    | Value |

|---------------|---------------------------------------------|-------|

| BADDR[2:0]    | TAPI Control (0x600)                        | 111   |

| ALL1ENB       | TAPI Control (0x600)                        | 1     |

| Reserved[1:0] | TAPI Control (0x600)                        | 00    |

| ENABLE        | TAPI Control (0x600)                        | 0     |

| BLEN[7:0]     | TAPI Indirect Channel Data Register (0x608) | 0x00  |

The default indicates that data provided to the TAPI672 by the transmit APPI will be ignored.

## Activation of the TAPI672

By default, data provided to the TAPI672 by the transmit APPI is ignored. The ENABLE bit must be set to enable normal operation of the TAPI672. The encoding of this bit is:

| ENABLE | Function                                                                                                                                                                                                                                                              |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | The state machines in the TAPI672 are held in their idle state.<br>The TAPI672 will complete the current data transfer and will<br>respond to any further transactions on the transmit APPI<br>normally (by setting TRDY high), but data provided will be<br>ignored. |

| 1      | The TAPI672 operates normally. Data can be transferred from the transmit APPI to the partial packet buffer in the THDL672.                                                                                                                                            |

PM7381 FREEDM-32A672

PROGRAMMER'S GUIDE

**Base Address of the Receive APPI**

The base address bits (BADDR[2:0]) configure the address space occupied by the FREEDM-32A672 device for purposes of responding to transmit polling and transmit data transfers. During polling, the TXADDR[12:10] pins are compared with the BADDR[2:0] bits to determine if the poll address identified by TXADDR[9:0] is intended for a channel in this FREEDM-32A672 device. During data transmission, the TXDATA[15:13] pins of the prepended channel address are compared with the BADDR[2:0] bits to determine if the data to follow is intended for this FREEDM-32A672 device.

# All Ones Enable

The All Ones Enable bit (ALL1ENB) permits the FREEDM-32A672 to respond to transmit polling and device selection when BADDR[2:0] = '111'. The encoding of this bit is:

| ALL1ENB | Function                                                                                                                                                                                                             |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | The FREEDM-32A672 responds to transmit polling when BADDR[2:0] = TXADDR[12:10] = '111' and device selection when BADDR[2:0] = TXDATA[15:13] = '111'.                                                                 |

| 1       | The FREEDM-32A672 regards the all-ones address as a null address and does not respond to transmit polling and device selection when BADDR[2:0] = '111', regardless of the values of TXADDR[12:10] and TXDATA[15:13]. |

## **Channel Burst Length**

The channel burst length (BLEN[7:0]) bits report the data transfer burst length read from the TAPI672 channel provision RAM after an indirect read operation has completed. The data transfer burst length specifies the length (in bytes, less one) of burst data transfers on the transmit APPI which are not terminated by the assertion of TEOP. The data transfer burst length can be specified on a perchannel basis with burst lengths of up to 256 bytes. The data transfer burst length to be written to the channel provision RAM in an indirect write operation must be set up in this register before triggering the write. BLEN[7:0] reflects the value written until the completion of a subsequent indirect read operation.

The BLEN[7:0] value must be set according to the indirect channel transfer size of the THDL672 block (XFER[3:0] in the **THDL Indirect Channel Data #3** (0x38C) register) using the following equation:

APPLICATION NOTE PMC-990639

PM7381 FREEDM-32A672

ISSUE 1

PROGRAMMER'S GUIDE

BLEN[7:0] = (XFER[3:0] + 1)×16 -1.

A description of the XFER[3:0] bits can be found in section 7.5. The relationship between XFER[3:0] and BLEN[7:0] is shown in the following table.

| XFER[3:0] | BLEN[7:0] |

|-----------|-----------|

| 0000      | 0x0F      |

| 0001      | 0x1F      |

| 0010      | 0x2F      |

| 0011      | 0x3F      |

| 0100      | 0x4F      |

| 0101      | 0x5F      |

| 0110      | 0x6F      |

| 0111      | 0x7F      |

| 1000      | 0x8F      |

| 1001      | 0x9F      |

| 1010      | 0xAF      |

| 1011      | 0xBF      |

| 1100      | 0xCF      |

| 1101      | 0xDF      |

| 1110      | 0xEF      |

| 1111      | 0xFF      |

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS' INTERNAL USE 25

ISSUE 1

PROGRAMMER'S GUIDE

## 7 HDLC AND CHANNEL FIFO CONFIGURATION

The FREEDM-32A672 processes the data stream in the receive direction via the RHDL672 block and it processes the data stream in the transmit direction via the THDL672 block. Each of these blocks must be configured via the normal mode registers.

## 7.1 Configuring the RHDL672

The RHDL672 is configured by programming bits within the **RHDL Configuration** (0x220) register and the **RHDL Maximum Packet Length** (0x224) register. The values programmed affect all receive channels. The default configuration is as follows:

| Bit       | Register                           | Value  |

|-----------|------------------------------------|--------|

| LENCHK    | RHDL Configuration (0x220)         | 0      |

| TSTD      | RHDL Configuration (0x220)         | 0      |

| MAX[15:0] | RHDL Maximum Packet Length (0x224) | 0xFFFF |

The default indicates no maximum packet length checking and datacom bit ordering.

### Maximum Packet Length

The RHDL672 may be configured to abort packets which exceed the maximum length of *n* where  $0 \le n \le 0xFFFF$ . The following bits are written to enable or disable this feature:

| LENCHK | MAX[15:0] | Function                                                                                                                                                                      |

|--------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0xFFFF    | Receive packets are not checked for maximum size and MAX[15:0] must be set to 0xFFFF.                                                                                         |

| 1      | n         | Receive packets with total length, including address, control, information and FCS fields, greater than MAX[15:0] bytes are aborted and the remainder of the frame discarded. |

PM7381 FREEDM-32A672

PROGRAMMER'S GUIDE

ISSUE 1

#### Datacom/Telecom Bit Order

The RHDL672 may be configured to reverse the order of bits in the HDLC data transferred across the receive APPI. The following bit is written to specify the order of bits:

| TSTD | Function                                                                                                                                                                                                    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Datacom standard: least significant bit of each byte on the receive APPI bus (AD[0] and AD[8]) is the first HDLC bit received. Normally, when HDLC processing is enabled, the TSTD bit must be set to zero. |

| 1    | Telecom standard: most significant bit of each byte on the receive APPI bus (AD[7] and AD[15]) is the first HDLC bit received.                                                                              |

## 7.2 Configuring the THDL672

The THDL672 is configured by programming bits within the **THDL Configuration** (0x3B0) register. The values programmed affect all transmit channels. The default configuration is as follows:

| Bit           | Register                   | Value |

|---------------|----------------------------|-------|

| Reserved[3:0] | THDL Configuration (0x3B0) | 0x0   |

| Reserved[4]   | THDL Configuration (0x3B0) | 0     |

| TSTD          | THDL Configuration (0x3B0) | 0     |

| BIT8          | THDL Configuration (0x3B0) | 0     |

The default indicates that data is formatted in datacom bit ordering.

### Datacom/Telecom Bit Order

The THDL672 may be configured to reverse the order of bits in the HDLC data transferred on the transmit APPI. The following bit is written to specify the order of bits:

| TSTD | Function                                                                                                                                                                                                        |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Datacom standard: least significant bit of each byte on the transmit APPI bus (AD[0] and AD[8]) is the first HDLC bit transmitted. Normally, when HDLC processing is enabled, the TSTD bit must be set to zero. |

APPLICATION NOTE PMC-990639

PMC-Sierra, Inc.

PM7381 FREEDM-32A672

ISSUE 1

PROGRAMMER'S GUIDE

| TSTD | Function                                                                                                                           |

|------|------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Telecom standard: most significant bit of each byte on the transmit APPI bus (AD[7] and AD[15]) is the first HDLC bit transmitted. |

#### BIT8

The BIT8 field affects channels of the THDL672 that are configured with 7BIT set. The BIT8 value specifies the data bit transmitted on the least significant bit of each octet.

| BIT8 | Function                                                                                      |

|------|-----------------------------------------------------------------------------------------------|

| 0    | Channels configured for 7BIT will transmit a zero on the least significant bit of each octet. |

| 1    | Channels configured for 7BIT will transmit a one on the least significant bit of each octet.  |

## 7.3 Programming a Channel FIFO

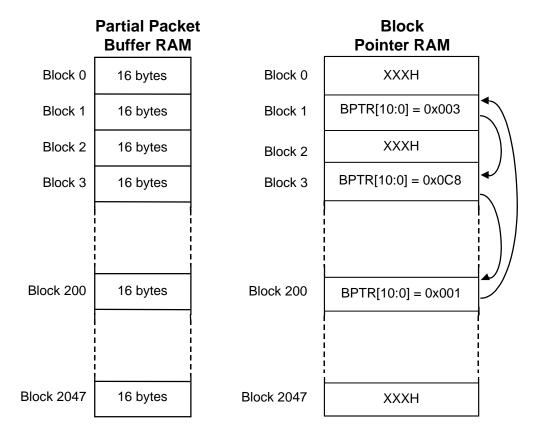

A Channel FIFO is created from 3 or more blocks of internal RAM, and each block holds 16 bytes of packet data. There is a total of 2048 blocks (32 Kbytes) available to assign among the receive channels, and another 2048 blocks (32 Kbytes) available to assign among the transmit channels.

A FIFO is created by assigning a circular linked list of blocks as shown in Figure 14. This shows a channel FIFO consisting of 3 blocks. The quantity of buffers and the arrangement of links is chosen by the programmer, and the selection of blocks can be arbitrary. The programmer must ensure that a block is not assigned to more than one circularly linked list.

APPLICATION NOTE PMC-990639

PM7381 FREEDM-32A672

PROGRAMMER'S GUIDE

Figure 14 – Specifying a Channel FIFO

ISSUE 1

## 7.3.1 Receive Channel FIFO

A receive channel FIFO is programmed by repeating the following procedure for each block within the circularly linked list:

- 1. Poll the BUSY bit of the **RHDL Indirect Block Select** (0x210) register until it is zero. This ensures that a previous indirect RAM access has completed and that a new indirect RAM access can be started.

- 2. Write the following register with the next block in the circular linked list, or exit if all links have been programmed:

| Bit        | Register                         | Value                           |

|------------|----------------------------------|---------------------------------|

| BPTR[10:0] | RHDL Indirect Block Data (0x214) | 0 through<br>0x7FF are<br>valid |

APPLICATION NOTE PMC-990639

PROGRAMMER'S GUIDE

| Bit      | Register                         | Value |

|----------|----------------------------------|-------|

| Reserved | RHDL Indirect Block Data (0x214) | 0     |

3. Specify the block and update the internal block pointer RAM by writing the following register. Proceed to step 1.

| Bit         | Register                           | Value                           |

|-------------|------------------------------------|---------------------------------|

| BLOCK[10:0] | RHDL Indirect Block Select (0x210) | 0 through<br>0x7FF are<br>valid |

| Reserved    | RHDL Indirect Block Select (0x210) | 0                               |

| BRWB        | RHDL Indirect Block Select (0x210) | 0                               |

| BUSY        | RHDL Indirect Block Select (0x210) | Х                               |

## 7.3.2 Transmit Channel FIFO

A transmit channel FIFO is programmed by repeating the following procedure for each block within the circularly linked list:

- 1. Poll the BUSY bit of the THDL Indirect Block Select (0x3A0) register until it is zero. This ensures that a previous indirect RAM access has completed and that a new indirect RAM access can be started.

- 2. Write the following register with the next block in the circular linked list, or exit if all links have been programmed:

| Bit         | Register                         | Value                           |

|-------------|----------------------------------|---------------------------------|

| BPTR[10:0]  | THDL Indirect Block Data (0x3A4) | 0 through<br>0x7FF are<br>valid |

| Reserved[0] | THDL Indirect Block Data (0x3A4) | 0                               |

| Reserved[1] | THDL Indirect Block Data (0x3A4) | 0                               |

3. Specify the block and update the internal block pointer RAM by writing the following register. Proceed to step 1.

PMC-Sierra, Inc.

ISSUE 1

APPLICATION NOTE PMC-990639

ISSUE 1

PROGRAMMER'S GUIDE

PM7381 FREEDM-32A672

| Bit         | Register                           | Value                           |

|-------------|------------------------------------|---------------------------------|

| BLOCK[10:0] | THDL Indirect Block Select (0x3A0) | 0 through<br>0x7FF are<br>valid |

| Reserved    | THDL Indirect Block Select (0x3A0) | 0                               |

| BRWB        | THDL Indirect Block Select (0x3A0) | 0                               |

| BUSY        | THDL Indirect Block Select (0x3A0) | Х                               |

PMC-Sierra, Inc.

#### 7.4 RHDL672 Channel Configuration

The RHDL672 provides configurable options for each receive channel as identified in the following register fields:

| Bit         | Register                                       |

|-------------|------------------------------------------------|

| DELIN       | RHDL Indirect Channel Data Register #1 (0x204) |

| STRIP       | RHDL Indirect Channel Data Register #1 (0x204) |

| XFER[3:0]   | RHDL Indirect Channel Data Register #2 (0x208) |

| OFFSET[1:0] | RHDL Indirect Channel Data Register #2 (0x208) |

| CRC[1:0]    | RHDL Indirect Channel Data Register #2 (0x208) |

| INVERT      | RHDL Indirect Channel Data Register #2 (0x208) |

| PRIORITY    | RHDL Indirect Channel Data Register #2 (0x208) |

| 7BIT        | RHDL Indirect Channel Data Register #2 (0x208) |

**Note:** When writing to **RHDL Indirect Channel Data Register #1** (0x204), the reserved bit (bit 11) must be set low for correct operation of the FREEDM-32A672.

#### Delineation

The data bits from the RCAS672 can be written directly to the Partial Packet Buffer or processed for flag sequence delineation, bit de-stuffing and CRC verification. The following bit enables or disables this feature:

APPLICATION NOTE PMC-990639

ISSUE 1

PM7381 FREEDM-32A672

PROGRAMMER'S GUIDE

| DELIN | Function                                                                                                                                                              |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Data is written to the Partial Packet Buffer without any HDLC processing (no flag sequence delineation, bit de-stuffing nor CRC verification) on the incoming stream. |

| 1     | Data is processed for flag sequence delineation, bit de-<br>stuffing and optionally, CRC verification (CRC verification<br>depends on CRC[1:0] value).                |

PMC-Sierra, Inc.

## Strip FCS Bit

The indirect frame check sequence discard bit (STRIP) enables the RHDL672 to remove the FCS data before writing to the channel FIFO. STRIP is ignored when DELIN is low or when CRC[1:0] = 00B. This feature is configured as follows:

| STRIP | Function                                                               |

|-------|------------------------------------------------------------------------|

| 0     | Includes FCS data with the data stream written to the channel FIFO.    |

| 1     | Removes the FCS data from the data stream written to the channel FIFO. |

## DMA Transfer Size

The indirect channel transfer size configures the amount of data transferred in each transaction. When the channel FIFO depth reaches the depth specified by XFER[3:0] or when an end-of-packet exists in the FIFO, a poll of this FREEDM-32A672 device will indicate that data exists and is ready to be transferred across the receive APPI. Specifying a large transfer size may affect APPI bus access latencies for other channels. The following bits specify the channel transfer size:

| XFER[3:0]                 | Function                                                                                             |

|---------------------------|------------------------------------------------------------------------------------------------------|

| 0 through 15<br>are valid | Specifies the data transfer size in blocks: Blocks = XFER[3:0] +1, and there are 16 bytes per block. |

## Notes:

• XFER[3:0] should be set such that the number of blocks transferred is at least two fewer than the total allocated to the associated channel.

PROGRAMMER'S GUIDE

ISSUE 1

## **Insertion of Offset Bytes**

The RHDL672 can be configured to insert offset bytes into the data stream before writing the data stream to the channel FIFO. The offset bytes are placed before each packet and their value is undefined. The following configuration options are available:

| OFFSET[1:0] | Function                                  |

|-------------|-------------------------------------------|

| 00          | RHDL672 does not insert offset bytes      |

| 01          | RHDL672 inserts 1 offset byte per packet  |

| 10          | RHDL672 inserts 2 offset bytes per packet |

| 11          | RHDL672 inserts 3 offset bytes per packet |

## **CRC Algorithm**

The RHDL672 can perform CRC verification of the incoming data stream. The available options are as follows:

| CRC[1:0] | DELIN | Function               |

|----------|-------|------------------------|

| Х        | 0     | No CRC verification    |

| 00       | 1     | No CRC verification    |

| 01       | 1     | CRC-CCITT verification |

| 10       | 1     | CRC-32 verification    |

| 11       | 1     | Reserved               |

## **HDLC Data Inversion**

The INVERT bit configures the RHDL672 to logically invert the incoming HDLC stream from the RCAS672 before processing it. The bit is specified as follows:

| INVERT | Function                     |

|--------|------------------------------|

| 0      | HDLC stream is not inverted. |

| 1      | HDLC stream is inverted.     |

## Specifying Receive Channel Priority

All receive channels that must transfer data from their channel FIFO to packet memory contend for access to the receive APPI bus. The PRIORITY bit allows

PM7381 FREEDM-32A672

ISSUE 1

PROGRAMMER'S GUIDE

specified channels to have priority access to the receive APPI bus. The bit encoding is as follows:

| PRIORITY | Function                                                  |

|----------|-----------------------------------------------------------|

| 0        | This channel is serviced after channels with PRIORITY=1.  |

| 1        | This channel is serviced before channels with PRIORITY=0. |

## Handling of Robbed bit Signaling

The 7BIT enable configures the RHDL672 to ignore the least significant bit of each octet (last bit of each octet received) in the corresponding link RD[n]. This bit is encoded as follows:

| 7BIT | Function                                                                |

|------|-------------------------------------------------------------------------|

| 0    | The entire receive data stream is processed.                            |

| 1    | The least significant bit (last bit of each octet received) is ignored. |

# 7.5 THDL672 Channel Configuration

The THDL672 provides configurable options for each transmit channel as identified in the following register fields:

| Bit        | Register                                       |

|------------|------------------------------------------------|

| DELIN      | THDL Indirect Channel Data Register #1 (0x384) |

| CRC[1:0]   | THDL Indirect Channel Data Register #1 (0x384) |

| FLEN[10:0] | THDL Indirect Channel Data Register #2 (0x388) |

| DFCS       | THDL Indirect Channel Data Register #2 (0x388) |

| INVERT     | THDL Indirect Channel Data Register #2 (0x388) |

| 7BIT       | THDL Indirect Channel Data Register #2 (0x388) |

| XFER[3:0]  | THDL Indirect Channel Data Register #3 (0x38C) |

| FLAG[2:0]  | THDL Indirect Channel Data Register #3 (0x38C) |

| LEVEL[3:0] | THDL Indirect Channel Data Register #3 (0x38C) |

| IDLE       | THDL Indirect Channel Data Register #3 (0x38C) |

| TRANS      | THDL Indirect Channel Data Register #3 (0x38C) |

ISSUE 1

PROGRAMMER'S GUIDE

**Note:** When writing to **THDL Indirect Channel Data Register #1** (0x384), the reserved bit (bit 11) must be set low for correct operation of the FREEDM-32A672. When writing to **THDL Indirect Channel Data Register #2** (0x388), the reserved bits (bits 11 and 14) must be set low for correct operation of the FREEDM-32A672.

## **Frame Delineation**

The transmit packet data from packet memory can be written directly to the outgoing data stream or processed for flag sequence insertion, bit stuffing and CRC generation. The following bit enables or disables this feature:

| DELIN | Function                                                                                                                                              |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0     | Data is written directly to the outgoing data stream without<br>any HDLC processing (no flag sequence insertion, bit stuffing<br>nor CRC generation). |  |

| 1     | Data is processed for flag sequence insertion, bit stuffing and optionally, CRC generation (CRC generation depends on CRC[1:0] value).                |  |

## CRC Algorithm

The THDL672 can perform CRC generation on the outgoing data stream. The available options are as follows:

| CRC[1:0] | DELIN | Function             |

|----------|-------|----------------------|

| Х        | 0     | No CRC generation    |

| 00       | 1     | No CRC generation    |

| 01       | 1     | CRC-CCITT generation |

| 10       | 1     | CRC-32 generation    |

| 11       | 1     | Reserved             |

## Channel FIFO Length

The indirect FIFO length (FLEN[10:0]) is the number of blocks, less one, that is provisioned to the circular channel FIFO specified by the FPTR[10:0] block pointer.

APPLICATION NOTE PMC-990639 PINC PMC-Sierra, Inc.

PM7381 FREEDM-32A672

ISSUE 1

PROGRAMMER'S GUIDE

| FLEN[10:0] | Function                                                                                              |

|------------|-------------------------------------------------------------------------------------------------------|

|            | Specifies the Channel FIFO size in blocks, where Blocks = FLEN[10:0] + 1, and each block is 16 bytes. |

## **Inverting the FCS**

The diagnose frame check sequence bit (DFCS) specifies whether the FCS field inserted into the transmit data stream is inverted. This is provided for diagnostic purposes and is programmed as follows:

| DFCS | Function                                                     |  |

|------|--------------------------------------------------------------|--|

| 0    | FCS field in the outgoing HDLC stream is not inverted.       |  |

| 1    | FCS field in the outgoing HDLC stream is logically inverted. |  |

## **Robbed Bit Signaling**

The least significant stuff enable bit (7BIT) configures the THDL672 to stuff the least significant bit of each octet assigned to the transmit channel in the corresponding transmit link (TD[n]).

| 7BIT | Function                                                                                                                                                     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | The entire octet contains valid data and BIT8 is ignored.                                                                                                    |

| 1    | The least significant bit (last bit of each octet transmitted) does not contain channel data and is forced to the value configured by the BIT8 register bit. |

## **DMA Transfer Size**

The indirect channel transfer size specifies the amount of data that the partial packet processor requests from the TAPI672 block. When the channel FIFO free space reaches or exceeds the limit specified by XFER[3:0], the partial packet processor will inform the TAPI672 so that a poll on that channel reflects that the channel FIFO is able to accept XFER[3:0] + 1 blocks of data. Specifying a large transfer size may affect APPI bus access latencies for other channels. The following bits specify the channel transfer size:

| XFER[3:0] | Function                                                                                              |  |

|-----------|-------------------------------------------------------------------------------------------------------|--|

| _         | Specifies the data transfer size in blocks, where Blocks = XFER[3:0] + 1, and each block is 16 bytes. |  |

APPLICATION NOTE PMC-990639

PMC-Sierra, Inc.

PM7381 FREEDM-32A672

ISSUE 1

PROGRAMMER'S GUIDE

#### Notes:

• To prevent lockup, the channel transfer size (XFER[3:0]) can be configured to be less than or equal to the start transmission level set by LEVEL[3:0] and TRANS. Alternatively, the channel transfer size can be set such that the total number of blocks in the logical channel FIFO minus the start transmission level is an integer multiple of the channel transfer size.

## Specifying The Number of Flag or Idle Bytes Inserted Between Frames

The THDL672 can be configured to insert either flag or idle bytes (8 bits of one's) into the data stream between HDLC packets. The number of these is programmed as follows:

| FLAG[2:0] | Minimum Number of Flag/Idle Bytes |  |

|-----------|-----------------------------------|--|

| 000       | 1 flag / 0 Idle byte              |  |