PMC-Sierra

**ISSUE 2**

REGISTER DESCRIPTION PMC-1990682

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

PM5365

# **TEMAP**

# HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

# REGISTER DESCRIPTION

**Proprietary and Confidential**

**ISSUE 2: JULY 2001**

ISSUE 2

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

### **CONTENTS**

| 1 | NOR  | MAL MODE REGISTER DESCRIPTION 1                             |

|---|------|-------------------------------------------------------------|

|   | 1.1  | TOP LEVEL MASTER REGISTERS                                  |

|   | 1.2  | T1/E1 MASTER CONFIGURATION REGISTERS (N=1 TO 28) . 31       |

|   | 1.3  | RJAT RECEIVE JITTER ATTENUATOR REGISTERS (N=1 TO 28)47      |

|   | 1.4  | TJAT TRANSMIT JITTER ATTENUATOR REGISTERS (N=1 TO 28)       |

|   | 1.5  | PMON PERFORMANCE MONITOR REGISTERS (N=1 TO 28) 57           |

|   | 1.6  | PRBS GENERATOR/CHECKER REGISTERS (N=1 TO 28) 63             |

|   | 1.7  | ALMI ALARM INTEGRATOR REGISTERS (N=1 TO 28)70               |

|   | 1.8  | T1-FRMR FRAMER REGISTERS (N=1 TO 28)75                      |

|   | 1.9  | E1-FRMR FRAMER REGISTERS (N=1 TO 21) 81                     |

|   | 1.10 | DS3/M13 MASTER REGISTERS                                    |

|   | 1.11 | DS3 TRAN TRANSMITTER REGISTERS 121                          |

|   | 1.12 | DS3 FRMR RECEIVE FRAMER REGISTERS 125                       |

|   | 1.13 | DS3 PERFORMANCE MONITORING REGISTERS 136                    |

|   | 1.14 | DS3 TRANSMIT HDLC CONTROLLER REGISTERS 148                  |

|   | 1.15 | DS3 RECEIVE HDLC CONTROLLER REGISTERS 157                   |

|   | 1.16 | PRGD PSEUDO RANDOM PATTERN GENERATOR AND DETECTOR REGISTERS |

|   | 1.17 | MX23 MULTIPLEXER REGISTERS                                  |

|   | 1.18 | FEAC TRANSMIT BIT ORIENTED CODE REGISTERS 186               |

|   | 1.19 | FEAC RECEIVE BIT ORIENTED CODE REGISTERS 189                |

i

ISSUE 2

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

| 1.20       | DS2 FRAMER REGISTERS (N=1 TO 7)                                | 191 |

|------------|----------------------------------------------------------------|-----|

| 1.21       | MX12 MULTIPLEXER REGISTERS (N=1 TO 7)                          | 203 |

| 1.22       | SONET/SDH MAPPER MASTER CONFIGURATION REGISTE                  |     |

| 1.23       | VTPP INGRESS TRIBUTARY PAYLOAD PROCESSOR REGISTERS             | 233 |

| 1.24       | RTDM RECEIVE TRIBUTARY DEMAPPER REGISTERS                      | 261 |

| 1.25       | RTOP RECEIVE TRIBUTARY PATH OVERHEAD PROCESSOREGISTERS         |     |

| 1.26       | VTPP EGRESS TRIBUTARY PAYLOAD PROCESSOR REGISTERS              | 374 |

| 1.27       | TRAP TRANSMIT ALARM PROCESSOR REGISTERS                        | 402 |

| 1.28       | TTOP TRANSMIT TRIBUTARY PATH OVERHEAD PROCESS REGISTERS        | _   |

| 1.29       | TTMP TRANSMIT TRIBUTARY MAPPER REGISTERS                       | 501 |

| 1.30       | D3MD DS3 DROP SIDE MAPPER REGISTERS                            | 537 |

| 1.31       | D3MA DS3 ADD SIDE MAPPER REGISTERS                             | 540 |

| 1.32       | SCALEABLE BANDWIDTH INTERCONNECT MASTER CONFIGURATION REGISTER | 543 |

| 1.33       | EXSBI EXTRACT SCALEABLE BANDWIDTH INTERCONNEC                  | _   |

| 1.34       | INSBI INSERT SCALEABLE BANDWIDTH INTERCONNECT REGISTERS        | 559 |

| LIST OF TA | <u>BLES</u>                                                    |     |

| TABLE 1 -  | - INGRESS SERIAL INTERFACE MODE SELECTION                      | 39  |

| TABLE 2    | - EGRESS SERIAL INTERFACE MODE SELECTION                       | 40  |

REGISTER DESCRIPTION PMC-1990682

| HIGH DENSITY VT/TU MAPPER |

|---------------------------|

| AND M13 MULTIPLEXER       |

| TABLE 3 - TIMESLOT 0 BIT POSITION ALLOCATION                      | 94  |

|-------------------------------------------------------------------|-----|

| TABLE 4 - SIGNALING MULTIFRAME TIMESLOT 16, FRAME 0 BIT POSITIONS |     |

| TABLE 5 - E1 FRMR CODEWORD SELECT                                 | 100 |

ISSUE 2

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### 1 NORMAL MODE REGISTER DESCRIPTION

Normal mode registers are used to configure and monitor the operation of the TEMAP. Normal mode registers (as opposed to test mode registers) are selected when TRS (A[13]) is low.

Notes on Normal Mode Register Bits:

- 1) Writing values into unused register bits typically has no effect. However, to ensure software compatibility with future, feature-enhanced versions of the product, unused register bit must be written with logic 0. Reading back unused bits can produce either a logic 1 or a logic 0; hence unused register bits should be masked off by software when read.

- All configuration bits that can be written into can also be read back. This

allows the processor controlling the TEMAP to determine the programming

state of the block.

- Writeable normal mode register bits are cleared to logic 0 upon reset unless otherwise noted.

- 4) Writing into read-only normal mode register bit locations does not affect TEMAP operation unless otherwise noted.

- 5) The TEMAP registers default to a DS3 M13 mux with T1 framers enabled. Default system side access is via the SBI bus without any tributaries enabled. The SONET/SDH blocks are by default in a reset state.

- 6) In the SONET/SDH register descriptions virtual tribtuaries, VT, and Tributary units, TU, are sometimes used interchangeably. Sometimes TU is only only mentioned but the intention is that the register applies to both TUs and the equivilent VTs.

- 7) Some configurations of the device will hold certain sections of the TEMAP in reset. For example when in T1 mode, the E1 specific blocks are held in reset and vice versa. The individual register descriptions indicate when certain registers are held in reset.

1

**ISSUE 2**

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### 1.1 Top Level Master Registers

Register 0000H: Global Reset

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 |      | Unused   | Х       |

| Bit 6 |      | Unused   | Х       |

| Bit 5 |      | Unused   | Х       |

| Bit 4 |      | Unused   | Х       |

| Bit 3 |      | Unused   | Х       |

| Bit 2 |      | Unused   | Х       |

| Bit 1 |      | Unused   | Х       |

| Bit 0 | R/W  | RESET    | 0       |

#### RESET:

The RESET bit implements a software reset for the entire TEMAP. If the RESET bit is a logic 1, the entire TEMAP is held in reset. This bit is not self-clearing; therefore, a logic 0 must be written to bring the TEMAP out of reset. Holding the TEMAP in a reset state effectively puts it into a low power, standby mode. A hardware reset clears the RESET bit, thus deasserting the software reset.

**ISSUE 2**

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### Register 0001H: Global Configuration

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R/W  | E1/T1B   | 0       |

| Bit 6 | R/W  | LINEOPT1 | 0       |

| Bit 5 | R/W  | LINEOPT0 | 0       |

| Bit 4 | R/W  | SYSOPT2  | 0       |

| Bit 3 | R/W  | SYSOPT1  | 1       |

| Bit 2 | R/W  | SYSOPT0  | 0       |

| Bit 1 | R/W  | OPMODE1  | 0       |

| Bit 0 | R/W  | OPMODE0  | 0       |

#### OPMODE[1:0]:

Configures the master operating mode of the TEMAP. The three modes are Mapper/Multiplexer, Transmux or DS3 framer. In mapper/multiplexer mode, all the T1/E1 framer slices are configured to pass unframed data through to the system interface and the TEMAP becomes a SONET/SDH mapper or DS3 multiplexer only. For transmit performance monitoring in SBI mode, OPMODE[0:1] must be set to 01. In Transmux mode unframed T1 streams are passed between the SONET/SDH mapper and the DS3 multiplexer. In DS3 Framer only mode all the T1/E1 framers, the SONET/SDH mapper, the MX23, MX12 and DS2 blocks are disabled and the RDATO, RFPO/RMFPO, RGAPCLK/RSCLK, ROVRHD, TFPO/TMFPO, TFPI/TMFPI, TGAPCLK and TDATI I/O pins are enabled for serial clock and data mode. The following table shows the OPMODE values for each mode:

| OPMODE[1:0] | Mode                    |

|-------------|-------------------------|

| 00          | Reserved                |

| 01          | Mapper/Multiplexer mode |

| 10          | Transmux mode           |

| 11          | DS3 Framer Only mode    |

Note that in DS3 Framer-only mode, RXMFPO and TXMFPI in Register 1002H must be programmed correctly.

PMC-Sierra

**ISSUE 2**

REGISTER DESCRIPTION PMC-1990682

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

Note that in Transmux mode, the SYSOPT[2:0] bits must be programmed to "010". Also note that the T1/E1 receive jitter attenuators must be used for each tributary. This can be selected by setting RJATBYP to logic 0 for all T1/E1 framers in Register 002H+80H\*N: T1/E1 Receive Options.

#### SYSOPT:

The System Side Options bits, SYSOPT[2:0], configures the system side interface of the TEMAP. The possible system side interface selections are serial clock and data interfaces and Scaleable Bandwidth Interconnect bus interface. The following table shows the SYSOPT[2:0] values for each system side interface configuration:

| SYSOPT[2:0] | System Interface Mode           |

|-------------|---------------------------------|

| 000         | Serial Clock and Data Interface |

| 001         | Reserved                        |

| 010         | SBI Interface                   |

| 011         | Reserved                        |

| 1XX         | Reserved                        |

Note that in Transmux operating mode(OPMODE[1:0]="10"), the SYSOPT[2:0] bits must be programmed to "010".

#### LINEOPT[1:0]:

The Line Side Options bits, LINEOPT[1:0], select the line side multiplexing interface of the TEMAP. When the TEMAP is configured for high density T1/E1 framer mode or Mapper/Multiplexer mode the LINEOPT[1:0] bits select between a DS3 multiplexer, DS3 Mapper or T1/E1 mapper. When in DS3 Framer only mode LINEOPT[1:0] selects the DS3 LIU interface or DS3 Mapper. These bits must be left selecting the LIU interface when in Transmux mode. The following table shows the LINEOPT[1:0] values for each line side interface configuration:

| LINEOPT[1:0] | Line Interface Mode               |

|--------------|-----------------------------------|

| 00           | DS3 Mux with serial LIU interface |

| 01           | DS3 Mux with DS3 SONET/SDH Mapper |

| 1X           | T1/E1 Mapper                      |

REGISTER DESCRIPTION

PMC-1990682

ISSUE 2

PMC-Sierra

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### E1/T1B:

The E1/T1B pin configures the T1/E1 framer slices to be configured as either 28 T1 framers or 21 E1 framers. When E1/T1B is a logic 0 the T1/E1 framer slices are configured as 28 T1 framers. When E1/T1B is a logic the T1/E1 framer slices are configured as 21 E1 framers.

ISSUE 2

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### Register 0002H: Revision/Global PMON Update

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R    | TYPE3    | 0       |

| Bit 6 | R    | TYPE2    | 0       |

| Bit 5 | R    | TYPE1    | 0       |

| Bit 4 | R    | TYPE0    | 1       |

| Bit 3 | R    | ID3      | 0       |

| Bit 2 | R    | ID2      | 1       |

| Bit 1 | R    | ID1      | 0       |

| Bit 0 | R    | ID0      | 1       |

Writing to this register causes all performance monitoring to be updated simultaneously.

#### ID[3:0]:

The version identification bits ID[3:0], are set to a fixed value representing the version number of the TEMAP. These bits can be read by software to determine the version number.

#### TYPE[3:0]:

The type identification bits TYPE[3:0], identify this device from other products in the same Asynchronous Multiplexer family of devices.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### Register 003H: Master Recovered Clock#1/Reference Clock Select

| Bit   | Туре | Function  | Default |

|-------|------|-----------|---------|

| Bit 7 | R/W  | REFCLK1   | 0       |

| Bit 6 | R/W  | REFCLK0   | 0       |

| Bit 5 | R/W  | Reserved  | 0       |

| Bit 4 | R/W  | RECV1SEL4 | 0       |

| Bit 3 | R/W  | RECV1SEL3 | 0       |

| Bit 2 | R/W  | RECV1SEL2 | 0       |

| Bit 1 | R/W  | RECV1SEL1 | 0       |

| Bit 0 | R/W  | RECV1SEL0 | 0       |

#### RECV1SEL[4:0]:

Select the source of the recovered clock which will be output on pin RECVCLK1. When this register is a logic 0 no registers are selected and the RECVCLK1 output will be held at logic 0. Values from 1 to 28 select the recovered clock from one of the 28 T1/E1 framers slices. When in E1 mode the T1/E1 framers slices from 22 through 28 will result in an invalid recovered clock.

#### Reserved:

This bit must be set to logic 0 for proper operation of the TEMAP.

#### REFCLK[1:0]:

The Reference clock select bits, REFCLK[1:0], select the source of the clock to be used as the transmit T1/E1 clock. The following table shows the REFCLK[1:0] selections:

| REFCLK[1:0] | Clock                               |

|-------------|-------------------------------------|

| 00          | CTCLK pin                           |

| 01          | RECVCLK1 pin (generated internally) |

| 10          | RECVCLK2 pin (generated internally) |

| 11          | Unused                              |

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

## Register 0004H: Recovered Clock#2 Select

**ISSUE 2**

| Bit   | Туре | Function  | Default |

|-------|------|-----------|---------|

| Bit 7 |      | Unused    | Х       |

| Bit 6 |      | Unused    | Х       |

| Bit 5 |      | Unused    | Х       |

| Bit 4 | R/W  | RECV2SEL4 | 0       |

| Bit 3 | R/W  | RECV2SEL3 | 0       |

| Bit 2 | R/W  | RECV2SEL2 | 0       |

| Bit 1 | R/W  | RECV2SEL1 | 0       |

| Bit 0 | R/W  | RECV2SEL0 | 0       |

#### RECV2SEL[4:0]:

Select the source of the recovered clock which will be output on pin RECVCLK2. When this register is a logic 0 no registers are selected and the RECVCLK2 output will be held at logic 0. Values from 1 to 28 select the recovered clock from one of the 28 T1/E1 framers slices. When in E1 mode the T1/E1 framers slices from 22 through 28 will result in an invalid recovered clock.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

### Register 0010H: Master Clock Monitor #1

ISSUE 2

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 |      | Unused   | Х       |

| Bit 6 | R    | RCLKA    | Х       |

| Bit 5 | R    | TICLKA   | Х       |

| Bit 4 | R    | CTCLKA   | Х       |

| Bit 3 | R    | XCLKA    | X       |

| Bit 2 | R    | CLK52MA  | Х       |

| Bit 1 | R    | LREFCLKA | Х       |

| Bit 0 | R    | SREFCLKA | Х       |

When a monitored clock signal makes a low to high transition, the corresponding register bit is set high. The bit will remain high until this register is read, at which point all the bits in this register are cleared. A lack of transitions is indicated by the corresponding register bit reading low. This register should be read at periodic intervals to detect clock failures.

#### SREFCLKA:

The SREFCLK active, SREFCLKA, bit detects low to high transitions on the SREFCLK input. SREFCLKA is set high on a rising edge of SREFCLK, and is set low when this register is read.

#### LREFCLKA:

The LREFCLK active, LREFCLKA, bit detects low to high transitions on the LREFCLK input. LREFCLKA is set high on a rising edge of LREFCLK, and is set low when this register is read.

#### CLK52MA:

The CLK52M active, CLK52MA, bit detects low to high transitions on the CLK52M input. CLK52MA is set high on a rising edge of CLK52M, and is set low when this register is read.

#### XCLKA:

The XCLK active, XCLKA, bit detects for low to high transitions on the XCLK input. XCLKA is set high on a rising edge of XCLK, and is set low when this register is read.

PMC-Sierra

**ISSUE 2**

REGISTER DESCRIPTION PMC-1990682

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### CTCLKA:

The CTCLK active, CTCLKA, bit detects for low to high transitions on the CTCLK input. CTCLKA is set high on a rising edge of CTCLK, and is set low when this register is read.

#### TICLKA:

The TICLK active, TICLKA, bit detects for low to high transitions on the TICLK input. TICLKA is set high on a rising edge of TICLK, and is set low when this register is read.

#### RCLKA:

The RCLK active, RCLKA, bit detects for low to high transitions on the RCLK input. RCLKA is set high on a rising edge of RCLK, and is set low when this register is read.

PMC-Sierra

REGISTER DESCRIPTION PMC-1990682

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### Register 0011H: Master Clock Monitor #2

**ISSUE 2**

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R    | ECLKA8   | Х       |

| Bit 6 | R    | ECLKA7   | Х       |

| Bit 5 | R    | ECLKA6   | Х       |

| Bit 4 | R    | ECLKA5   | Х       |

| Bit 3 | R    | ECLKA4   | X       |

| Bit 2 | R    | ECLKA3   | X       |

| Bit 1 | R    | ECLKA2   | Х       |

| Bit 0 | R    | ECLKA1   | Х       |

When a monitored clock signal makes a low to high transition, the corresponding register bit is set high. The bit will remain high until this register is read, at which point all the bits in this register are cleared. A lack of transitions is indicated by the corresponding register bit reading low. This register should be read at periodic intervals to detect clock failures.

#### ECLKA[1:8]:

The ECLK[x] active, ECLKA[x], bit detects low to high transitions on the ECLK inputs when the egress interface is configured for Clock Slave mode. ECLKA[x] is set high on a rising edge of ECLK[x], and is set low when this register is read.

REGISTER DESCRIPTION PMC-1990682 **ISSUE 2**

PMC-Sierra

HIGH DENSITY VT/TU MAPPER **AND M13 MULTIPLEXER**

#### Register 0012H: Master Clock Monitor #3

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R    | ECLKA16  | Х       |

| Bit 6 | R    | ECLKA15  | Х       |

| Bit 5 | R    | ECLKA14  | X       |

| Bit 4 | R    | ECLKA13  | Х       |

| Bit 3 | R    | ECLKA12  | X       |

| Bit 2 | R    | ECLKA11  | Х       |

| Bit 1 | R    | ECLKA10  | Х       |

| Bit 0 | R    | ECLKA9   | Х       |

When a monitored clock signal makes a low to high transition, the corresponding register bit is set high. The bit will remain high until this register is read, at which point all the bits in this register are cleared. A lack of transitions is indicated by the corresponding register bit reading low. This register should be read at periodic intervals to detect clock failures.

#### ECLKA[9:16]:

The ECLK[x] active, ECLKA[x], bit detects low to high transitions on the ECLK inputs when the egress interface is configured for Clock Slave mode. ECLKA[x] is set high on a rising edge of ECLK[x], and is set low when this register is read.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### Register 0013H: Master Clock Monitor #4

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R    | ECLKA24  | Х       |

| Bit 6 | R    | ECLKA23  | Х       |

| Bit 5 | R    | ECLKA22  | Х       |

| Bit 4 | R    | ECLKA21  | Х       |

| Bit 3 | R    | ECLKA20  | X       |

| Bit 2 | R    | ECLKA19  | Х       |

| Bit 1 | R    | ECLKA18  | Х       |

| Bit 0 | R    | ECLKA17  | Х       |

When a monitored clock signal makes a low to high transition, the corresponding register bit is set high. The bit will remain high until this register is read, at which point all the bits in this register are cleared. A lack of transitions is indicated by the corresponding register bit reading low. This register should be read at periodic intervals to detect clock failures.

#### ECLKA[17:24]:

The ECLK[x] active, ECLKA[x], bit detects low to high transitions on the ECLK inputs when the egress interface is configured for Clock Slave mode. ECLKA[x] is set high on a rising edge of ECLK[x], and is set low when this register is read.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### Register 0014H: Master Clock Monitor #5

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 |      | Unused   | Х       |

| Bit 6 |      | Unused   | Х       |

| Bit 5 |      | Unused   | Х       |

| Bit 4 |      | Unused   | Х       |

| Bit 3 | R    | ECLKA28  | Х       |

| Bit 2 | R    | ECLKA27  | Х       |

| Bit 1 | R    | ECLKA26  | Х       |

| Bit 0 | R    | ECLKA25  | Х       |

When a monitored clock signal makes a low to high transition, the corresponding register bit is set high. The bit will remain high until this register is read, at which point all the bits in this register are cleared. A lack of transitions is indicated by the corresponding register bit reading low. This register should be read at periodic intervals to detect clock failures.

#### ECLKA[25:28]:

The ECLK[x] active, ECLKA[x], bit detects low to high transitions on the ECLK inputs when the egress interface is configured for Clock Slave mode. ECLKA[x] is set high on a rising edge of ECLK[x], and is set low when this register is read.

HIGH DENSITY VT/TU MAPPER **AND M13 MULTIPLEXER**

#### Register 0020H: Master Interrupt Source

| Bit   | Туре | Function   | Default |

|-------|------|------------|---------|

| Bit 7 | R    | T1E1INT1   | Х       |

| Bit 6 | R    | T1E1INT2   | Х       |

| Bit 5 | R    | T1E1INT3   | Х       |

| Bit 4 | R    | T1E1INT4   | Х       |

| Bit 3 | R    | SDH/SBIINT | Х       |

| Bit 2 | R    | DS3INT     | X       |

| Bit 1 | R    | DS2INT     | Х       |

| Bit 0 | R    | MX12INT    | Х       |

#### MX12INT:

If the MX12INT bit is a logic 1, at least one bit in the Master Interrupt Source MX12 Register is set.

#### DS2INT:

If the DS2INT bit is a logic 1, at least one bit in the Master Interrupt Source DS2 Register is set.

#### DS3INT:

If the DS3INT bit is a logic 1, at least one bit in the Master Interrupt Source DS3 Register is set.

#### SDH/SBIINT:

If the SDH/SBIINT bit is a logic 1, at least one bit in either of the Master Interrupt Source SDH or SBI Registers is set.

#### T1E1INT4:

If the T1E1INT4 bit is a logic 1, at least one bit in the Master Interrupt Source T1E1#25-28 Register is set, that is, at least one of the fourth group of four T1 framers numbered 25-28 is generating an interrupt.

#### **T1E1INT3**:

If the T1E1INT3 bit is a logic 1, at least one bit in the Master Interrupt Source T1E1#17-24 Register is set, that is, at least one of the third group of eight T1/E1 framers numbered 17-24 is generating an interrupt.

**ISSUE 2**

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### **T1E1INT2**:

If the T1E1INT2 bit is a logic 1, at least one bit in the Master Interrupt Source T1E1#9-16 Register is set, that is, at least one of the second group of eight T1/E1 framers numbered 9-16 is generating an interrupt.

### **T1E1INT1**:

If the T1E1INT1 bit is a logic 1, at least one bit in the Master Interrupt Source T1E1#1-8 Register is set, that is, at least one of the first group of eight T1/E1 framers numbered 1-8 is generating an interrupt.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

### Register 0021H: Master Interrupt Source T1E1#1-8

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R    | T1E1#8   | Х       |

| Bit 6 | R    | T1E1#7   | Х       |

| Bit 5 | R    | T1E1#6   | Х       |

| Bit 4 | R    | T1E1#5   | Х       |

| Bit 3 | R    | T1E1#4   | Х       |

| Bit 2 | R    | T1E1#3   | Х       |

| Bit 1 | R    | T1E1#2   | Х       |

| Bit 0 | R    | T1E1#1   | Х       |

#### T1E1#[8:1]:

If the T1E1#[x] bit is a logic 1, an interrupt has been generated by T1/E1 framer slice x. To determine the T1/E1 block generating the interrupt and to clear the interrupt signal, read the T1/E1 Interrupt Source #1 and #2 registers for T1/E1 slice x.

**ISSUE 2**

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

### Register 0022H: Master Interrupt Source T1E1#9-16

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R    | T1E1#16  | Х       |

| Bit 6 | R    | T1E1#15  | Х       |

| Bit 5 | R    | T1E1#14  | X       |

| Bit 4 | R    | T1E1#13  | Х       |

| Bit 3 | R    | T1E1#12  | Х       |

| Bit 2 | R    | T1E1#11  | Х       |

| Bit 1 | R    | T1E1#10  | Х       |

| Bit 0 | R    | T1E1#9   | Х       |

#### T1E1#[16:9]:

If the T1E1#[x] bit is a logic 1, an interrupt has been generated by T1/E1 framer slice x. To determine the T1/E1 block generating the interrupt and to clear the interrupt signal, read the T1/E1 Interrupt Source #1 and #2 registers for T1/E1 slice x.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### Register 0023H: Master Interrupt Source T1E1#17-24

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R    | T1E1#24  | Х       |

| Bit 6 | R    | T1E1#23  | Х       |

| Bit 5 | R    | T1E1#22  | Х       |

| Bit 4 | R    | T1E1#21  | Х       |

| Bit 3 | R    | T1E1#20  | Х       |

| Bit 2 | R    | T1E1#19  | Х       |

| Bit 1 | R    | T1E1#18  | Х       |

| Bit 0 | R    | T1E1#17  | Х       |

#### T1E1#[24:17]:

If the T1E1#[x] bit is a logic 1, an interrupt has been generated by T1/E1 framer slice x. To determine the T1/E1 block generating the interrupt and to clear the interrupt signal, read the T1/E1 Interrupt Source #1 and #2 registers for T1/E1 slice x.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### Register 0024H: Master Interrupt Source T1E1#25-28

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 |      | Unused   | Х       |

| Bit 6 |      | Unused   | Х       |

| Bit 5 |      | Unused   | Х       |

| Bit 4 |      | Unused   | Х       |

| Bit 3 | R    | T1E1#28  | Х       |

| Bit 2 | R    | T1E1#27  | Х       |

| Bit 1 | R    | T1E1#26  | Х       |

| Bit 0 | R    | T1E1#25  | Х       |

#### T1E1#[28:25]:

If the T1E1#[x] bit is a logic 1, an interrupt has been generated by T1/E1 framer slice x. To determine the T1/E1 block is generating the interrupt and to clear the interrupt signal, read the T1/E1 Interrupt Source #1 and #2 registers.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

### Register 0025H: Master Interrupt Source SDH

ISSUE 2

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R    | Unused   | Х       |

| Bit 6 | R    | Unused   | Х       |

| Bit 5 | R    | LDPINT   | Х       |

| Bit 4 | R    | D3MAINT  | Х       |

| Bit 3 | R    | D3MDINT  | Х       |

| Bit 2 | R    | EVTPPINT | Х       |

| Bit 1 | R    | IVTPPINT | Х       |

| Bit 0 | R    | RTOPINT  | Х       |

#### RTOPINT:

If the RTOPINT bit is a logic 1, an interrupt has been generated by the RTOP block. The RTOP Interrupt register must be read to clear this interrupt.

#### **IVTPPINT**:

If the IVTPPINT bit is a logic 1, an interrupt has been generated by the Ingress VTPP block. The Ingress VTPP Interrupt register must be read to clear this interrupt.

#### **EVTPPINT**:

If the EVTPPINT bit is a logic 1, an interrupt has been generated by the egress VTPP block. The egress VTPP Interrupt register must be read to clear this interrupt.

#### D3MDINT:

If the D3MDINT bit is a logic 1, the D3MD block is generating an interrupt. The D3MD Interrupt register must be read to clear this interrupt.

#### D3MAINT:

If the D3MAINT bit is a logic 1, the D3MA block is generating an interrupt. The D3MA Interrupt register must be read to clear this interrupt.

#### LDPINT:

If the LDPINT bit is a logic 1, an interrupt has been generated from a parity error on the Line DROP bus. This is an indication that there may be multiple

REGISTER DESCRIPTION

PMC-1990682 ISSUE 2

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

devices driving the Line DROP bus simultaneously. This interrupt is enabled with the LDPE bit in the SONET/SDH Master Ingress Configuration register. This Interrupt register will be cleared when read.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### Register 0026H: Master Interrupt Source SBI

ISSUE 2

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 |      | Unused   | Х       |

| Bit 6 |      | Unused   | Х       |

| Bit 5 | R    | EXSBIINT | Х       |

| Bit 4 | R    | INSBIINT | Х       |

| Bit 3 | R/W  | SDET1E   | 0       |

| Bit 2 | R/W  | SDET0E   | 0       |

| Bit 1 | R    | SDET1INT | Х       |

| Bit 0 | R    | SDET0INT | Х       |

#### SDET0INT:

If the SACT0INT bit is a logic 1, an interrupt has been generated by the SBIDET[0] signal high concurrently with this device driving the SBI DROP bus. This is an indication that there are multiple devices driving the SBI DROP bus simultaneously. The TEMAP will not output data when SBIDET[0] is asserted. The SBIDET0 Collision Detect register must be read to determine which tributary was in conflict. This Interrupt register will be cleared when read.

#### SDET1INT:

If the SDET1INT bit is a logic 1, an interrupt has been generated by the SBIDET[1] signal high concurrently with this device driving the SBI DROP bus. This is an indication that there are multiple devices driving the SBI DROP bus simultaneously. The TEMAP will not output data when SBIDET[1] is asserted. The SBIDET1 Collision Detect register must be read to determine which tributary was in conflict. This Interrupt register will be cleared when read.

#### SDET0E:

The SBI ADD activity detect interrupt enable bit, SDET0E, enables interrupts to be generated on INTB when the SBIDET[0] signal is asserted concurrently with this device driving the SBI DROP bus. When SDET0E is a logic 1, an interrupt will be generated when SBIDET[0] is active with this device driving the SBI DROP bus. When SBIDET[0] is a logic 0, errors are not generated due to SBIDET[0] concurrent with this device driving the SBI DROP bus.

**ISSUE 2**

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### SDET1E:

The SBI ADD activity detect interrupt enable bit, SDET1E, enables interrupts to be generated on INTB when the SBIDET[1] signal is asserted concurrently with this device driving the SBI DROP bus. When SDET1E is a logic 1, an interrupt will be generated when SBIDET[1] is active with this device driving the SBI DROP bus. When SBIDET[1] is a logic 0, errors are not generated due to SBIDET[1] concurrent with this device driving the SBI DROP bus.

#### **INSBIINT**:

If the INSBIINT bit is a logic 1, the INSBI block is generating an interrupt due to a FIFO underrun or overrun. The INSBI Interrupt register must be read to clear this interrupt.

#### **EXSBIINT**:

If the EXSBIINT bit is a logic 1, the EXSBI block is generating an interrupt due to a FIFO underrun or overrun. The EXSBI Interrupt register must be read to clear this interrupt.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### Register 0028H: Master Interrupt Source DS3

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R    | DS3PMON  | Х       |

| Bit 6 | R    | DS3RDLC  | Х       |

| Bit 5 | R    | DS3RBOC  | Х       |

| Bit 4 | R    | DS3FRMR  | Х       |

| Bit 3 | R    | DS3TDPR  | X       |

| Bit 2 | R    | DS3XBOC  | X       |

| Bit 1 | R    | MX23     | Х       |

| Bit 0 | R    | DS3PRGD  | X       |

#### **DS3PRGD**:

If the DS3PRGD bit is a logic 1, the PRGD (Pseudo Random Generator/Receiver) connecting to the DS3 framer is generating an interrupt. Register 1031H must be read to determine the source of the interrupt and to clear this interrupt signal.

#### MX23:

If the MX23 bit is a logic 1, the MX23 block is generating an interrupt due to the detection of a DS2 loopback request. The MX23 Loopback Request Interrupt register at address 1046H must be read to clear this interrupt.

#### **DS3XBOC**:

If the DS3XBOC bit is a logic 1, the DS3 XBOC block is generating an interrupt.

#### DS3TDPR:

If the DS3TDPR bit is a logic 1, the DS3 TDPR block is generating an interrupt. The DS3 TDPR Interrupt Status register at address 1024H must be read to determine which event in DS3 TDPR has caused the interrupt.

#### **DS3FRMR**:

If the DS3FRMR bit is a logic 1, the DS3 FRMR block is generating an interrupt. The DS3 FRMR Interrupt status register at address 100EH must be read to determine which event in DS3 FRMR has caused the interrupt.

PMC-Sierra

**ISSUE 2**

REGISTER DESCRIPTION PMC-1990682

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### **DS3RBOC**:

If the DS3RBOC bit is a logic 1, the DS3 RBOC block is generating an interrupt. The DS3 RBOC Interrupt Status register at address 104BH must be read to determine which event in DS3 RBOC has caused the interrupt.

#### DS3RDLC:

If the DS3RDLC bit is a logic 1, the DS3 RDLC block is generating an interrupt. The DS3 RDLC Status register at address 102AH must be read to determine which event in DS3 RDLC has caused the interrupt.

#### **DS3PMON**:

If the DS3PMON bit is a logic 1, the DS3 PMON block is generating an interrupt. The DS3 PMON Interrupt Status register at address 1011H must be read to determine which event in DS3 PMON has caused the interrupt.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### Register 0029H: Master Interrupt Source DS2

| Bit   | Туре | Function   | Default |

|-------|------|------------|---------|

| Bit 7 |      | Unused     | Х       |

| Bit 6 | R    | DS2 FRMR#7 | Х       |

| Bit 5 | R    | DS2 FRMR#6 | Х       |

| Bit 4 | R    | DS2 FRMR#5 | Х       |

| Bit 3 | R    | DS2 FRMR#4 | Х       |

| Bit 2 | R    | DS2 FRMR#3 | Х       |

| Bit 1 | R    | DS2 FRMR#2 | Х       |

| Bit 0 | R    | DS2 FRMR#1 | Х       |

#### DS2 FRMR#[7:1]:

Any DS2 FRMR#[7:1] bits which are a logic 1 indicate which of the seven DS2 Framers is generating an interrupt on the INTB output pin. The appropriate DS2 FRMR Interrupt Status register must be read to clear the interrupt.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### Register 002AH: Master Interrupt Source MX12

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 |      | Unused   | Х       |

| Bit 6 | R    | MX12#7   | Х       |

| Bit 5 | R    | MX12#6   | Х       |

| Bit 4 | R    | MX12#5   | Х       |

| Bit 3 | R    | MX12#4   | Х       |

| Bit 2 | R    | MX12#3   | Х       |

| Bit 1 | R    | MX12#2   | Х       |

| Bit 0 | R    | MX12#1   | Х       |

#### MX12#[7:1]:

Any MX12#[7:1] bits which are a logic 1 indicate a MX12 block that is generating an interrupt on the INTB output pin due to the detection of a DS1 loopback request. The appropriate MX12 Loopback Interrupt register must be read to clear the interrupt.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### Register 002CH: Master SBIDET0 Collision Detect LSB

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R    | COL7     | 0       |

| Bit 6 | R    | COL6     | 0       |

| Bit 5 | R    | COL5     | 0       |

| Bit 4 | R    | COL4     | 0       |

| Bit 3 | R    | COL3     | 0       |

| Bit 2 | R    | COL2     | 0       |

| Bit 1 | R    | COL1     | 0       |

| Bit 0 | R    | COL0     | 0       |

#### Register 002DH: Master SBIDET0 Collision Detect MSB

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 |      | Unused   | Х       |

| Bit 6 |      | Unused   | Х       |

| Bit 5 |      | Unused   | Х       |

| Bit 4 |      | Unused   | Х       |

| Bit 3 |      | Unused   | Х       |

| Bit 2 |      | Unused   | Х       |

| Bit 1 |      | Unused   | Х       |

| Bit 0 | R    | COL8     | 0       |

#### COL[8:0]:

The SBIDET[0] Collision Detection identifier, COL[8:0], identifies the SBI column number of the last collision as indicated by the SDET0INT interrupt. The tributary experiencing contention is calculated from COL[8:0] as follows: SPE# or DS3# = MOD(COL[8:0]-1,3)+1

T1# or TVT1.5# = SPE#, MOD(TRUNC((COL[8:0]-10)/3-1),28)+1 E1# or TVT2# = SPE#, MOD(TRUNC((COL[8:0]-10)/3-1),21)+1

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### Register 002EH: Master SBIDET1 Collision Detect LSB

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R    | COL7     | 0       |

| Bit 6 | R    | COL6     | 0       |

| Bit 5 | R    | COL5     | 0       |

| Bit 4 | R    | COL4     | 0       |

| Bit 3 | R    | COL3     | 0       |

| Bit 2 | R    | COL2     | 0       |

| Bit 1 | R    | COL1     | 0       |

| Bit 0 | R    | COL0     | 0       |

#### Register 002FH: Master SBIDET1 Collision Detect MSB

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 |      | Unused   | Х       |

| Bit 6 |      | Unused   | Х       |

| Bit 5 |      | Unused   | Х       |

| Bit 4 |      | Unused   | Х       |

| Bit 3 |      | Unused   | Х       |

| Bit 2 |      | Unused   | Х       |

| Bit 1 |      | Unused   | Х       |

| Bit 0 | R    | COL8     | 0       |

#### COL[8:0]:

The SBIDET[1] Collision Detection identifier, COL[8:0], identifies the SBI column number of the last collision as indicated by the SDET1INT interrupt. The tributary experiencing contention is calculated from COL[8:0] as follows: SPE# or DS3# = MOD(COL[8:0]-1,3)+1

T1# or TVT1.5# = SPE#, MOD(TRUNC((COL[8:0]-10)/3-1),28)+1 E1# or TVT2# = SPE#, MOD(TRUNC((COL[8:0]-10)/3-1),21)+1

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### 1.2 T1/E1 Master Configuration Registers (N=1 to 28)

ISSUE 2

#### Register 0000H+80H\*N: T1/E1 Master Configuration

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 |      | Unused   | Х       |

| Bit 6 |      | Unused   | Х       |

| Bit 5 | R/W  | PMONRST  | 0       |

| Bit 4 | R/W  | TXPMON   | 0       |

| Bit 3 | R/W  | Reserved | 0       |

| Bit 2 | R/W  | Reserved | 0       |

| Bit 1 | R/W  | Reserved | 0       |

| Bit 0 | R/W  | RESET    | 0       |

#### RESET:

The RESET bit allows software to hold each T1/E1 framer slice in a reset condition. When RESET is a logic 1 the entire T1/E1 slice will be held in a reset state which is also a low power state. This will force all registers to their default state. While in reset the clocks can not be guaranteed accurate or existing. When RESET is a logic 0 the T1/E1 framer slice is in normal operating mode.

When the TEMAP DS3 mux is configured in G.747 mode every forth T1/E1 framer must be held in reset, ie. N=4,8,12,16,20,24,28 in the address calculation for this register.

#### Reserved:

This bit must be set to logic 0 for proper operation of the TEMAP.

#### TXPMON:

When in Mapper/Multiplexer mode this bit selects performance monitoring for the transmit path. When TXPMON is a logic 1 performance monitoring is performed on the egress tributary. When TXPMON is a logic 0 performance monitoring is performed on the ingress tributary. In Transmux mode TXPMON set to 1 selects the mapper transmit stream for performance monitoring and TXPMON set to 0 selects the DS3 transmit stream for performance monitoring. The LINEOPT[1:0] bits in the Global Configuration register must be set to "00" when in transmux mode for TXPMON to be active.

PMC-Sierra

REGISTER DESCRIPTION PMC-1990682

ISSUE 2 HIGH DENSITY VT/TU MAPPER

AND M13 MULTIPLEXER

TXPMON can be used in High Density Framer mode with clear channel system interfaces enabled by the RCVCLRCH bit in the T1/E1 Receive Options register set to logic 1. TXPMON must be set to logic 0 when RCVCLRCH is logic 0 in High Density Framer mode.

#### PMONRST:

The performance monitor reset bit, PMONRST, forces the PMON block into reset. When PMONRST is a logic 1 the PMON block will be held in a reset state. When PMONRST is a logic 0 the PMON block is in normal operating mode.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

## Register 0002H+80H\*N: T1/E1 Receive Options

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R/W  | RJATBYP  | 1       |

| Bit 6 | R/W  | Reserved | 0       |

| Bit 5 | R/W  | Reserved | 0       |

| Bit 4 | R/W  | Unused   | 0       |

| Bit 3 | R/W  | Reserved | 0       |

| Bit 2 | R/W  | WORDERR  | 0       |

| Bit 1 | R/W  | CNTNFAS  | 0       |

| Bit 0 | R/W  | CCOFA    | 0       |

This register allows software to configure the receive functions of each framer.

### **CCOFA**

The CCOFA bit determines whether the PMON counts Change-Of-Frame Alignment (COFA) events or out-of-frame (OOF) events. When CCOFA is set to logic 1, COFA events are counted by PMON. When CCOFA is set to logic 0, OOF events are counted by PMON. The CCOFA bit is only valid in T1 mode.

### **CNTNFAS:**

In E1 mode, when the CNTNFAS bit is a logic 1, a zero in bit 2 of time slot 0 of non-frame alignment signal (NFAS) frames results in an increment of the framing error count. If WORDERR is also a logic 1, the word is defined as the eight bits consisting of the seven-bit FAS pattern and bit 2 of time slot 0 of the next NFAS frame. When the CNTNFAS bit is a logic 0, only errors in the FAS affect the framing error count.

### WORDERR:

In E1 mode, the WORDERR bit determines how frame alignment signal (FAS) errors are reported. When WORDERR is logic 1, one or more errors in the seven bit FAS word results in a single framing error count. When WORDERR is logic 0, each error in a FAS word results in a single framing error count.

#### Reserved:

This bit must be set to logic 0 for proper operation of the TEMAP.

ISSUE 2

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

## **RJATBYP**:

The RJATBYP bit disables jitter attenuation in the receive direction. When receive jitter attenuation is not being used, setting RJATBYP to logic 1 will reduce the latency through the receiver section by typically 40 bits. The receive jitter attenuator must not be bypassed when receiving T1 tributaries via the DS3 multiplexer.

**ISSUE 2**

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

## Register 0003H+80H\*N: T1/E1 Alarm Configuration

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R/W  | Reserved | 0       |

| Bit 6 | R/W  | Reserved | 0       |

| Bit 5 | R/W  | Reserved | 0       |

| Bit 4 | R/W  | Reserved | 0       |

| Bit 3 | R/W  | TAISEN   | 0       |

| Bit 2 |      | Unused   | Х       |

| Bit 1 | R/W  | Reserved | 0       |

| Bit 0 | R/W  | EALMEN   | 0       |

#### Reserved:

This bit must be set to logic 0 for proper operation of the TEMAP.

### TAISEN:

The TAISEN bit enables generation of an all ones AIS alarm in the egress tributary. When TAISEN is a logic 1 the egress data stream is forced to all ones. When TAISEN is a logic 0 the egress tributary operates normally. Note that the diagnostic loopback point is downstream of this AIS insertion point (i.e. AIS will be looped back to the receive side when diagnostic loopback is enabled).

#### Reserved:

This bit must be set to logic 0 for proper operation of the TEMAP.

### EALMEN:

The EALMEN bit enables an egress SBI alarm indication signal to force the transmit data stream into an all ones AIS. When EALMEN is a logic 1 and the SBI bus is selected, an alarm indication from the SBI bus will force the transmit data to the VT/TU mapper and DS3 M13 multiplexer to all ones. When EALMEN is a logic 0, an SBI alarm indication will not affect the transmit data stream.

The diagnostic loopback point is upstream of this AIS insertion point.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

# Register 0004H+80H\*N: T1/E1 Egress Line Interface Configuration

| Bit   | Туре | Function    | Default |

|-------|------|-------------|---------|

| Bit 7 | R/W  | Reserved    | 0       |

| Bit 6 | R/W  | Reserved    | 1       |

| Bit 5 | R/W  | SBICLKMODE  | 0       |

| Bit 4 |      | Unused      | Х       |

| Bit 3 | R/W  | TJATFIFOBYP | 0       |

| Bit 2 | R/W  | TJATPLLBYP  | 0       |

| Bit 1 | R/W  | PLLREF1     | 0       |

| Bit 0 | R/W  | PLLREF0     | 0       |

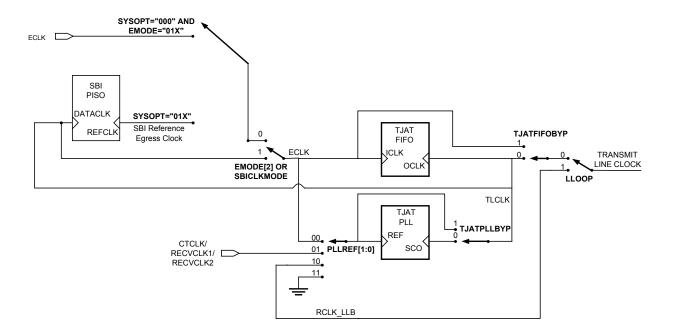

Figure 1 shows how the transmit jitter attenuator can be configured to be in or out of the transmit path. TXCLK is the TEMAP internal clock that is used for egress timing in Master clock modes and is the data clock to the DS3 M13 mux and SONET/SDH mapper. RCLK is the recovered clock.

Figure 1 – Transmit Timing Options Diagram

ISSUE 2

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

#### PLLREF[1:0]:

The TJAT PLL reference select bits, PLLREF[1:0], select the source of the clock going into the TJAT digital PLL. The PLLREF[1:0] bits are also used to select between the transmit reference clocks and the receive clock, RCLK, in Master mode. Care must be taken to prevent PLLREF[1:0] from being set to "00" or "11" when EMODE[2:0] selects the master mode configuration. If EMODE is in master timing mode and PLLREF is set to "00" or "11" a timing loop will be formed and the clock will become unstable. The following table shows the settings for PLLREF[1:0]:

| PLLREF[1:0] | Selection                                                          |

|-------------|--------------------------------------------------------------------|

| 00          | Slave clock                                                        |

|             | <ul> <li>do not use with EMODE set to clock Master mode</li> </ul> |

| 01          | External Transmit reference                                        |

| 10          | Recovered Receive clock                                            |

| 11          | Reserved                                                           |

## **TJATPLLBYP**:

The TJATPLLBYP bit disables transmit transmit clock jitter attenuation. Transmit jitter attenuation may be unnecessary when the T1/E1 framer slice is configured for egress Clock Master modes and the reference clock is a line rate clock or when configured for Clock Slave: Clear Channel mode. Jitter attenuation must be used when additional jitter attenuation is required on the external transmit reference clock or when in clock slave mode and the slave clock is not at the line rate or it needs jitter attenuation.

#### **TJATFIFOBYP:**

The TJAT fifo bypass bit, TJATFIFOBYP, is used to remove the transmit jitter attenuator FIFO from the transmit data path. When transmit jitter attenuation is not being used as selected by the TJATPLLBYP register bit, setting TJATFIFOBYP to logic 1 will reduce the latency through the transmitter section by typically 40 bits.

### SBICLKMODE:

The SBI clock Mode bit, SBICLKMODE, selects the egress clocking mode used over the SBI bus. When SBICLKMODE is a logic 1 and the system interface is configured for the SBI interface, egress tributary clocking is set for Master mode. In this mode the TEMAP T1/E1 transmit clock is used to control the SBI tributary rate for this T1/E1. The CLK\_MSTR bit in the

PMC-Sierra

**ISSUE 2**

REGISTER DESCRIPTION PMC-1990682

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

corresponding EXSBI register must also be set to Master mode for correct operation. When SBICLKMODE is a logic 0 and the system interface is configured for the SBI bus, the egress T1/E1 clock is slaved to the T1/E1 rate from the tributary on the SBI bus. The CLK\_MSTR bit in the corresponding EXSBI register must also be set to Slave mode for correct operation. When the SBI bus is operating in Synchronous mode as selected by the SYNCSBI bit in the SBI Master Configuration register, this bit must be set to 0 corresponding to slave mode.

SBICLKMODE affects the transmit timing options as shown in Figure 1. When the SBI Add bus is set to master mode, SBICLKMODE is 1, the switch labeled EMODE[2] is in the "1" switch position.

The SBICLKMODE bit must be set before the tributaries within the SBI are enabled.

#### Reserved:

Bit 7 must be set to logic 0 and bit 6 must be set to logic 1 for proper operation of the TEMAP.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

# Register 0005H+80H\*N: T1/E1 Ingress Serial Interface Mode Select

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R/W  | Reserved | 0       |

| Bit 6 | R/W  | Reserved | 0       |

| Bit 5 | R/W  | Reserved | 0       |

| Bit 4 | R/W  | Reserved | 0       |

| Bit 3 | R/W  | Reserved | 0       |

| Bit 2 | R/W  | Reserved | 0       |

| Bit 1 | R/W  | IMODE1   | 0       |

| Bit 0 | R/W  | IMODE0   | 0       |

## **IMODE**:

The ingress clock mode bits, IMODE[1:0], determine which serial interface mode is being used for this tributary. These bits must be programmed to "11" for proper operation of the TEMAP, selecting the Clock Master: Clear Channel mode.

Table 1 - Ingress Serial Interface Mode Selection

| IMODE[1] | IMODE[0] | Operation                   |

|----------|----------|-----------------------------|

| 0        | 0        | Reserved                    |

| 0        | 1        | Reserved                    |

| 1        | 0        | Reserved                    |

| 1        | 1        | Clock Master: Clear Channel |

### Reserved:

This bit must be set to logic 0 for proper operation of the TEMAP.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

# Register 0006H+80H\*N: T1/E1 Egress Serial Interface Mode Select

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R/W  | Reserved | 0       |

| Bit 6 | R/W  | Reserved | 0       |

| Bit 5 | R/W  | Reserved | 0       |

| Bit 4 | R/W  | Reserved | 0       |

| Bit 3 | R/W  | Reserved | 0       |

| Bit 2 | R/W  | EMODE2   | 0       |

| Bit 1 | R/W  | EMODE1   | 0       |

| Bit 0 | R/W  | EMODE0   | 0       |

# EMODE:

The egress clock mode, EMODE, bit determines which serial interface mode is being used for this tributary.

The modes are listed in the following table:

Table 2 - Egress Serial Interface Mode Selection

| EMODE[2] | EMODE[1] | EMODE[0] | Operation                   |

|----------|----------|----------|-----------------------------|

| Х        | Χ        | 1        | Reserved                    |

| Х        | 0        | 0        | Reserved                    |

| 0        | 1        | 0        | Clock Slave: Clear Channel  |

| 1        | 1        | 0        | Clock Master: Clear Channel |

## Reserved:

This bit must be set to logic 0 for proper operation of the TEMAP.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

## Register 0009H+80H\*N: T1/E1 Serial Interface Configuration

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R/W  | Reserved | 0       |

| Bit 6 | R/W  | IDE      | 0       |

| Bit 5 | R/W  | Reserved | 0       |

| Bit 4 | R/W  | Reserved | 0       |

| Bit 3 | R/W  | Reserved | 0       |

| Bit 2 | R/W  | EDE      | 1       |

| Bit 1 | R/W  | Reserved | 0       |

| Bit 0 | R/W  | Reserved | 0       |

This register only affects the serial clock and data interface signals when enabled as the system interface via the SYSOPT[2:0] bits in the Global Configuration register.

### Reserved:

This bit must be set to logic 0 for proper operation of the TEMAP.

### EDE:

When EDE is set to logic 1, the ED[x] signal is sampled by the rising ECLK[x] edge. When EDE is set to logic 0, the ED[x] signal is sampled by the falling ECLK[x] edge.

### IDE:

When IDE is set to logic 1, the ID[x] signal is updated on the rising edge of ICLK[x]. When IDE is set to logic 0, the ID[x] signal is updated on the falling edge of ICLK[x].

**ISSUE 2**

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

# Register 000BH+80H\*N: T1/E1 Interrupt Source #1

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R    | RJAT     | 0       |

| Bit 6 | R    | TJAT     | 0       |

| Bit 5 | R    | Reserved | X       |

| Bit 4 | R    | Reserved | Х       |

| Bit 3 | R    | Reserved | Х       |

| Bit 2 | R    | Reserved | Х       |

| Bit 1 | R    | T1E1FRMR | 0       |

| Bit 0 | R    | PMON     | 0       |

This register allows software to determine the block which produced the interrupt on the INTB output pin.

Reading this register does not remove the interrupt indication; the corresponding block's interrupt status register must be read to remove the interrupt indication.

PMC-1990682

**ISSUE 2**

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

# Register 000CH+80H\*N: T1/E1 Interrupt Source #2

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R    | Reserved | X       |

| Bit 6 | R    | PRBS     | 0       |

| Bit 5 | R    | Reserved | Х       |

| Bit 4 | R    | Reserved | Х       |

| Bit 3 | R    | Reserved | Х       |

| Bit 2 | R    | ALMI     | 0       |

| Bit 1 |      | Unused   | Х       |

| Bit 0 | R    | Reserved | Х       |

This register allows software to determine the block that produced the interrupt on the INTB output pin.

Reading this register does not remove the interrupt indication; the corresponding block's interrupt status register must be read to remove the interrupt indication.

**ISSUE 2**

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

## Register 000DH+80H\*N: T1/E1 Diagnostics

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 |      | Unused   | Х       |

| Bit 6 |      | Unused   | Х       |

| Bit 5 | R/W  | Reserved | 0       |

| Bit 4 | R/W  | LLOOP    | 0       |

| Bit 3 | R/W  | RAIS     | 0       |

| Bit 2 | R/W  | DLOOP    | 0       |

| Bit 1 | R/W  | Reserved | 0       |

| Bit 0 |      | Unused   | Х       |

#### Reserved:

This bit must be set to logic 0 for proper operation of the TEMAP.

### **DLOOP**:

The DLOOP bit selects the digital diagnostic loopback mode, where the TEMAP is configured to internally direct the output of the TJAT to the input of the RJAT. When DLOOP is set to logic 1, the digital diagnostic loopback mode is enabled. When DLOOP is set to logic 0, the digital diagnostic loopback mode is disabled. The RJATBYP or TJATBYP register bits can be used to bypass the ingress and egress jitter attenuators to decrease delay.

## RAIS:

When a logic 1, the RAIS bit forces all ones into the ingress data stream. The ingress data stream will freeze at the current valid signaling.

#### LLOOP:

The LLOOP bit selects the line loopback mode, where the recovered data are internally directed downstream of the FIFO of the transmit jitter attenuator. When LLOOP is set to logic 1, the line loopback mode is enabled. When LLOOP is set to logic 0, the line loopback mode is disabled.

### Reserved:

This bit must be set to logic 0 for proper operation of the TEMAP.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

## Register 000EH+80H\*N: T1/E1 PRBS Positioning and Control

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 |      | Unused   | Х       |

| Bit 6 |      | Unused   | Х       |

| Bit 5 | R/W  | Reserved | 0       |

| Bit 4 | R/W  | Reserved | 0       |

| Bit 3 | R/W  | Reserved | 0       |

| Bit 2 | R/W  | RXPATGEN | 0       |

| Bit 1 | R/W  | UNF_GEN  | 0       |

| Bit 0 | R/W  | UNF_DET  | 0       |

This register modifies the way in which the PRBS generator/checker is used.

## **UNF DET**

When the Unframed Pattern Detection bit, UNF\_DET, is set to logic 1, the PRBS Checker will search for the pattern in all 193 bits/256 bits of the transmit or receive stream, depending on the setting of RXPATGEN. This bit must be set to logic 1 for proper detection of PRBS sequences.

### UNF GEN

When the Unframed Pattern Generation bit, UNF\_GEN, is set to logic 1, the PRBS Generator will overwrite all 193 bits/256 bits in every frame in the direction specified by the RXPATGEN bit. This bit must be set to logic 1 for proper generation of PRBS sequences.

### RXPATGEN:

The Receive Pattern Generate, RXPATGEN, bit controls the location of the PRBS generator/detector. When RXPATGEN is set to logic 1, the PRBS generator is inserted in the ingress receive path and the PRBS checker is inserted in the egress transmit path. Payload from the receive line may be overwritten with generated PRBS patterns before appearing on the receive system interface, and timeslots from the transmit system interface may be checked for the generated pattern before appearing on the transmit line. Note that this mode requires an appropriate receive line clock (RCLK when in DS3 LIU mode or LREFCLK when in DS3/T1/E1 mapper mode) for proper insertion of the PRBS sequence. Alternatively, the PRBS generator can clocked by the T1/E1 transmit clock when DLOOP is set to logic 1 in Register

REGISTER DESCRIPTION PMC-1990682

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

00DH +80H\*N - T1/E1 Diagnostics. When inserting framed PRBS from the receiver per channel serial controller, the tributary needs to be in frame.

When RXPATGEN is set to logic 0, the PRBS detector is inserted in the ingress receive path and the PRBS generator is inserted in the egress transmit path. Payload from the transmit system interface may be overwritten with generated PRBS patterns before appearing on the transmit line, and timeslots from the receive line may be checked for the generated pattern before appearing on the receive system interface.

### Reserved:

This bit must be set to logic 0 for proper operation of the TEMAP.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

## 1.3 RJAT Receive Jitter Attenuator Registers (N=1 to 28)

## Register 0010H+80H\*N: RJAT Interrupt Status

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 |      | Unused   | Х       |

| Bit 6 |      | Unused   | Х       |

| Bit 5 |      | Unused   | Х       |

| Bit 4 |      | Unused   | Х       |

| Bit 3 |      | Unused   | Х       |

| Bit 2 |      | Unused   | Х       |

| Bit 1 | R    | OVRI     | Х       |

| Bit 0 | R    | UNDI     | Х       |

### UNDI:

The UNDI bit is asserted when an attempt is made to read data from the receive FIFO when the FIFO is already empty. When UNDI is a logic 1, an underrun event has occurred. Reading this register will clear the UNDI bit to logic 0.

### OVRI:

The OVRI bit is asserted when an attempt is made to write data into the receive FIFO when the FIFO is already full. When OVRI is a logic 1, an overrun event has occurred. Reading this register will clear the OVRI bit to logic 0.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

# Register 0011H+80H\*N: RJAT Reference Clock Divider N1 Control

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R/W  | N1[7]    | 0       |

| Bit 6 | R/W  | N1[6]    | 0       |

| Bit 5 | R/W  | N1[5]    | 1       |

| Bit 4 | R/W  | N1[4]    | 0       |

| Bit 3 | R/W  | N1[3]    | 1       |

| Bit 2 | R/W  | N1[2]    | 1       |

| Bit 1 | R/W  | N1[1]    | 1       |

| Bit 0 | R/W  | N1[0]    | 1       |

This register contains an 8-bit binary number, N1, which is one less than the magnitude of the reference clock divisor. The reference divisor magnitude, (N1+1), is the ratio between the frequency of the recovered clock (or the transmit clock if a diagnostic loopback is enabled) and the frequency at the phase discriminator input.

Writing to this register will reset the PLL.

The default value of N1 after a device reset is 47 = 2FH.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

# Register 0012H+80H\*N: RJAT Output Clock Divider N2 Control

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R/W  | N2[7]    | 0       |

| Bit 6 | R/W  | N2[6]    | 0       |

| Bit 5 | R/W  | N2[5]    | 1       |

| Bit 4 | R/W  | N2[4]    | 0       |

| Bit 3 | R/W  | N2[3]    | 1       |

| Bit 2 | R/W  | N2[2]    | 1       |

| Bit 1 | R/W  | N2[1]    | 1       |

| Bit 0 | R/W  | N2[0]    | 1       |

This register contains an 8-bit binary number, N2, which is one less than the magnitude of the output clock divisor. The output clock divisor magnitude, (N2+1), is the ratio between the frequency of the smooth output clock, ID[x], and the frequency applied to the phase discriminator input.

Writing to this register will reset the PLL.

The default value of N2 after a device reset is 47 = 2FH.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

## Register 0013H+80H\*N: RJAT Configuration

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 |      | Unused   | Х       |

| Bit 6 |      | Unused   | Х       |

| Bit 5 | R/W  | Reserved | 1       |

| Bit 4 | R/W  | CENT     | 0       |

| Bit 3 | R/W  | UNDE     | 0       |

| Bit 2 | R/W  | OVRE     | 0       |

| Bit 1 | R/W  | SYNC     | 1       |

| Bit 0 | R/W  | LIMIT    | 1       |

Please note that the TEMAP start-up procedure in the TEMUX/TEMAP Programmer's Guide should be referenced for correct sequencing of the jitter attenuators.

### CENT:

The CENT bit allows the FIFO to self-center its read pointer, maintaining the pointer at least 4 UI away from the FIFO being empty or full. When CENT is set to logic 1, the FIFO is enabled to self-center for the next 384 transmit data bit period, and for the first 384 bit periods following an overrun or underrun event. If an EMPTY or FULL alarm occurs during this 384 UI period, the period will be extended by the number of UI that the EMPTY or FULL alarm persists. During the EMPTY or FULL alarm conditions, data is lost. When CENT is set to logic 0, the self-centering function is disabled, allowing the data to pass through uncorrupted during EMPTY or FULL alarm conditions. It is recommended to set this bit to 1.

The CENT bit can only be set to logic 1 if the SYNC bit is set to logic 0.

### **UNDE:**

Setting the UNDE bit to logic 1 enables an underrun event to assert the INTB output low.

#### OVRE:

Setting the OVRE bit to logic 1 enables an overrun event to assert the INT output low.

**ISSUE 2**

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

### SYNC:

The SYNC bit enables the PLL to synchronize the phase delay between the FIFO input and output data to the phase delay between reference clock input and smooth output clock at the PLL. For example, if the PLL is operating so that the smooth output clock lags the reference clock by 24 UI, then the synchronization pulses that the PLL sends to the FIFO will force its output data to lag its input data by 24 UI. When SYNC is set to logic 1, then the RJAT divisors (N1 and N2) must be set so that N1+1 is a multiple of 48 decimal, and N2+1 is a multiple of 48 decimal.

#### LIMIT:

Setting the LIMIT bit to logic 1 will limit the PLL jitter attenuation by enabling the FIFO to increase or decrease the frequency of the smooth output clock whenever the FIFO is within one UI of overflowing or underflowing. This limiting of jitter ensures that no data is lost during high phase shift conditions. When LIMIT is set to logic 0, underflows and overflows may occur.

## Reserved:

This bit must be programmed to logic 1 for future compatibility.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

## 1.4 TJAT Transmit Jitter Attenuator Registers (N=1 to 28)

## Register 0014H+80H\*N: TJAT Interrupt Status

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 |      | Unused   | Х       |

| Bit 6 |      | Unused   | Х       |

| Bit 5 |      | Unused   | Х       |

| Bit 4 |      | Unused   | Х       |

| Bit 3 |      | Unused   | Х       |

| Bit 2 |      | Unused   | Х       |

| Bit 1 | R    | OVRI     | Х       |

| Bit 0 | R    | UNDI     | Х       |

### UNDI:

The UNDI bit is asserted when an attempt is made to read data from the transmit FIFO when the FIFO is already empty. When UNDI is a logic 1, an underrun event has occurred. Reading this register will clear the UNDI bit to logic 0.

### OVRI:

The OVRI bit is asserted when an attempt is made to write data into the transmit FIFO when the FIFO is already full. When OVRI is a logic 1, an overrun event has occurred. Reading this register will clear the OVRI bit to logic 0.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

# Register 0015H+80H\*N: TJAT Jitter Attenuator Divider N1 Control

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R/W  | N1[7]    | 0       |

| Bit 6 | R/W  | N1[6]    | 0       |

| Bit 5 | R/W  | N1[5]    | 1       |

| Bit 4 | R/W  | N1[4]    | 0       |

| Bit 3 | R/W  | N1[3]    | 1       |

| Bit 2 | R/W  | N1[2]    | 1       |

| Bit 1 | R/W  | N1[1]    | 1       |

| Bit 0 | R/W  | N1[0]    | 1       |

This register contains an 8-bit binary number, N1, which is one less than the magnitude of the reference clock divisor. The reference divisor magnitude, (N1+1), is the ratio between the frequency of the reference clock (as selected by the PLLREF1 and PLLREF0 bits of the Egress Interface Configuration register) and the frequency at the phase discriminator input.

Writing to this register will reset the PLL.

The default value of N1 after a device reset is 47 = 2FH.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

# Register 0016H+80H\*N: TJAT Divider N2 Control

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R/W  | N2[7]    | 0       |

| Bit 6 | R/W  | N2[6]    | 0       |

| Bit 5 | R/W  | N2[5]    | 1       |

| Bit 4 | R/W  | N2[4]    | 0       |

| Bit 3 | R/W  | N2[3]    | 1       |

| Bit 2 | R/W  | N2[2]    | 1       |

| Bit 1 | R/W  | N2[1]    | 1       |

| Bit 0 | R/W  | N2[0]    | 1       |

This register contains an 8-bit binary number, N2, which is one less than the magnitude of the output clock divisor. The output clock divisor magnitude, (N2+1), is the ratio between the frequency of the smooth output clock and the frequency applied to the phase discriminator input.

Writing to this register will reset the PLL.

The default value of N2 after a device reset is 47 = 2FH.

ISSUE 2

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

## Register 0017H+80H\*N: TJAT Configuration

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 |      | Unused   | Х       |

| Bit 6 |      | Unused   | Х       |

| Bit 5 | R/W  | Reserved | 1       |

| Bit 4 | R/W  | CENT     | 0       |

| Bit 3 | R/W  | UNDE     | 0       |

| Bit 2 | R/W  | OVRE     | 0       |

| Bit 1 | R/W  | SYNC     | 1       |

| Bit 0 | R/W  | LIMIT    | 1       |

#### CENT:

The CENT bit allows the FIFO to self-center its read pointer, maintaining the pointer at least 4 UI away from the FIFO being empty or full. When CENT is set to logic 1, the FIFO is enabled to self-center for the next 384 transmit data bit period, and for the first 384 bit periods following an overrun or underrun event. If an EMPTY or FULL alarm occurs during this 384 UI period, the period will be extended by the number of UI that the EMPTY or FULL alarm persists. During the EMPTY or FULL alarm conditions, data is lost. When CENT is set to logic 0, the self-centering function is disabled, allowing the data to pass through uncorrupted during EMPTY or FULL alarm conditions. It is recommended to set this bit to 1.

The CENT bit can only be set to logic 1 if the SYNC bit is set to logic 0.

#### UNDE:

Setting the UNDE bit to logic 1 enables an underrun event to assert the INTB output low.

### **OVRE:**

Setting the OVRE bit to logic 1 enables an overrun event to assert the INT output low.

#### SYNC:

The SYNC bit enables the PLL to synchronize the phase delay between the FIFO input and output data to the phase delay between reference clock input and smooth output clock at the PLL. For example, if the PLL is operating so

PMC-Sierra

**ISSUE 2**

REGISTER DESCRIPTION PMC-1990682

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

that the smooth output clock lags the reference clock by 24 UI, then the synchronization pulses that the PLL sends to the FIFO will force its output data to lag its input data by 24 UI. When using the 2Mbit/s transmit backplane option, the SYNC bit must be set to logic 0. When SYNC is set to logic 1, then the TJAT divisors (N1 and N2) must be set so that N1+1 is a multiple of 48 decimal, and N2+1 is a multiple of 48 decimal.

SYNC must only be set to logic 1 when The Egress Interface is in a Clock Slave mode (PLLREF[1:0] = 00 in Register 004H+80H\*N)

#### LIMIT:

Setting the LIMIT bit to logic 1 will limit the PLL jitter attenuation by enabling the FIFO to increase or decrease the frequency of the smooth output clock whenever the FIFO is within one UI of overflowing or underflowing. This limiting of jitter ensures that no data is lost during high phase shift conditions. When LIMIT is set to logic 0, underflows and overflows may occur.

## Reserved:

The Reserved bit must be programmed to logic 1 for future compatibility.

REGISTER DESCRIPTION

PMC-1990682

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

# 1.5 PMON Performance Monitor Registers (N=1 to 28)

## Register 0038H+80H\*N: PMON Interrupt Enable/Status

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 |      | Unused   | Х       |

| Bit 6 |      | Unused   | Х       |

| Bit 5 |      | Unused   | Х       |

| Bit 4 |      | Unused   | Х       |

| Bit 3 |      | Unused   | Х       |

| Bit 2 | R/W  | INTE     | 0       |

| Bit 1 | R    | XFER     | 0       |

| Bit 0 | R    | OVR      | 0       |

This register contains status information indicating when counter data has been transferred into the holding registers and indicating whether the holding registers have been overrun.

#### INTE:

The INTE bit controls the generation of a microprocessor interrupt when the transfer clock has caused the counter values to be stored in the holding registers. A logic 1 bit in the INTE position enables the generation of an interrupt via the INTB output; a logic 0 bit in the INTE position disables the generation of an interrupt.

## XFER:

The XFER bit indicates that a transfer of counter data has occurred. A logic 1 in this bit position indicates that a latch request, initiated by writing to one of the counter register locations or the Global PMON Update register, was received and a transfer of the counter values has occurred. A logic 0 indicates that no transfer has occurred. The XFER bit is cleared (acknowledged) by reading this register.

### OVR:

The OVR bit is the overrun status of the holding registers. A logic 1 in this bit position indicates that a previous transfer (indicated by XFER being logic 1) has not been acknowledged before the next transfer clock has been issued and that the contents of the holding registers have been overwritten. A logic 0

REGISTER DESCRIPTION PMC-1990682

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

indicates that no overrun has occurred. The OVR bit is cleared by reading this register.

### Registers 0038H+80H\*N -003DH+80H\*N: Latching Performance Data

The Performance Data registers for a single framer are updated as a group by writing to any of the PMON count registers (Framing Bit Error count register, OOF/COFA/Fare End Block Error count register or Bit Error/CRCE Error count register). A write to one (and only one) of these locations loads performance data located in the PMON into the internal holding registers. Alternatively, the Performance Data registers are updated by writing to the Revision / Global PMON Update register (address 0002H). The data contained in the holding registers can then be subsequently read by microprocessor accesses into the PMON count register address space. The latching of count data, and subsequent resetting of the counters, is synchronized to the internal event timing so that no events are missed.

The PMON is loaded with new performance data within 3.5 recovered clock periods of the latch performance data register write. With nominal line rates, the PMON registers should not be polled until 2.3 µsec have elapsed from the "latch performance data" register write.

When the TEMAP is reset, the contents of the PMON count registers are unknown until the first latching of performance data is performed.

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

## Register 0039H+80H\*N: PMON Framing Bit Error Count

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 |      | Unused   | Х       |

| Bit 6 | R    | FER[6]   | Х       |

| Bit 5 | R    | FER[5]   | Х       |

| Bit 4 | R    | FER[4]   | Х       |

| Bit 3 | R    | FER[3]   | Х       |

| Bit 2 | R    | FER[2]   | Х       |

| Bit 1 | R    | FER[1]   | Х       |

| Bit 0 | R    | FER[0]   | X       |

### FER[6:0]:

The FER[6:0] bits indicate the number of framing bit error events that occurred during the previous accumulation interval. The FER counts are suppressed when the framer has lost frame alignment (OOF in the E1-FRMR Framing Status register is logic 1 or INFR in the T1-FRMR Interrupt Status register is logic 0).

In T1 mode, a framing bit error is defined as an F<sub>e</sub>-bit error in ESF mode or a framing bit error in SF mode.

In E1 mode, the count is either the number of FAS (frame alignment signal) bits (default) or words in error. As an option, a zero in bit 2 of time slot 0 of non-frame alignment signal (NFAS) frames results in an increment of the framing error count. Refer to the Receive Options register.

**ISSUE 2**

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER

## Register 003AH+80H\*N: PMON OOF/COFA/Far End Block Error Count LSB

| Bit   | Туре | Function    | Default |

|-------|------|-------------|---------|

| Bit 7 | R    | OOF/FEBE[7] | Х       |

| Bit 6 | R    | OOF/FEBE[6] | Х       |

| Bit 5 | R    | OOF/FEBE[5] | Х       |

| Bit 4 | R    | OOF/FEBE[4] | Х       |

| Bit 3 | R    | OOF/FEBE[3] | Х       |

| Bit 2 | R    | OOF/FEBE[2] | Х       |

| Bit 1 | R    | OOF/FEBE[1] | Х       |

| Bit 0 | R    | OOF/FEBE[0] | Х       |

# Register 003BH+80H\*N: PMON OOF/COFA/Far End Block Error Count MSB

| Bit   | Туре | Function    | Default |

|-------|------|-------------|---------|

| Bit 7 |      | Unused      | Х       |

| Bit 6 |      | Unused      | Х       |

| Bit 5 |      | Unused      | Х       |

| Bit 4 |      | Unused      | Х       |

| Bit 3 |      | Unused      | Х       |

| Bit 2 |      | Unused      | Х       |

| Bit 1 | R    | OOF/FEBE[9] | Х       |

| Bit 0 | R    | OOF/FEBE[8] | Х       |

## OOF/FEBE[9:0]:

In T1 mode, the OOF[9:0] bits indicate the number Out Of Frame or Change Of Frame Alignment events that occurred during the previous accumulation interval, as specified by the CCOFA bit in the Receive Options register. If OOFs are being accumulated, the count is incremented each time a severely errored framing event forces a reframe. IF COFAs are being accumulated, the count is incremented if a new alignment differs from the previous alignment.

In E1 mode, the FEBE[9:0] bits indicate the number of far end block error events that occurred during the previous accumulation interval. The FEBE

REGISTER DESCRIPTION

PMC-1990682

HIGH DENSITY VT/TU MAPPER AND M13 MULTIPLEXER