# μ**PD75336**

# **4-BIT SINGLE-CHIP MICROCOMPUTER**

μPD75336 μPD75P338

© NEC Corporation 1991

6427525 0094844 68T **8**

This Material Copyrighted By Its Respective Manufacturer

#### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

The devices listed in this document are not suitable for use in aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. If customers intend to use NEC devices for above applications or they intend to use "Standard" quality grade NEC devices for applications not intended by NEC, please contact our sales people in advance.

Application examples recommended by NEC Corporation

Standard: Computer, Office equipment, Communication equipment, Test and Measurement equipment, Machine tools, Industrial robots, Audio and Visual equipment, Other consumer products, etc.

Special: Automotive and Transportation equipment, Traffic control systems, Antidisaster systems, Anticrime systems, etc.

M7 92.6

💶 6427525 0094845 516 🎟

# Major Revisions in This Edition

| Location        | Description                                                                                           |

|-----------------|-------------------------------------------------------------------------------------------------------|

| Whole<br>manual | uPD75P336GK Under development → Development<br>completed                                              |

| 1-6             | Amendment of Table 1-1 "Differences between<br>uPD75336 and uPD75P336"                                |

| 2-13            | 2.2.10 INTO, INT1<br>Addition of text covering STOP mode and HALT mode<br>release                     |

| 2-14            | 2.2.11 INT2<br>Addition of text covering STOP mode and HALT mode<br>release                           |

| 2-18            | Amendment of 2.2.26 IC (uPD75336 only) item                                                           |

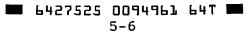

| 5-7             | Amendment of Figure 5-3 "Configurations of Ports 3n and 6n"                                           |

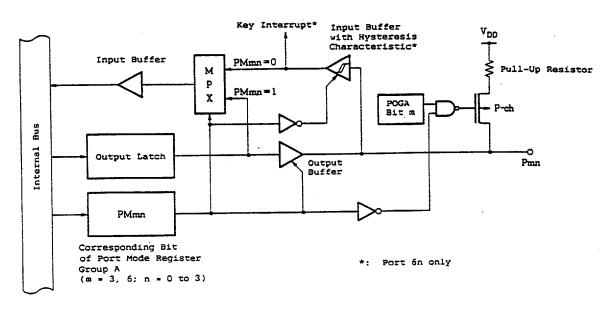

| 5-7             | Amendment of Figure 5-4 "Configurations of Ports 2<br>and 7                                           |

| 5-8             | Addition of cautions to Table 5-5 "Maximum Time<br>Required for System Clock and CPU Clock Switching" |

| 6-6             | Amendment of text in 6.3 (1) "Interrupt request flags<br>& interrupt enable flags"                    |

| 8-1             | Amendment of Table 8-1 "Hardware Status after Reset"                                                  |

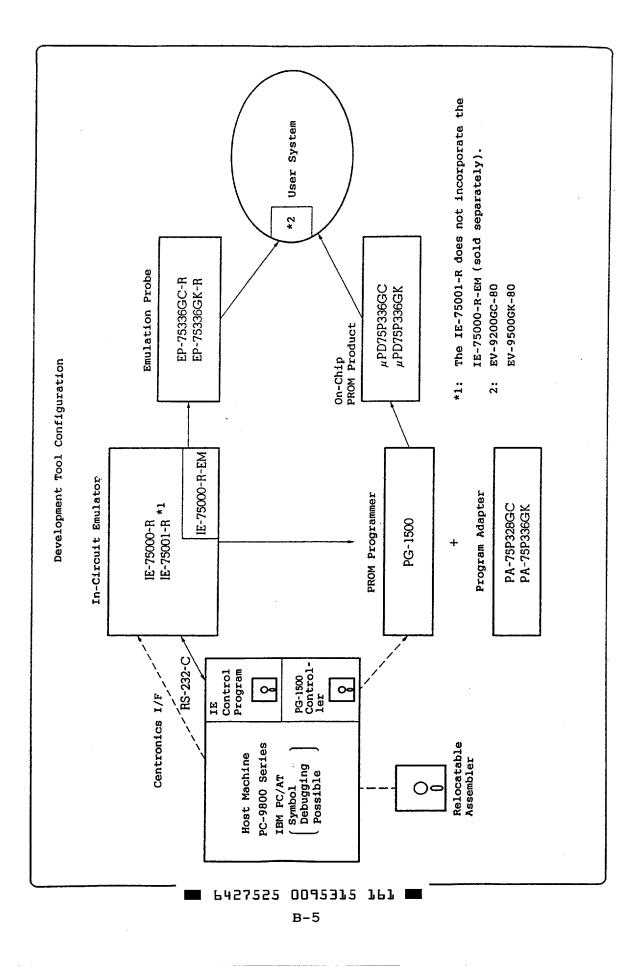

| B-1             | Appendix B "Development Tools" Version upgrade of relevant MS-DOS (Ver. 5.00/5.00A)                   |

- i -• 6427525 0094846 452 🎟 PREFACE

Intended

Readership : This manual is intended for user engineers who understand the uPD75336 and uPD75P336 functions and wish to design an application system with those functions.

Purpose : This manual has been prepared to enable the users to have an understanding of the uPD75336 and uPD75P336 hardware functions.

How to Read

- this Manual: Readers of this manual are required to have a general knowledge of electric and logic circuits and microcomputers.

- . Users who have previously used the uPD75328

- → The basic functions are the same. The uPD75336 can be used as the 16K version of the uPD75328. The uPD75336 has an improved CPU (instructions and registers) and timer. Refer to Appendix A. "Functional comparison of uPD75336, uPD75P336 and uPD75328" for details of additional functions and instructions.

- . Users who use this manual for the uPD75P336

- → Unless there are functional differences, this manual describes the uPD75336 as a representative type. After checking the functional differences by referring to Section 1.3 "Differences between uPD75336 and uPD75P336", use this manual by replacing "uPD75336" with "uPD75P336".

- ii -• 6427525 0094847 399 •

- . When checking instruction functions with knowledge of mnemonics

- > Refer to Appendix D.2 "Instruction Index

(in Alphabetical Order)".

- . When checking instructions with understanding of functions but not mnemonics

- Check the mnemonics of functions by referring to Section 10.2 "Instruction Set and Operations" and then check the functions by referring to Section 10.4 "Instruction Functions and Use".

- . When having an understanding of uPD75336 and uPD75P336

- After checking the main functions by referring to Section 1.1 "Function Outline", read this manual in the order of the contents.

- . For the electrical specifications of the uPD75336/75P336

→ See the separate Data Sheet.

- iii -■ 6427525 0094848 225 ■

This Material Copyrighted By Its Respective Manufacturer

| Legend | : | Data representation | ns: | Most significant digit on<br>the left and least<br>significant digit on the<br>right |

|--------|---|---------------------|-----|--------------------------------------------------------------------------------------|

|        |   | Active-low          |     |                                                                                      |

|        |   | representations     | :   | $\overline{xxx}$ (line above pin and                                                 |

|        |   |                     |     | signal names)                                                                        |

|        |   | Memory map address  | :   | Upper - low, lower - high                                                            |

|        |   | *                   | :   | Description of * in the text                                                         |

|        |   | NOTE                | :   | Contents to be read with                                                             |

|        |   |                     |     | particular attention                                                                 |

|        |   | Remarks             | :   | Supplementary description of                                                         |

|        |   |                     |     | text                                                                                 |

|        |   | Numeric             |     |                                                                                      |

|        |   | representations     | :   | Binary number xxxx                                                                   |

|        |   |                     |     | or xxxxB                                                                             |

|        |   |                     |     | Decimal number xxxx                                                                  |

|        |   |                     |     | Hexadecimal number xxxxH                                                             |

|        |   |                     |     |                                                                                      |

Relevant Documents

$\sim$

Device Documentation

| Product                        | uPD75336    | uPD75P336 |  |  |

|--------------------------------|-------------|-----------|--|--|

| Document                       |             |           |  |  |

| Data Sheet                     | IC-7972     | IC-8371   |  |  |

| User's Manual                  | This manual |           |  |  |

| Instruction Operation<br>Table | IEM-5516    |           |  |  |

| 75X Series<br>Selection Guide  | IF-151      |           |  |  |

■ 6427525 0094849 161 ■ - iv - Development Tool Documentation

|                  | Document Name                       | Document No.     |           |

|------------------|-------------------------------------|------------------|-----------|

| н<br>а           | IE-75000-R/IE-75001-R               | EEU-846          |           |

| r                | IE-75000-R-EM User's                | EEU-673          |           |

| w<br>a<br>r<br>e | EP-75336GC-R User's M               | EEU-691          |           |

|                  | EP-75336GK-R User's M               | EEU-837          |           |

|                  | PG-1500 User's Manual               | EEU-651          |           |

| S<br>O           | RA75X<br>Assembler Package          | Operation Volume | · EEU-731 |

| f<br>t           | User's Manual                       | Language Volume  | EEU-730   |

| w<br>a<br>r<br>e | PG-1500 Controller<br>User's Manual | EEU-704          |           |

Other Documentation

| Document Name                                                       | Document No. |

|---------------------------------------------------------------------|--------------|

| Package Manual                                                      | IEI-635      |

| Semiconductor Device Mounting Manual                                | IEI-616      |

| NEC Semiconductor Device Quality Standards                          | IEI-620      |

| NEC Semiconductor Device Reliability and<br>Quality Control         | IEM-5068     |

| Electrostatic Discharge (ESD) Testing                               | MEM-539      |

| Semiconductor Device Quality Assurance Guide                        | MEI-603      |

| Microcomputer Related Product Guide<br>- Other Manufacturers Volume | MEI-604      |

NOTE: The contents of the above documents are subject to change without notice. Please ensure that the latest versions are used for design work, etc.

■ 6427525 0094850 983 ■ - v -

#### CONTENTS

| CHAPTER 1. | OVERVIEW                                  | . 1-1 |

|------------|-------------------------------------------|-------|

| 1.1 F      | unction Outline                           | 1-3   |

|            | rdering Information and Quality Grade     |       |

|            | ifferences between uPD75336 and uPD75P336 |       |

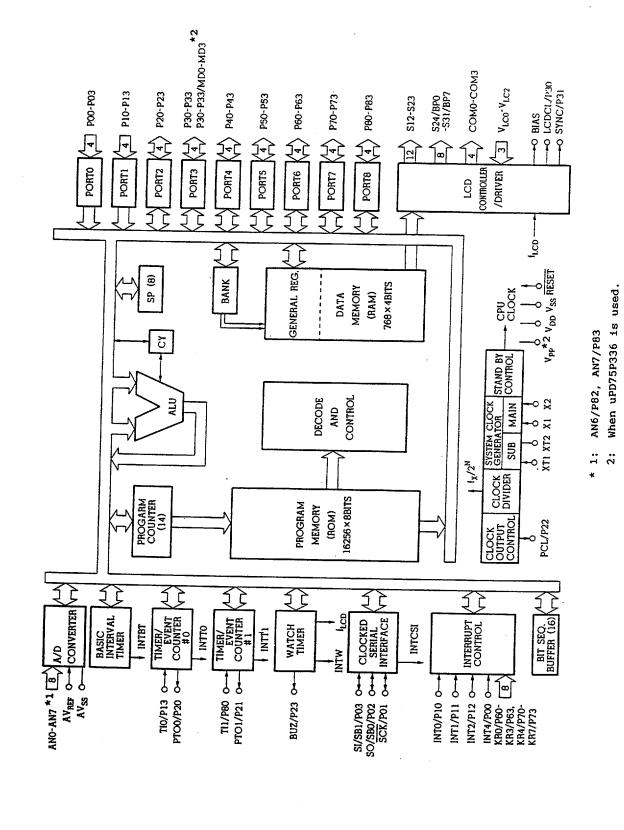

|            | lock Diagram                              |       |

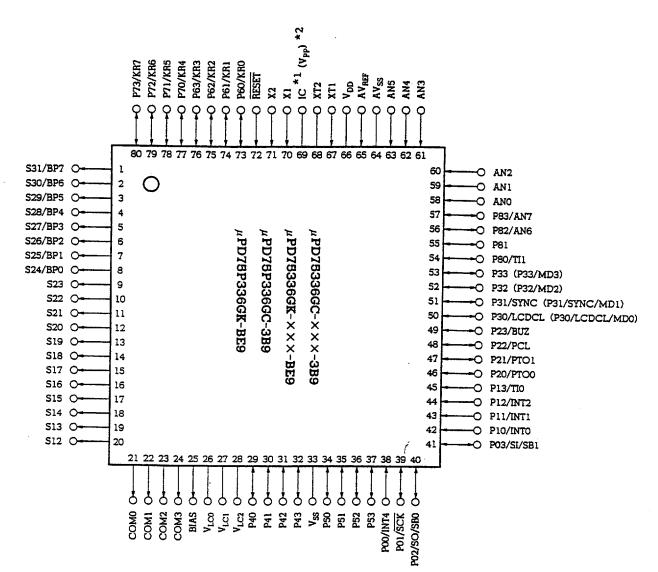

|            | in Configuration                          |       |

|            |                                           | 1 2   |

| CHAPTER 2. | PIN FUNCTIONS                             | 2-1   |

| 2.1 L      | ist of uPD75336 Pin Functions             | 2-1   |

|            | escription of Pin Functions               |       |

| 2.2.1      | P00 to P03 (PORTO), P10 to P13 (PORT1)    |       |

| 2.2.2      | P20 to P23 (PORT2), P30 to P33 (PORT3),   |       |

|            | P40 to P43 (PORT4), P50 to P53 (PORT5),   |       |

|            | P60 to P63 (PORT6), P70 to P73 (PORT7),   |       |

|            | P80 to P83 (PORT8)                        | 2-10  |

| 2.2.3      | BP0 to BP7                                | 2-11  |

| 2.2.4      | TIO, TI1                                  | 2-11  |

| 2.2.5      | PT00, PT01                                | 2-11  |

| 2.2.6      | PCL                                       | 2-12  |

| 2.2.7      | BUZ                                       | 2-12  |

| 2.2.8      | SCK, SO/SBO, SI/SB1                       | 2-12  |

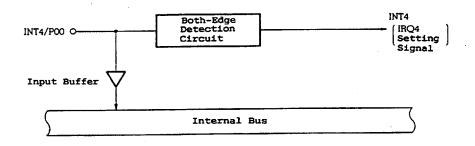

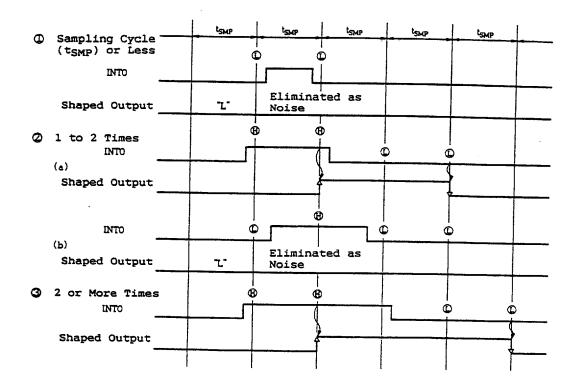

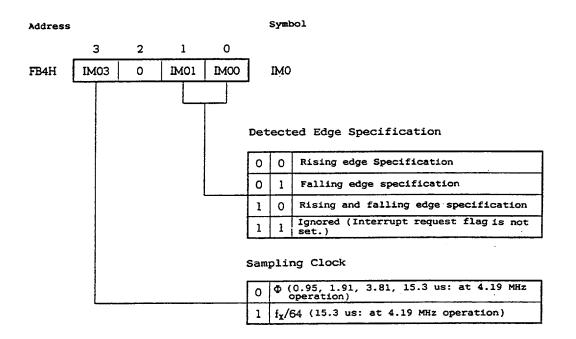

| 2.2.9      | INT4                                      |       |

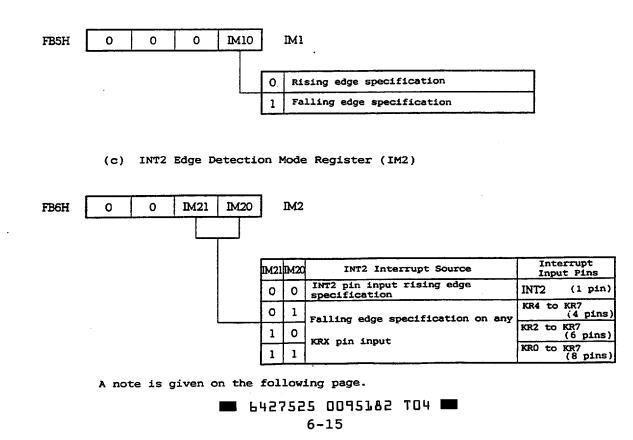

| 2.2.10     | INTO, INT1                                | 2-13  |

| 2.2.11     | INT2                                      | 2-14  |

| 2.2.12     | KRO to KR3, KR4 to KR7                    | 2-15  |

| 2.2.13     | S12 to S23, S24 to S31                    |       |

| 2.2.14     | COMO to COM3                              | 2-15  |

| 2.2.15     | $v_{LC0}$ to $v_{LC2}$                    |       |

| 2.2.16     | BIAS                                      |       |

| 2.2.17     | LCDCL                                     |       |

| 2.2.18     | SYNC                                      |       |

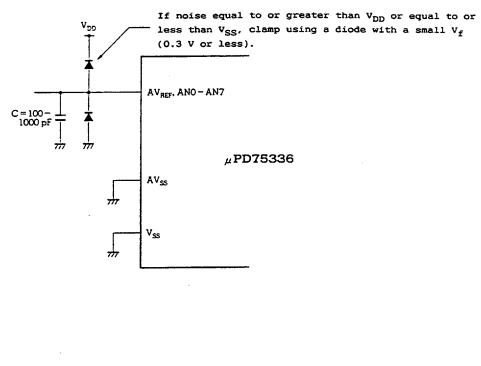

| 2.2.19     | ANO to AN5, AN6 & AN7                     | 2-16  |

| 2.2.20     | AV <sub>REF</sub>                         | 2-16  |

| 2.2.21     | AV <sub>SS</sub>                          | 2-16  |

- vi -6427525 0094851 81T 🎟

| 2.2.22 X1             | , X2                                        | 2-17 |

|-----------------------|---------------------------------------------|------|

| 2.2.23 XT             | 1, XT2                                      | 2-17 |

| 2.2.24 RE             | SET                                         | 2-18 |

| 2.2.25 MD             | 0 to MD3 (uPD75P336 Only)                   | 2-18 |

| 2.2.26 IC             | (uPD75P336 Only)                            | 2-18 |

| 2.2.27 V <sub>P</sub> | p (uPD75P336 Only)                          | 2-19 |

| 2.2.28 V <sub>D</sub> | D                                           | 2-19 |

| 2.2.29 V <sub>S</sub> | s ••••••••••••••••••••••••••••••••••••      | 2-19 |

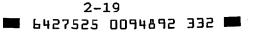

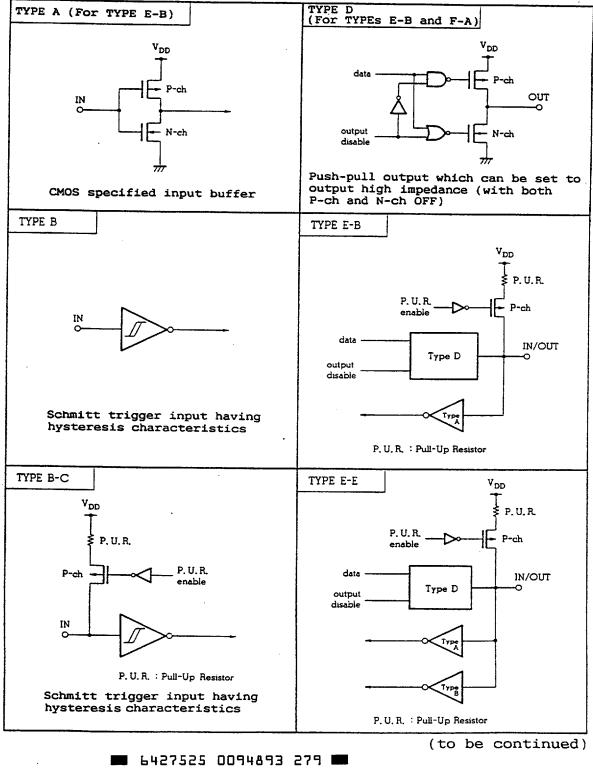

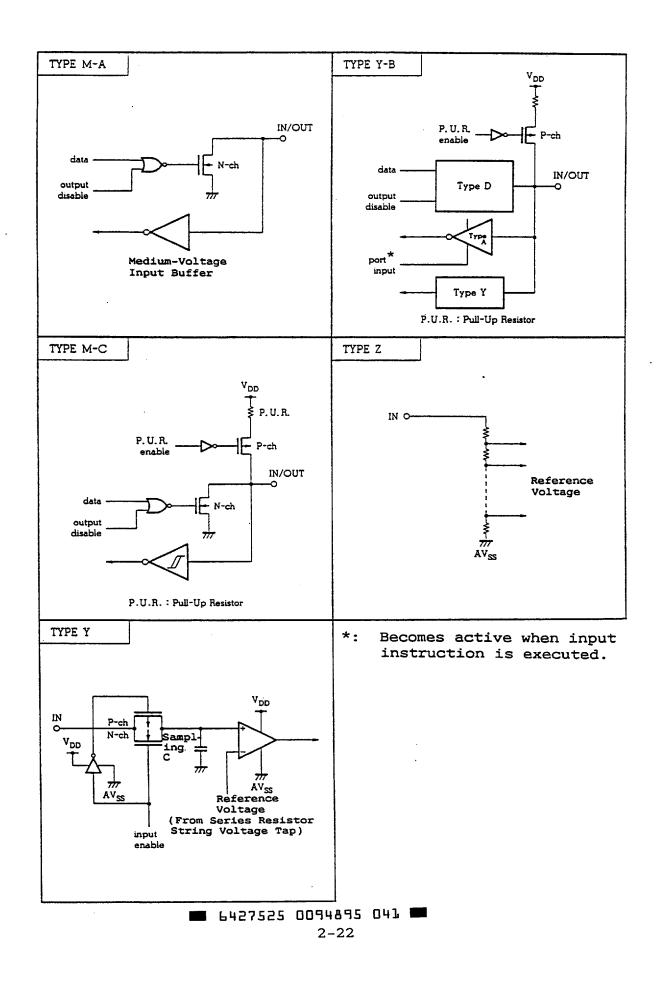

| 2.3 Pin I             | nput/Output Circuits                        | 2-20 |

| 2.4 Recom             | mended Connection of Unused Pins            | 2-23 |

| 2.5 Mask              | Option Selection                            | 2-24 |

| •                     |                                             |      |

| CHAPTER 3. DA         | TA MEMORY OPERATION AND MEMORY MAP          | 3-1  |

|                       |                                             |      |

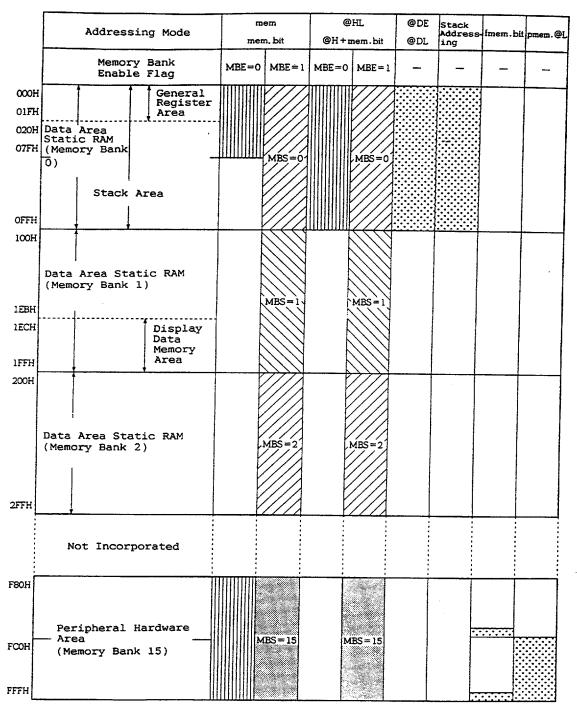

|                       | Memory Bank Configuration and Addressing    |      |

| Mode                  | • • • • • • • • • • • • • • • • • • • •     | 3-2  |

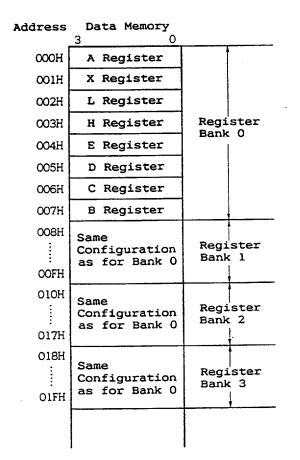

| 3.1.1 Da              | ta Memory Bank Configuration                | 3-2  |

|                       | ta Memory Addressing Mode                   |      |

|                       | al Register Bank Configuration              |      |

| 3.3 Memory            | y Mapped I/O                                | 3-27 |

| CHAPTER 4. IN         | TERNAL CPU FUNCTIONS                        | 4-1  |

| 4.1 Progra            | am Counter (PC)                             | 4-1  |

| -                     | am Memory (ROM)                             |      |

| -                     | Memory (RAM)                                |      |

|                       | al Register                                 |      |

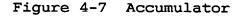

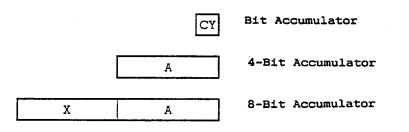

|                       | ulator                                      |      |

|                       | Pointer (SP)                                |      |

|                       | am Status Word (PSW)                        |      |

| -                     | Select Register (BS)                        |      |

|                       |                                             |      |

| CHAPTER 5. PER        | RIPHERAL HARDWARE FUNCTIONS                 | 5-1  |

| 5.1 Digita            | al Input/Output Ports                       | 5-1  |

| 5.1.1 Typ             | pes, Features and Configurations of Digital |      |

| Ing                   | put/Output Ports                            | 5-4  |

| 5.1.2 Ing             | put/Output Mode Setting                     | 5-10 |

|                       | - <b>v</b> ii -                             |      |

🔲 6427525 0094852 756 📟

| 5.1.3          | Digital Input/Output Port Operation            |       |

|----------------|------------------------------------------------|-------|

|                | Instructions                                   | 5-12  |

| 5.1.4          | Digital Input/Output Port Operations           | 5-16  |

| 5.1.5          | On-Chip Pull-Up Resistor                       | 5-19  |

| 5.1.6          | Digital Input/Output Port Input/Output         |       |

|                | Timings                                        | 5-22  |

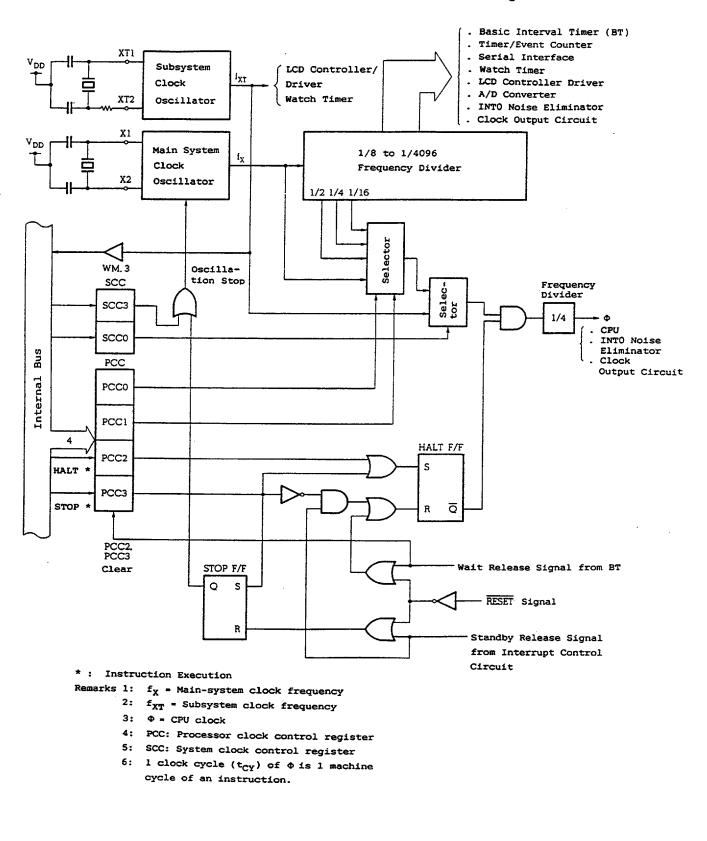

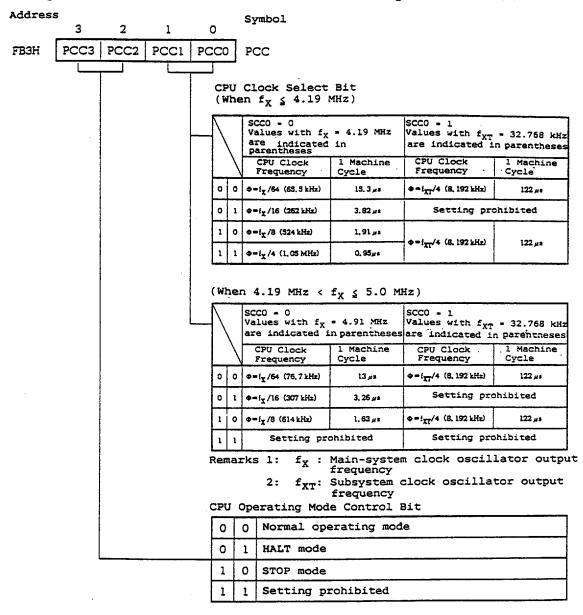

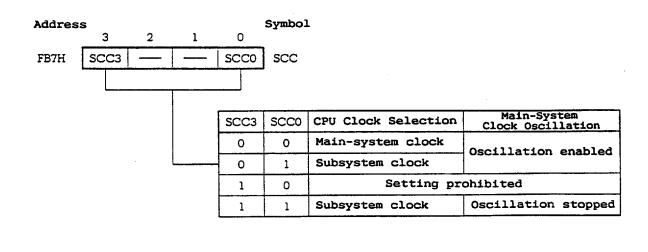

| 5.2            | Clock Generator                                | 5-25  |

| 5.2.1          | Clock Generator Configuration                  | 5-25  |

| 5.2.2          | Clock Generator Functions and Operations       | 5-27  |

| 5.2.3          | System Clock and CPU Clock Settings            | 5-38  |

| 5.2.4          | Clock Output Circuit                           | 5-42  |

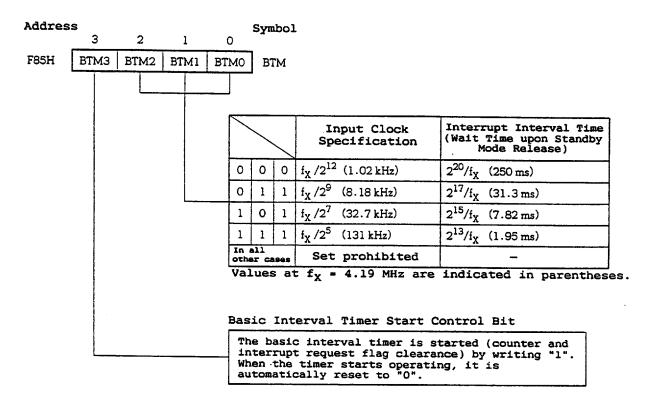

| 5.3            | Basic Interval Timer                           | 5-46  |

| 5.3.1          | Basic Interval Timer Configuration             | 5-46  |

| 5.3.2          | Basic Interval Timer Mode Register (BTM)       | •     |

| 5.3.3          | Basic Interval Timer Operation                 |       |

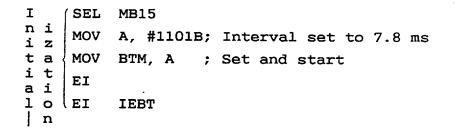

| 5.3.4          | Basic Interval Timer Application Example       |       |

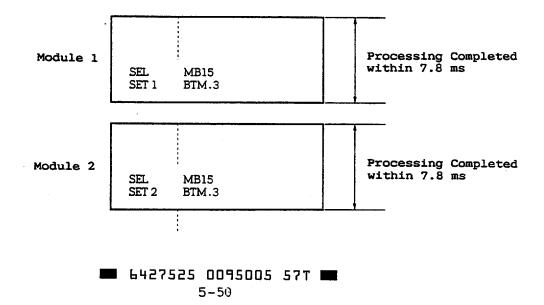

|                | Watch Timer                                    |       |

| 5.4.1          | Watch Timer Configuration                      |       |

| 5.4.2          | Clock Mode Register                            |       |

|                | Timer/Event Counter                            |       |

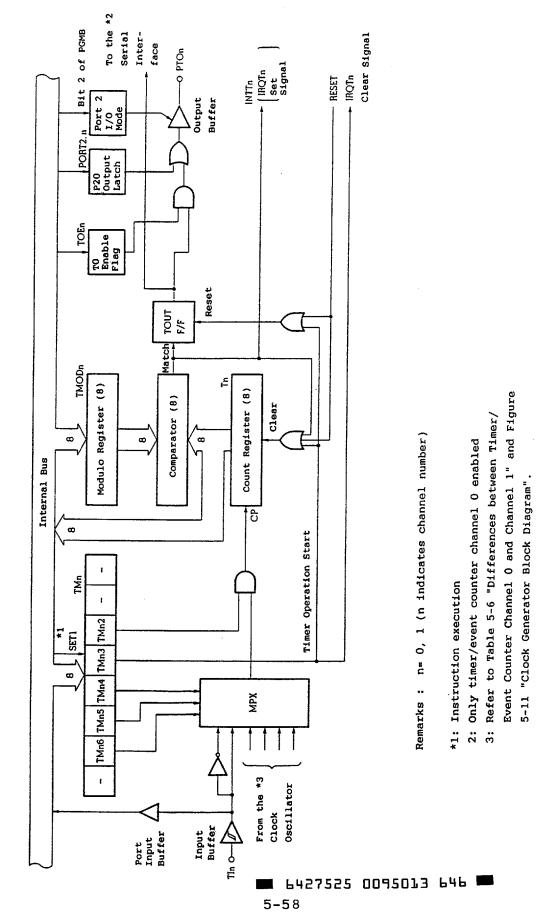

| 5.5.1          | Timer/Event Counter Configuration              | 5-57  |

| 5.5.2          | Timer/Event Counter Basic Configuration and    |       |

|                | Operation                                      | 5-59  |

| 5.5.3          | Timer/Event Counter Mode Registers (TMO,       |       |

|                | TM1)                                           | 5-60  |

| 5.5.4          | Timer/Event Counter Output Enable Flags (TOEO, |       |

|                | TOE1)                                          |       |

| 5.5.5          | Timer/Event Counter Operating Modes            |       |

| 5.5.6          | Timer/Event Counter Time Setting               |       |

| 5.5.7          | Timer/Event Counter Application Precautions    |       |

| 5.5.8          | Timer/Event Counter Applications               |       |

|                | Serial Interface                               |       |

| 5.6.1          | Serial Interface Functions                     |       |

| 5.6.2          | Serial Interface Configuration                 |       |

| 5.6.3<br>5.6.4 | Register Functions                             |       |

| 5.6.5          | Operation-Halted Mode                          |       |

|                | 3-Wire Serial I/O Mode Operation               |       |

| 5.6.6          | 2-Wire Serial I/O Mode Operation               | 5-105 |

### - viii -6427525 0094853 692 🎟

| 5.6.7   | ' SBI Mode Operation                                                       | 5-115 |

|---------|----------------------------------------------------------------------------|-------|

| 5.6.8   | SCK Pin Output Manipulation                                                | 5-158 |

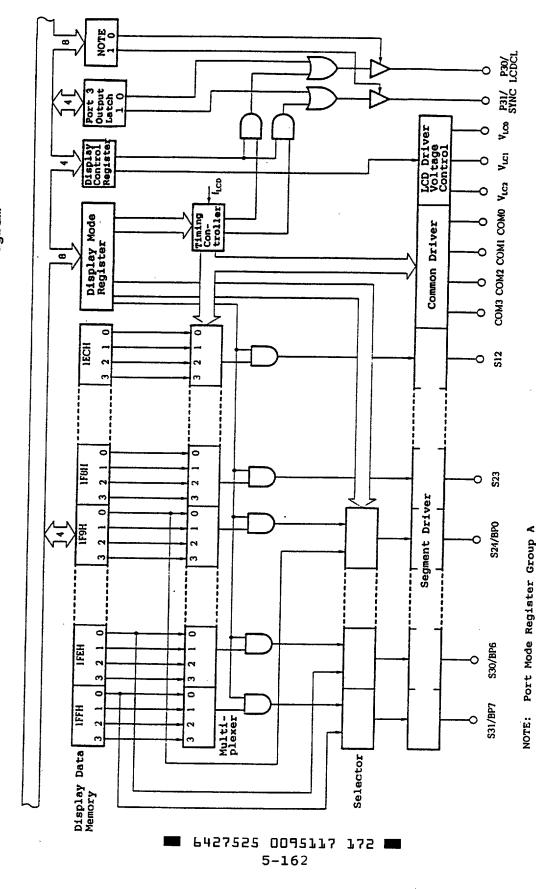

| 5.7     | LCD Controller/Driver                                                      | 5-161 |

| 5.7.1   | LCD Controller/Driver Configuration                                        | 5-161 |

| 5.7.2   | LCD Controller/Driver Functions                                            | 5-163 |

| 5.7.3   | Display Mode Register                                                      | 5-165 |

| 5.7.4   | Display Control Register                                                   | 5-167 |

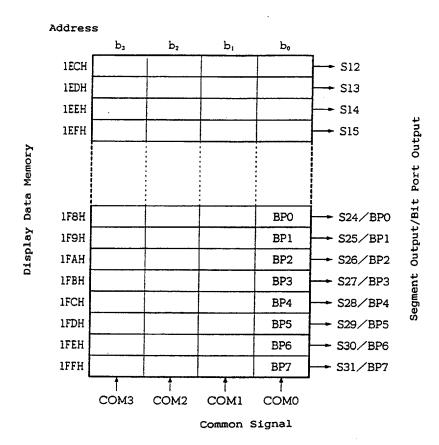

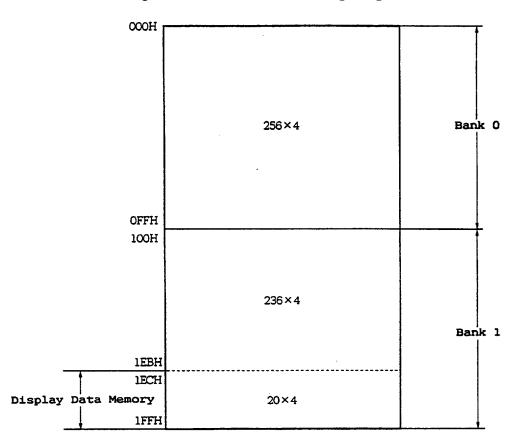

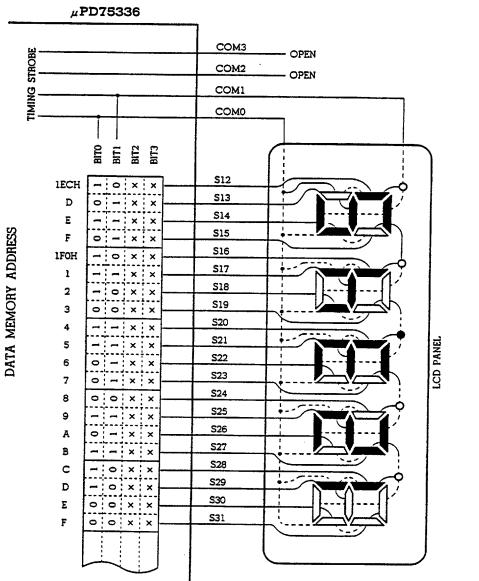

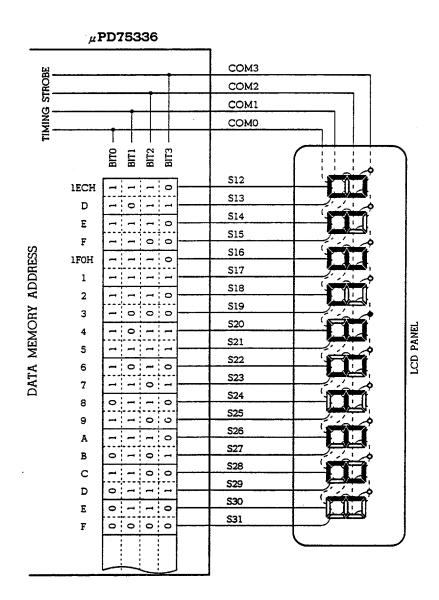

| 5.7.5   | Display Data Memory                                                        | 5-168 |

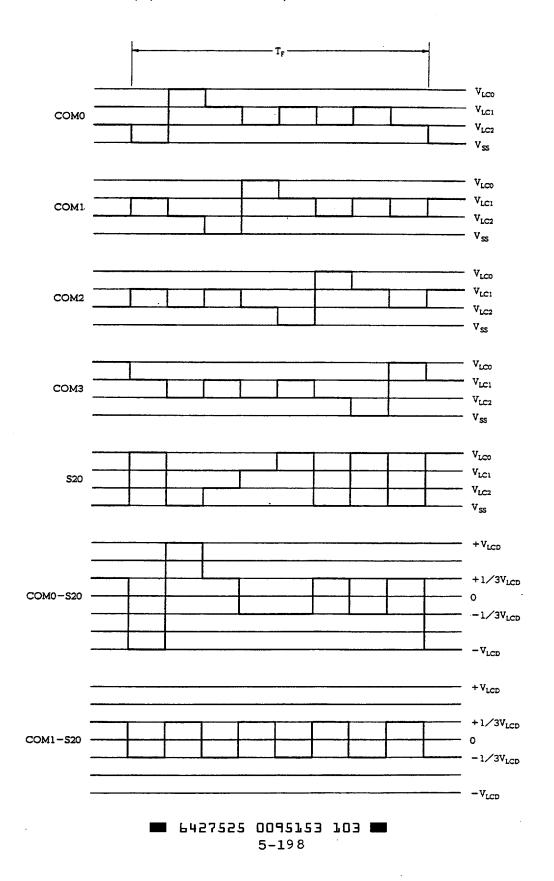

| 5.7.6   | Common Signal and Segment Signal                                           | 5-171 |

| 5.7.7   | $v_{ m LC0}^{}, v_{ m LC1}^{},$ and $v_{ m LC2}^{}$ Power Supplies for LCD |       |

|         | Drive                                                                      | 5-177 |

| 5.7.8   | Display Modes                                                              | 5-182 |

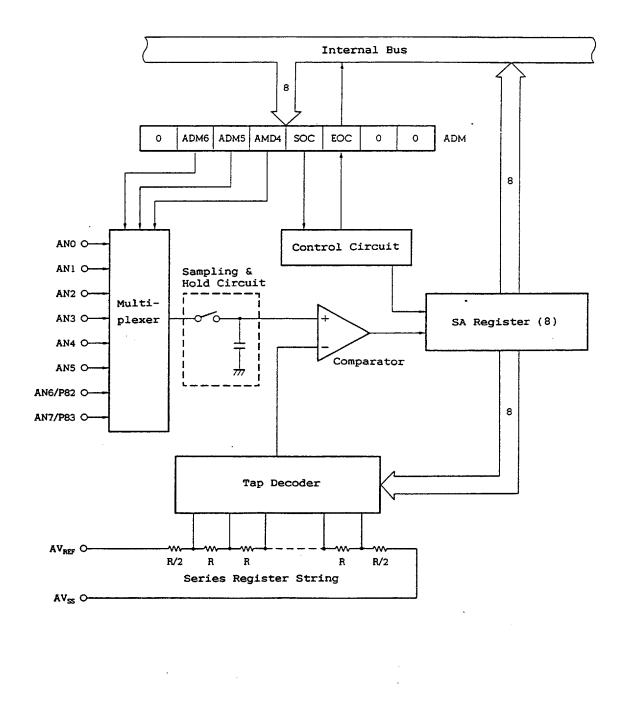

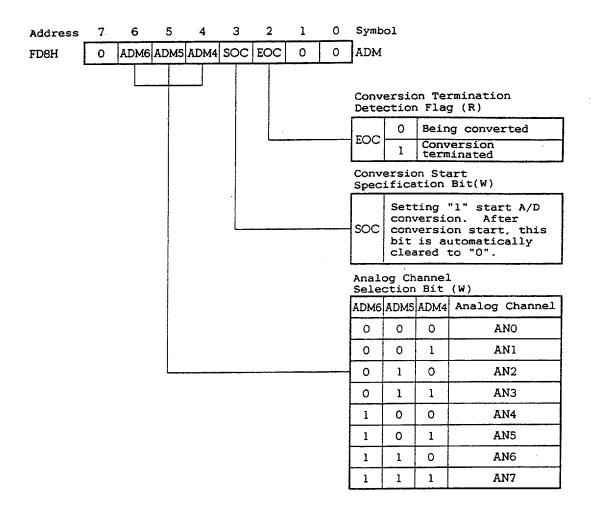

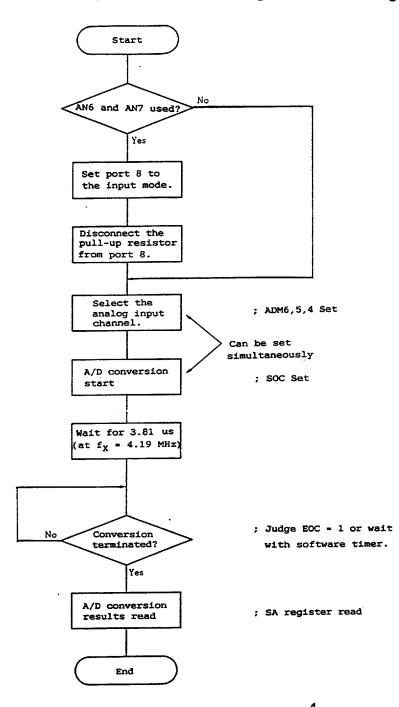

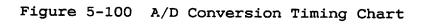

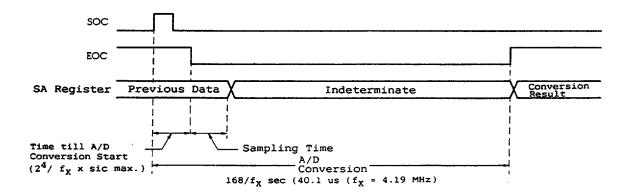

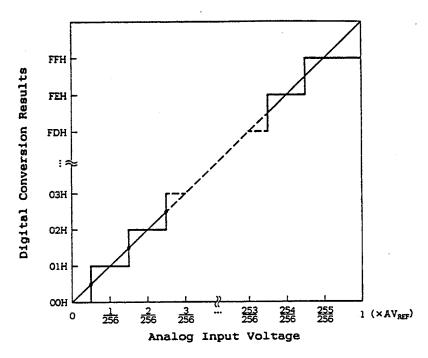

| 5.8     | A/D Converter                                                              | 5-199 |

| 5.8.1   | A/D Converter Configuration                                                | 5-199 |

| 5.8.2   | A/D Converter Operations                                                   | 5-204 |

| 5.8.3   | Standby Mode Precautions                                                   | 5-207 |

| 5.8.4   | Operating Precautions and Others                                           | 5-209 |

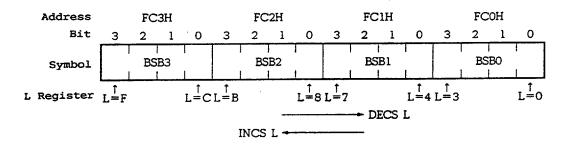

| 5.9     | Bit Sequential Buffer                                                      | 5-211 |

| CHAPTER | 6. INTERRUPT FUNCTIONS                                                     | 6-1   |

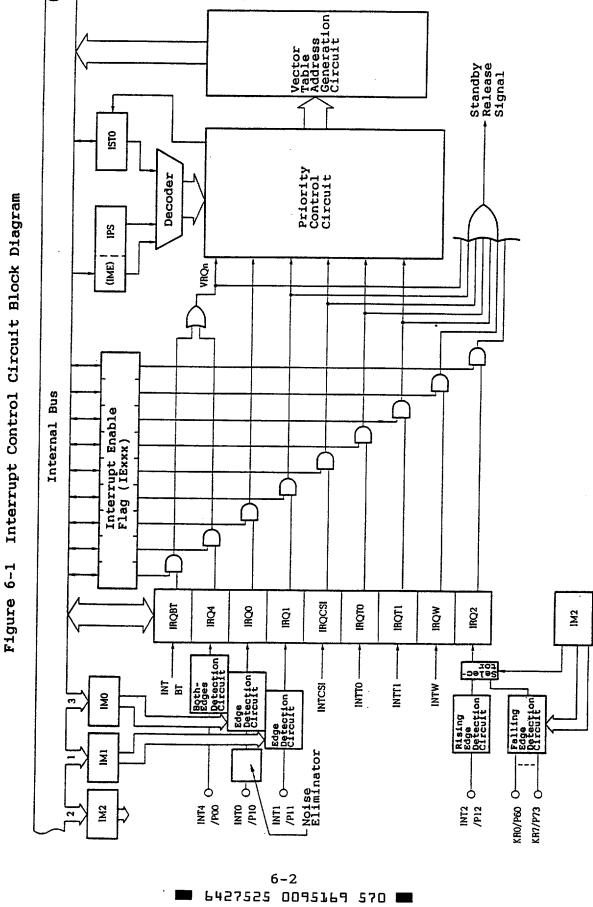

| 6.1     | Interrupt Control Circuit Configuration                                    | 6-1   |

| 6.2     | Interrupt Source Types and Vector Table                                    | 6-3   |

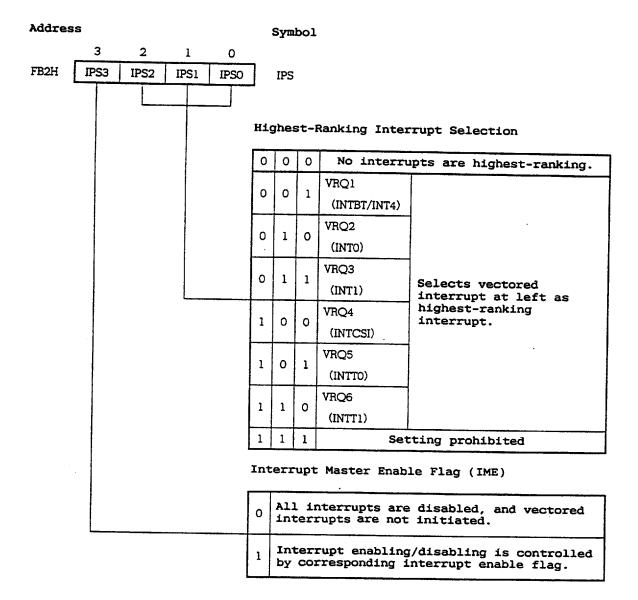

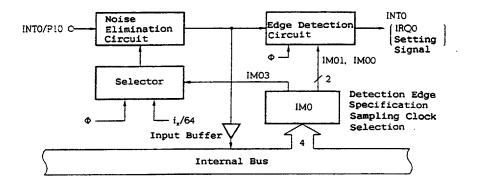

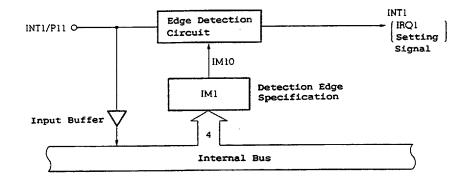

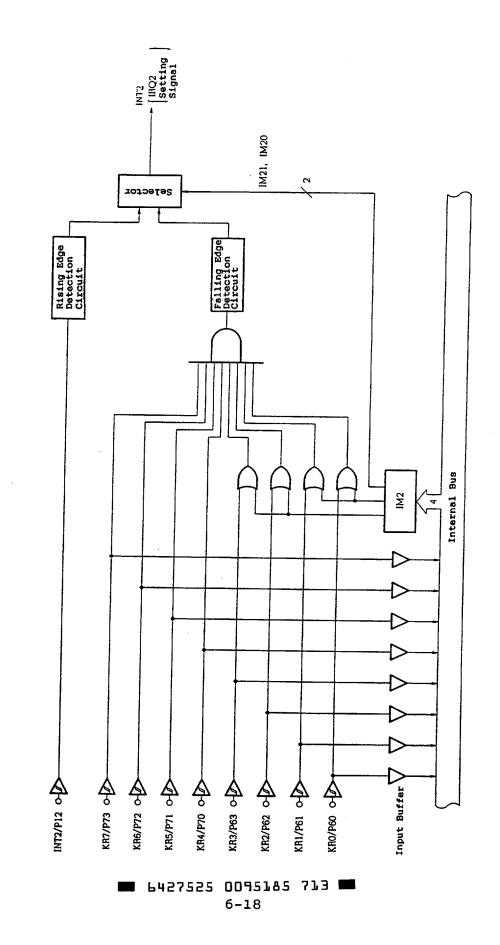

| 6.3     | Interrupt Control Circuit Hardware                                         | 6-6   |

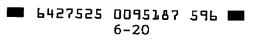

| 6.4     | Interrupt Sequence                                                         | 6-21  |

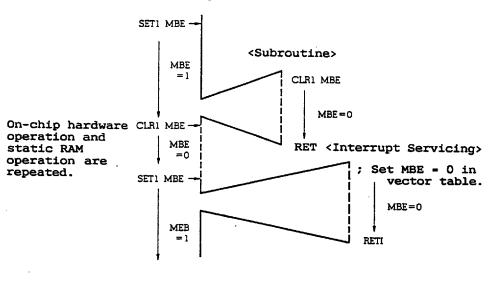

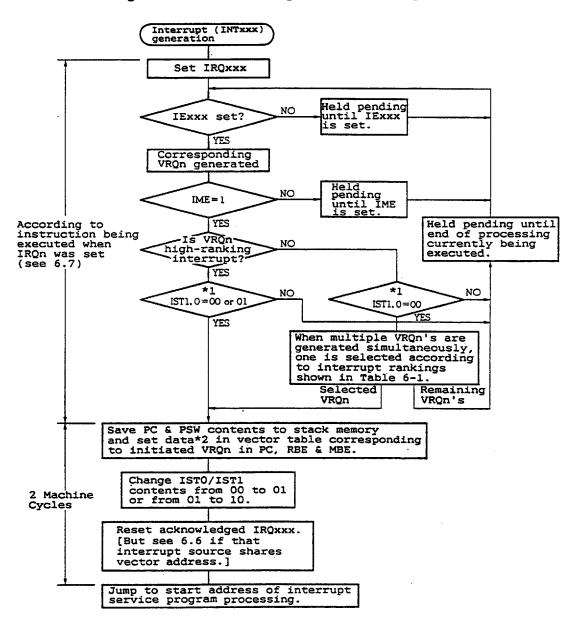

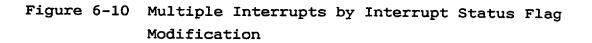

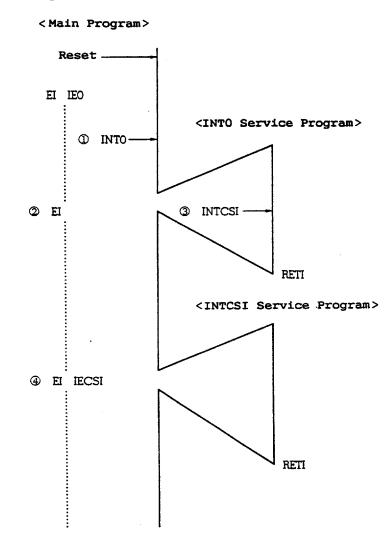

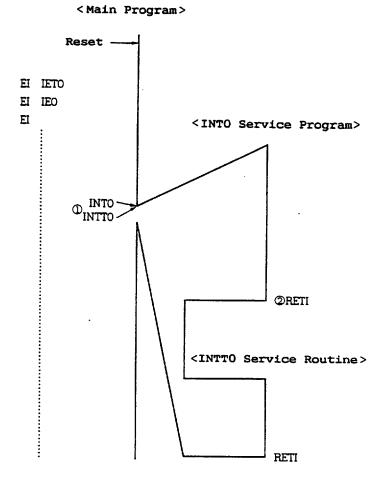

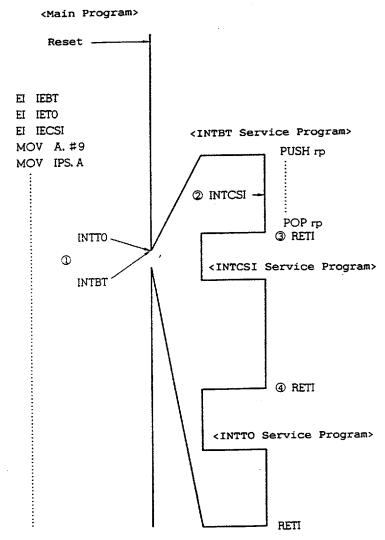

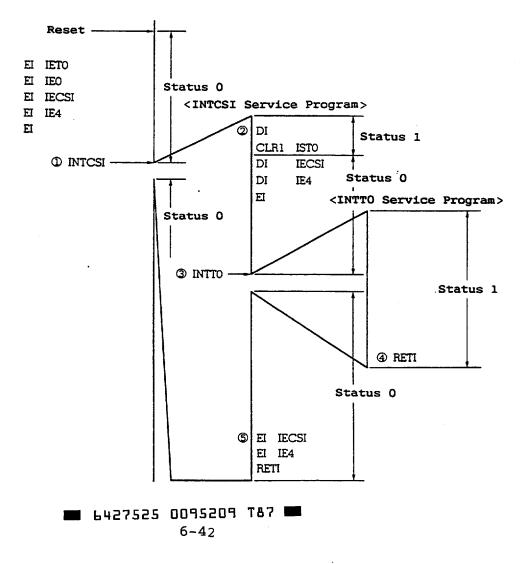

| 6.5     | Multiple Interrupt Service Control                                         | 6-22  |

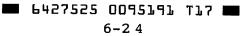

| 6.6     | Vector Address Sharing Interrupt Servicing                                 | 6-25  |

| 6.7     | Machine Cycles until Interrupt Servicing                                   | 6-28  |

| 6.8     | Effective Use of Interrupts                                                | 6-32  |

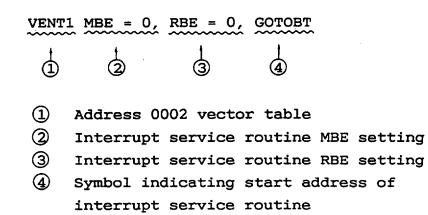

| 6.9     | Use of Interrupts                                                          | 6-34  |

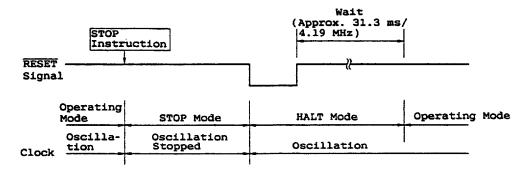

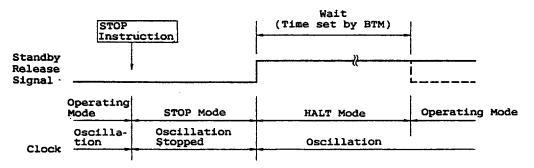

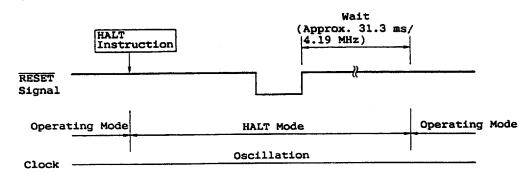

| CHAPTER | 7. STANDBY FUNCTIONS                                                       | 7-1   |

| 7.1     | Standby Mode Setting and Operating Status                                  | 7-3   |

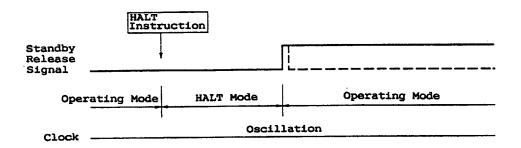

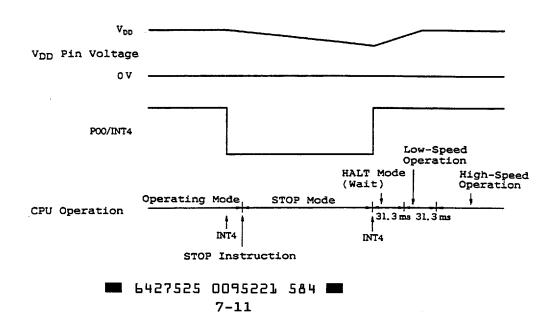

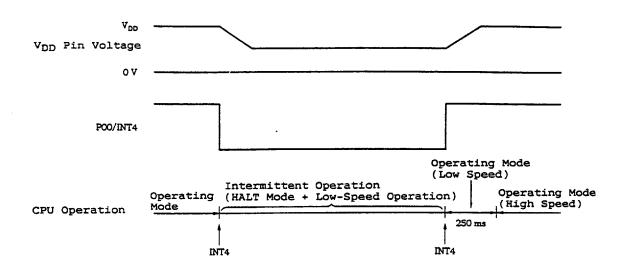

| 7.2     | Standby Mode Release                                                       | 7-6   |

| 7.3     | Operation after Standby Mode Release                                       | 7-9   |

| 7.4     | Use of Standby Mode                                                        | 7-10  |

|         |                                                                            |       |

- ix -■ 6427525 0094854 529 ■  $\mathbf{i}$

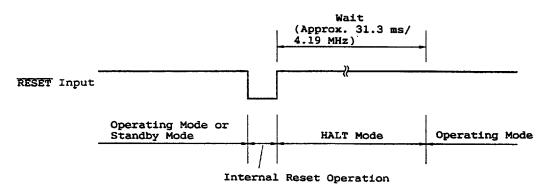

| CHAPTER 8.  | RESET FUNCTION                                    | 8-1   |

|-------------|---------------------------------------------------|-------|

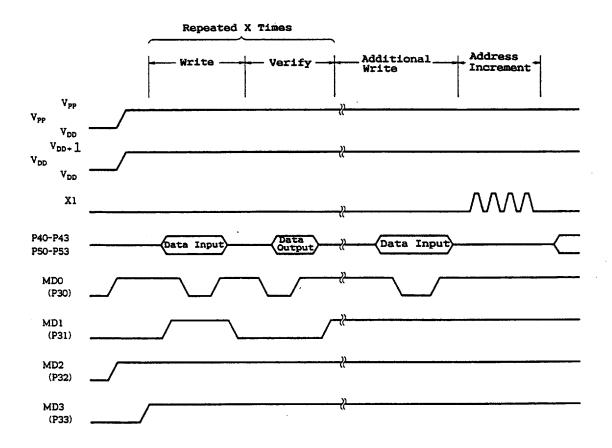

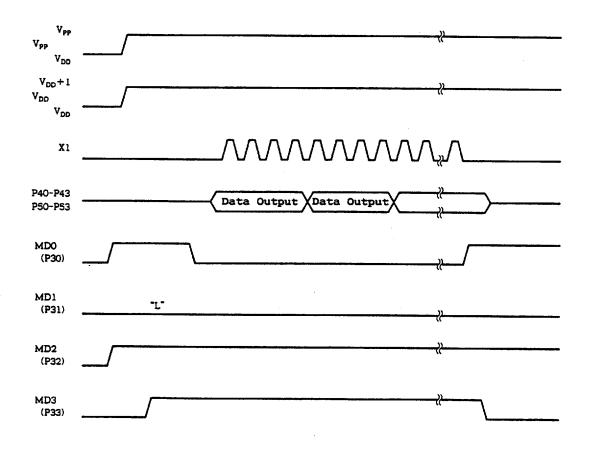

| CHAPTER 9.  | PROM (PROGRAM MEMORY) WRITE AND VERIFY OPERATIONS | 9-1   |

| 9.1 Pr      | ogram Memory Write/Verify Operating Modes         | 9-2   |

| 9.2 Pr      | ogram Memory Write Procedure                      | 9-3   |

| 9.3 Pr      | ogram Memory Read Procedure                       | 9-5   |

| CHAPTER 10. | INSTRUCTION SET                                   | 10-1  |

| 10.1 Sp     | ecial Instructions                                | 10-2  |

| 10.1.1      | GETI Instruction                                  | 10-2  |

| 10.1.2      | Bit Manipulation Instructions                     | 10-3  |

| 10.1.3      | Stacked Instructions                              | 10-3  |

| 10.1.4      | Radix Adjustment Instructions                     | 10-4  |

| 10.1.5      | Skip Instructions and Machine Cycles Required     |       |

|             | for Skipping                                      | 10-6  |

|             | struction Set and Operations                      | 10-7  |

|             | struction Operation Codes                         |       |

|             | struction Functions and Use                       |       |

| 10.4.1      | Transfer Instructions                             |       |

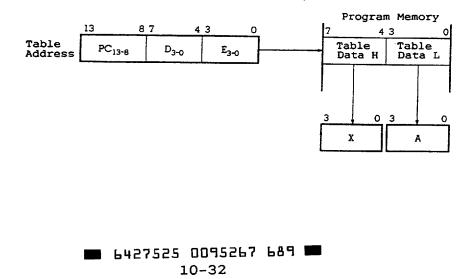

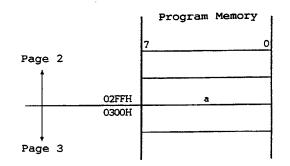

| 10.4.2      | Table Referencing Instructions                    |       |

| 10.4.3      | Bit Transfer Instructions                         | 10-35 |

| 10.4.4      | Operation Instructions                            |       |

| 10.4.5      | Accumulator Manipulating Instructions             |       |

| 10.4.6      | Increment/Decrement Instructions                  | 10-47 |

| 10.4.7      | Compare Instructions                              | 10-49 |

| 10.4.8      | Carry Flag Manipulating Instructions              | 10-51 |

| 10.4.9      | Memory Bit Manipulating Instructions              |       |

| 10.4.10     | Branch Instructions                               | 10-56 |

| 10.4.11     | Subroutine/Stack Control Instructions             | 10-60 |

| 10.4.12     | Interrupt Control Instructions                    | 10-65 |

| 10.4.13     | Input/Output Instructions                         | 10-66 |

| 10.4.14     | CPU Control Instructions                          |       |

| 10.4.15     | Special Instructions                              | 10-69 |

- x -• 6427525 0094855 465 •

| APPENDIX   | Α.         |         |        |             |             |             | •           |               |             |     |

|------------|------------|---------|--------|-------------|-------------|-------------|-------------|---------------|-------------|-----|

|            |            | AND u   | PD7532 | 28          | • • • • • • | • • • • • • | ••••        | • • • • • •   | • • • • • • | A-1 |

| A.1        | Func       | tional  | l Diff | ference     | s           | ••••        | • • • • • • | • • • • • • • |             | A-1 |

| A.2        | Diff       | ference | es bet | ween u      | PD7533      | 86 and      | uPD75       | 328           |             |     |

|            | Inst       | ructio  | ons    | • • • • • • | • • • • • • | • • • • •   | • • • • • • |               | • • • • • • | A-3 |

|            |            |         |        |             |             |             |             |               |             |     |

| APPENDIX   | в.         | DEVEL   | OPMENT | TOOLS       | • • • • •   | ••••        | • • • • • • | • • • • • • • | • • • • •   | B-1 |

|            |            |         |        |             |             |             |             |               |             |     |

| APPENDIX   | c.         | MASK I  | ROM OR | DERING      | PROCE       | DURE        | • • • • • • | • • • • • • • | ••••        | C-1 |

|            |            |         |        |             |             |             |             |               |             |     |

| APPENDIX   | D.         | INSTRU  | JCTION | INDEX       | • • • • •   | • • • • •   | • • • • • • | • • • • • • • | • • • • •   | D-1 |

|            | <b>-</b> . |         |        | <i>.</i> –  | <b>.</b>    |             |             |               |             |     |

| D.1        | Inst       | ructio  | on Ind | ex (In      | Funct       | ional       | Order       | )             | • • • • •   | D-1 |

| <b>п</b> 2 | Inst       | motic   | n Tha  | ex (In      | Alsha       | botio       |             | ·             |             |     |

|            | 11150      | LUCLI   |        | er (III     | мтриа       | Dertce      | ar Orde     | 31)           | • • • • •   | D-3 |

| APPENDIX   | E.         | HARDWA  | RE IN  | DEX (AI     | lphabe      | tical       | Order       |               |             | E-1 |

### - xi -■ 6427525 0094856 3Tl ■

# Contents of Figures

| Figure<br>No. | Title                                             | Page |

|---------------|---------------------------------------------------|------|

| 3-1           | MBE = 0 Mode and MBE = 1 Mode Distinction         | 3-3  |

| 3-2           | Data Memory Configuration and Addressing Range in |      |

|               | Each Addressing Mode                              | 3-5  |

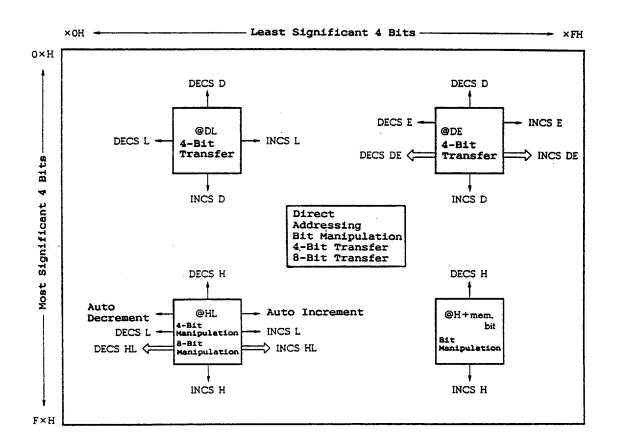

| 3-3           | Static RAM Address Updating Method                | 3-13 |

| 3-4           | Register Bank Usage                               | 3-23 |

| 3-5           | General Register Configuration (4-Bit             |      |

|               | Processing)                                       | 3-25 |

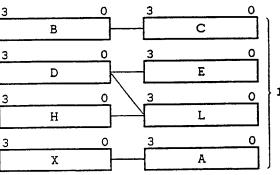

| 3-6           | General Register Configuration (8-Bit             |      |

|               | Processing)                                       | 3-26 |

| 3-7           | uPD75336 I/O Map                                  | 3-29 |

| 4-1           | Program Counter Configuration                     | 4-1  |

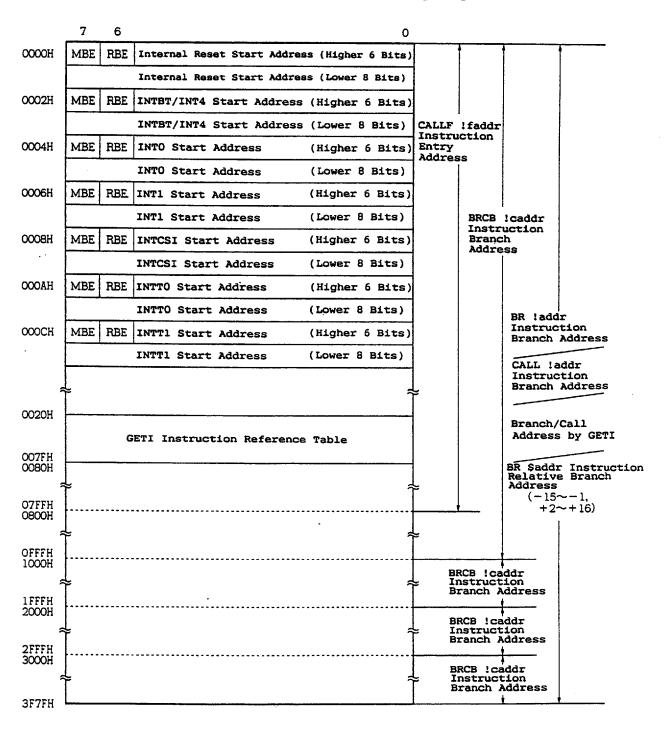

| 4-2           | Program Memory Map                                | 4-4  |

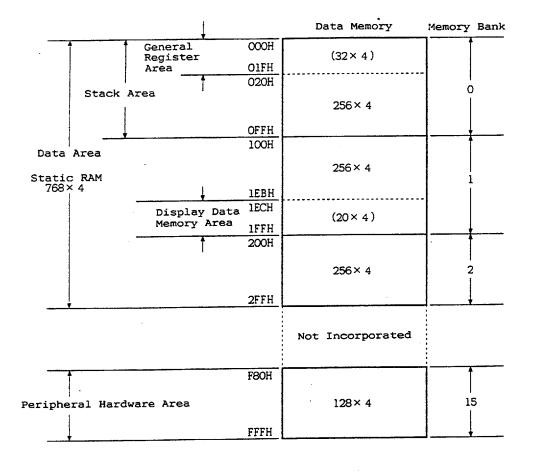

| 4-3           | Data Memory Map                                   | 4-5  |

| 4-4           | Display Data Memory Configuration                 | 4-10 |

| 4-5           | General Register Configuration                    | 4-13 |

| 4-6           | Register Pair Configuration                       | 4-13 |

| 4-7           | Accumulator                                       | 4-14 |

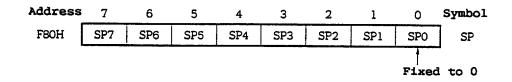

| 4-8           | Stack Pointer Configuration                       | 4-16 |

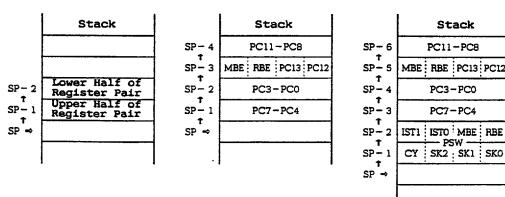

| 4-9           | Data Saved into Stack Memory                      | 4-16 |

| 4-10          | Data Restored from Stack Memory                   | 4-16 |

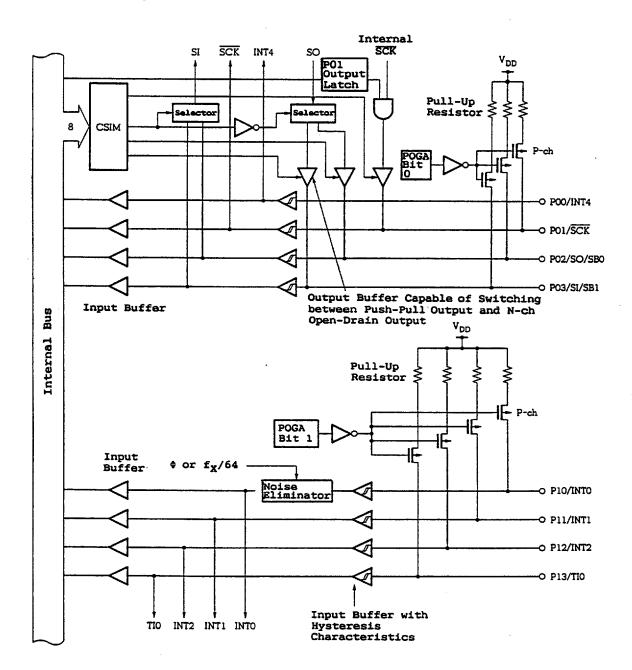

| 4-11          | Program Status Word Configuration                 | 4-17 |

| 4-12          | Bank Select Register Configuration                | 4-23 |

| 5-1           | Digital Port Data Memory Addresses                | 5-2  |

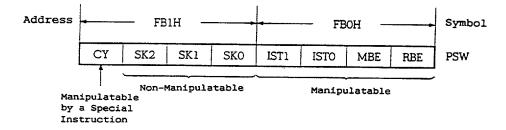

| 5-2           | Configurations of Ports 0 and 1                   | 5-6  |

| 5-3           | Configurations of Ports 3n and 6n (n = 0 to 3)    | 5-7  |

| 5-4           | Configurations of Ports 2 and 7                   | 5-7  |

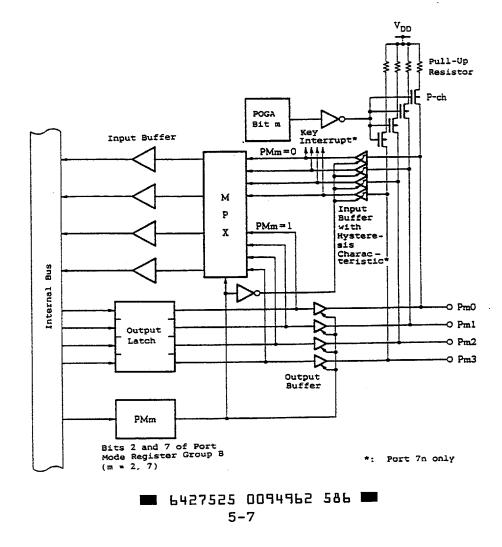

| 5-5           | Configurations of Ports 4 and 5                   | 5-8  |

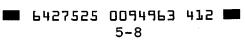

| 5-6           | Port 8 Configuration                              | 5-9  |

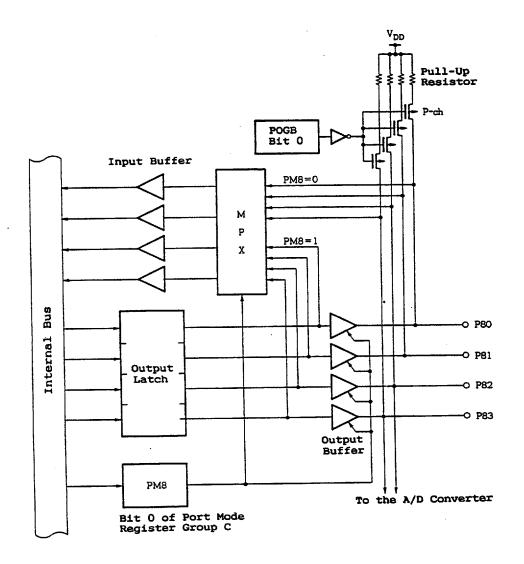

| 5-7           | Port Mode Register Formats                        | 5-11 |

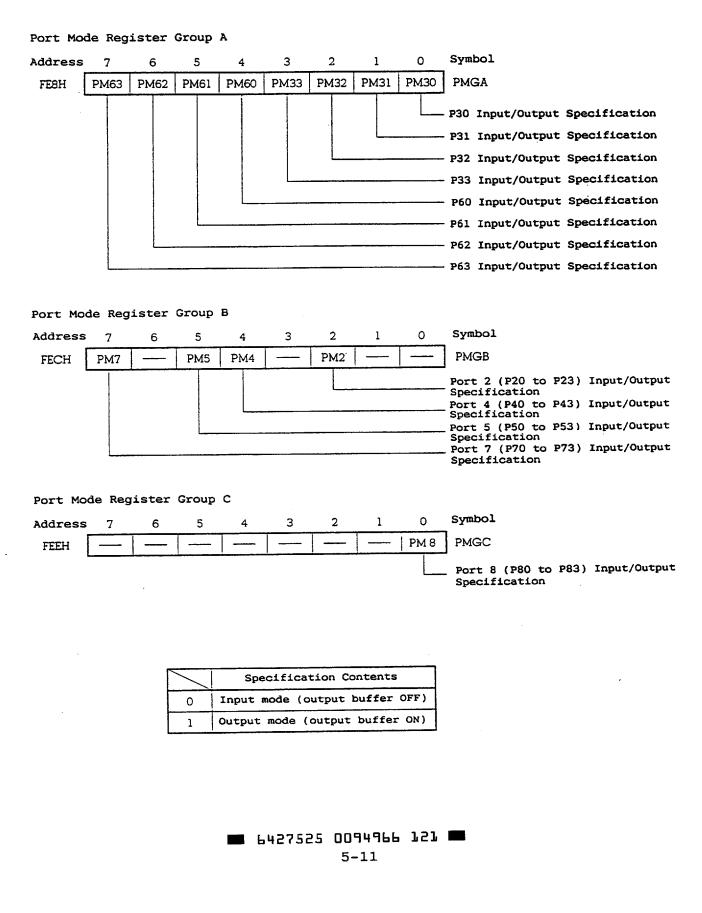

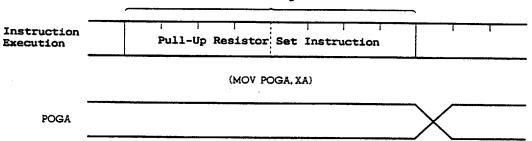

| 5-8           | Pull-Up Resistor Specification Register Format    | 5-20 |

| 5-9           | Digital Input/Output Port Input/Output Timings    | 5-23 |

- xii -6427525 0094857 238 🖿

| Figure |

|--------|

| No.    |

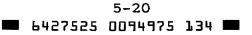

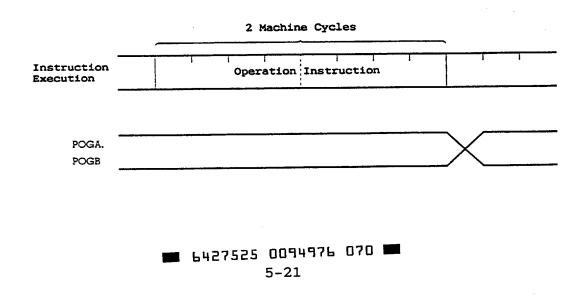

| 5-10 | Pull-Up Resistor ON Timing by Software 5-           | 24  |

|------|-----------------------------------------------------|-----|

| 5-11 | Clock Generator Block Diagram                       | 26  |

| -12  | Processor Clock Control Register Format 5-          | 30  |

| -13  | System Clock Control Register Format 5-             | 31  |

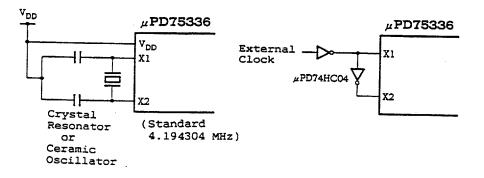

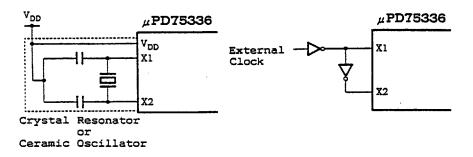

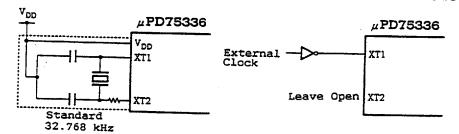

| -14  | External Circuit of Main-System Clock Oscillator 5- | 33  |

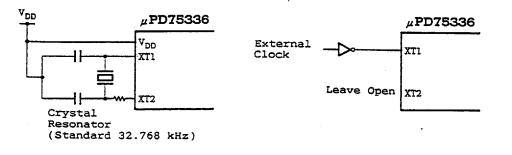

| -15  | External Circuit of Subsystem Clock Oscillator 5-3  | 34  |

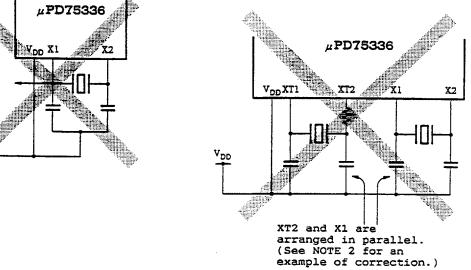

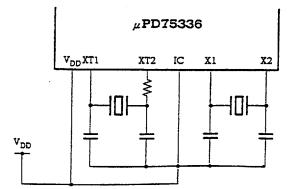

| -16  | Bad Examples of Resonator Connection Circuit 5-3    | 35  |

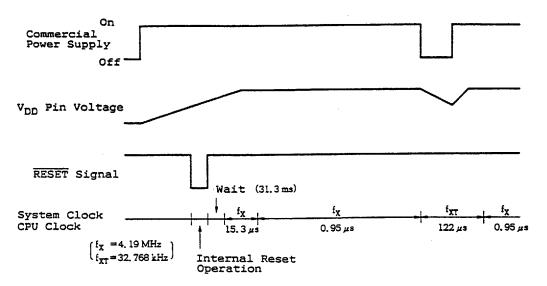

| -17  | System Clock and CPU Clock Switching 5-4            | 41  |

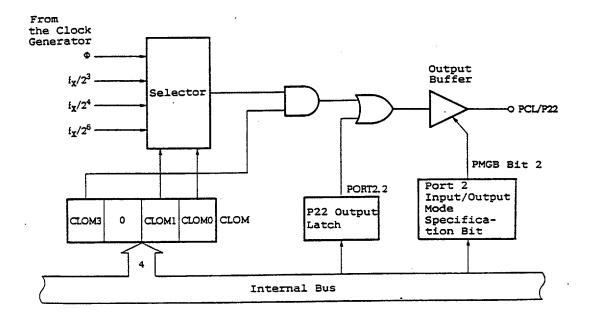

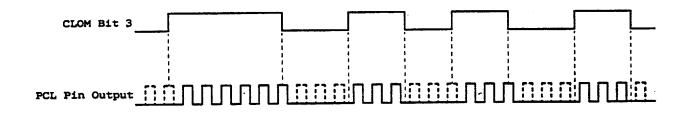

| -18  | Clock Output Circuit Configuration 5-4              | 43  |

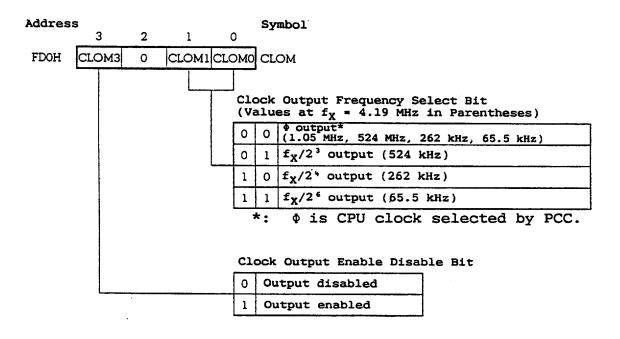

| -19  | Clock Output Mode Register Format                   | 44  |

| -20  | Example of Application to Remote Controlled         |     |

|      | Output                                              | 45  |

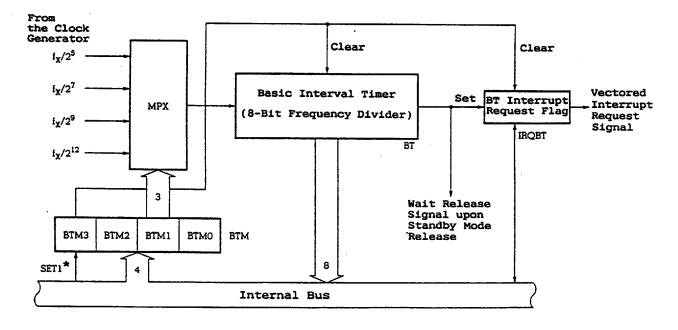

| -21  | Basic Interval Timer Configuration                  | 46  |

| -22  | Basic Interval Timer Mode Register Format 5-4       | 48  |

| -23  | Watch Timer Block Diagram 5-5                       | 54  |

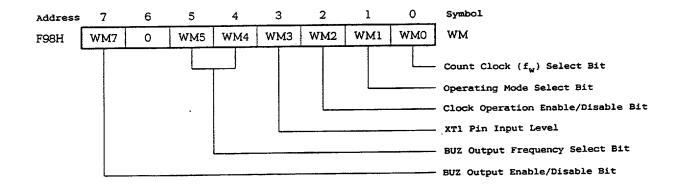

| -24  | Clock Mode Register Format 5-5                      | 55  |

| -25  | Timer/Event Counter Block Diagram                   | 58  |

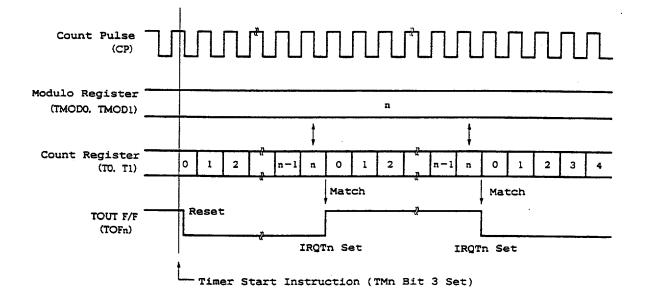

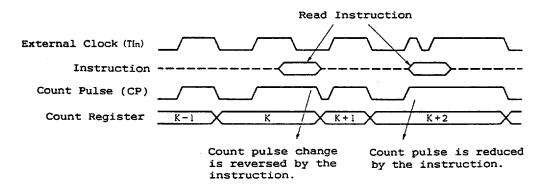

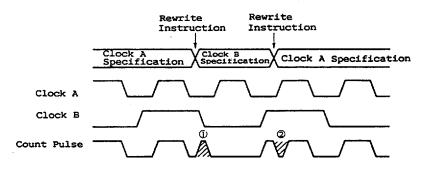

| -26  | Count Operation Timings 5-6                         | 60  |

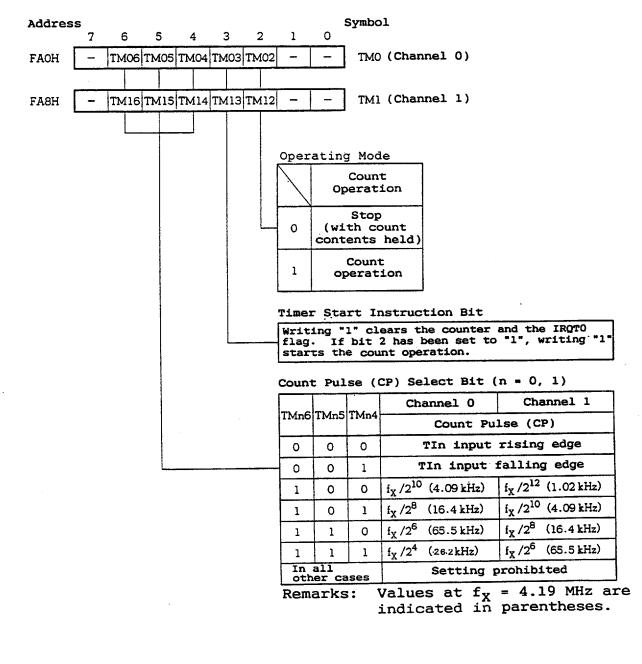

| -27  | Timer/Event Counter Mode Register Format (Channels  |     |

|      | 0 and 1) 5-6                                        | 61  |

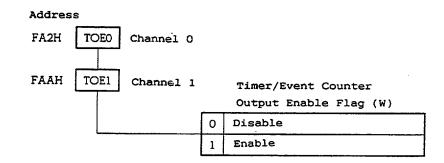

| -28  | Timer/Event Counter Output Enable Flag Format       |     |

|      | (Channels 0, 1) 5-6                                 | 62  |

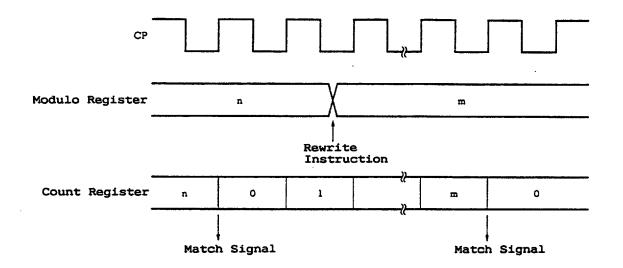

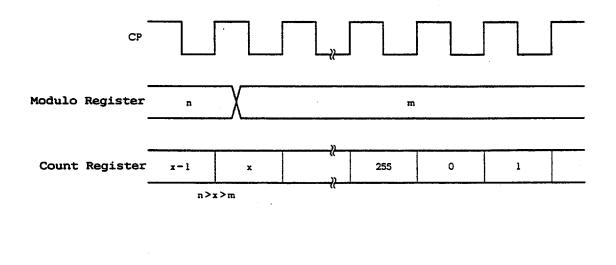

| -29  | Operation in Count Operating Mode                   | б4  |

| -30  | Count Register Clear Timing 5-6                     | 66  |

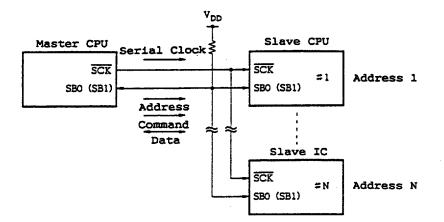

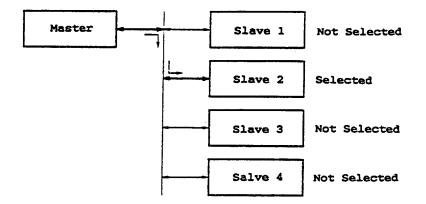

| -31  | SBI System Configuration Example 5-7                | 75  |

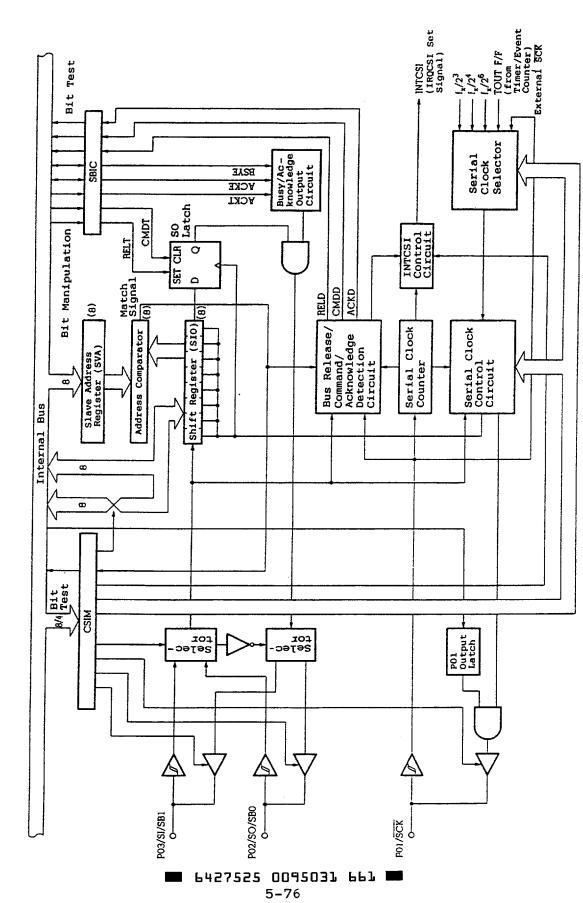

| -32  | Serial Interface Block Diagram 5-7                  | 76  |

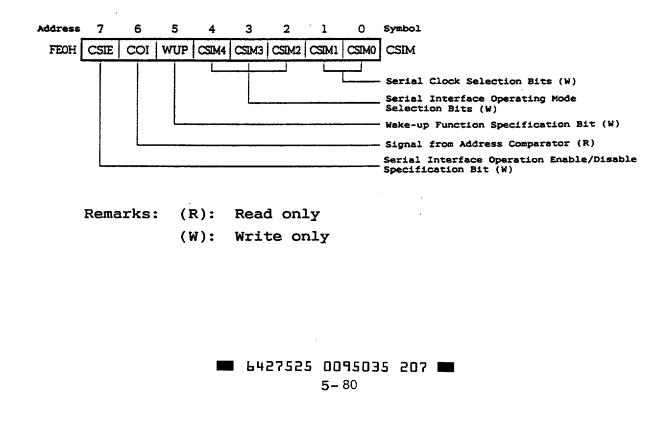

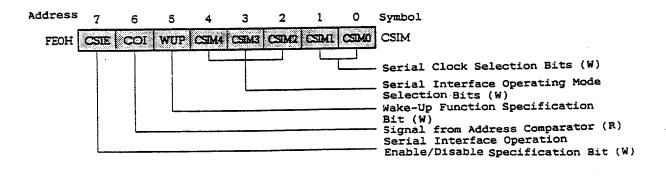

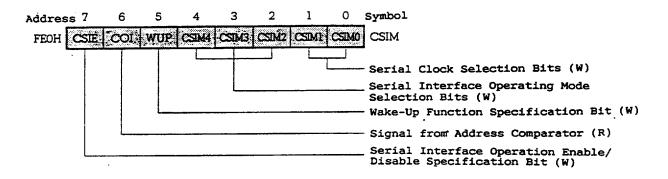

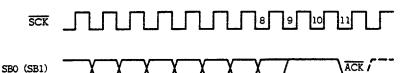

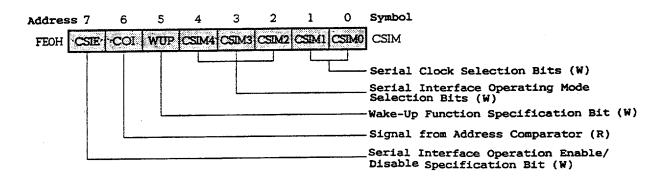

| -33  | Serial Operating Mode Register (CSIM) Format 5-8    | 80  |

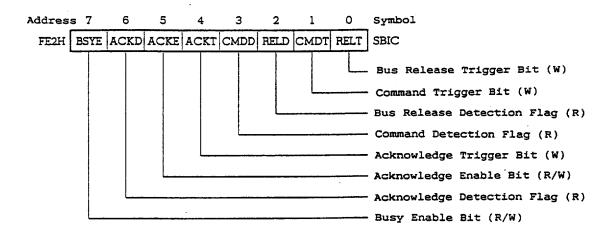

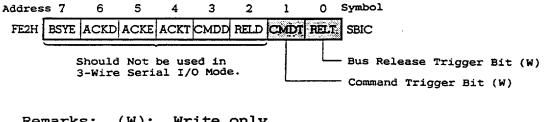

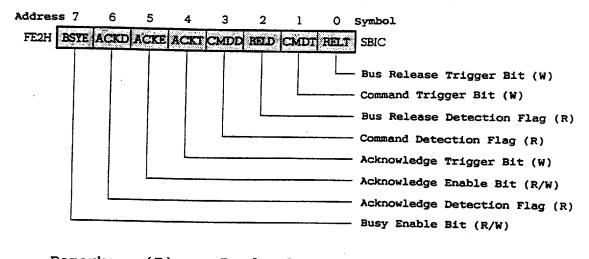

| -34  | Serial Bus Interface Control Register (SBIC)        |     |

|      | Format                                              | 85  |

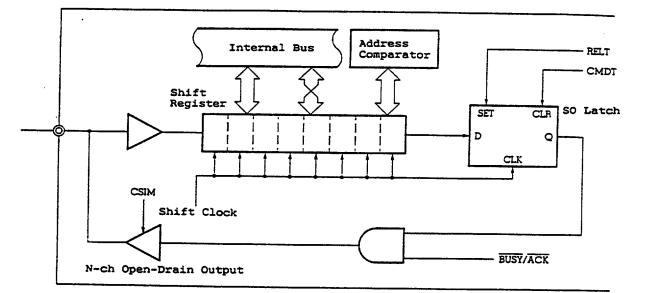

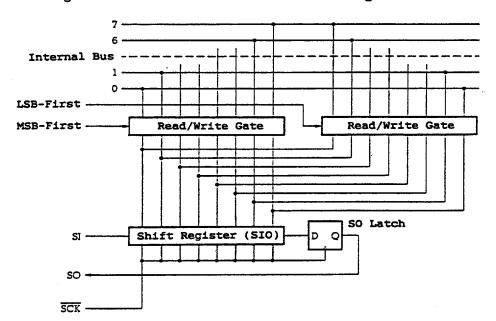

| -35  | Configuration around Shift Register 5-9             | 90  |

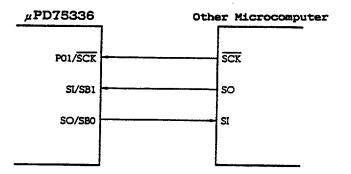

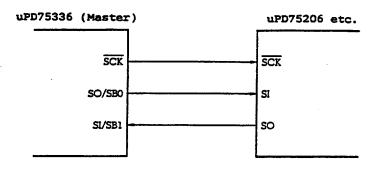

| -36  | Example of 3-Wire Serial I/O System                 |     |

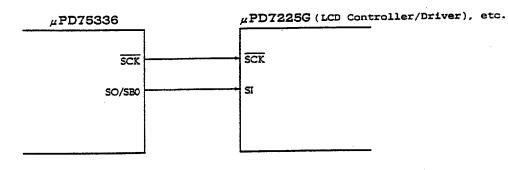

|      | Configuration 5-9                                   |     |

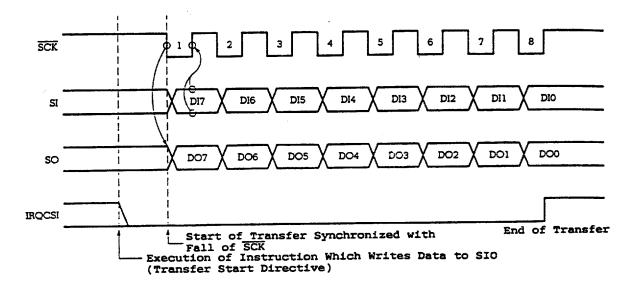

| -37  | 3-Wire Serial I/O Mode Timing                       |     |

| -38  | RELT & CMDT Operation                               |     |

| 5-39 | Transfer Bit Switching Circuit                      | 101 |

- xiii -• 6427525 0094858 174 🚥

| 5-40       Example of 2-Wire Serial I/O System<br>Configuration       5-         5-41       2-Wire Serial I/O Mode Timing       5-         5-42       RELT & CMDT Operation       5-         5-43       Example of SBI Serial Bus Configuration       5-         5-44       SBI Transfer Timing       5-         5-45       Bus Release Signal       5-         5-46       Command Signal       5-         5-47       Address       5-         5-48       Slave Selection by Address       5-         5-49       Command       5-         5-40       Command       5-         5-41       Command       5-         5-50       Data       5-         5-51       Acknowledge Signal       5-         5-52       Busy Signal & Ready Signal       5-         5-53       RELT, CMDT, RELD & CMDD Operation (Master)       5-         5-54       RELT, CMDT, RELD & CMDD Operation (Slave)       5-         5-55       ACKT Operation       5-         5-56       ACKE Operation       5-         5-57       ACKD Operation       5-         5-58       BSYE Operation       5-         5-59       Pin Configuration Diagram                                             | Figure<br>No. | Title                                   | Page              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------|-------------------|

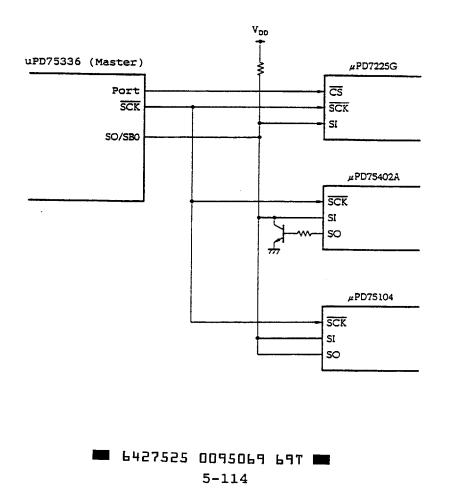

| 5-41       2-Wire Serial I/O Mode Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-40          | Example of 2-Wire Serial I/O System     |                   |

| 5-42       RELT & CMDT Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               | Configuration                           | 5-106             |

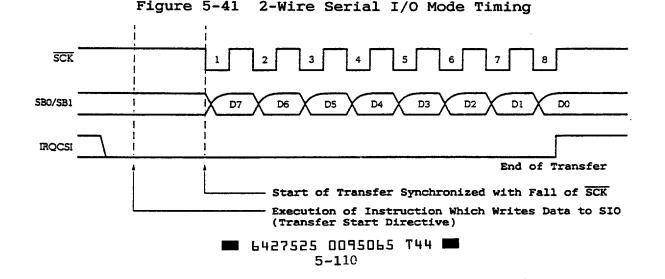

| 5-43       Example of SBI Serial Bus Configuration       5-         5-44       SBI Transfer Timing       5-         5-45       Bus Release Signal       5-         5-46       Command Signal       5-         5-47       Address       5-         5-48       Slave Selection by Address       5-         5-49       Command       5-         5-40       Command       5-         5-41       Slave Selection by Address       5-         5-42       Command       5-         5-43       Slave Selection by Address       5-         5-44       Slave Selection by Address       5-         5-45       Data       5-         5-50       Data       5-         5-51       Acknowledge Signal       5-         5-52       Busy Signal & Ready Signal       5-         5-53       RELT, CMDT, RELD & CMDD Operation (Master)       5-         5-54       RELT, CMDT, RELD & CMDD Operation (Slave)       5-         5-55       ACKT Operation       5-         5-56       ACKE Operation       5-         5-57       AcKD Operation Diagram       5-         5-58       BSYE Operation from Master Device to Slave       <                                              | 5-41          | 2-Wire Serial I/O Mode Timing           | 5-110             |

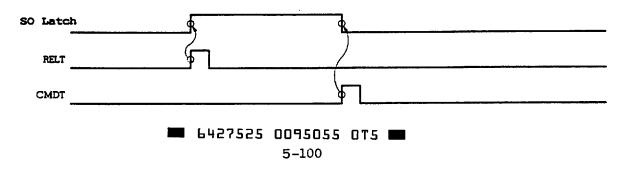

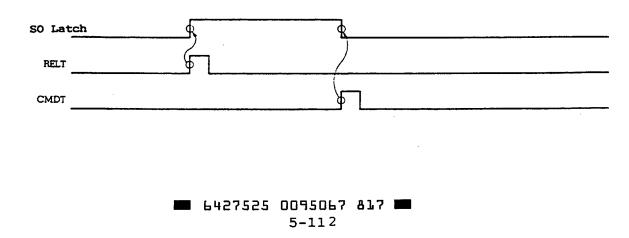

| 5-44       SBI Transfer Timing       5-         5-45       Bus Release Signal       5-         5-46       Command Signal       5-         5-47       Address       5-         5-48       Slave Selection by Address       5-         5-49       Command       5-         5-40       Data       5-         5-41       Slave Selection by Address       5-         5-42       Command       5-         5-43       Command       5-         5-44       Slave Selection by Address       5-         5-45       Renowledge Signal       5-         5-50       Data       5-         5-51       Acknowledge Signal       5-         5-52       Busy Signal & Ready Signal       5-         5-53       RELT, CMDT, RELD & CMDD Operation (Master)       5-         5-54       RELT, CMDT, RELD & CMDD Operation (Slave)       5-         5-55       ACKT Operation       5-         5-56       ACKE Operation       5-         5-57       AcKD Operation       5-         5-58       BSYE Operation       5-         5-59       Pin Configuration Diagram       5-         5-61 <td< td=""><td>5-42</td><td>RELT &amp; CMDT Operation</td><td>5-112</td></td<>            | 5-42          | RELT & CMDT Operation                   | 5-112             |

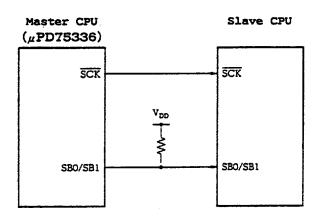

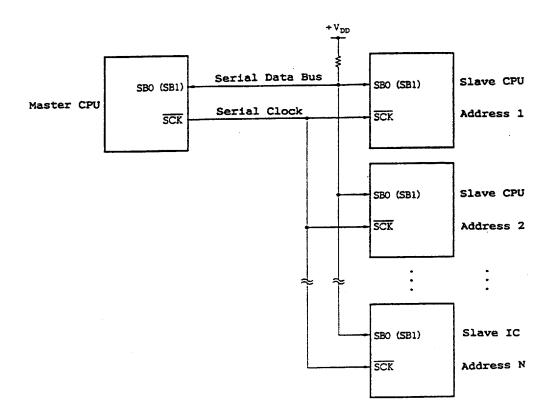

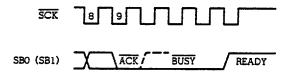

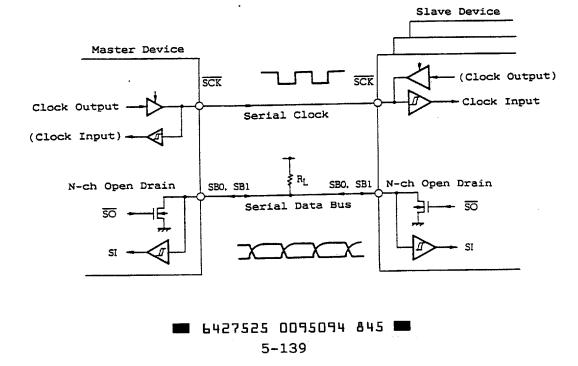

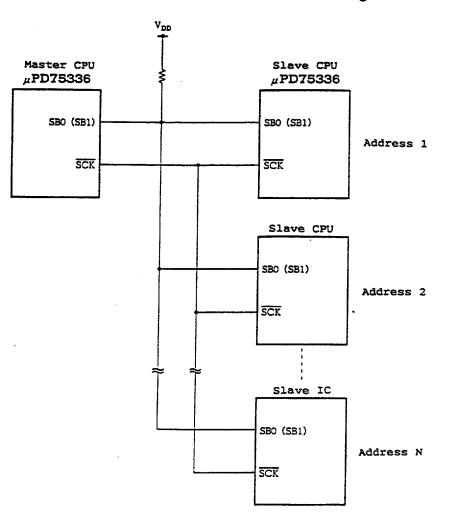

| 5-45       Bus Release Signal       5-         5-46       Command Signal       5-         5-47       Address       5-         5-48       Slave Selection by Address       5-         5-49       Command       5-         5-40       Command       5-         5-41       Slave Selection by Address       5-         5-42       Command       5-         5-43       Slave Selection by Address       5-         5-44       Slave Selection by Address       5-         5-50       Data       5-       5-         5-51       Acknowledge Signal       5-         5-52       Busy Signal & Ready Signal       5-         5-53       RELT, CMDT, RELD & CMDD Operation (Master)       5-         5-54       RELT, CMDT, RELD & CMDD Operation (Slave)       5-         5-55       ACKE Operation       5-         5-57       ACKD Operation       5-         5-58       BSYE Operation       5-         5-59       Pin Configuration Diagram       5-         5-61       Command Transmission from Master Device to Slave       5-         5-62       Data Transmission from Master Device to Slave       5-         5-64                                              | 5-43          | Example of SBI Serial Bus Configuration | 5-117             |

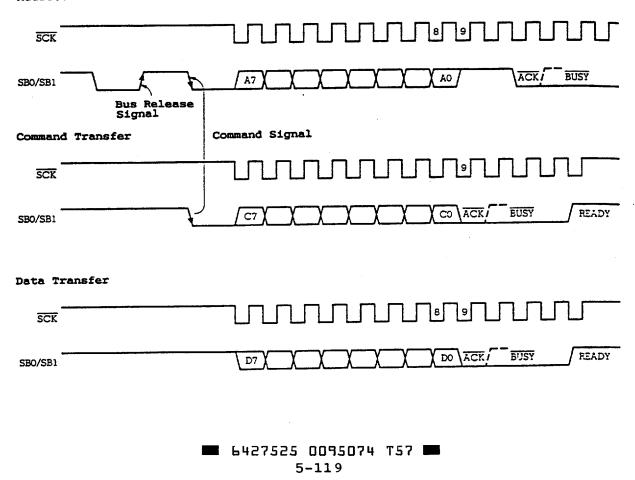

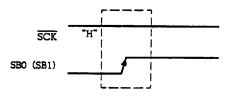

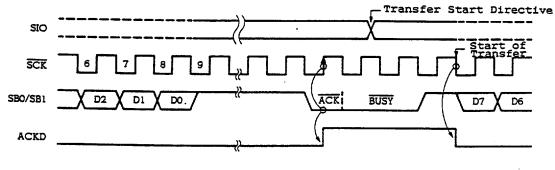

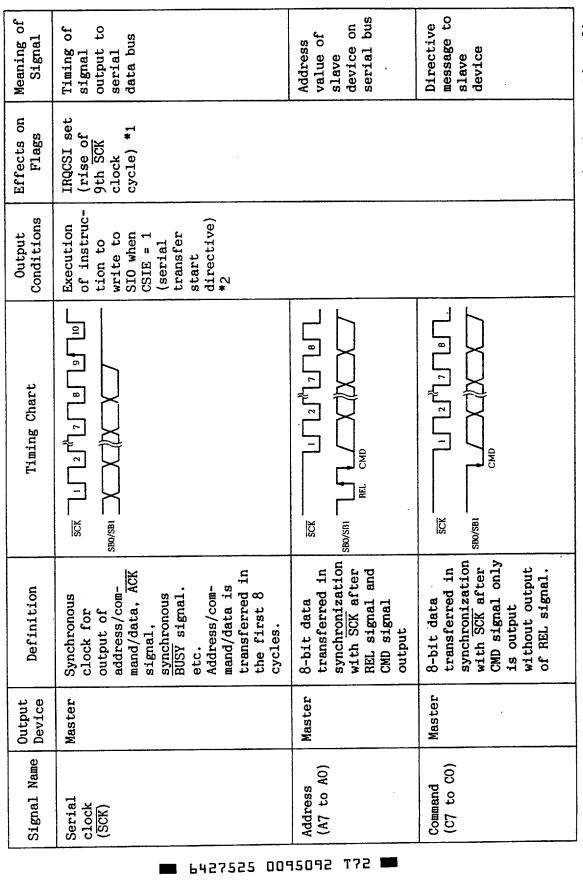

| 5-45       Bus Release Signal       5-         5-46       Command Signal       5-         5-47       Address       5-         5-48       Slave Selection by Address       5-         5-49       Command       5-         5-40       Command       5-         5-41       Slave Selection by Address       5-         5-42       Command       5-         5-43       Slave Selection by Address       5-         5-44       Slave Selection by Address       5-         5-50       Data       5-       5-         5-51       Acknowledge Signal       5-         5-52       Busy Signal & Ready Signal       5-         5-53       RELT, CMDT, RELD & CMDD Operation (Master)       5-         5-54       RELT, CMDT, RELD & CMDD Operation (Slave)       5-         5-55       ACKT Operation       5-         5-56       ACKE Operation       5-         5-57       ACKD Operation       5-         5-58       BSYE Operation       5-         5-59       Pin Configuration Diagram       5-         5-61       Command Transmission from Master Device to Slave       5-         5-62       Data Transmission fr                                                  | 5-44          |                                         |                   |

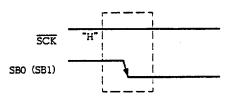

| 5-47       Address       5-         5-48       Slave Selection by Address       5-         5-49       Command       5-         5-50       Data       5-         5-51       Acknowledge Signal       5-         5-52       Busy Signal & Ready Signal       5-         5-53       RELT, CMDT, RELD & CMDD Operation (Master)       5-         5-54       RELT, CMDT, RELD & CMDD Operation (Slave)       5-         5-55       ACKT Operation       5-         5-56       ACKE Operation       5-         5-57       ACKD Operation       5-         5-58       BSYE Operation       5-         5-59       Pin Configuration Diagram       5-         5-50       Address Transmission from Master Device to Slave       5-         5-61       Command Transmission from Master Device to Slave       5-         5-62       Data Transmission from Master Device to Slave       5-         5-63       Data Transmission from Slave Device to Master       5-         5-64       Example of Serial Bus Configuration       5-1         5-65       READ Command Transfer Format       5-1         5-66       WRITE & END Command Transfer Format       5-1             | 5-45          |                                         |                   |

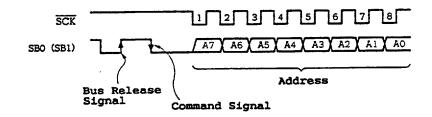

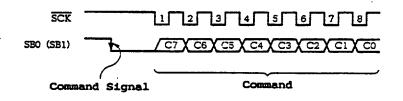

| 5-47       Address       5-         5-48       Slave Selection by Address       5-         5-49       Command       5-         5-50       Data       5-         5-51       Acknowledge Signal       5-         5-52       Busy Signal & Ready Signal       5-         5-53       RELT, CMDT, RELD & CMDD Operation (Master)       5-         5-54       RELT, CMDT, RELD & CMDD Operation (Slave)       5-         5-55       ACKT Operation       5-         5-56       ACKE Operation       5-         5-57       ACKD Operation       5-         5-58       BSYE Operation       5-         5-59       Pin Configuration Diagram       5-         5-60       Address Transmission from Master Device to Slave       5-         Device (WUP = 1)       5-1       5-1         5-61       Command Transmission from Master Device to Slave       5-1         5-63       Data Transmission from Slave Device to Master       5-1         5-64       Example of Serial Bus Configuration       5-1         5-65       READ Command Transfer Format       5-1         5-66       WRITE & END Command Transfer Format       5-1                                        | 5-46          | Command Signal                          | 5-121             |

| 5-48       Slave Selection by Address       5-         5-49       Command       5-         5-50       Data       5-         5-51       Acknowledge Signal       5-         5-52       Busy Signal & Ready Signal       5-         5-53       RELT, CMDT, RELD & CMDD Operation (Master)       5-         5-54       RELT, CMDT, RELD & CMDD Operation (Slave)       5-         5-55       ACKT Operation       5-         5-56       ACKE Operation       5-         5-57       ACKD Operation       5-         5-58       BSYE Operation       5-         5-59       Pin Configuration Diagram       5-         5-60       Address Transmission from Master Device to Slave       5-         Device (WUP = 1)       5-1       5-1         5-61       Command Transmission from Master Device to Slave       5-1         5-62       Data Transmission from Slave Device to Master       5-1         5-63       Data Transmission from Slave Device to Master       5-1         5-64       Example of Serial Bus Configuration       5-1         5-65       READ Command Transfer Format       5-1         5-66       WRITE & END Command Transfer Format       5-1 | 5-47          |                                         |                   |

| 5-49       Command       5-         5-50       Data       5-         5-51       Acknowledge Signal       5-         5-52       Busy Signal & Ready Signal       5-         5-53       RELT, CMDT, RELD & CMDD Operation (Master)       5-         5-54       RELT, CMDT, RELD & CMDD Operation (Slave)       5-         5-55       ACKT Operation       5-         5-56       ACKE Operation       5-         5-57       ACKD Operation       5-         5-58       BSYE Operation       5-         5-59       Pin Configuration Diagram       5-         5-50       Address Transmission from Master Device to Slave       5-         Device (WUP = 1)       5-1       5-1         5-61       Command Transmission from Master Device to Slave       5-1         5-62       Data Transmission from Slave Device to Master       5-1         5-63       Data Transmission from Slave Device to Master       5-1         5-64       Example of Serial Bus Configuration       5-1         5-65       READ Command Transfer Format       5-1         5-66       WRITE & END Command Transfer Format       5-1                                                        | 5-48          |                                         |                   |

| 5-50       Data       5-         5-51       Acknowledge Signal       5-         5-52       Busy Signal & Ready Signal       5-         5-53       RELT, CMDT, RELD & CMDD Operation (Master)       5-         5-54       RELT, CMDT, RELD & CMDD Operation (Slave)       5-         5-55       ACKT Operation       5-         5-56       ACKE Operation       5-         5-57       ACKD Operation       5-         5-58       BSYE Operation       5-         5-59       Pin Configuration Diagram       5-         5-50       Address Transmission from Master Device to Slave       5-         5-61       Command Transmission from Master Device to Slave       5-         5-62       Data Transmission from Master Device to Slave       5-1         5-63       Data Transmission from Slave Device to Slave       5-1         5-64       Example of Serial Bus Configuration       5-1         5-65       READ Command Transfer Format       5-1                                                                                                                                                                                                            | 5-49          |                                         |                   |

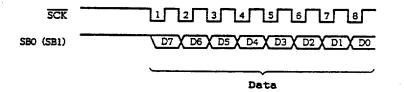

| 5-51       Acknowledge Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-50          |                                         |                   |

| 5-52       Busy Signal & Ready Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-51          |                                         |                   |

| 5-53       RELT, CMDT, RELD & CMDD Operation (Master)       5-         5-54       RELT, CMDT, RELD & CMDD Operation (Slave)       5-         5-55       ACKT Operation       5-         5-56       ACKE Operation       5-         5-57       ACKD Operation       5-         5-58       BSYE Operation       5-         5-59       Pin Configuration Diagram       5-         5-60       Address Transmission from Master Device to Slave       5-         5-61       Command Transmission from Master Device to Slave       5-1         5-62       Data Transmission from Master Device to Slave       5-1         5-63       Data Transmission from Slave Device to Master       5-1         5-64       Example of Serial Bus Configuration       5-1         5-65       READ Command Transfer Format       5-1                                                                                                                                                                                                                                                                                                                                                 | 5-52          |                                         |                   |

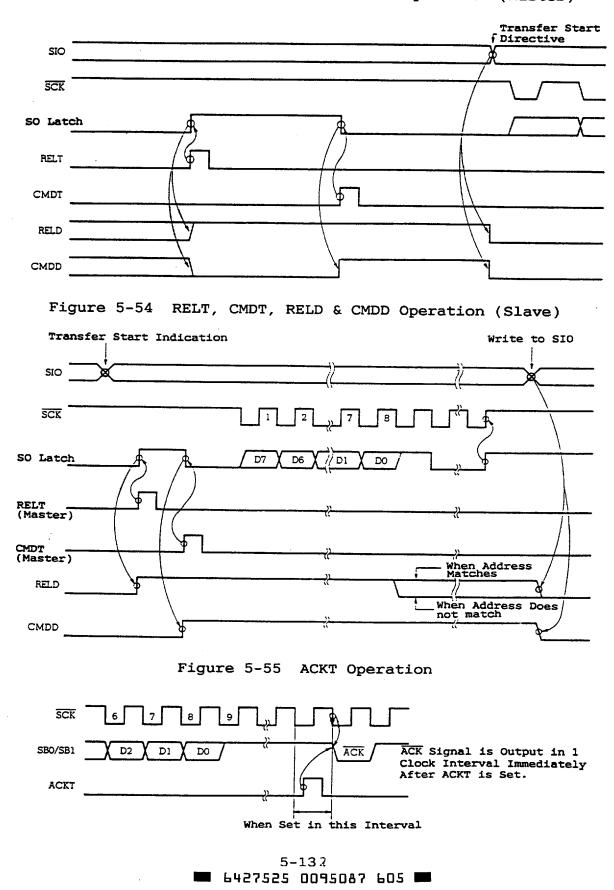

| 5-54       RELT, CMDT, RELD & CMDD Operation (Slave)       5         5-55       ACKT Operation       5         5-56       ACKE Operation       5         5-57       ACKD Operation       5         5-58       BSYE Operation       5         5-59       Pin Configuration Diagram       5         5-60       Address Transmission from Master Device to Slave       5         Device (WUP = 1)       5       5         5-61       Command Transmission from Master Device to Slave       5         Device       5       5         5-62       Data Transmission from Master Device to Slave       5         5-63       Data Transmission from Slave Device to Master       5         5-64       Example of Serial Bus Configuration       5         5-65       READ Command Transfer Format       51         5-66       WRITE & END Command Transfer Format       51                                                                                                                                                                                                                                                                                                | 5-53          |                                         |                   |

| <ul> <li>5-55 ACKT Operation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-54          |                                         |                   |

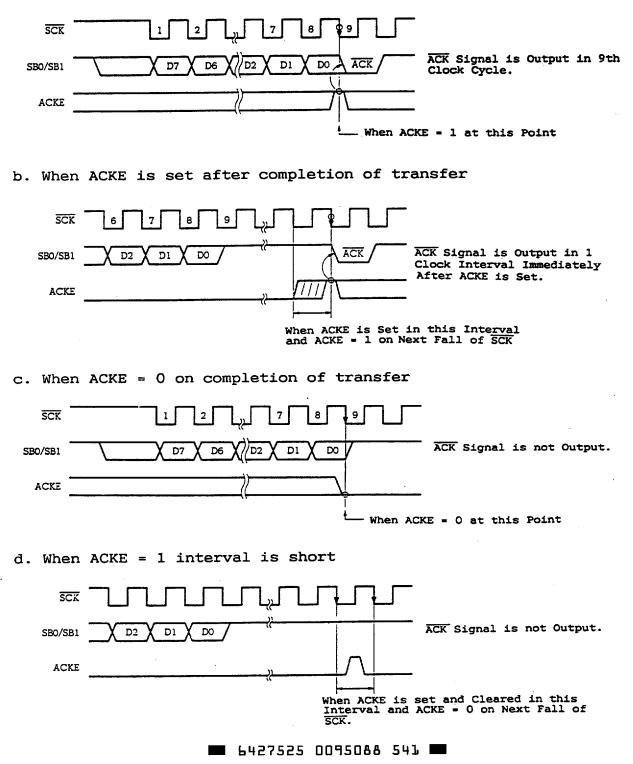

| <ul> <li>5-56 ACKE Operation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-55          |                                         |                   |

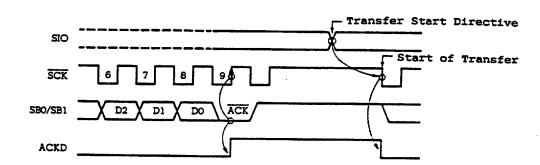

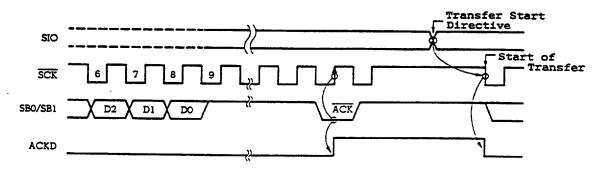

| <ul> <li>5-57 ACKD Operation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-56          |                                         |                   |

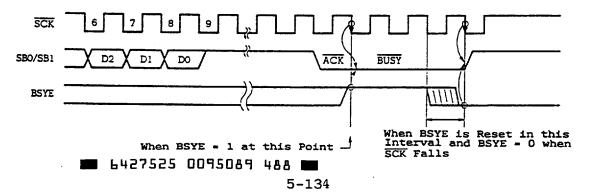

| <ul> <li>5-58 BSYE Operation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-57          |                                         |                   |

| <ul> <li>5-59 Pin Configuration Diagram</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-58          |                                         |                   |

| <ul> <li>5-60 Address Transmission from Master Device to Slave<br/>Device (WUP = 1)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-59          |                                         |                   |

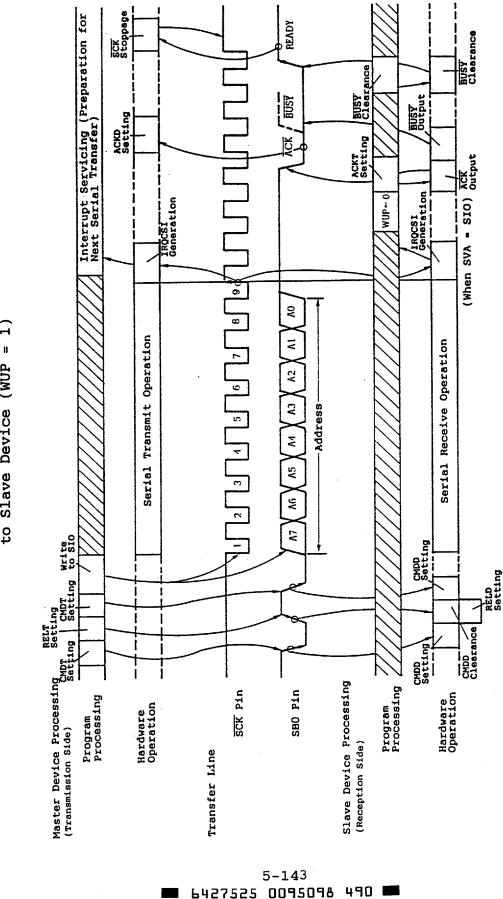

| Device (WUP = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-60          |                                         | 0 10)             |

| <ul> <li>5-61 Command Transmission from Master Device to Slave<br/>Device</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |                                         | 5-143             |

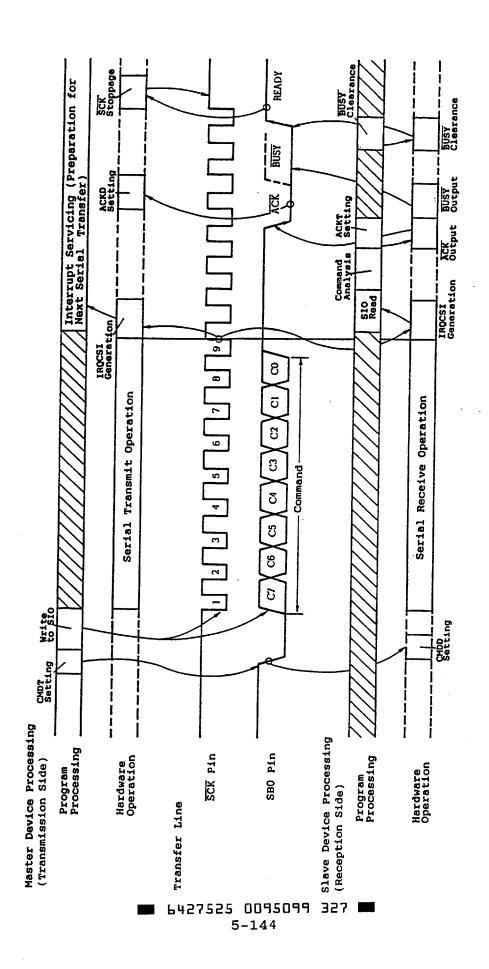

| Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-61          |                                         | 9-140             |

| <ul> <li>5-62 Data Transmission from Master Device to Slave<br/>Device</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |                                         | 5-144             |

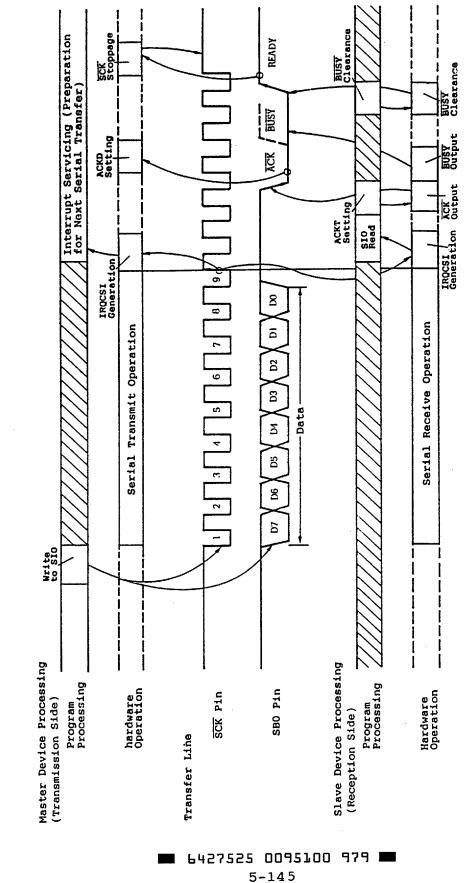

| Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-62          |                                         | 0-1 <del>44</del> |

| <ul> <li>5-63 Data Transmission from Slave Device to Master<br/>Device</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |                                         | 5-145             |

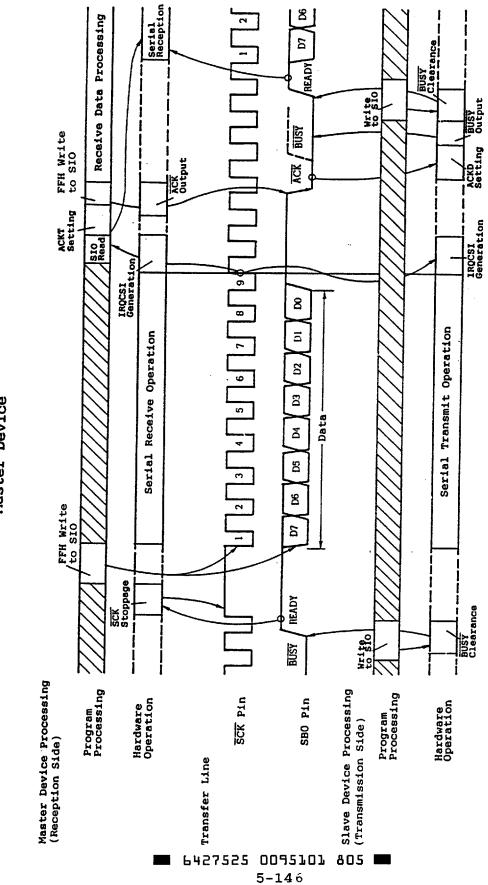

| Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-63          |                                         | 2-142             |

| 5-64Example of Serial Bus Configuration5-15-65READ Command Transfer Format5-15-66WRITE & END Command Transfer Format5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |                                         | 5 146             |

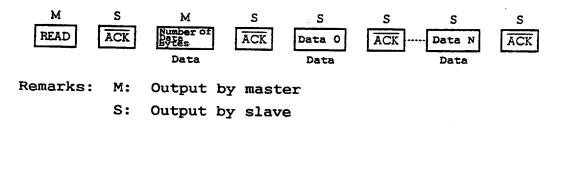

| 5-65 READ Command Transfer Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-64          |                                         |                   |

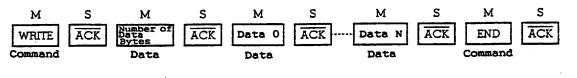

| 5-66 WRITE & END Command Transfer Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |                                         |                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |                                         |                   |

| Commune Itemater Putmat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |                                         |                   |

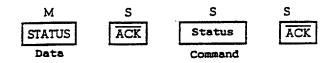

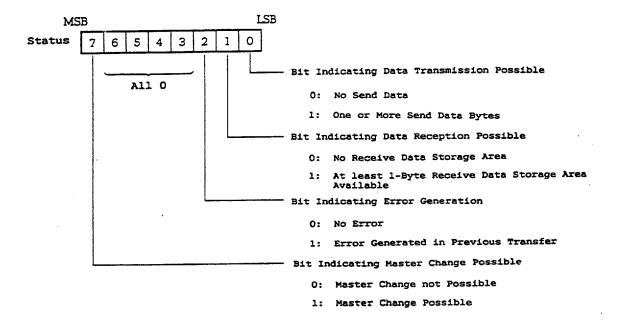

| 5-68 STATUS Command Transfer Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |                                         |                   |

•

- xiv -■ 6427525 0094859 000 ■

-

| Figure |  |

|--------|--|

| No.    |  |

.

Page

-----

| 5-69 | STATUS Command Status Format                          |

|------|-------------------------------------------------------|

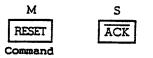

| 5-70 | RESET Command Transfer Format                         |

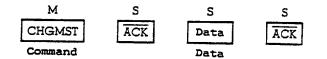

| 5-71 | CHGMST Command Transfer Format                        |

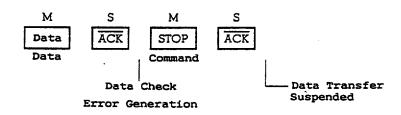

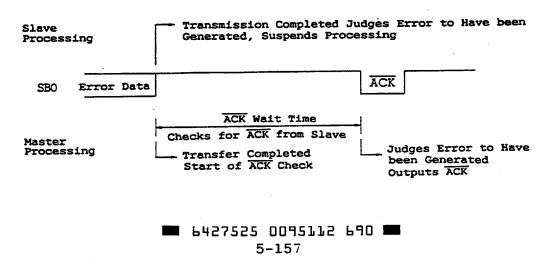

| 5-72 | Master & Slave Operation in Case of Error             |

|      | Generation                                            |

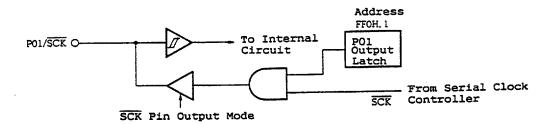

| 5-73 | SCK/P01 Pin Configuration 5-159                       |

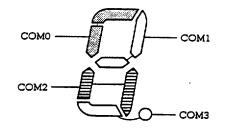

| 5-74 | LCD Controller/Driver Block Diagram                   |

| 5-75 | Display Mode Register Format 5-166                    |

| 5-76 | Display Control Register Format                       |

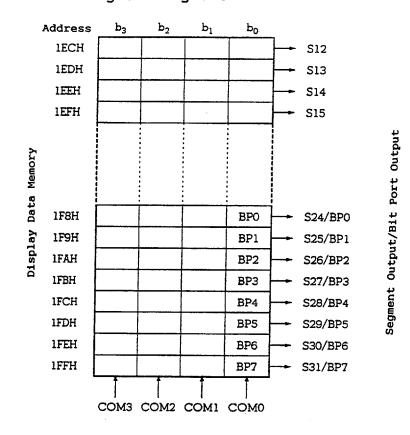

| 5-77 | Data Memory Map 5-169                                 |

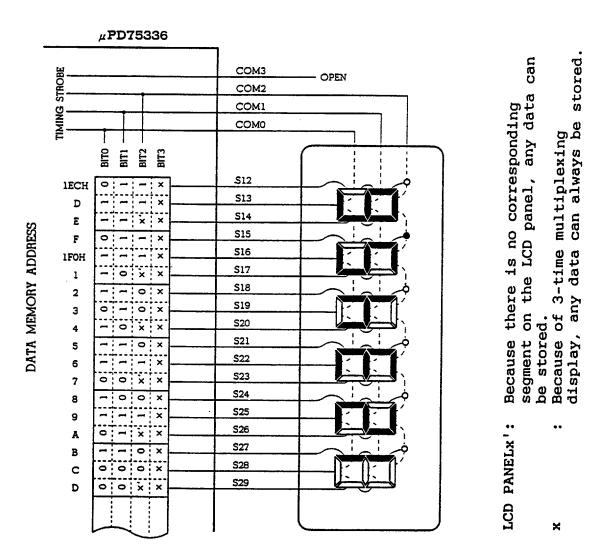

| 5-78 | Relations between Display Data Memory and Common      |

|      | and Segment Signals 5-170                             |

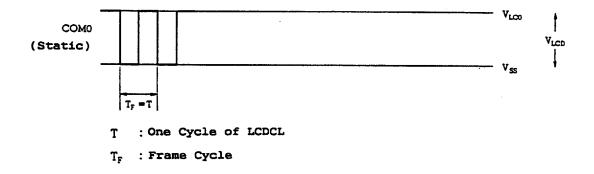

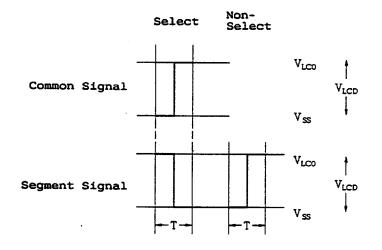

| 5-79 | Common Signal Waveform (Static)                       |

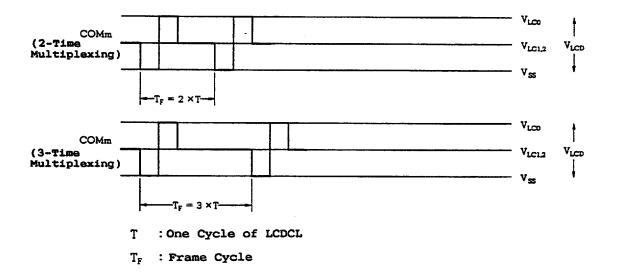

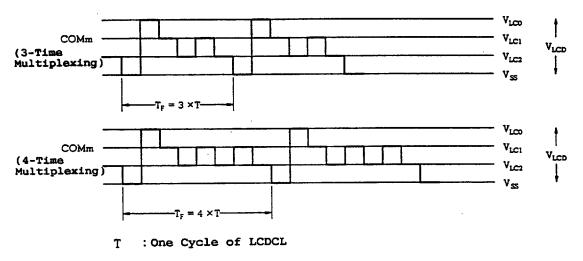

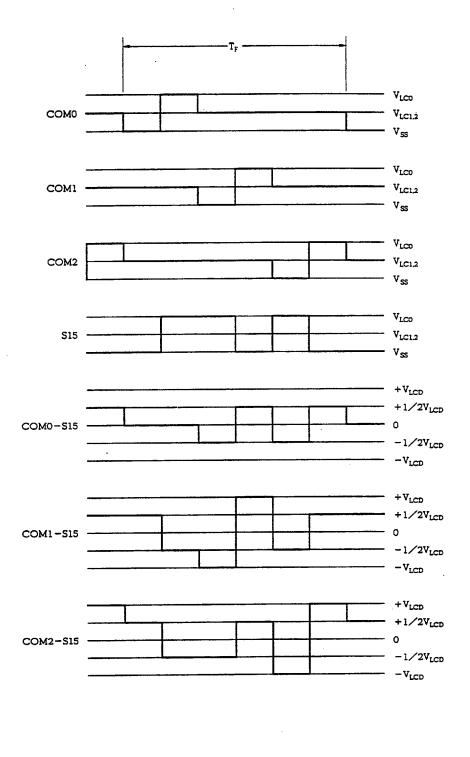

| 5-80 | Common Signal Waveform (1/2 Bias Method) 5-174        |

| 5-81 | Common Signal Waveform (1/3 Bias Method) 5-175        |

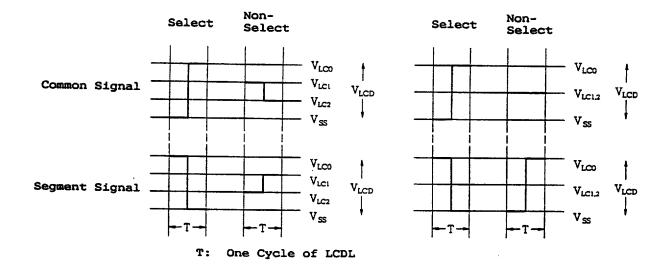

| 5-82 | Common and Segment Signal Voltages and Phases 5-176   |

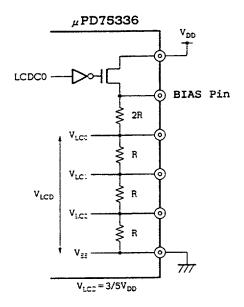

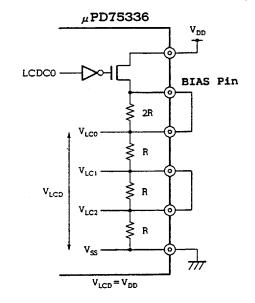

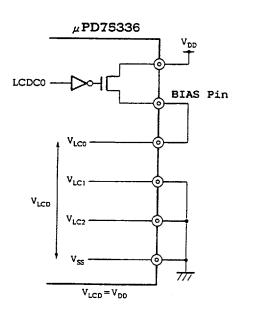

| 5-83 | LCD Drive Power Supply Connection Examples            |

|      | (with On-Chip Split Resistors) 5-179                  |

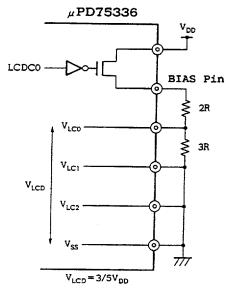

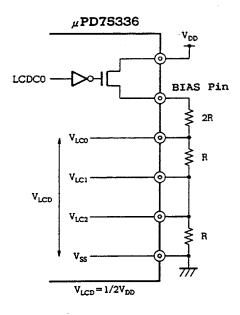

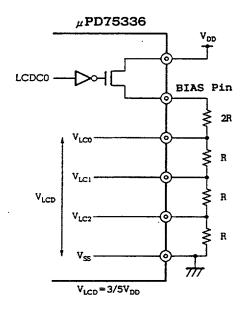

| 5-84 | LCD Drive Power Supply Connection Examples            |

|      | (with External Split Resistors)                       |

| 5-85 | Static LCD Display Pattern and Electrode Wiring 5-183 |

| 5-86 | Static LCD Panel Wiring Example                       |

| 5-87 | Static LCD Drive Waveform Example                     |

| 5-88 | 2-Time Multiplexing LCD Display Parameter and         |

|      | Electrode Wiring 5-187                                |

| 5-89 | 2-Time Multiplexing LCD Panel Wiring Example 5-188    |

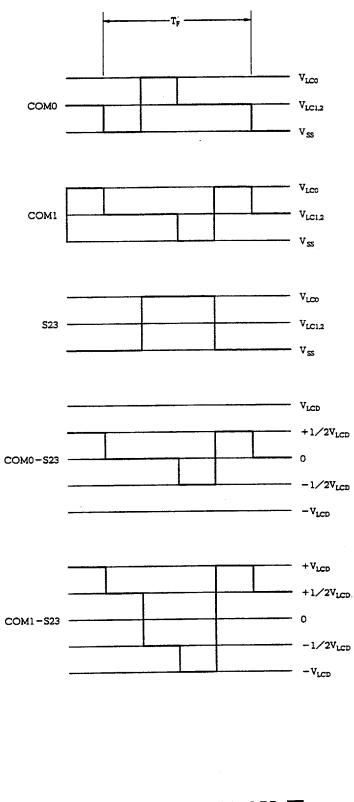

| 5-90 | 2-Time Multiplexing LCD Drive Waveform Example        |

|      | (1/2 Bias Method) 5-189                               |

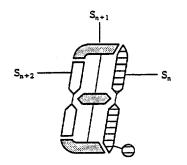

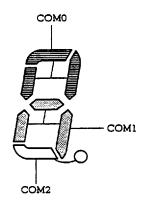

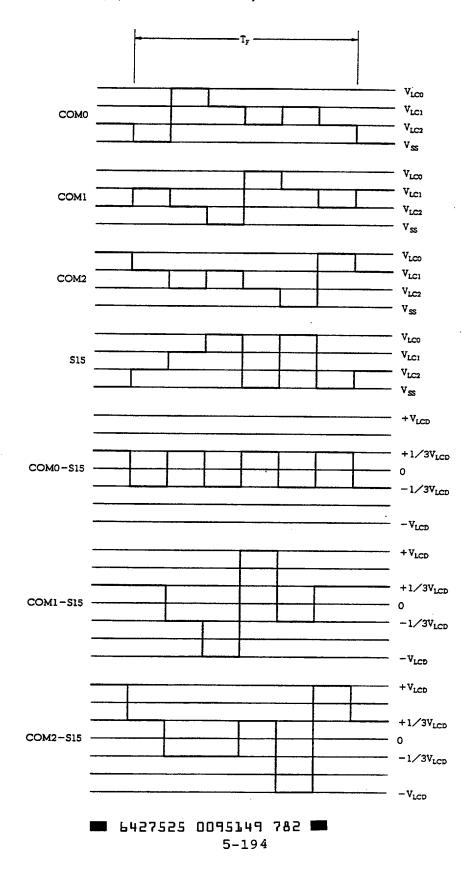

| 5-91 | 3-Time Multiplexing LCD Display Pattern and           |

|      | Electrode Wiring 5-191                                |

| 5-92 | 3-Time Multiplexing LCD Panel Wiring Example 5-192    |

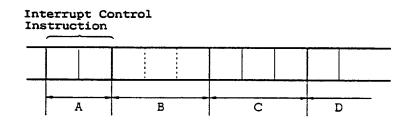

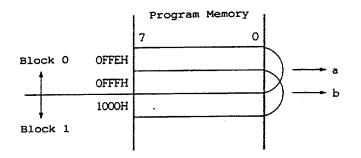

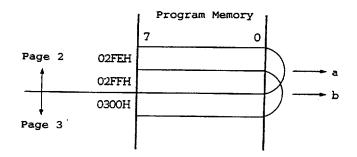

| 5-93 | 3-Time Multiplexing LCD Drive Waveform Example        |