#### **Features**

- Host Interface

- ATAPI Compatible (ANSI ATA-1, ATA-2, ATA-3 and ATA-4 compliant) Host Mode

- Ultra DMA Support (66 MB/sec)

- High-current (12 mA) Drivers for Direct Connection to AT Cable (slew rate controlled)

- 256-byte Bidirectional Data FIFO to Improve Throughput

- Embedded Processor

- ARM7TDMI<sup>™</sup> RISC Processor

- Open Processor Architecture Protects Firmware Investment

- Wide Selection of Development Tools from ARM<sup>®</sup> and Third-party Vendors

- 1-Mbyte External Flash Interface for Code/Data

- 16-Kbyte Internal SRAM for Data

- Buffer Manager

- Supports SDRAM up to 32 Mbytes (16M x 16)

- DRAM Bandwidth of up to 160 Mbytes/sec (burst)

- Priority Buffer Arbiter

- Read Channel Interface

- Nibble Interface Speed (code cell rate): 40 MHz (160 Mbs, DVD 5X)

- EFM (8/14) and EFM+ (8/16) Demodulation

- Write Channel Interface

- Serial Interface Speed (code cell rate): DVD 2X

- EFM (8/14) and EFM+ (8/16) Modulation

- DVD-R Pre-pit Decoder with Error Detection and Correction

- DVD+RW ADIP Decoder with Error Detection and Correction

- CD-R/RW ATIP Decoder with Error Detection

- Error Correction Logic

- DVD Data Block Error Detection and Correction

- DVD EDC Error Detection

- DVD IEC Header Error Detection and Correction

- All CD Formats

- Lower Power Operation with 3.3V Core and 5V Tolerant I/Os

# **Description**

The Atmel AT78C1501 is a high-performance DVD/CD ATAPI Ultra DMA66 Interface Controller, designed to interface to the AT78C1502 DVD Servo Controller, the AT78C1503 DVD Read Channel and the AT78C1504 Automatic Laser Power Control (ALPC). The interface controller (AT78C1501) contains ARM® and AVR® microcontrollers, buffer management, error correction code (ECC) and encoder/decoder (ENDEC) for DVD and CD. Also included are a writeable control store for timing generation and an on-board frequency synthesizer to generate system frequencies from one crystal. ATA66/ATAPI66 and I2S interfaces are provided.

The major functions of the AT78C1501 include data format encoding/decoding, error detection/correction, buffer management, ATAPI host interface and serial interface master. The AT78C1501 also includes an embedded ARM7 RISC Core to perform all system (drive) microprocessor functions and an embedded AVR RISC core to perform internal data path and buffer management control.

The AT78C1501 disk formats include DVD-ROM, DVD-RAM (Read/Write), CD-ROM, CD-R (Read/Write), CD-RW (Read/Write), DVD-R (Read/Write), DVD-RW (Read/Write), and DVD+RW (Read/Write).

# DVD/CD ATAPI Controller

AT78C1501

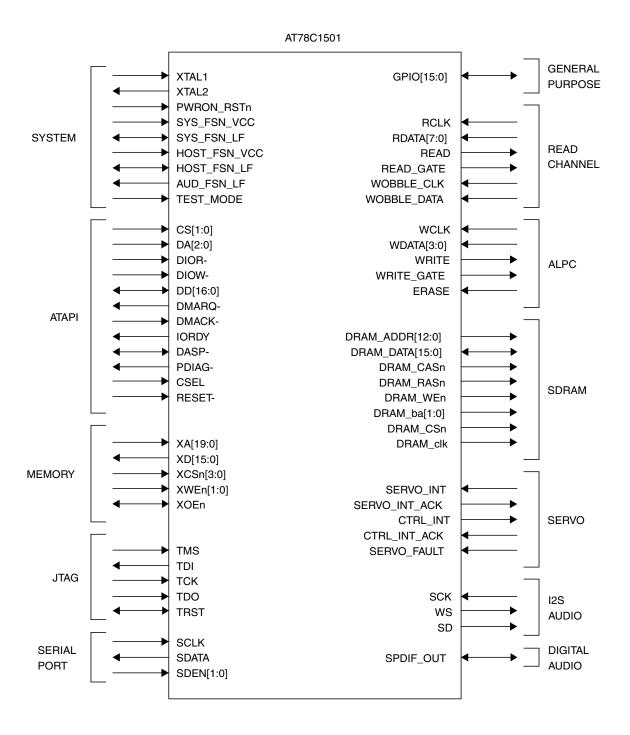

Figure 1. DVD System Block Diagram

Table 1. DC Parameters

| Symbol          | Parameter         | Min | Nom | Max | Units | Notes  |

|-----------------|-------------------|-----|-----|-----|-------|--------|

| V <sub>CC</sub> | Supply Voltage    | 3.0 | 3.3 | 3.6 | V     |        |

| I <sub>CC</sub> | Operating Current | _   |     | 500 | mA    | Note 1 |

Note: 1. Values listed are advance information and are likely to change as production silicon is characterized.

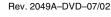

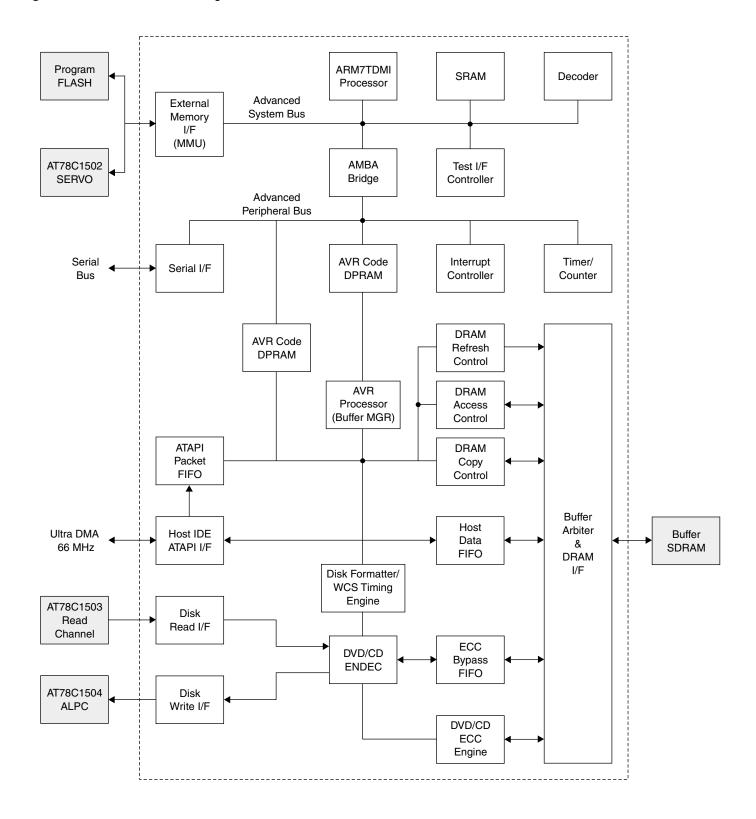

Figure 2. Pin Assignment

# **Pin Definitions**

## **General I/O Pin List**

Table 1. General I/O Pin List

| Pin Name     | Pin # | Pin Type | Pin Description                                                                                                          |  |  |  |

|--------------|-------|----------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|

| XTAL1        | 145   | I        | Crystal Input                                                                                                            |  |  |  |

| XTAL2        | 146   | В        | Crystal I/O                                                                                                              |  |  |  |

| PWRON_RSTn   | 153   | I        | Power On Reset: This signal is used to initialize all logic in the controller including the ARM7 and AVR cores.          |  |  |  |

| TEST_MODE    | 181   | I        | RAM Test Mode: This signal is used by the chip tester to place all embedded memory cells in BIST mode for test.          |  |  |  |

| GPIO[0]      | 172   | Р        |                                                                                                                          |  |  |  |

| GPIO[1]      | 173   | Р        |                                                                                                                          |  |  |  |

| GPIO[2]      | 174   | Р        |                                                                                                                          |  |  |  |

| GPIO[3]      | 175   | Р        |                                                                                                                          |  |  |  |

| GPIO[4]      | 177   | Р        |                                                                                                                          |  |  |  |

| GPIO[5]      | 178   | Р        |                                                                                                                          |  |  |  |

| GPIO[6]      | 179   | Р        |                                                                                                                          |  |  |  |

| GPIO[7]      | 180   | Р        | O and and I Brown and I I/O                                                                                              |  |  |  |

| GPIO[8]      | 128   | Р        | General Purpose I/O                                                                                                      |  |  |  |

| GPIO[9]      | 129   | Р        |                                                                                                                          |  |  |  |

| GPIO[10]     | 130   | Р        |                                                                                                                          |  |  |  |

| GPIO[11]     | 131   | Р        |                                                                                                                          |  |  |  |

| GPIO[12]     | 189   | Р        |                                                                                                                          |  |  |  |

| GPIO[13]     | 190   | Р        |                                                                                                                          |  |  |  |

| GPIO[14]     | 191   | Р        |                                                                                                                          |  |  |  |

| GPIO[15]     | 192   | Р        |                                                                                                                          |  |  |  |

| BCLK_out     | 171   | 0        | Processor Clock Output: This signal is the ARM7 and AVR core clock. It can be used as the clock input to the servo chip. |  |  |  |

| SYS_FSN_VCC  | 158   | I        | System FSN VCC: This is the power supply pin for the system frequency synthesizer.                                       |  |  |  |

| SYS_FSN_LF   | 159   | 0        | System FSN Loop Filter: This signal is the loop filter pin for the system frequency synthesizer.                         |  |  |  |

| HOST_FSN_VCC | 154   | I        | Host FSN VCCc: This is the power supply pin for the host frequency synthesizer.                                          |  |  |  |

| HOST_FSN_LF  | 155   | 0        | Host FSN Loop Filter: This signal is the loop filter pin for the host frequency synthesizer.                             |  |  |  |

| AUD_FSN_LF   | 187   | 0        | Audio FSN Loop Filter: This signal is the loop filter pin for the audio frequency synthesizer.                           |  |  |  |

#### **ATAPI Interface**

The AT78C1501 supports the ATAPI CD-ROM specification (IDE CD-ROM Interface) and can drive IDE signals directly. The host interface contains a 12-byte command packet FIFO and IDE registers for transferring command and status data. The host interface also contains a data FIFO for transferring data from buffer DRAM to the host. The host interface contains the following pins:

Table 2. ATAPI Interface I/O Pin List

| Pin Name | Pin # | Pin Type | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|----------|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CS0-     | 205   | I        | Device Chip Select 0: Chip select signal from host to select the Command Block registers.                                                                                                                                                                                                                                                                                                                                                |  |

| CS1-     | 204   | I        | Device Chip Select 1: Chip select signal from host to select the Command Block registers.                                                                                                                                                                                                                                                                                                                                                |  |

| DD[15]   | 13    | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DD[14]   | 15    | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DD[13]   | 17    | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DD[12]   | 19    | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DD[11]   | 22    | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DD[10]   | 24    | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DD[9]    | 26    | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DD[8]    | 28    | I/O      | Device Data Bus: Bidirectional data bus between the host and the device. The lower eight                                                                                                                                                                                                                                                                                                                                                 |  |

| DD[7]    | 29    | I/O      | bits are used for 8-bit register transfers. Data transfers are 16 bits wide.                                                                                                                                                                                                                                                                                                                                                             |  |

| DD[6]    | 27    | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DD[5]    | 25    | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DD[4]    | 23    | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DD[3]    | 20    | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DD[2]    | 18    | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DD[1]    | 16    | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DD[0]    | 14    | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DASP-    | 203   | I/O      | Device Active or Slave Present: This is a time-multiplexed signal that indicates that a device is active or that Device 1 is present.                                                                                                                                                                                                                                                                                                    |  |

| DA[2]    | 206   |          |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DA[1]    | 3     | ı        | Device Address: This is the 3-bit binary coded address asserted by the host to access a                                                                                                                                                                                                                                                                                                                                                  |  |

| DA[0]    | 207   |          | register or data port in the device.                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| DMACK-   | 5     | I        | DMA Acknowledge: This signal shall be used by the host in response to DMARQ- to initiate DMA transfers.                                                                                                                                                                                                                                                                                                                                  |  |

| DMARQ-   | 11    | 0        | DMA Request: This signal, used for DMA data transfers between the host and device, shall be asserted by the device when it is ready to transfer data to or from the host. The direction of data transfer is controlled by DIOR- and DIOW This signal is used in a handshake manner with DMACK, i.e., the device shall wait until the host asserts DMACK, before negating DMARQ and reasserting DMARQ, if there is more data to transfer. |  |

| INTRQ    | 4     | 0        | Device Interrupt: This signal is used by the selected device to interrupt the host system. When the nIEN bit is cleared to "0" and the device is selected, INTRQ shall be enabled through a tristate buffer. When the nIEN bit is set to "1" or the device is not selected, the INTRQ signal shall be in a high impedance state.                                                                                                         |  |

Table 2. ATAPI Interface I/O Pin List (Continued)

| Pin Name                     | Pin # | Pin Type | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|------------------------------|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DIOR-<br>HDMARDY-<br>HSTROBE | 8     | I        | Device I/O Read: This is the strobe signal asserted by the host to read device registers or the data port.  Host DMA Ready: This signal is a flow control signal for Ultra DMA data in bursts. This signal is asserted by the host to indicate to the host that the device is ready to receive Ultra DMA data in bursts. The host may negate HDMARDY- to pause an Ultra DMA data in burst.  Host Strobe: This signal is the data in strobe from the host for an Ultra DMA data out burst. Both the rising and falling edge of HSTROBE latch the data from DD[15:0] into the device. The host may stop generating DSTROBE edges to pause an Ultra DMA data out burst.                                                                                    |  |

| IORDY<br>DDMARDY-<br>DSTROBE | 7     | 0        | Device I/O Ready: This signal is negated to extend the host transfer cycle of any host regist access (Read or Write) when the device is not ready to respond to a data transfer request. Device DMA Ready: This signal is a flow control signal for Ultra DMA data out bursts. This signal is asserted by the device to indicate to the host that the device is ready to receive Ult DMA data out bursts. The device may negate DDMARDY- to pause an Ultra DMA data out burst.  Device Strobe: This signal is the data in strobe from the device for an Ultra DMA data in burst. Both the rising and falling edge of DSTROBE latch the data from DD[15:0] into the host. The device may stop generating DSTROBE edges to pause an Ultra DMA data in bur |  |

| DIOW-<br>STOP                | 10    | ı        | Device I/O Write: This is the strobe signal asserted by the host to write device registers or the data port.  STOP: STOP shall be negated by the host before data is transferred in an Ultra DMA burst. Assertion of STOP by the host during an Ultra DMA burst signals the termination of the Ultra DMA burst.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| PDIAG-                       | 2     | 0        | Device Passed Diagnostics: This signal shall be asserted by Device 1 to indicate to Device 0 that it has completed diagnostics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| CSEL                         | 6     | I        | Cable Select: Used to select Ddevice 0 or 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| RESET-                       | 202   | I        | Device Reset: This signal, referred to as hardware reset, shall be used by the host to reset the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

#### JTAG/ICE Interface

The JTAG/ICE Interface is used as the in-circuit emulator for the ARM7TDMI Processor.

Table 3. JTAG/ICE Interface I/O Pin List

| Pin Name | Pin # | Pin Type | Pin Description  |

|----------|-------|----------|------------------|

| TMS      | 194   | I        | Test Mode Select |

| TDI      | 196   | I        | Test Data Input  |

| тск      | 195   | I        | Test Clock       |

| TDO      | 197   | 0        | Test Data Output |

| TRST     | 193   | I        | Test Reset       |

### **Disk Read Interface**

The Disk Read Interface connects the DVD/CD Read Channel device to the controller.

Table 4. Disk Read Interface I/O Pin List

| Pin Name    | Pin # | Pin Type | Pin Description                                                                                                                                                                                                                |

|-------------|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCLK        | 135   | I        | Recovered Clock: This is the recovered data rate clock from the read channel. This clock is used for the sync detection logic as well as the WCS programmable state machine.                                                   |

| RDATA[0]    | 136   | ı        |                                                                                                                                                                                                                                |

| RDATA[1]    | 137   | I        |                                                                                                                                                                                                                                |

| RDATA[2]    | 138   | I        | B 15 1 Ti 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                    |

| RDATA[3]    | 139   | I        | Recovered Data: This is the recovered data from the disk. This is used by the sync detection and                                                                                                                               |

| RDATA[4]    | 141   | I        | ENDEC to recover the user data on the disk.                                                                                                                                                                                    |

| RDATA[5]    | 142   | I        |                                                                                                                                                                                                                                |

| RDATA[6]    | 143   | I        |                                                                                                                                                                                                                                |

| RDATA[7]    | 144   | l        |                                                                                                                                                                                                                                |

| READ        | 132   | 0        | Read Mode: This signal is used to place the ALPC in read mode.                                                                                                                                                                 |

| READ_GATE   | 134   | 0        | Read Gate: This signal is used by the read channel to lock the PLL to the recovered data instead of the synthesizer.                                                                                                           |

| WOBBLE_CLK  | 169   | I        | Wobble Clock: Recovered wobble clock from read channel. This clock is used for the ADIP, ATIP and PRE-PIT decoder state machines. This clock is also used to clock the WCS programmable state machine during write operations. |

| WOBBLE_DATA | 168   | I        | Wobble Data: Recovered wobble data from read channel. This is used to decode the ADIP, ATIP and PRE-PIT data.                                                                                                                  |

#### **Disk Write Interface**

The Disk Write Interface connects the DVD/CD Write device to the controller.

Table 5. Disk Write Interface I/O Pin List

| Pin Name      | Pin # | Pin Type | Pin Description                                                                                                                                                                                               |

|---------------|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WCLK          | 166   | ı        | Write Clock: Bit clock used to generate the NRZI data stream to the ALPC. This clock originates from the recovered wobble clock in the read channel, which is then multiplied up to the bit rate in the ALPC. |

| WRITE_DATA[0] | 163   | 0        |                                                                                                                                                                                                               |

| WRITE_DATA[1] | 164   | 0        | Write Data: This is the NRZI data stream from the                                                                                                                                                             |

| WRITE_DATA[2] | 165   | 0        | controller to the ALPC.                                                                                                                                                                                       |

| WRITE_DATA[3] | 166   | 0        |                                                                                                                                                                                                               |

| WRITE         | 161   | 0        | Write Mode: This signal is used to place the ALPC in write mode.                                                                                                                                              |

| WRITE_GATE    | 162   | 0        | Write Gate: This signal is used by the ALPC to allow writing to the disk.                                                                                                                                     |

| ERASE         | 157   | 0        | Erase Mode: This signal indicates that the ALPC should use the erase power level between write pulse trains. This is used for any rewritable disk format. (DVD-RW, CD-RW, DVD+RW).                            |

#### **DRAM Interface**

The DRAM Interface connects the controller to the buffer DRAM.

Table 6. DRAM Interface I/O Pin List

| Pin Name      | Pin # | Pin Type | Pin Description       |  |

|---------------|-------|----------|-----------------------|--|

| DRAM_RASn     | 96    | 0        | Row Address Strobe    |  |

| DRAM_CASn     | 95    | 0        | Column Address Strobe |  |

| DRAM_ADDR[0]  | 102   | 0        |                       |  |

| DRAM_ADDR[1]  | 103   | 0        |                       |  |

| DRAM_ADDR[2]  | 106   | 0        |                       |  |

| DRAM_ADDR[3]  | 107   | 0        |                       |  |

| DRAM_ADDR[4]  | 108   | 0        |                       |  |

| DRAM_ADDR[5]  | 109   | 0        |                       |  |

| DRAM_ADDR[6]  | 110   | 0        | DRAM Buffer Address   |  |

| DRAM_ADDR[7]  | 111   | 0        |                       |  |

| DRAM_ADDR[8]  | 112   | 0        |                       |  |

| DRAM_ADDR[9]  | 113   | 0        |                       |  |

| DRAM_ADDR[10] | 101   | 0        |                       |  |

| DRAM_ADDR[11] | 115   | 0        |                       |  |

| DRAM_ADDR[12] | 116   | 0        |                       |  |

| DRAM_DATA[0]  | 83    | I/O      |                       |  |

| DRAM_DATA[1]  | 84    | I/O      |                       |  |

| DRAM_DATA[2]  | 85    | I/O      |                       |  |

| DRAM_DATA[3]  | 86    | I/O      |                       |  |

| DRAM_DATA[4]  | 87    | I/O      |                       |  |

| DRAM_DATA[5]  | 88    | I/O      |                       |  |

| DRAM_DATA[6]  | 89    | I/O      |                       |  |

| DRAM_DATA[7]  | 91    | I/O      | DRAM Buffer Data      |  |

| DRAM_DATA[8]  | 118   | I/O      | Dhaw builer Data      |  |

| DRAM_DATA[9]  | 119   | I/O      |                       |  |

| DRAM_DATA[10] | 120   | I/O      |                       |  |

| DRAM_DATA[11] | 121   | I/O      |                       |  |

| DRAM_DATA[12] | 122   | I/O      |                       |  |

| DRAM_DATA[13] | 124   | I/O      |                       |  |

| DRAM_DATA[14] | 125   | I/O      |                       |  |

| DRAM_DATA[15] | 127   | I/O      |                       |  |

| DRAM_WEn      | 94    | 0        | DRAM Write Strobe     |  |

| DRAM_cs_n     | 97    | 0        | DRAM Chip Select      |  |

| DRAM_ba[0]    | 99    | 0        | DDAM Book Coloot      |  |

| DRAM_ba[1]    | 100   | 0        | DRAM Bank Select      |  |

| DRAM_clk      | 117   | 0        | DRAM Clock            |  |

# **External Memory Interface**

The External Memory Interface connects external program memory to the controller. The DVD RAM Servo device is also connected to this bus.

Table 7. External Memory Interface I/O Pin List

| XA[0]   55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Pin Name | Pin # | Pin Type | Pin Description        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|----------|------------------------|

| XA[2]   51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | XA[0]    | 55    | 0        |                        |

| XA[3]   50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |       |          |                        |

| XA[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | XA[2]    | 51    | 0        |                        |

| XA[5]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | XA[3]    | 50    | 0        |                        |

| XA[6]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | XA[4]    | 49    | 0        |                        |

| XA[7]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | XA[5]    |       |          |                        |

| XA[8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | XA[6]    |       |          |                        |

| XA[9]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |       |          |                        |

| XA[10]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | 44    | 0        |                        |

| XA[11]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XA[9]    | 43    |          |                        |

| XA[12]   39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | XA[10]   |       |          | memory banks           |

| XA[13]   38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | XA[11]   | 41    |          |                        |

| XA[14]   37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | XA[12]   | 39    |          |                        |

| XA[15]   36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |       |          |                        |

| XA[16]   35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          | 37    | 0        |                        |

| XA[17]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |       |          |                        |

| XA[18]   32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |       |          |                        |

| XA[19]   31   O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |       |          |                        |

| XD[0]   56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |       |          |                        |

| XD[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | XA[19]   | 31    | 0        |                        |

| XD[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | XD[0]    | 56    | I/O      |                        |

| XD[3]   59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | XD[1]    | 57    | I/O      |                        |

| XD[4]       60       I/O         XD[5]       61       I/O         XD[6]       63       I/O         XD[7]       64       I/O         XD[8]       65       I/O         XD[9]       66       I/O         XD[10]       67       I/O         XD[11]       68       I/O         XD[12]       69       I/O         XD[13]       70       I/O         XD[14]       72       I/O         XD[15]       73       I/O         XCSn[0]       76       O         XCSn[1]       77       O         XCSn[2]       78       O         XCSn[3]       79       O         XWEn[0]       80       O         XWEn[1]       82       O         External Write Enable | XD[2]    | 58    | I/O      |                        |

| XD[5]       61       I/O         XD[6]       63       I/O         XD[7]       64       I/O         XD[8]       65       I/O         XD[9]       66       I/O         XD[10]       67       I/O         XD[11]       68       I/O         XD[12]       69       I/O         XD[13]       70       I/O         XD[14]       72       I/O         XD[15]       73       I/O         XCSn[0]       76       O         XCSn[1]       77       O         XCSn[2]       78       O         XCSn[3]       79       O         XWEn[0]       80       O         XWEn[1]       82       O         External Write Enable                                  | XD[3]    | 59    | I/O      |                        |

| XD[6]       63       I/O         XD[7]       64       I/O         XD[8]       65       I/O         XD[9]       66       I/O         XD[10]       67       I/O         XD[11]       68       I/O         XD[12]       69       I/O         XD[13]       70       I/O         XD[14]       72       I/O         XD[15]       73       I/O         XCSn[0]       76       O         XCSn[1]       77       O         XCSn[2]       78       O         XCSn[3]       79       O         XWEn[0]       80       O         XWEn[1]       82       O     External Data Bus   External Data Bus                                                       | XD[4]    | 60    | I/O      |                        |

| XD[7]       64       I/O       External Data Bus         XD[8]       65       I/O       External Data Bus         XD[9]       66       I/O       I/O         XD[10]       67       I/O       I/O         XD[11]       68       I/O       I/O         XD[12]       69       I/O       I/O         XD[13]       70       I/O       I/O         XD[14]       72       I/O       I/O         XCSn[0]       76       O       O         XCSn[1]       77       O       External Chip Select         XCSn[2]       78       O       External Write Enable         XWEn[0]       80       O       External Write Enable                               | XD[5]    | 61    | I/O      |                        |

| XD[8]   65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | XD[6]    | 63    | I/O      |                        |

| XD[8]   65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | XD[7]    | 64    | I/O      | External Data Bug      |

| XD[10]       67       I/O         XD[11]       68       I/O         XD[12]       69       I/O         XD[13]       70       I/O         XD[14]       72       I/O         XD[15]       73       I/O         XCSn[0]       76       O         XCSn[1]       77       O         XCSn[2]       78       O         XCSn[2]       78       O         XCSn[3]       79       O         XWEn[0]       80       O         XWEn[1]       82       O         External Write Enable                                                                                                                                                                      | XD[8]    | 65    | I/O      | External Data Bus      |

| XD[11]       68       I/O         XD[12]       69       I/O         XD[13]       70       I/O         XD[14]       72       I/O         XD[15]       73       I/O         XCSn[0]       76       O         XCSn[1]       77       O         XCSn[2]       78       O         XCSn[2]       78       O         XCSn[3]       79       O         XWEn[0]       80       O         XWEn[1]       82       O    External Write Enable                                                                                                                                                                                                             | XD[9]    | 66    | I/O      |                        |

| XD[12]       69       I/O         XD[13]       70       I/O         XD[14]       72       I/O         XD[15]       73       I/O         XCSn[0]       76       O         XCSn[1]       77       O         XCSn[2]       78       O         XCSn[3]       79       O         XWEn[0]       80       O         XWEn[1]       82       O         External Write Enable                                                                                                                                                                                                                                                                           | XD[10]   | 67    | I/O      |                        |

| XD[13]       70       I/O         XD[14]       72       I/O         XD[15]       73       I/O         XCSn[0]       76       O         XCSn[1]       77       O         XCSn[2]       78       O         XCSn[3]       79       O         XWEn[0]       80       O         XWEn[1]       82       O         External Write Enable                                                                                                                                                                                                                                                                                                             | XD[11]   | 68    | I/O      |                        |

| XD[14]       72       I/O         XD[15]       73       I/O         XCSn[0]       76       O         XCSn[1]       77       O         XCSn[2]       78       O         XCSn[3]       79       O         XWEn[0]       80       O         XWEn[1]       82       O         External Write Enable                                                                                                                                                                                                                                                                                                                                               | XD[12]   | 69    | I/O      |                        |

| XD[15]       73       I/O         XCSn[0]       76       O         XCSn[1]       77       O         XCSn[2]       78       O         XCSn[3]       79       O         XWEn[0]       80       O         XWEn[1]       82       O         External Write Enable                                                                                                                                                                                                                                                                                                                                                                                 | XD[13]   | 70    | I/O      |                        |

| XCSn[0]       76       O         XCSn[1]       77       O         XCSn[2]       78       O         XCSn[3]       79       O         XWEn[0]       80       O         XWEn[1]       82       O         External Write Enable                                                                                                                                                                                                                                                                                                                                                                                                                   | XD[14]   | 72    | I/O      |                        |

| XCSn[1]       77       O       External Chip Select         XCSn[2]       78       O       External Chip Select         XCSn[3]       79       O       O       External Write Enable         XWEn[0]       80       O       External Write Enable                                                                                                                                                                                                                                                                                                                                                                                             | XD[15]   | 73    | I/O      |                        |

| XCSn[1]       77       O       External Chip Select         XCSn[2]       78       O       External Chip Select         XCSn[3]       79       O       O       External Write Enable         XWEn[0]       80       O       External Write Enable                                                                                                                                                                                                                                                                                                                                                                                             | XCSn[0]  | 76    | 0        |                        |

| XCSn[2]       78       O       External Cnip Select         XCSn[3]       79       O         XWEn[0]       80       O       External Write Enable         XWEn[1]       82       O                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | l     |          |                        |

| XCSn[3]         79         O           XWEn[0]         80         O           XWEn[1]         82         O   External Write Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |       |          | External Chip Select   |

| XWEn[1] 82 O External Write Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |       |          |                        |

| XWEn[1] 82 O External Write Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | 80    | 0        |                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |       |          | External Write Enable  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |       |          | External Output Enable |

#### **Servo Interface**

The Servo Interface connects the servo device to the controller.

Table 8. Servo Interface I/O Pin List

| Pin Name      | Pin # | Pin Type | Pin Description                                                                                                                              |

|---------------|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| SERVO_INT     | 147   | I        | Servo Interrupt Input: Interrupt signal from the servo to the controller                                                                     |

| SERVO_INT_ACK | 149   | 0        | Servo Interrupt Acknowledge: Interrupt acknowledge from the controller to the servo                                                          |

| CTRL_INT      | 150   | 0        | Controller Interrupt Output: Interrupt signal from the controller to the servo                                                               |

| CTRL_INT_ACK  | 151   | ı        | Controller Interrupt Acknowledge: Interrupt acknowledge from the servo to the controller                                                     |

| SERVO_FAULT   | 152   | I        | Servo Fault: Indicates that some kind of fault has occurred in the servo or read channel. This is used to gate off any disk write functions. |

#### **Serial Interface**

The Serial Interface connects all slave devices to the controller.

Table 9. Serial Interface I/O Pin List

| Pin Name | Pin # | Pin Type | Pin Description |

|----------|-------|----------|-----------------|

| SCLK     | 186   | 0        | Serial Clock    |

| SDATA    | 184   | I/O      | Serial Data     |

| SDEN1    | 183   | 0        | Serial Enable 1 |

| SDEN2    | 182   | 0        | Serial Enable 2 |

#### **I2S Audio Interface**

The I2S Audio Interface is a serial interface for external audio devices.

Table 10. I2S Audio Interface I/O Pin List

| Pin Name | Pin # | Pin Type | Pin Description |

|----------|-------|----------|-----------------|

| SCK      | 201   | 0        | Serial Clock    |

| WS       | 200   | 0        | Word Select     |

| SD       | 100   | 0        | Serial Data     |

# Sony<sup>®</sup> Philips<sup>®</sup> Digital Audio Interface

The Sony Philips Digital Audio Interface is a standard digital interface for external audio devices.

Table 11. Sony Philips Digital Audio Interface I/O Pin List

| Pin Name  | Pin # | Pin Type | Pin Description                |

|-----------|-------|----------|--------------------------------|

| SPDIF_OUT | 92    | 0        | Sony Philips Digital Interface |

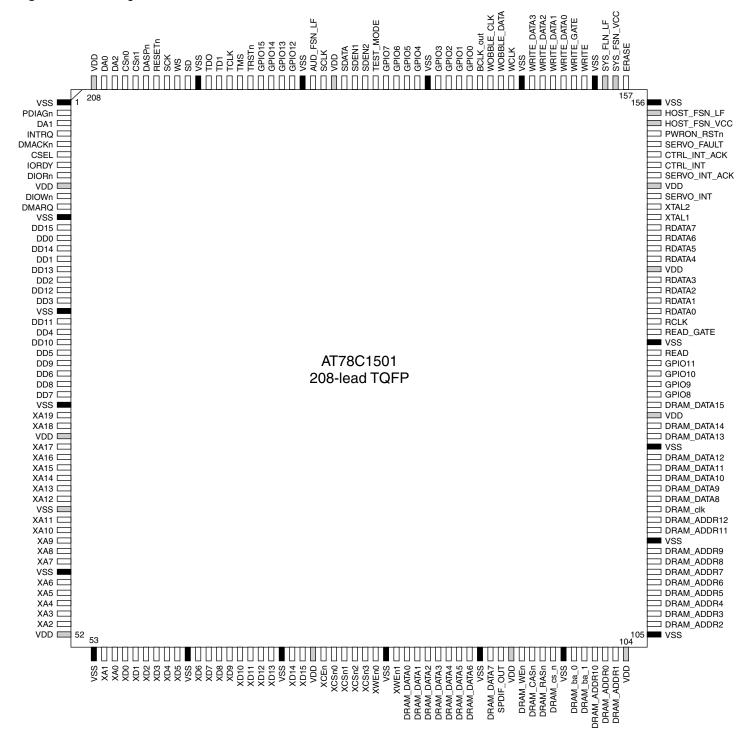

Figure 3. Functional Pinout

Figure 4. AT78C1501 Block Diagram

#### **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 487-2600

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

#### **Atmel Operations**

#### Memory

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 2-40-18-18-18 FAX (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-42-53-60-00 FAX (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland TEL (44) 1355-803-000 FAX (44) 1355-242-743

#### RF/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany TEL (49) 71-31-67-0 FAX (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-76-58-30-00 FAX (33) 4-76-58-34-80

e-mail

literature@atmel.com

Web Site http://www.atmel.com

#### © Atmel Corporation 2002.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

ATMEL<sup>®</sup> and AVR<sup>®</sup> are the registered trademarks of Atmel. ARM<sup>®</sup> is the registered trademark of ARM Limited. ARM7TDMI<sup>™</sup> is the trademark of ARM Limited. Sony<sup>®</sup> is a registered trademerk of Sony Corporation. Philips<sup>®</sup> is a registered trademark of Koninklijke Philips Electronics N.V.

Other terms and product names may be trademarks of others.

#### **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 487-2600

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

#### **Atmel Operations**

#### Memory

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 2-40-18-18-18 FAX (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-42-53-60-00 FAX (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland TEL (44) 1355-803-000 FAX (44) 1355-242-743

#### RF/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany TEL (49) 71-31-67-0 FAX (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-76-58-30-00 FAX (33) 4-76-58-34-80

e-mail literature@atmel.com

Web Site http://www.atmel.com

#### © Atmel Corporation 2002.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.