# MT90528 28-Port Primary Rate Circuit Emulation AAL1 SAR

**Data Sheet**

#### **Features**

- AAL1 Segmentation and Reassembly device compliant with Circuit Emulation Services (CES) standard (af-vtoa-0078.000)

- Supports both Unstructured and Structured Circuit Emulation of 28 independent DS1/E1/ST-BUS interfaces

- Supports AAL1 trunking, with up to 128 TDM channels per VC (af-vtoa-0089.001)

- Supports CAS transmission and reception in all structured modes of operation

- Supports simultaneous processing of up to 896 bidirectional Virtual Circuits

- Supports mixed DS1/E1 operation

- Supports mixed Unstructured and Structured CES operation

- · Fully flexible DS0 assignment

- Complete clock recovery solution provided onchip: Synchronous, Adaptive, or Synchronous Residual Time Stamp (SRTS) via 28 independent PLLs

DS5814 ISSUE 1 September 2002

## Ordering Information

MT90528AG 456 Pin Plastic BGA -40 to +85°C

- Dual-mode (ATM-end or PHY-end) UTOPIA port operates in Level 1 or Level 2 mode for connection to external PHY or ATM devices with UTOPIA clock rate up to 52 MHz

- TDM bus provides 28 bidirectional serial streams at 1.544, 2.048, or 4.096 MHz - compatible with Generic (1.544 Mbps or 2.048 Mbps) and ST-BUS (2.048 Mbps) interfaces

- Supports master and slave TDM backplane bus clock operation

- Supports TDM and UTOPIA loopback functions

- 16-bit microprocessor port, configurable to Motorola or Intel timing

- Master clock rate of 66.0 MHz

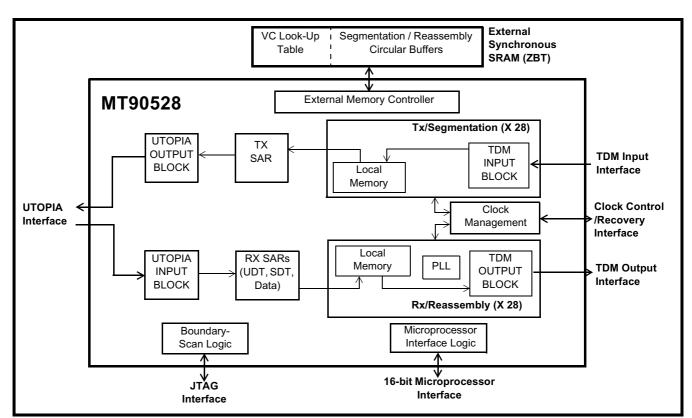

Figure A - MT90528 Block Diagram

#### **Applications**

- B-ISDN (Broadband ISDN) systems requiring flexible N x 64kbps transport

- Systems requiring af-vtoa-0078.000 (ATM Forum CES v2.0) "DS1 or E1 Nx64 Basic Service", "DS1 or E1 Nx64 Service with CAS", or "DS1 or E1 Unstructured Service" - flexible CES allows one-board solution to support multiple CES modes

- Systems requiring af-vtoa-0089.001 (ATM Forum ATM Trunking Using AAL1 for Narrowband Services) transport of up to 128 channels per VC

- · Ideal for carrier-class WAN access products, especially channelized DS3 or E3 interfaces

- · ATM Edge Switches

- Carrier Class Voice over ATM systems

- ATM Public Network access for PBX or CO

- · TDM traffic transfer over an asynchronous cell bus

#### **Description**

The MT90528 28-Port Primary Rate Circuit Emulation AAL1 SAR allows primary rate TDM circuits to be carried over ATM networks using Circuit Emulation Services. Up to 896 bidirectional ATM VC connections can be simultaneously processed by the MT90528 CES AAL1 SAR device.

The MT90528 supports several modes of Circuit Emulation Services for DS1 and E1 rates. These include Unstructured CES and Structured CES with and without Channel Associated Signalling (CAS).

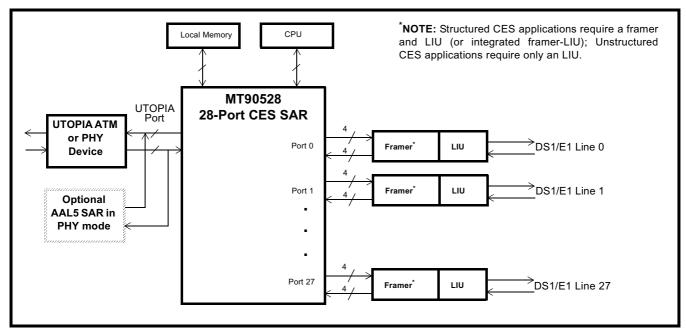

On the TDM bus side, the MT90528 interfaces with 28 primary rate TDM ports operating at 1.544 Mbps or 2.048 Mbps. The configurable TDM ports interface directly with DS1 or E1 framers for Nx64 Structured operation, or with DS1 or E1 LIUs in Unstructured mode.

On the ATM interface side, the MT90528 device meets the ATM Forum standard for UTOPIA Bus Level 2. The MT90528 is capable of operating as a UTOPIA "master" (ATM-end), "slave" (PHY-end), or "multi-PHY slave" (PHY-end). The UTOPIA port can operate in 8-bit or 16-bit mode, with a clock rate up to 52 MHz.

Each of the twenty-eight ports of the device contains a PLL, allowing independent timing of each TDM port. Each PLL supports four modes of clock recovery: SRTS, Adaptive, Synchronous (from the Physical layer), or from the TDM line clock. Although a complete clock recovery solution is provided internally, an optional external PLL or external clock source is also supported.

Figure B - MT90528 Device Application Block Diagram

# **Table of Contents**

|        | of Contents                                 |      |

|--------|---------------------------------------------|------|

| List o | f Figures                                   | 6    |

| List o | f Tables                                    | 8    |

| 1. Int | roduction                                   | .11  |

|        | 1 Functional Overview                       |      |

| 2. Fe  | atures                                      | . 13 |

|        | 1 Key Functionality                         |      |

|        | 2 Microprocessor Interface                  |      |

|        | 3 External Memory Interface                 |      |

| 2.     | 4 TDM Interface                             | .13  |

|        | 5 UTOPIA Interface                          |      |

|        | 6 Segmentation and Reassembly Modules       |      |

|        | 7 Clock Management                          |      |

|        | 8 Testing Modes                             |      |

|        | 9 Miscellaneous                             |      |

| 2.     | 10 Interrupts                               |      |

|        | 2.10.1 Module Level Service Requests        |      |

|        | 2.10.1.2 TDM Module                         |      |

|        | 2.10.1.3 UTOPIA Module                      |      |

|        | 2.10.1.4 TX SAR Module                      |      |

|        | 2.10.1.5 UDT RX_SAR Module                  |      |

|        | 2.10.1.6 SDT RX_SAR Module                  |      |

|        | 2.10.1.7 Data RX_SAR Module                 |      |

|        | 2.10.1.8 UDT Reassembly-Side Timeout Module |      |

| 2.     | .11 Statistics                              | .17  |

|        | 2.11.1 TDM Module                           |      |

|        | 2.11.2 UTOPIA Module                        |      |

|        | 2.11.3 TX_SAR Module                        |      |

|        | 2.11.4 UDT RX_SAR Module                    |      |

|        | 2.11.5 SDT RX_SAR Module                    |      |

|        | n Descriptions                              |      |

|        | 1 Functional Pin Descriptions               |      |

| 3.     | 2 Physical Pin Description                  |      |

|        | 3.2.1 Pin Description by Ball Pin Number    |      |

|        | 3.2.3 Package Specifications                |      |

| 4 14-  | · ·                                         |      |

|        | odule Functional Descriptions               |      |

| 4.     | 4.1.1 Global Reset                          |      |

|        | 4.1.2 CPU Interrupts                        |      |

| 4.     | 2 External Memory Interface                 |      |

|        | 3 TDM Interface Module                      |      |

|        | 4.3.1 Overview                              |      |

|        | 4.3.1.1 Segmentation Direction              | .41  |

|        | 4.3.1.2 Reassembly Direction                |      |

|        | 4.3.2 Functional Description                |      |

|        | 4.3.2.1 Segmentation Process                |      |

|        | 4.3.2.1.1 UDT Mode                          |      |

|        | 4.3.2.1.2 SDT Mode                          |      |

|        | 4.3.2.2 Reassembly Process                  |      |

|        | 4.3.2.2.1 UDT format                        |      |

|        | 4.J.Z.Z.Z JUT IUIIIIdt                      | .43  |

| 4.3.2.3 TDM Loopback                                                  |      |

|-----------------------------------------------------------------------|------|

| 4.3.2.3.1 TDM Low-Latency Loopback                                    | . 46 |

| 4.3.2.3.2 TDM Circular Buffer Loopback (SDT Mode)                     | . 46 |

| 4.4 UTOPIA Interface Module                                           | . 47 |

| 4.4.1 Functional Description                                          | . 48 |

| 4.4.1.1 Segmentation Direction                                        | . 48 |

| 4.4.1.1.1 TX UTOPIA Interface                                         | . 48 |

| 4.4.1.1.2 TX UTOPIA FIFO                                              | . 49 |

| 4.4.1.1.3 TX Parity                                                   | . 49 |

| 4.4.1.2 Reassembly Direction                                          | . 49 |

| 4.4.1.2.1 RX UTOPIA Interface                                         | . 49 |

| 4.4.1.2.2 OAM & VPI/VCI Filter                                        | . 49 |

| 4.4.1.2.3 RX UTOPIA FIFO                                              | . 51 |

| 4.4.1.2.4 UDT VCI/VPI Comparison and Look-up Table                    | . 51 |

| 4.4.1.2.5 RX Parity                                                   |      |

| 4.5 TX_SAR Module                                                     | . 55 |

| 4.5.1 ATM Overview                                                    | . 55 |

| 4.5.2 UDT Mode of Operation                                           | . 55 |

| 4.5.2.1 Control Structure Configuration                               | . 56 |

| 4.5.2.2 Operation                                                     | . 56 |

| 4.5.3 SDT Mode of Operation                                           | . 57 |

| 4.5.3.1 Control Structure Configuration                               | . 57 |

| 4.5.3.1.1 SDT Segmentation Control Structures                         | . 57 |

| 4.5.3.1.2 SDT Segmentation Pointer Tables                             | . 59 |

| 4.5.3.2 Operation                                                     | . 60 |

| 4.5.4 Data TX_SAR Module                                              | . 62 |

| 4.5.4.1 Mode of Operation                                             | . 62 |

| 4.5.4.2 Error Handling                                                | . 62 |

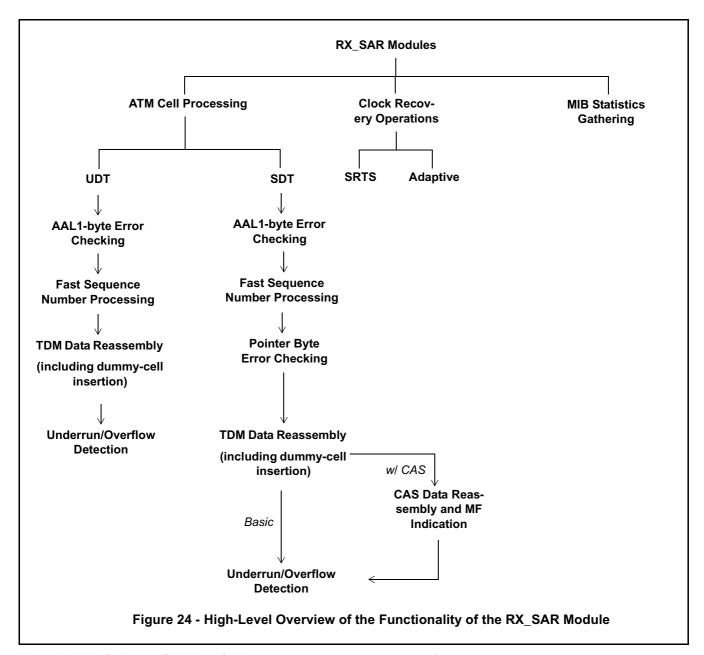

| 4.6 RX_SAR Modules                                                    | . 63 |

| 4.6.1 UDT RX_SAR and SDT RX_SAR Modules                               |      |

| 4.6.1.1 Data Flow and Processing Path Overview                        |      |

| 4.6.1.2 Reassembly Control Structures                                 |      |

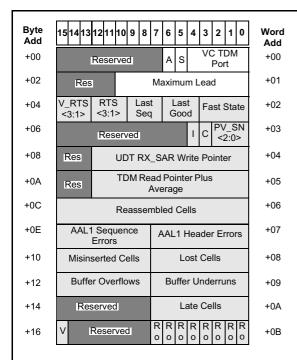

| 4.6.1.2.1 UDT Reassembly Control Structures                           |      |

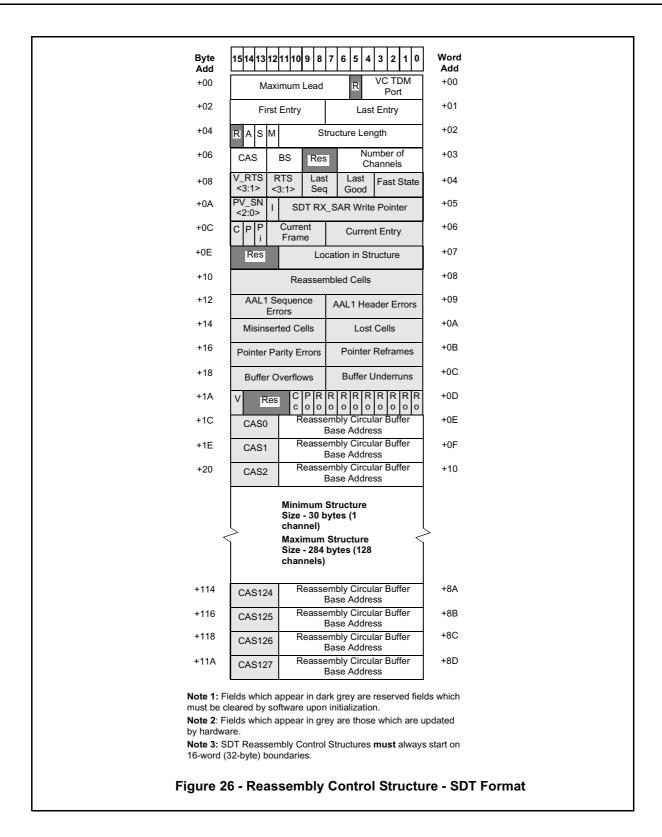

| 4.6.1.2.2 SDT Reassembly Control Structures                           |      |

| 4.6.1.3 Sequence Number Checking (Correction/Detection State Machine) |      |

| 4.6.1.4 Sequence Number Checking (Fast SN Processing State Machine)   |      |

| 4.6.1.5 Received Cell Processing                                      |      |

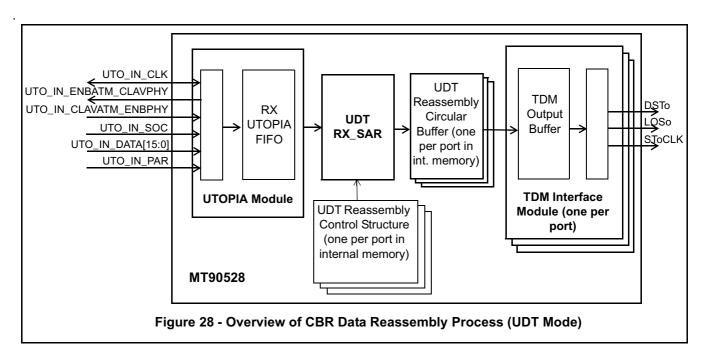

| 4.6.1.5.1 UDT Mode of Operation                                       | . 75 |

| 4.6.1.5.2 SDT Mode of Operation                                       |      |

| 4.6.1.5.3 Complete Reassembly Data Flow Overview                      |      |

| 4.6.1.6 Clock Recovery Operations                                     |      |

| 4.6.1.6.1 Digital Phaseword Generation for Adaptive Clock Recovery    |      |

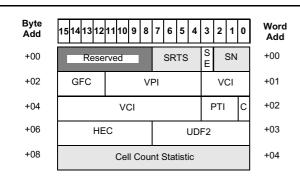

| 4.6.1.6.2 RTS Reception for SRTS Clock Recovery                       |      |

| 4.6.2 Timeout Circuitry                                               |      |

| 4.6.2.1 Cut VC Monitoring                                             |      |

| 4.6.2.2 Late Cell Insertion                                           |      |

| 4.6.2.3 Underrun Detection                                            |      |

| 4.6.3 Data RX_SAR Module                                              |      |

| 4.6.3.1 Mode of Operation                                             |      |

| 4.6.3.2 Error Handling                                                |      |

| 4.7 Clock Management Module                                           |      |

| 4.7.1 Overview                                                        |      |

| 4.7.1.1 Clock Control                                                 |      |

| 4.7.1.2 Clock Recovery                                                |      |

| 4.7.2 Functional Description                                          |      |

| 4.7.2.1 Interface to TDM Sub-Module                                   |      |

| 477 L LODERADOR OF SULFULL INTERACE                                   | . 91 |

# Data Sheet

|    | 4.7.2.1.2 Operation in TDM Backplane Mode             |       |

|----|-------------------------------------------------------|-------|

|    | 4.7.2.1.3 Common Clock Source Generation              |       |

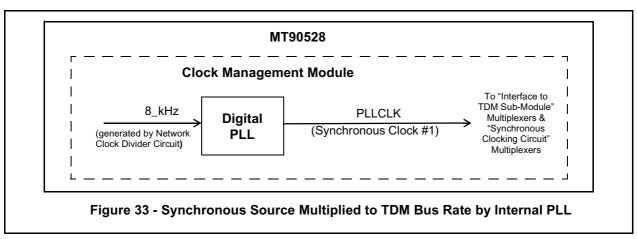

|    | 4.7.2.2.1 Synchronous Clock #1 (Internal Digital PLL) | 94    |

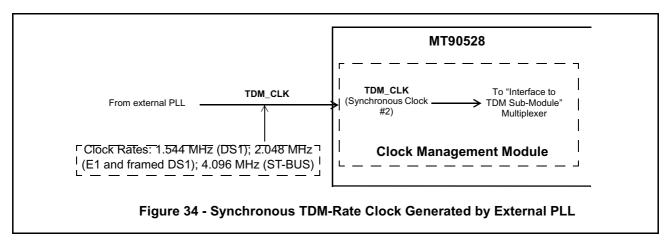

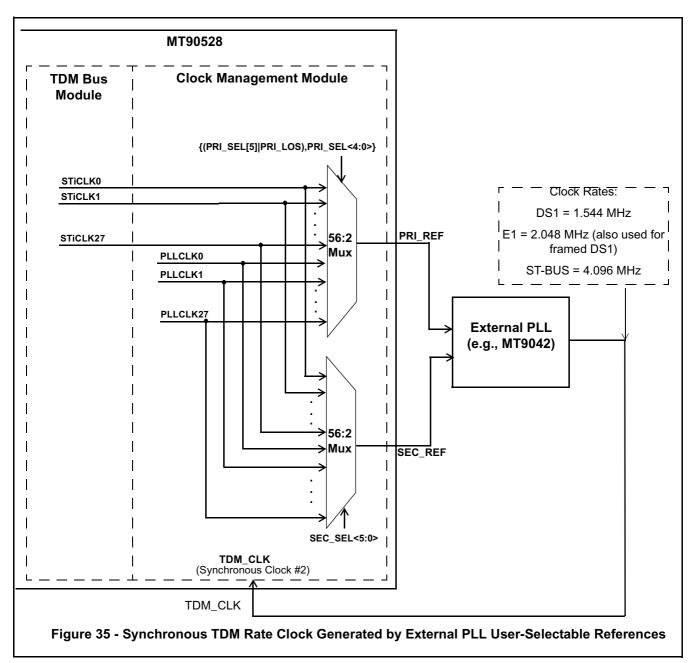

|    | 4.7.2.2.2 Synchronous Clock #2 (External PLL)         |       |

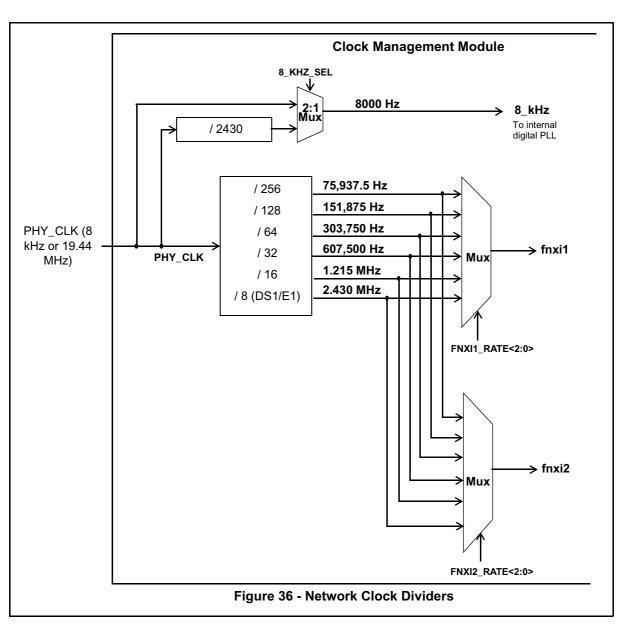

|    | 4.7.2.3 Network Clock Divider Circuit                 |       |

|    | 4.7.2.4.1 UDT Operation                               |       |

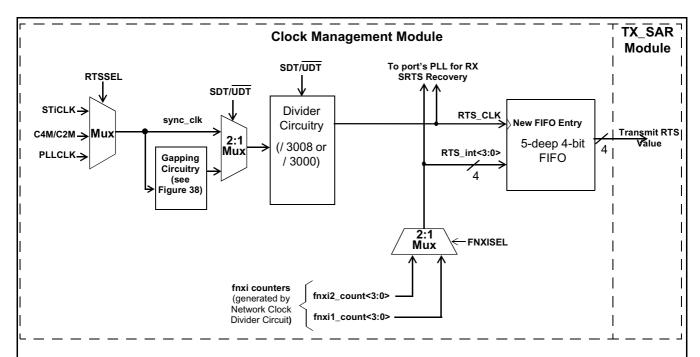

|    | 4.7.2.4.2 SDT Operation                               | 98    |

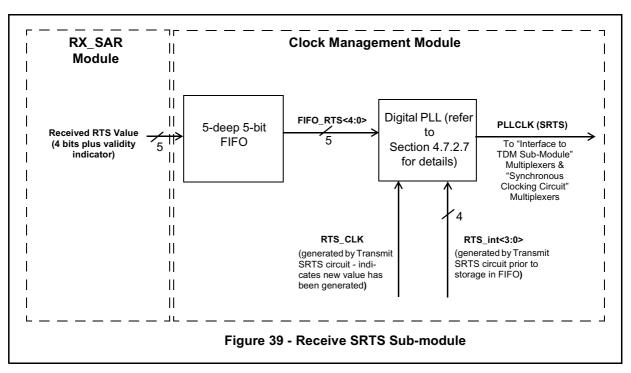

|    | 4.7.2.5 Receive SRTS Circuit Sub-Module               |       |

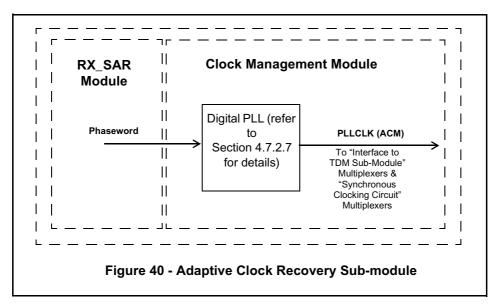

|    | 4.7.2.6 Adaptive Clock Recovery Circuit               |       |

|    | 4.7.2.7.1 Architecture                                |       |

|    | 4.7.2.7.2 Modes of Operation (PLL_INPUT_SEL bits)     |       |

|    | 4.7.2.7.3 Sub-modes of Operation (PLL_MODE_SEL bits)  |       |

|    | 4.7.2.7.4 Locking Range                               |       |

|    | 4.8.1 Test Access Port                                |       |

|    | 4.8.2 JTAG ID                                         |       |

|    | 4.8.3 Boundary Scan Instructions                      |       |

| _  | 4.8.4 BSDL                                            |       |

| 5. | Memory     5.1 Internal Memory Map                    |       |

|    | 5.2 External Memory                                   |       |

| 6. | Registers                                             | . 113 |

|    | 6.1 Register Overview                                 |       |

|    | 6.2 Register Description                              |       |

|    | 6.2.1 Microprocessor Interface Module                 |       |

|    | 6.2.3 UDT RX_SAR Module                               |       |

|    | 6.2.4 Data RX_SAR Module                              | . 134 |

|    | 6.2.5 SDT RX_SAR Module                               |       |

|    | 6.2.6 Reassembly-Side Timeout Module                  |       |

|    | 6.2.8 Clock Management Module.                        |       |

|    | 6.2.9 TDM Interface Module                            | . 150 |

|    | 6.2.10 External Memory Interface Module               | . 155 |

| 7. | Electrical Specification                              |       |

|    | 7.1 DC Characteristics                                |       |

|    | 7.2.1 CPU Interface                                   |       |

|    | 7.2.2 External Memory Interface                       |       |

|    | 7.2.3 TDM Interface                                   |       |

|    | 7.2.4 UTOPIA Interface                                |       |

|    | 7.2.4.2 UTOPIA Level 2                                |       |

| 8. | Applications                                          |       |

|    | 8.1 Board-Level Applications                          |       |

|    | 8.1.1 Power-Up and Power-Down Sequence                |       |

|    | 8.1.2 External Memory Interface Connections           |       |

|    | 8.1.3 UTOPIA Interface Connections                    |       |

| Re | ference Documents                                     |       |

|    | ossary                                                |       |

|    | <del>-</del>                                          |       |

# **List of Figures**

| Figure 1 -  | MT90528 Block Diagram                                                           | 12  |

|-------------|---------------------------------------------------------------------------------|-----|

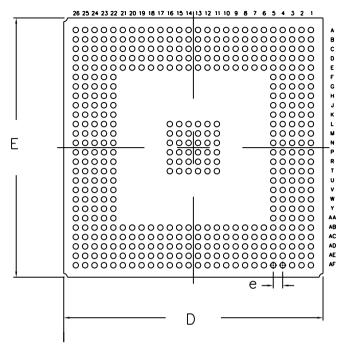

| Figure 2 -  | PCB Pad Diagram for 35mm x 35mm PBGA (JEDEC MO-151)                             | 32  |

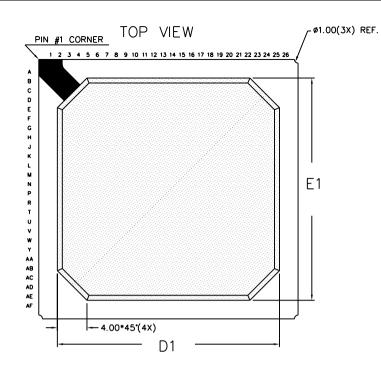

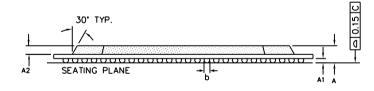

| Figure 3 -  | Aerial View of Package Specifications                                           | 33  |

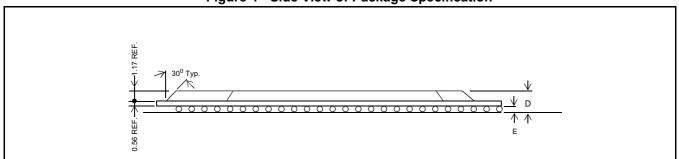

| Figure 4 -  | Side View of Package Specification                                              | 34  |

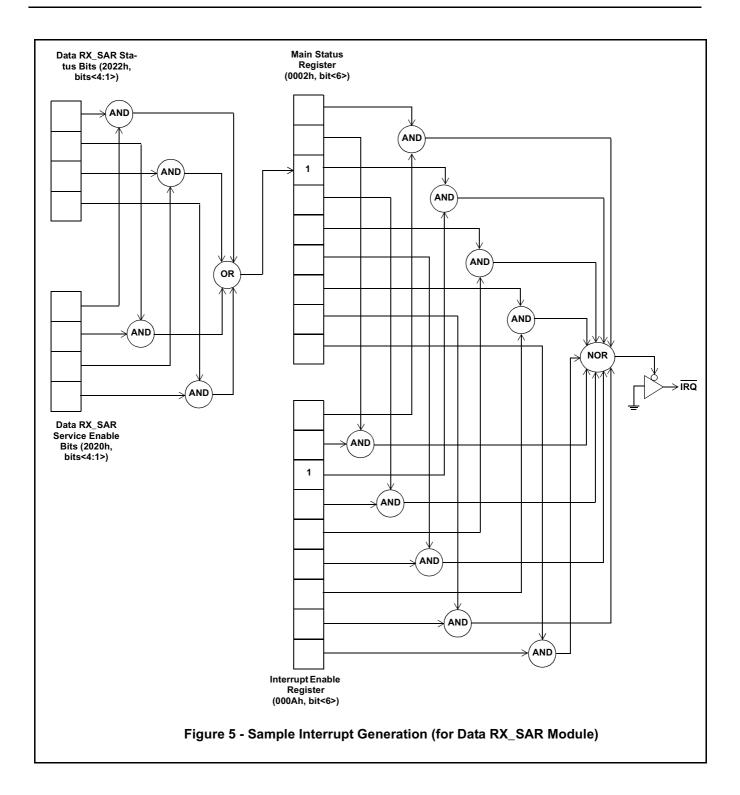

| Figure 5 -  | Sample Interrupt Generation (for Data RX_SAR Module)                            | 37  |

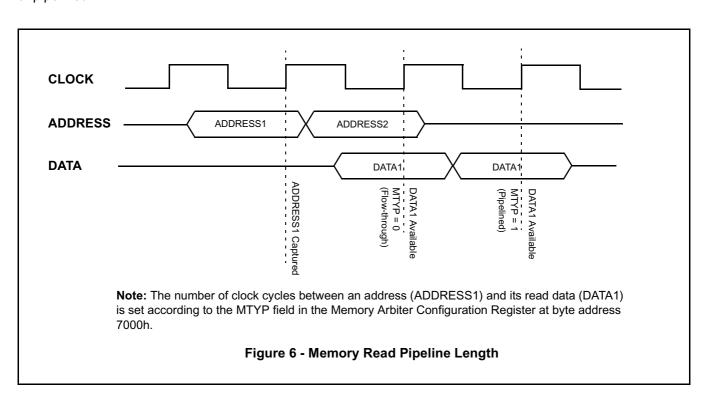

| Figure 6 -  | Memory Read Pipeline Length                                                     | 38  |

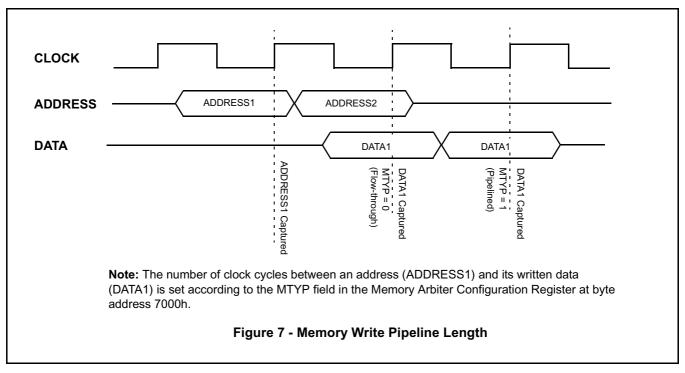

| Figure 7 -  | Memory Write Pipeline Length                                                    |     |

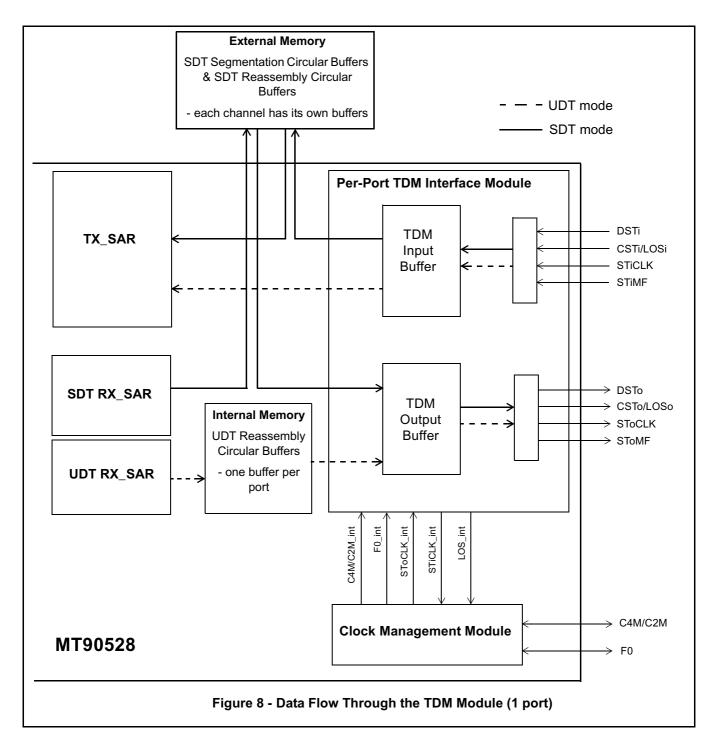

| Figure 8 -  | Data Flow Through the TDM Module (1 port)                                       | 40  |

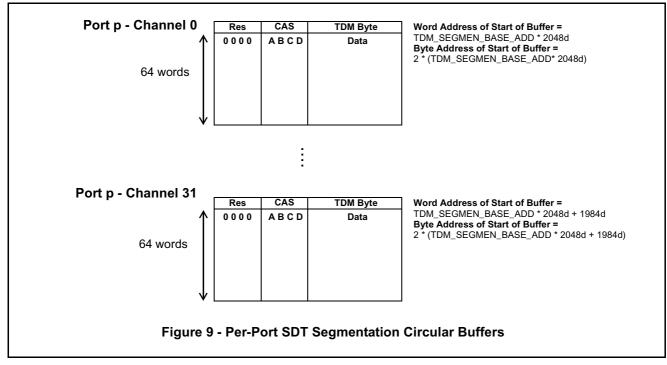

| Figure 9 -  | Per-Port SDT Segmentation Circular Buffers                                      | 42  |

| Figure 10 - | Per-Channel SDT Reassembly Circular Buffer                                      | 44  |

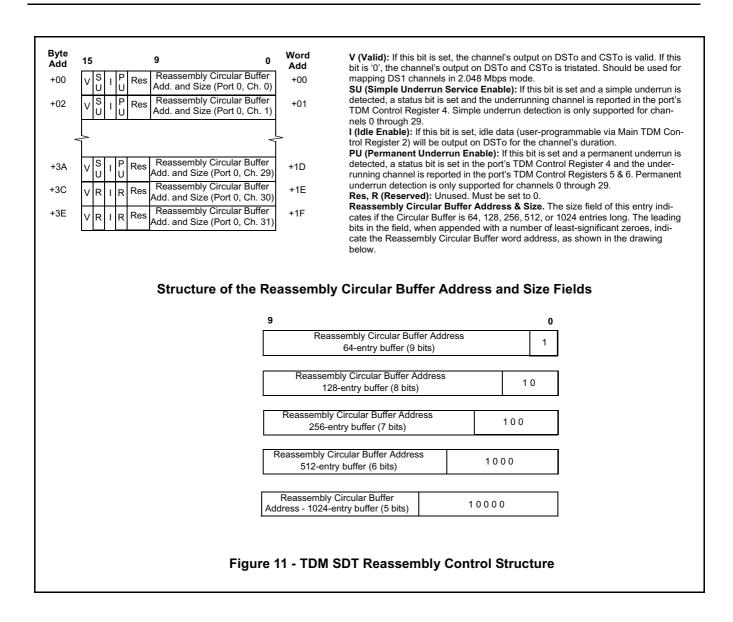

| Figure 11 - | TDM SDT Reassembly Control Structure                                            | 45  |

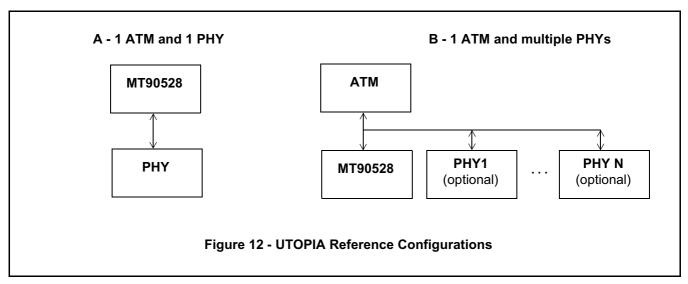

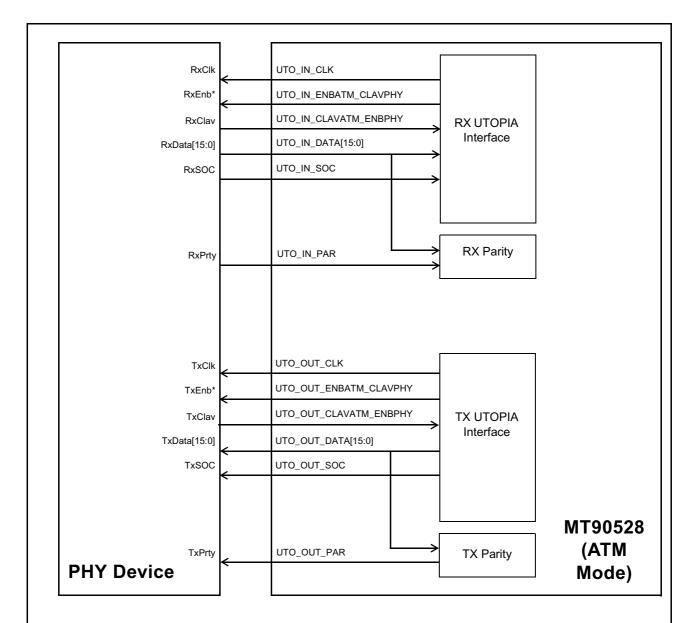

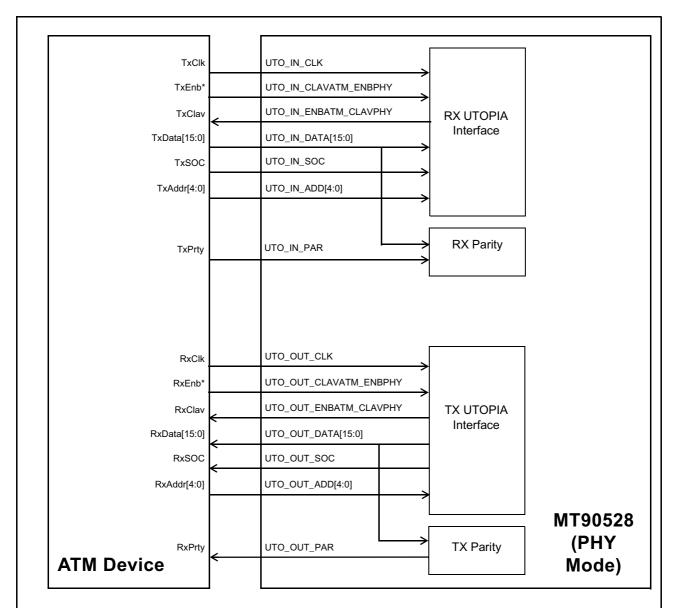

| Figure 12 - | UTOPIA Reference Configurations                                                 | 47  |

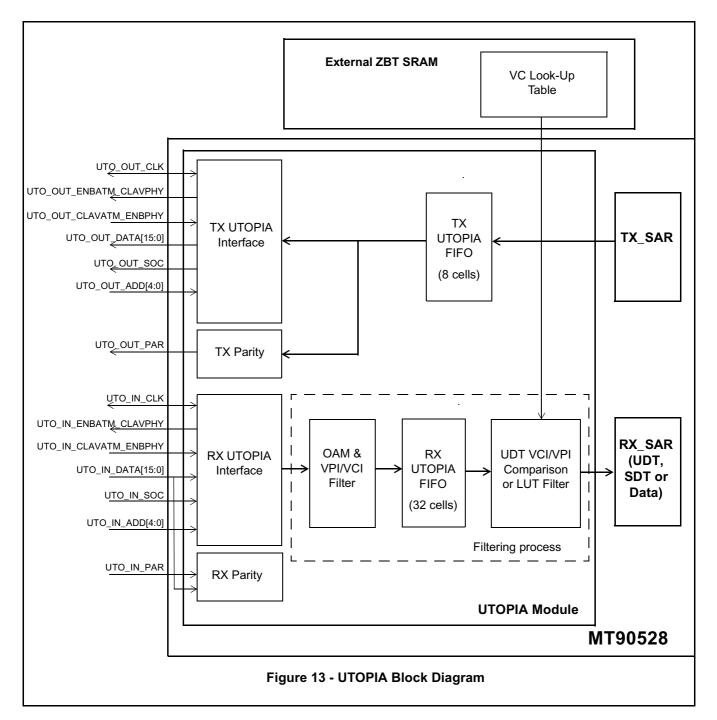

| Figure 13 - | UTOPIA Block Diagram                                                            | 48  |

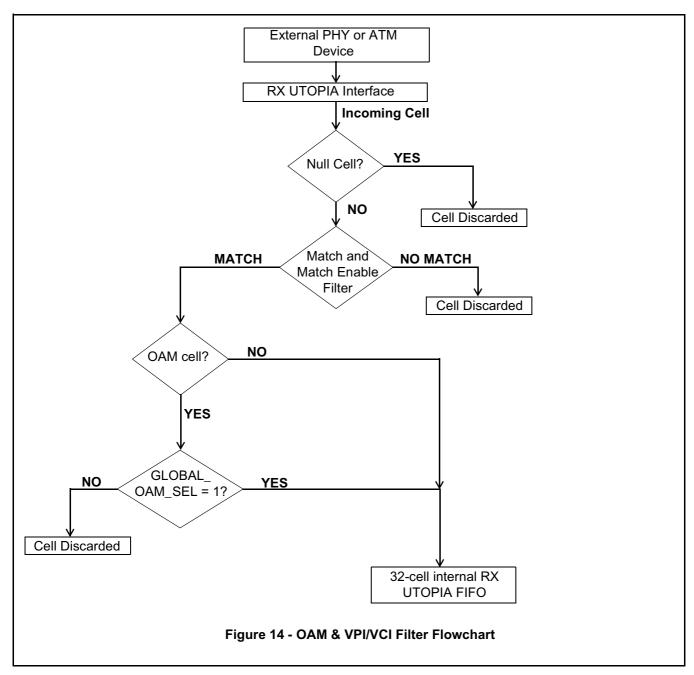

| Figure 14 - | OAM & VPI/VCI Filter Flowchart                                                  | 50  |

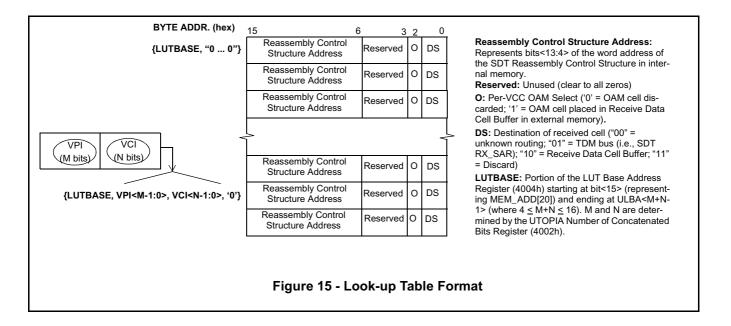

| Figure 15 - | Look-up Table Format                                                            | 52  |

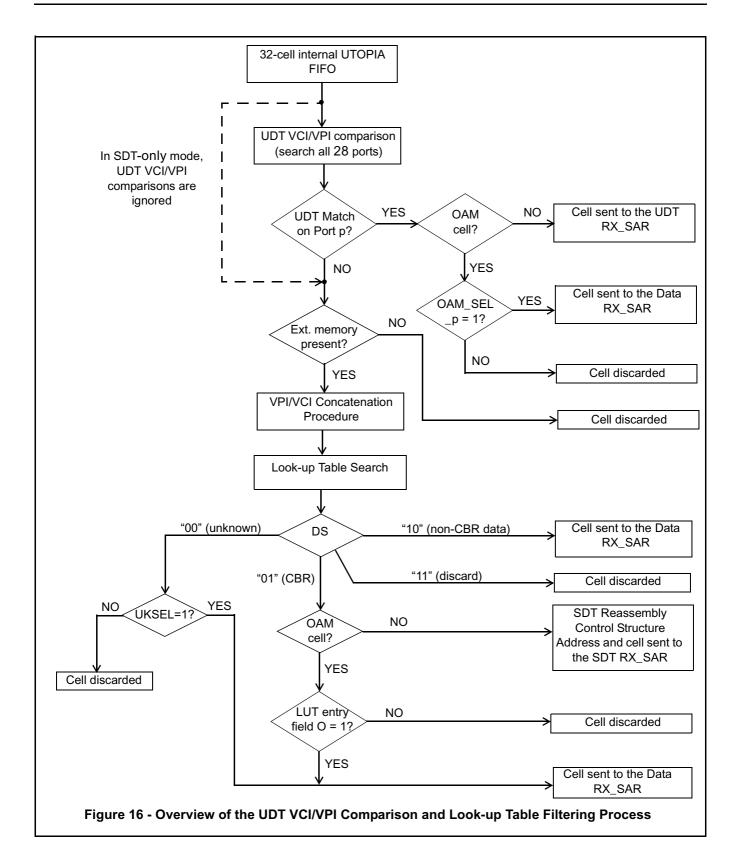

| Figure 16 - | Overview of the UDT VCI/VPI Comparison and Look-up Table Filtering Process      | 54  |

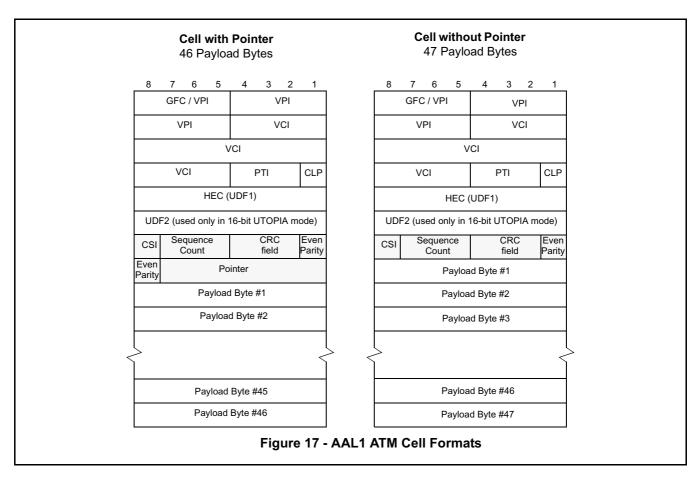

| Figure 17 - | AAL1 ATM Cell Formats                                                           | 55  |

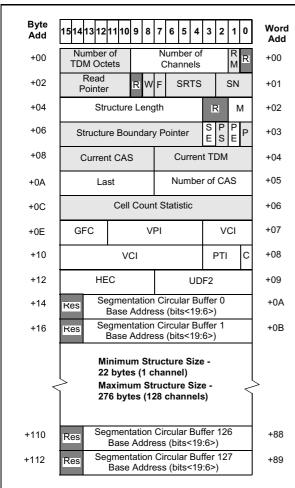

| Figure 18 - | Segmentation Control Structure - UDT Format                                     |     |

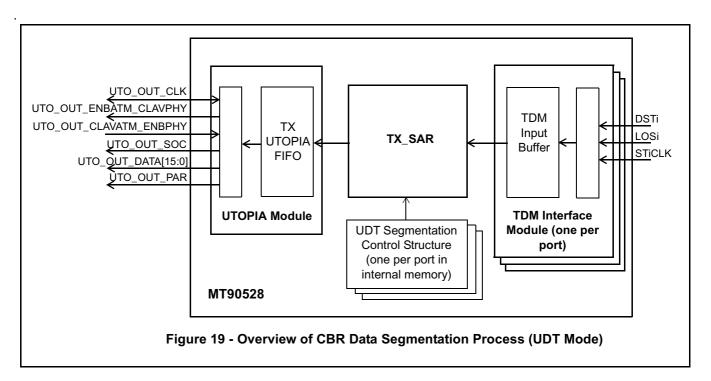

| Figure 19 - | Overview of CBR Data Segmentation Process (UDT Mode)                            | 57  |

| Figure 20 - | Segmentation Control Structure - SDT Format                                     | 58  |

| Figure 21 - | SDT Segmentation Pointer Table for Port p                                       | 60  |

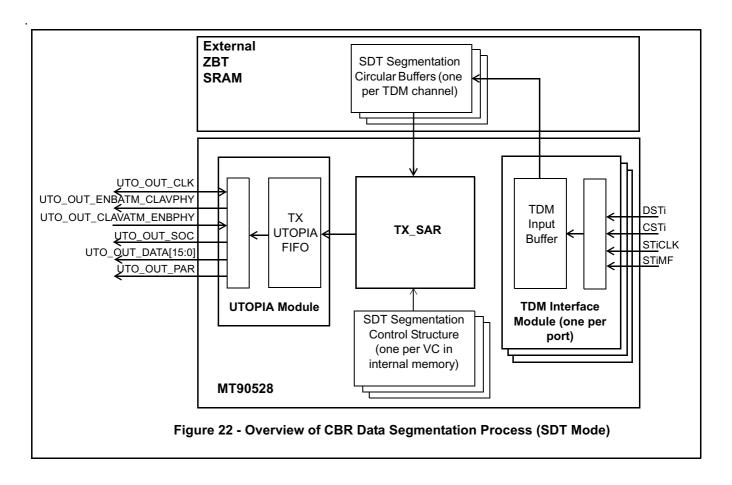

| Figure 22 - | Overview of CBR Data Segmentation Process (SDT Mode)                            | 61  |

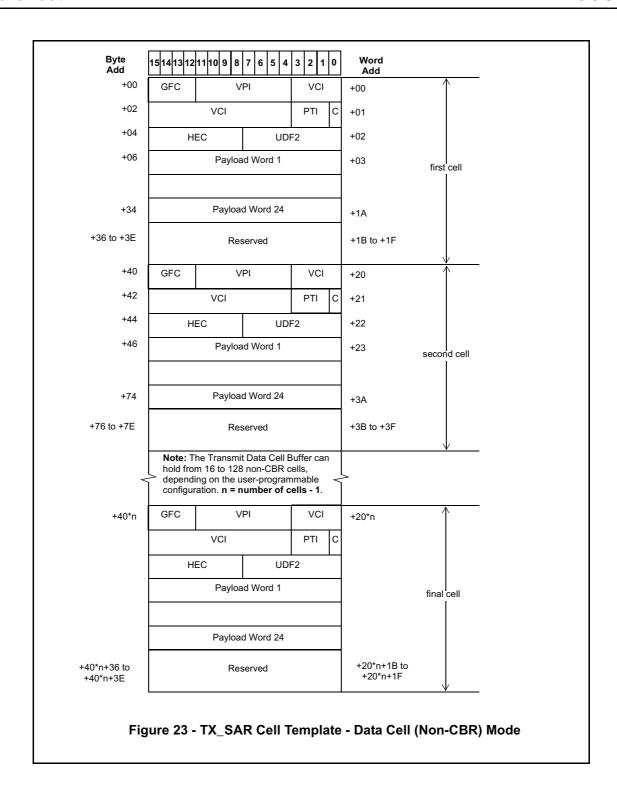

| Figure 23 - | TX_SAR Cell Template - Data Cell (Non-CBR) Mode                                 |     |

| Figure 24 - | High-Level Overview of the Functionality of the RX_SAR Module                   | 64  |

| Figure 25 - | Reassembly Control Structure - UDT Format                                       | 66  |

| Figure 26 - | Reassembly Control Structure - SDT Format                                       | 68  |

| Figure 27 - | Per-Channel SDT Reassembly Circular Buffer                                      | 80  |

| Figure 28 - | Overview of CBR Data Reassembly Process (UDT Mode)                              | 83  |

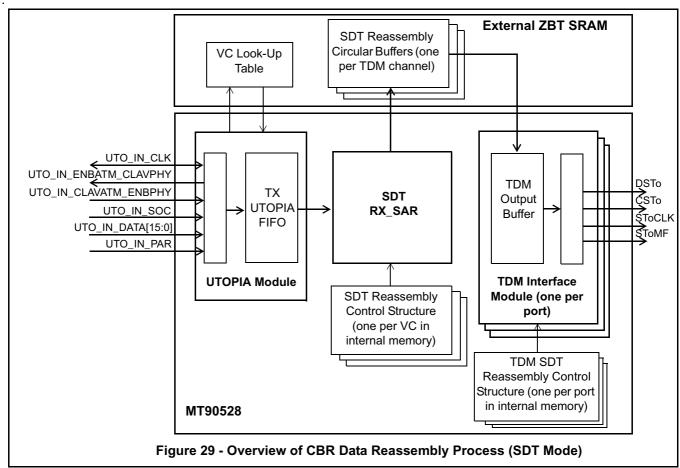

| Figure 29 - | Overview of CBR Data Reassembly Process (SDT Mode)                              | 83  |

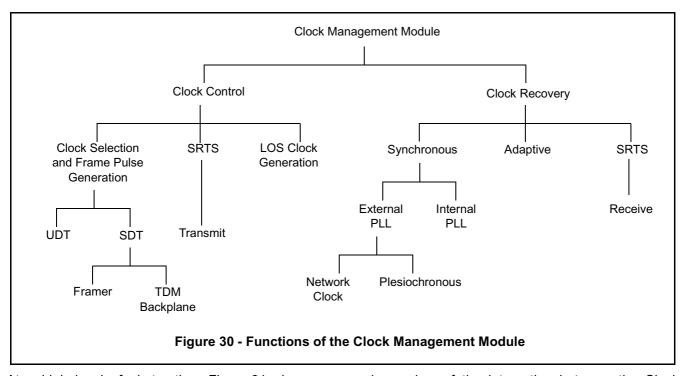

| Figure 30 - | Functions of the Clock Management Module                                        |     |

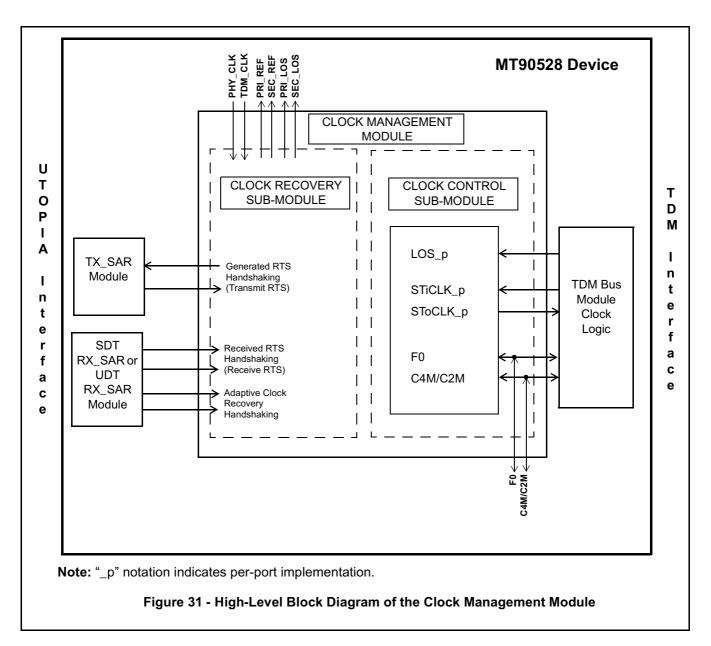

| Figure 31 - | High-Level Block Diagram of the Clock Management Module                         |     |

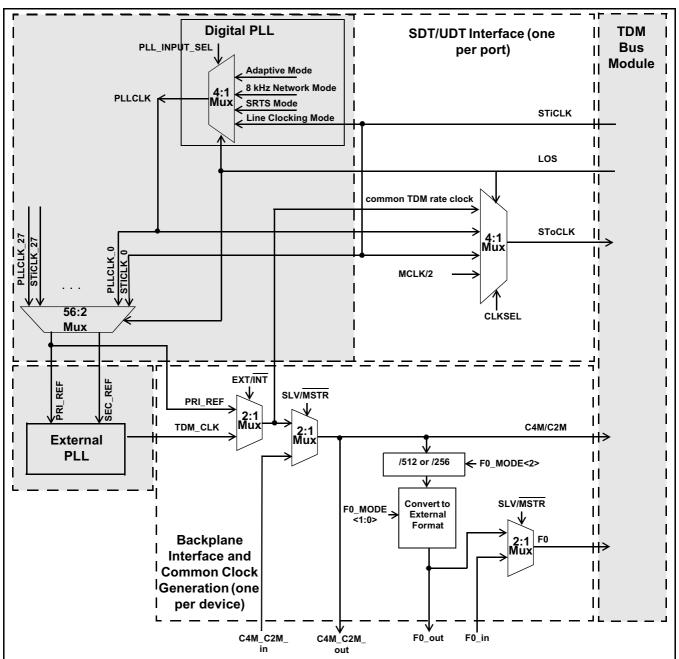

| Figure 32 - | Interface to TDM Bus Module and Common Clock Generation Circuitry               |     |

| Figure 33 - | Synchronous Source Multiplied to TDM Bus Rate by Internal PLL                   |     |

| Figure 34 - | Synchronous TDM-Rate Clock Generated by External PLL                            |     |

| Figure 35 - | Synchronous TDM Rate Clock Generated by External PLL User-Selectable References |     |

| Figure 36 - | Network Clock Dividers                                                          |     |

| Figure 37 - | Transmit SRTS Sub-module                                                        |     |

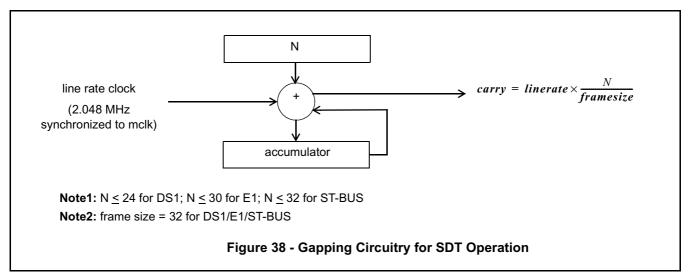

| Figure 38 - | Gapping Circuitry for SDT Operation                                             |     |

| Figure 39 - | Receive SRTS Sub-module                                                         |     |

| Figure 40 - | Adaptive Clock Recovery Sub-module                                              |     |

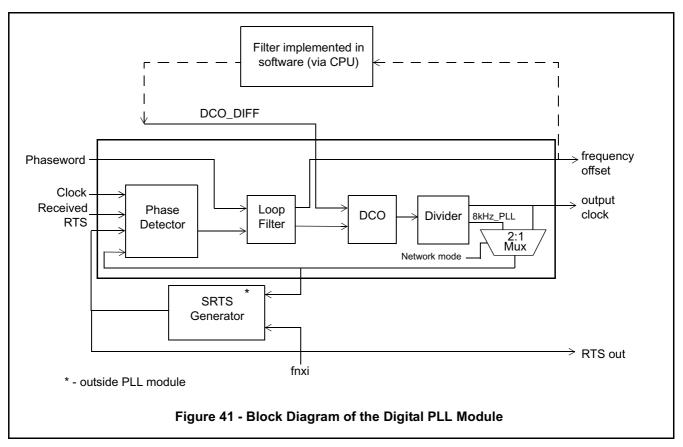

| Figure 41 - | Block Diagram of the Digital PLL Module                                         |     |

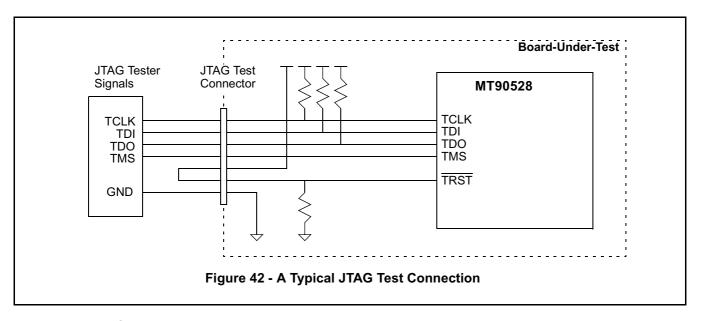

| Figure 42 - | A Typical JTAG Test Connection                                                  |     |

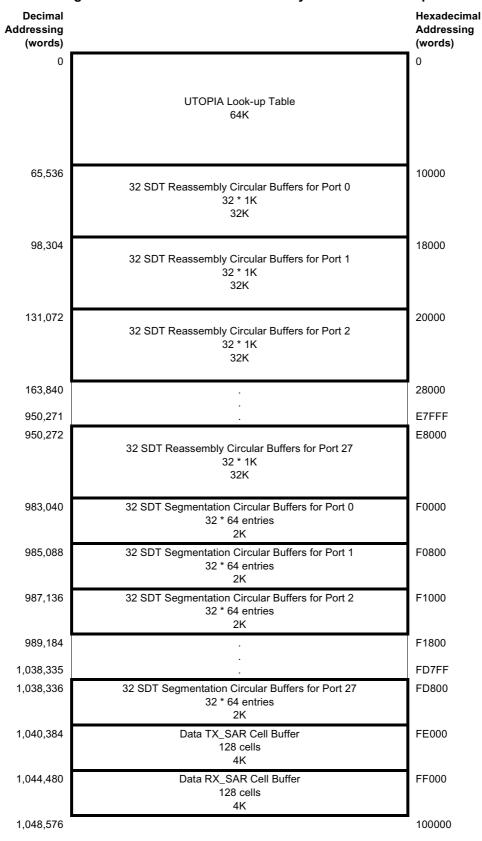

| Figure 43 - | Maximum External Memory Allocation - Example                                    |     |

| Figure 44 - | Minimum External Memory Allocation - Example                                    |     |

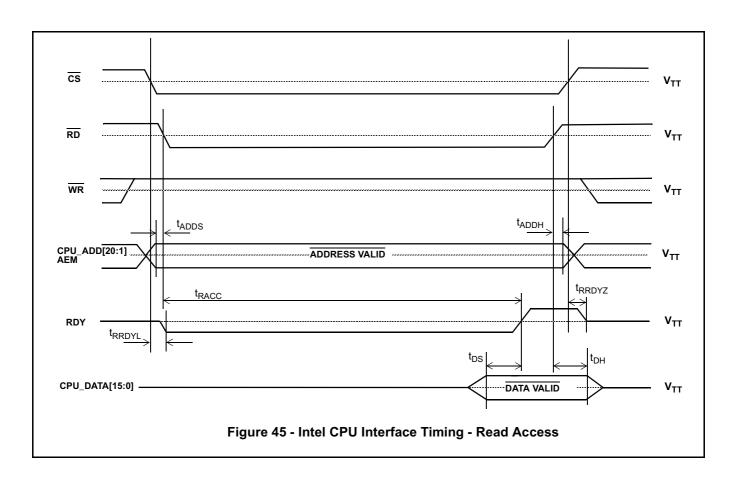

| Figure 45 - | Intel CPU Interface Timing - Read Access                                        |     |

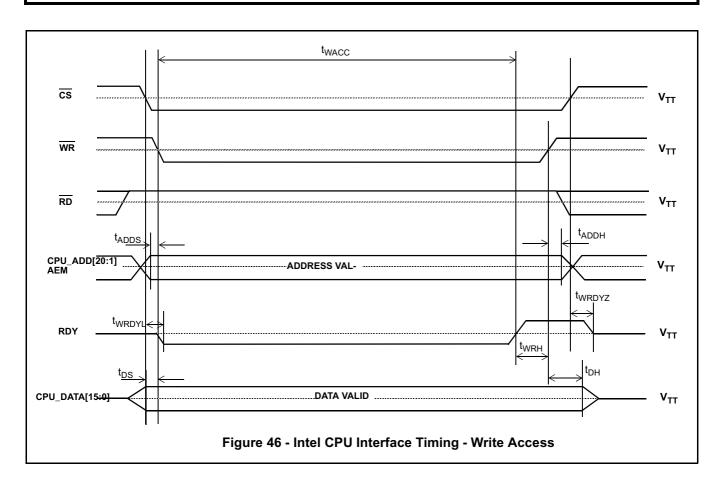

| Figure 46 - | Intel CPU Interface Timing - Write Access                                       |     |

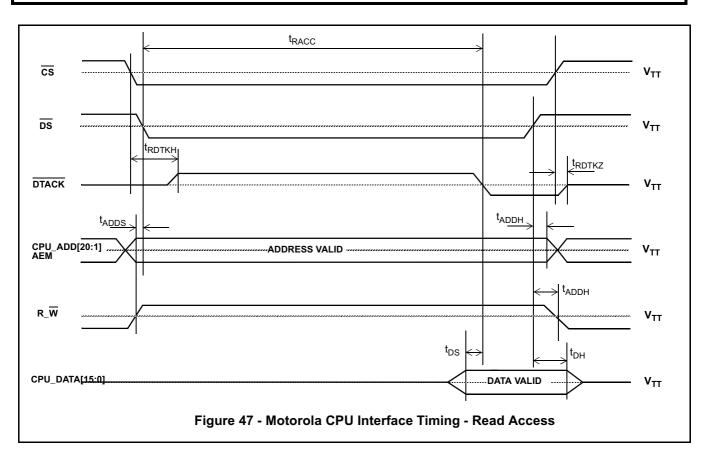

| Figure 47 - | Motorola CPU Interface Timing - Read Access                                     |     |

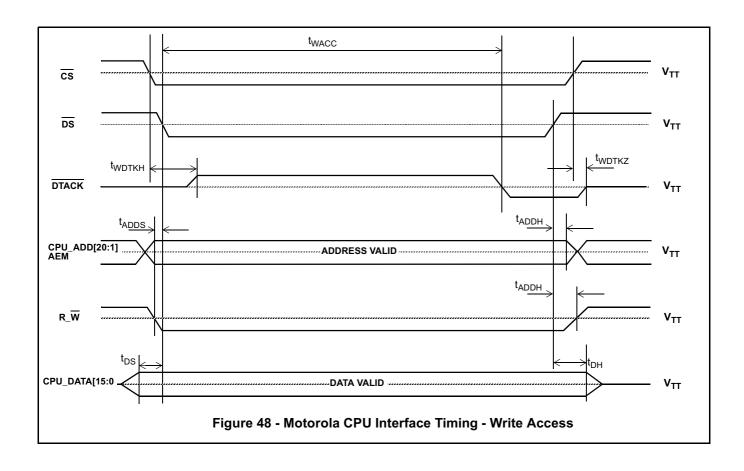

| Figure 48 - | Motorola CPU Interface Timing - Write Access                                    |     |

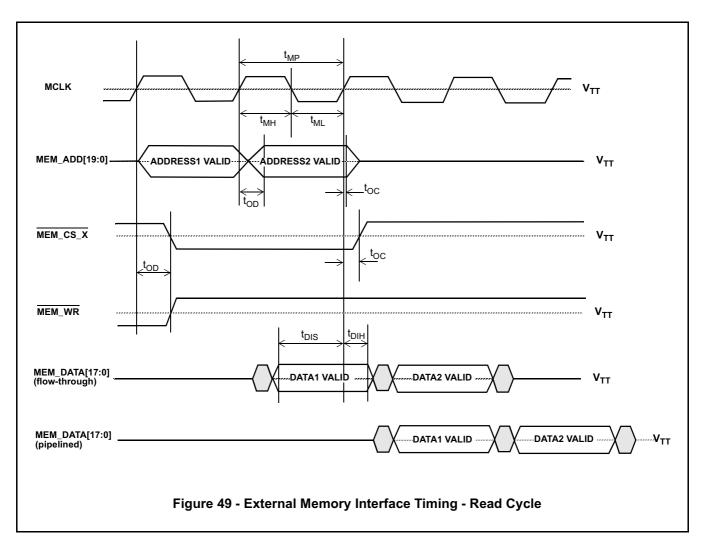

| Figure 49 - | External Memory Interface Timing - Read Cycle                                   |     |

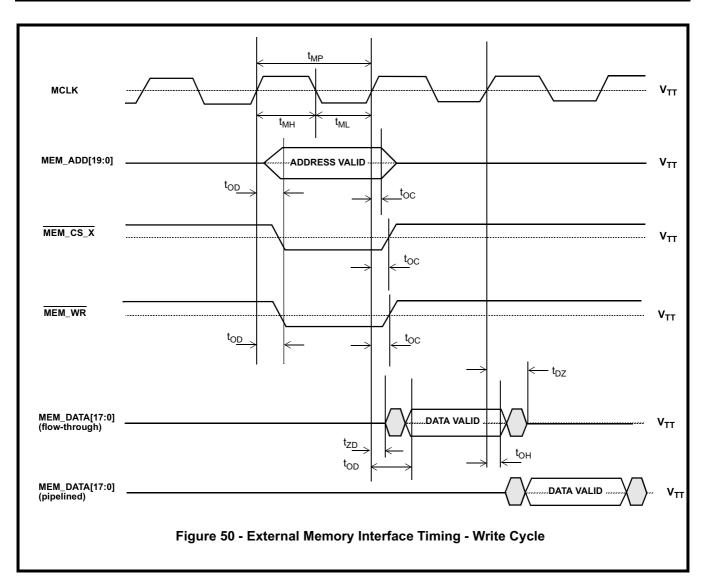

| Figure 50 - | External Memory Interface Timing - Write Cycle                                  | 164 |

# **Data Sheet**

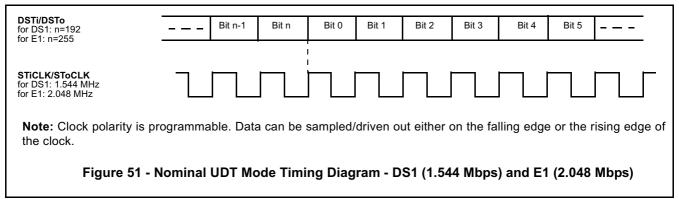

| Figure 51 - | Nominal UDT Mode Timing Diagram - DS1 (1.544 Mbps) and E1 (2.048 Mbps)      | 165 |

|-------------|-----------------------------------------------------------------------------|-----|

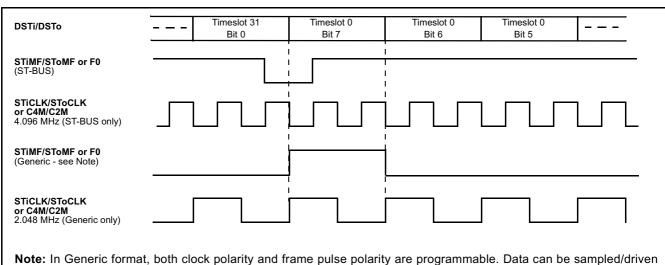

| Figure 52 - | Nominal SDT Mode Timing Diagram - Generic and ST-BUS DS1 or E1 (2.048 Mbps) | 165 |

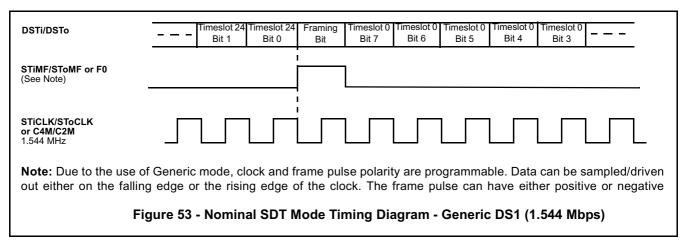

| Figure 53 - | Nominal SDT Mode Timing Diagram - Generic DS1 (1.544 Mbps)                  | 165 |

| Figure 54 - | TDM Bus Inputs - Generic Bus Sampling                                       | 166 |

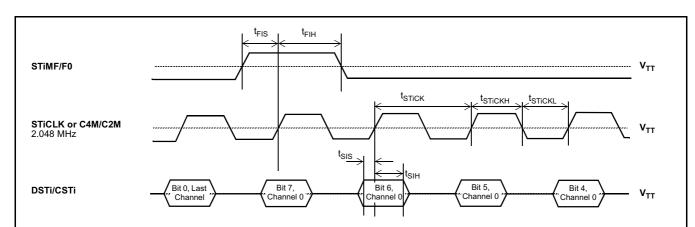

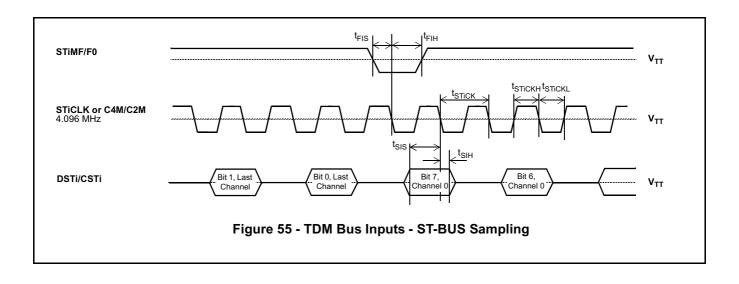

| Figure 55 - | TDM Bus Inputs - ST-BUS Sampling                                            | 167 |

| Figure 56 - | TDM Bus Output Clocking Parameters - Generic                                | 169 |

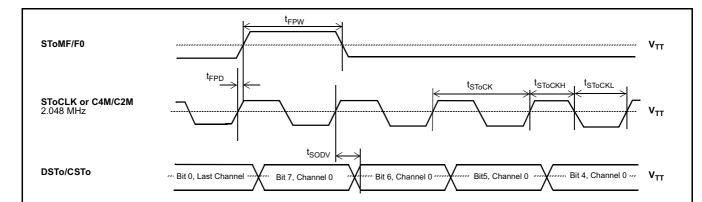

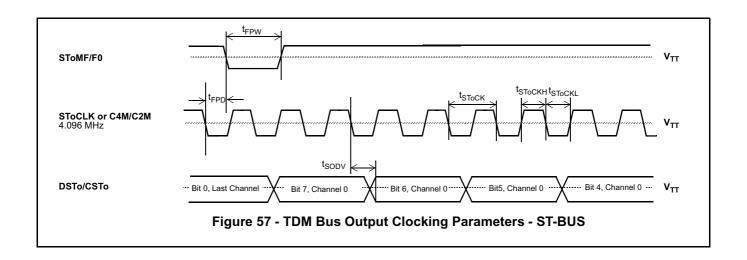

| Figure 57 - | TDM Bus Output Clocking Parameters - ST-BUS                                 | 169 |

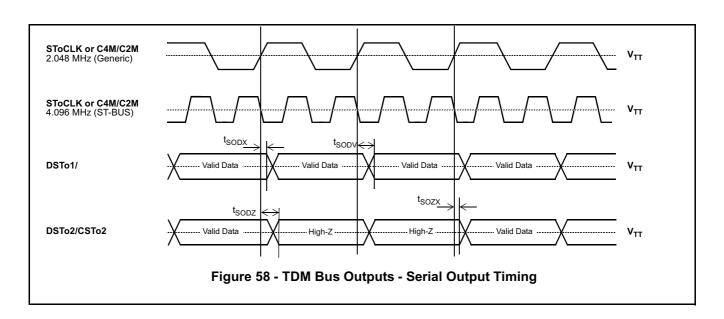

| Figure 58 - | TDM Bus Outputs - Serial Output Timing                                      | 169 |

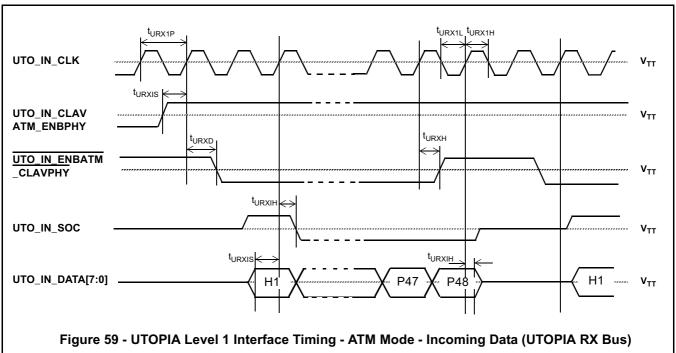

| Figure 59 - | UTOPIA Level 1 Interface Timing - ATM Mode - Incoming Data (UTOPIA RX Bus)  | 170 |

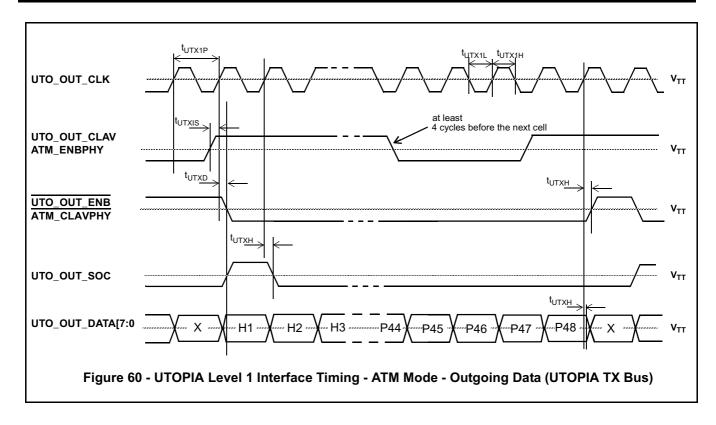

| Figure 60 - | UTOPIA Level 1 Interface Timing - ATM Mode - Outgoing Data (UTOPIA TX Bus)  | 171 |

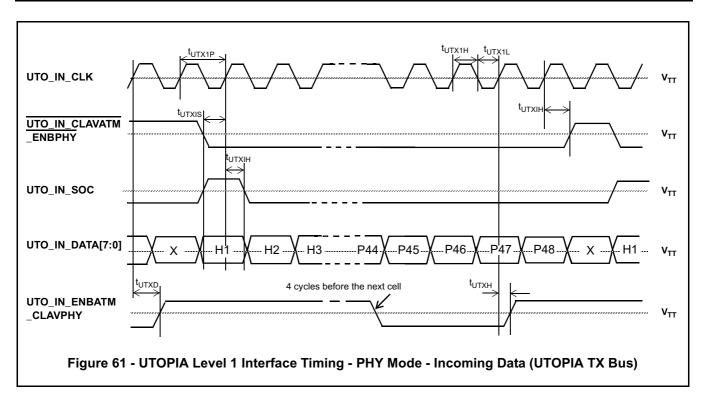

| Figure 61 - | UTOPIA Level 1 Interface Timing - PHY Mode - Incoming Data (UTOPIA TX Bus)  | 172 |

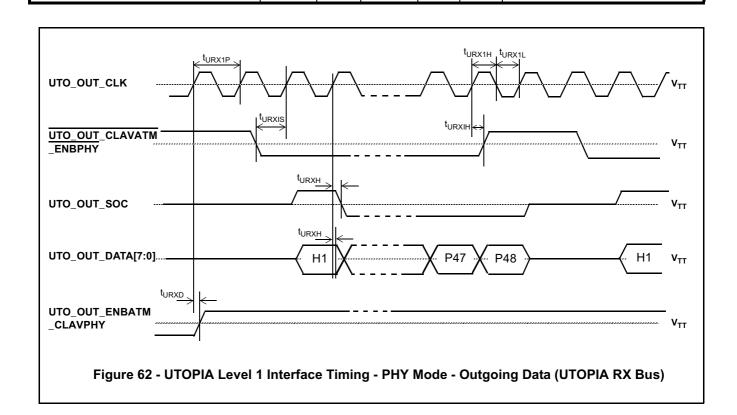

| Figure 62 - | UTOPIA Level 1 Interface Timing - PHY Mode - Outgoing Data (UTOPIA RX Bus)  | 173 |

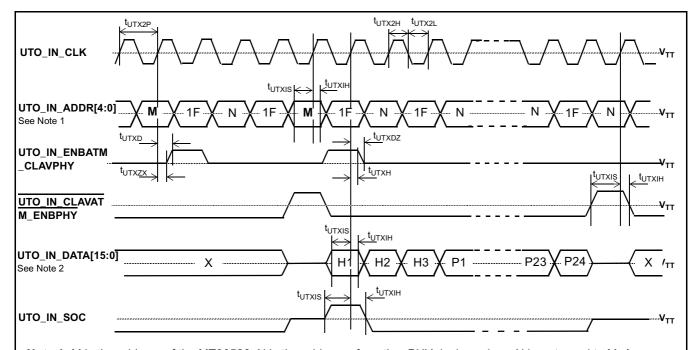

| Figure 63 - | UTOPIA Level 2 Interface Timing - PHY Mode - Incoming Data (UTOPIA TX Bus)  | 174 |

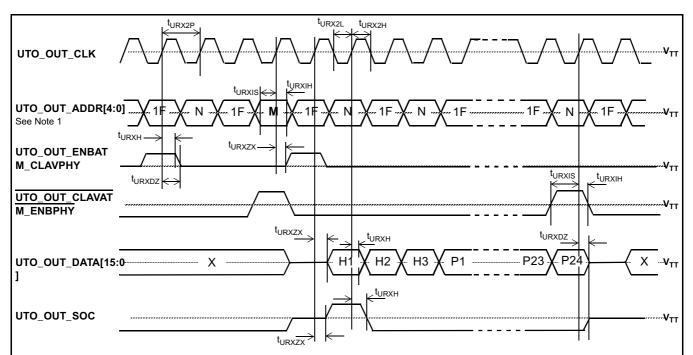

| Figure 64 - | UTOPIA Level 2 Interface Timing - PHY Mode - Outgoing Data (UTOPIA RX Bus)  | 176 |

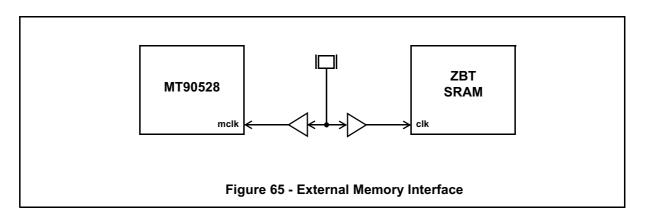

| Figure 65 - | External Memory Interface                                                   | 177 |

| Figure 66 - | ATM Mode: External UTOPIA Pin Connections                                   |     |

| Figure 67 - | PHY Mode: External UTOPIA Pin Connections                                   | 180 |

# **List of Tables**

| Table 1 -  | Microprocessor Interface Pins                                                  | 19  |

|------------|--------------------------------------------------------------------------------|-----|

| Table 2 -  | External Memory Interface Pins                                                 | 20  |

| Table 3 -  | TDM Port Pins                                                                  | 21  |

| Table 4 -  | UTOPIA Bus Pins                                                                | 23  |

| Table 5 -  | Clock Management Pins                                                          | 25  |

| Table 6 -  | Master Clock, Test, and Power Pins                                             | 26  |

| Table 7 -  | Pinout Summary                                                                 | 27  |

| Table 8 -  | Pinout by Ball Pin Number                                                      | 28  |

| Table 9 -  | Package Dimensions                                                             | 34  |

| Table 10 - | Possible Memory Configurations                                                 | 39  |

| Table 11 - | Formation of the Reassembly Circular Buffer Base Address                       | 45  |

| Table 12 - | Fields within the SDT Reassembly Control Structure                             | 69  |

| Table 13 - | Operation of Correction/Detection State Machine in Correction State            | 70  |

| Table 14 - | Operation of Correction/Detection State Machine in Detection State             | 70  |

| Table 15 - | Operation of UDT Fast Sequence Number Processing State Machine                 | 71  |

| Table 16 - | Examples of Operation of the UDT Fast Sequence Number Processing State Machine | 73  |

| Table 17 - | Operation of SDT Fast Sequence Number Processing State Machine                 |     |

| Table 18 - | Examples of Operation of SDT Fast Sequence Number Processing State Machine     | 75  |

| Table 19 - | Formation of SDT Reassembly Circular Buffer Base Addresses to External Memory  | 79  |

| Table 20 - | Sample Gapping Circuitry Calculation (N = 18)                                  | 99  |

| Table 21 - | Center Frequency and Accuracy                                                  | 104 |

| Table 22 - | Relevant Specifications                                                        | 104 |

| Table 23 - | Minimum Input Wander and Jitter Tolerance                                      | 105 |

| Table 24 - | Maximum Allowed Intrinsic Output Jitter                                        | 105 |

| Table 25 - | Internal Memory Map                                                            | 108 |

| Table 26 - | Register Summary                                                               | 114 |

| Table 27 - | Chip Wide Reset Register                                                       | 127 |

| Table 28 - | Main Status Register                                                           | 127 |

| Table 29 - | Low Address Word Indirection Register                                          | 127 |

| Table 30 - | High Address Indirection Command Register                                      | 128 |

| Table 31 - | Indirection Data Register                                                      | 128 |

| Table 32 - | Main Interrupt Enable Register                                                 | 128 |

| Table 33 - | MT90528 Revision Register                                                      | 129 |

| Table 34 - | TX_SAR Pointer Table Base Register (one per port)                              | 129 |

| Table 35 - | Data TX_SAR Configuration Register                                             | 130 |

| Table 36 - | Data TX_SAR Write Pointer Register                                             | 130 |

| Table 37 - | Data TX_SAR Read Pointer Register                                              | 130 |

| Table 38 - | Data TX_SAR Control Register                                                   | 131 |

| Table 39 - | Data Cell Generation Time Out Register                                         | 131 |

| Table 40 - | Data TX_SAR Status Register                                                    | 131 |

| Table 41 - | TX_SAR Master Enable Register                                                  | 132 |

| Table 42 - | UDT Reassembly Control Register                                                | 132 |

| Table 43 - | UDT Reassembly Service Enable Register                                         | 132 |

| Table 44 - | UDT Reassembly Status Register                                                 | 133 |

| Table 45 - | UDT Reassembly Cell Counter Register                                           |     |

| Table 46 - | Data RX_SAR Control Register                                                   | 134 |

| Table 47 - | Data RX_SAR Status Register                                                    | 134 |

| Table 48 - | Data RX_SAR Configuration Register                                             | 135 |

| Table 49 - | Data RX_SAR Write Pointer Register                                             | 135 |

| Table 50 - | Data RX_SAR Read Pointer Register                                              | 136 |

# Data Sheet

| Table 51 -  | Data DV SAD Call Counter Pagister                                 | 126 |

|-------------|-------------------------------------------------------------------|-----|

| Table 51 -  | Data RX_SAR Cell Counter RegisterSDT Reassembly Control Register  |     |

| Table 52 -  | SDT Reassembly Service Enable Register                            |     |

| Table 53 -  |                                                                   |     |

|             | SDT Reassembly Call Counter Status Register                       |     |

| Table 55 -  | SDT Reassembly Cell Counter Status Register                       |     |

| Table 56 -  | SDT Reassembly Cell Counter Register                              |     |

| Table 57 -  | MIB Timeout Configuration Register                                |     |

| Table 58 -  | MIB Timeout Status Register 1                                     |     |

| Table 59 -  | MIB Timeout Status Register 2                                     |     |

| Table 60 -  | Timeout Configuration Register (one per port)                     |     |

| Table 61 -  | UTOPIA Configuration Register                                     |     |

| Table 62 -  | UTOPIA Number of Concatenated Bits Register                       |     |

| Table 63 -  | LUT Base Address Register                                         |     |

| Table 64 -  | VC Match Register                                                 |     |

| Table 65 -  | VC Match Enable Register                                          | 143 |

| Table 66 -  | VP Match Register                                                 | 143 |

| Table 67 -  | VP Match Enable Register                                          | 143 |

| Table 68 -  | UTOPIA Parity Mismatches Register                                 | 143 |

| Table 69 -  | UTOPIA FIFO Status Register                                       | 144 |

| Table 70 -  | UTOPIA Status Register                                            | 144 |

| Table 71 -  | UTOPIA Service Enable Register                                    | 144 |

| Table 72 -  | UTOPIA Incoming Cell Counter                                      | 145 |

| Table 73 -  | UDT VCI for Port p (one per port)                                 | 145 |

| Table 74 -  | UDT VPI for Port p (one per port)                                 | 145 |

| Table 75 -  | Clock Management Configuration Register                           | 146 |

| Table 76 -  | External PLL Clock Source Register                                |     |

| Table 77 -  | Clocking Configuration Register (one per port)                    |     |

| Table 78 -  | Clocking Phase Accumulator Register (one per port)                |     |

| Table 79 -  | Clocking DCO Difference Register (one per port)                   |     |

| Table 80 -  | SRTS FIFO Status Register (one per port)                          |     |

| Table 81 -  | PLL Enable Register (one per port)                                |     |

| Table 82 -  | Main TDM Control Register 1                                       |     |

| Table 83 -  | Main TDM Control Register 2                                       |     |

| Table 84 -  | TDM Control Register 1 (one per port)                             |     |

| Table 85 -  | TDM Control Register 2 (one per port)                             |     |

| Table 86 -  | TDM Control Register 3 (one per port)                             |     |

| Table 87 -  | TDM Control Register 4 (one per port)                             |     |

| Table 88 -  | TDM Control Register 5 (one per port)                             |     |

| Table 89 -  | TDM Control Register 6 (one per port)                             |     |

| Table 99 -  | Memory Arbiter Configuration Register                             |     |

| Table 90 -  | Parity Error Status Register                                      |     |

|             | · · · · · · · · · · · · · · · · · · ·                             |     |

| Table 92 -  | Absolute Maximum Ratings                                          |     |

| Table 93 -  | Recommended Operating Conditions                                  |     |

| Table 94 -  | DC Characteristics                                                |     |

| Table 95 -  | MCLK - Master Clock Input Parameters                              |     |

| Table 96 -  | PHY_CLK - Clock Input Parameters                                  |     |

| Table 97 -  | Intel Microprocessor Interface Timing - Read Cycle Parameters     |     |

| Table 98 -  | Intel Microprocessor Interface Timing - Write Cycle Parameters    |     |

| Table 99 -  | Motorola Microprocessor Interface Timing - Read Cycle Parameters  |     |

| Table 100 - | Motorola Microprocessor Interface Timing - Write Cycle Parameters |     |

| Table 101 - | External Memory Interface Timing - Read Cycle Parameters          |     |

| Table 102 - | External Memory Interface Timing - Write Cycle Parameters         | 164 |

| Table 103 - | TDM Bus Input Clock Parameters                                             | 166 |

|-------------|----------------------------------------------------------------------------|-----|

| Table 104 - | TDM Bus Input Data Parameters                                              | 166 |

| Table 105 - | TDM Bus Output Clock Parameters                                            | 168 |

| Table 106 - | TDM Bus Data Output Parameters                                             | 168 |

| Table 107 - | UTOPIA Level 1 Interface Timing - ATM mode - Incoming Data (UTOPIA RX Bus) | 170 |

| Table 108 - | UTOPIA Level 1 Interface Timing - ATM mode - Outgoing Data (UTOPIA TX Bus) | 170 |

| Table 109 - | UTOPIA Level 1 Interface Timing - PHY mode - Incoming Data (UTOPIA TX Bus) | 171 |

| Table 110 - | UTOPIA Level 1 Interface Timing - PHY mode - Outgoing Data (UTOPIA RX Bus) | 173 |

| Table 111 - | UTOPIA Level 2 Interface Timing - PHY mode - Incoming Data (UTOPIA TX Bus) | 174 |

| Table 112 - | UTOPIA Level 2 Interface Timing - PHY mode - Outgoing Data (UTOPIA RX Bus) | 175 |

| Table 113 - | MT90528 UTOPIA Signal Directions                                           | 178 |

| TABLE 114.  | Segmentation Latency                                                       | 181 |

| TABLE 115.  | Reassembly Latency                                                         | 182 |

| TABLE 116.  | End-to-End Latency                                                         | 183 |

|             |                                                                            |     |

### 1. Introduction

#### 1.1 Functional Overview

The MT90528 28-Port Primary Rate Circuit Emulation AAL1 SAR (Segmentation and Reassembly) device is intended to carry twenty-eight primary rate TDM (Time Division Multiplexed) circuits (DS1 or E1) over an ATM (Asynchronous Transfer Mode) network using Circuit Emulation Services (CES). The MT90528 is ideally suited for channelized DS3/E3 (i.e., DS3/E3 accessed as multiple DS1/E1) bandwidth. At its interface to the TDM network, the MT90528 can be connected directly to a wide variety of industry-standard framers and LIUs (line interface units), or to a 2.048 Mbps ST-BUS TDM backplane. At its interface to the ATM network, the MT90528 supports a wide selection of UTOPIA-compliant Physical layer devices, and customer-specific ASICs which meet the UTOPIA (Level 1 or Level 2) specification.

The MT90528 provides several modes of Circuit Emulation Services in one device. The MT90528 implements CES for DS1 and E1 rates, as standardized in the ATM Forum CES standard (af-vtoa-0078.000 Version 2). The MT90528 supports both Unstructured and Structured circuit emulation of 28 independent TDM interfaces carrying DS1 or E1 traffic. In Unstructured CES mode, 28 VCCs (Virtual Circuit Connections) are supported. In Structured CES mode, flexible Nx64 kbps VCC assignment is supported, providing options ranging from a maximum of 896 VCCs carrying 64 kbps each (N = 1), to 28 VCCs carrying N = 32, to a smaller number of VCCs carrying up to N = 128. The MT90528 supports Structured CES with, or without, CAS (Channel Associated Signalling). MT90528 Management functions and statistics in accordance with the ATM Forum's CES MIB (Management Information Base) are supported.

On the TDM side, the MT90528 features twenty-eight primary rate TDM ports operating at 1.544 Mbps (Generic) or 2.048 Mbps (Generic or ST-BUS). The configurable TDM ports interface directly with DS1 or E1 framers for Nx64 Structured operation, as well as with DS1 or E1 LIUs (or M13 multiplexers) in Unstructured mode for reduced delay in the segmentation (ATM transmit) direction. The TDM interfaces are capable of operating with the line-rate bit clocks (1.544 MHz or 2.048 MHz), or with framed bus clocks at 1.544 MHz, 2.048 MHz or 4.096 MHz.

Each of the twenty-eight TDM ports contains a PLL (Phase Locked Loop), allowing independent timing of each TDM port. Alternatively in SDT mode, the MT90528 can be operated in backplane mode with a single timing source. Each independent PLL supports four modes of clock recovery: from SRTS time-stamps, from the cell-stream through the Adaptive Clock Method, from the Physical layer (synchronous method), or from the TDM interface line-rate. Although clock recovery is fully supported internally, an optional external PLL or clock source is also supported.

On the ATM interface side, the MT90528 device meets the ATM Forum standard UTOPIA Bus Level 2. The MT90528 is capable of operating as a UTOPIA "master" (ATM-end) or "slave" (PHY-end). ATM-end operation supports connection to a range of standard physical layer transceivers. PHY-end operation allows the MT90528 to be used in systems where pre-existing ASICs are available as "master" and require a "slave" device for interconnection. In PHY-end mode, the MT90528 is capable of Multi-PHY operation and has address inputs for this purpose. The UTOPIA port can operate in 8-bit or 16-bit mode, with a clock rate up to 52 MHz.

The MT90528 features a 16-bit microprocessor interface, capable of operating in Intel or Motorola mode, that is used to configure the device and monitor the management functions.

External memory (synchronous ZBT SRAM) is used in Structured CES operation to provide circular buffers in the segmentation direction and to provide CDV buffering in the reassembly direction. In addition, if the application's non-CBR data throughput (signalling or other) is low, the external memory can be used to provide a Receive Data Cell Buffer and a Transmit Data Cell Buffer for non-CBR data cells to be read or written, for processing by the external CPU. Unstructured CES operation requires no external memory (except where non-CBR data cell buffers are desired).

Segmentation / External VC Look-Up Reassembly **Synchronous** Table Circular Buffers **ZBT SRAM** MT90528 **External Memory** Controller Tx/Segmentation (X 28) CSTi/LOSi UTOPIA TDM DSTi STICLK TX **UTOPIA** OUTPUT **INPUT** SAR Interface BLOCK Local **BLOCK** STIMF Memory Clock > C4M/C2M\_b Management → F0\_b UTOPIA CSTo/LOSo **RX SARs** TDM INPUT DSTo (UDT, OUTPUT SToCLK **BLOCK** SDT, Data) SToMF Local **BLOCK** PLL Memory Rx/Reassembly (X 28) Registers Boundary-Microprocessor Scan Logic Interface Logic JTAG Interface 16-bit Microprocessor Interface

Figure 1 - MT90528 Block Diagram

### 2. Features

## 2.1 Key Functionality

- High-capacity AAL1 CES SAR device with 28 primary rate TDM ports operating at DS1 or E1 rates.

- Supports major modes of Circuit Emulation Services (CES) for DS1 and E1 as per af-vtoa-0078.000:

- Logical Nx64 Structured Service, using 2.048 Mbps TDM bus

- DS1 Nx64 Basic Service

- DS1 Nx64 Service with CAS

- E1 Nx64 Basic Service

- E1 Nx64 Service with CAS

- DS1 Unstructured Service

- E1 Unstructured Service.

- Supports AAL1 Trunking as per af-vtoa-0089.000:

- Up to 128 TDM channels can be carried per VCC (up to 896 TDM channels per device).

- Compliant with ITU-T Rec. I.363.1.

- Supports mixed DS1/E1 operation.

- Supports mixed UDT/SDT operation.

- Total clock recovery solution integrated on-chip.

- Supports non-CBR data cells and OAM cells destined for microprocessor with Transmit and Receive Data Cell Buffers.

## 2.2 Microprocessor Interface

- 16-bit microprocessor port, configurable to Motorola or Intel timing.

- Indirect reads and writes possible to internal and external memory blocks.

- Programmable interrupts for control and statistics.

- Allows access to internal registers and memory for initialization, control, and statistics.

- Allows access to external RAM for initialization, control, and observation.

# 2.3 External Memory Interface

- Supports common, commercially-available, no-latency flow-through and pipelined synchronous SRAM (ZBT, NoBL, NtRAM).

- Supports common SSRAM memory sizes 128K x 16, 256K x16, 512K x 16 and 1M x 16; 128K x 18, 256K x 18, 512K x 18 and 1M x 18 (parity is optional).

#### 2.4 TDM Interface

- Flexible TDM port allows operation with a wide selection of framers, LIUs, switches and multiplexers.

- Twenty-eight independently-timed, highly configurable, TDM interfaces can operate using:

- bit-clock rate (Unstructured CES)

- framed ST-BUS or Generic TDM bus (Structured CES independent mode)

- common TDM backplane clock using ST-BUS or Generic TDM bus (Structured CES backplane mode).

- Supports up to 896 bidirectional TDM channels.

### 2.5 UTOPIA Interface

- UTOPIA Level 2 compliant 16-bit or 8-bit bus, capable of running at up to 52 MHz.

- Accepts data rate of up to 622 Mbps.

- Supports both "master" (ATM-end) and "slave" (PHY-end) operation.

- Supports multi-PHY (MPHY) mode when operating as a PHY device.

- Capable of operating in UTOPIA Level 1 mode (8-bit bus running at up to 25 MHz), for connection to older devices.

- Supports up to 896 bidirectional VCCs (Structured Nx64 mode).

- VPI/VCI Match and Match Enable filter prevents excessive look-up table accesses to external memory.

- Cell reception based on look-up table allows flexible VCC assignment for CBR VCCs (allows non-contiguous VCC assignment).

- Automatically eliminates null cells (i.e., VPI and VCI = 0).

- Look-up table supports up to 65536 VCC entries.

### 2.6 Segmentation and Reassembly Modules

- Supports AAL1 Segmentation and Reassembly for Structured and Unstructured CES as specified in af-vtoa-0078.000.

- Supports non-multiframe or multiframe circuit emulation, using AAL1 structure formats as described in af-vtoa-0078.000: Nx64 Basic Service (single frame structure), or DS1 or E1 Nx64 Service with CAS (multiframe structure).

- Supports transmission and reception of up to 128 TDM channels per VCC in accordance with af-vtoa-0089.001 (ATM Trunking using AAL1 for Narrowband Services).

- Supports Unstructured CES and Structured CES simultaneously on different ports.

- Supports 28 bidirectional VCCs, carrying 1.544 Mbps or 2.048 Mbps, in Unstructured CES mode.

- Supports up to 896 bidirectional VCCs, carrying from 1 to 128 DS0 (64 kbps) TDM channels, in Structured CES mode (up to 896 DS0 channels total).

- UDT reassembly works with 28 per-port timing engines for fast processing and low delay variation in Unstructured CES mode. (1 VCC per port, for 28 UDT VCCs total.)

- Low latency in Unstructured CES mode provided by on-chip CDV buffering which does not require any external memory.

- Internal CDV buffers of 2048 bytes for each UDT port.

- Maximum UDT CDV buffering of ± 4.9 ms in DS1 mode and ± 3.7 ms in E1 mode.

- External CDV buffers of 1024 bytes for each SDT port.

- Maximum SDT CDV buffering of ±± 63.75 ms (dependent on the Reassembly Circular Buffer size and number of channels per VC).

- Non-CBR data cell transmission and reception for software-implemented SAR function (through non-CBR Data Cell Buffers in external memory).

- Gathers statistical information and provides management statistics for network management through microprocessor interface

- Per VCC monitoring compliant with ATMF CES specification Version 2.0 MIB.

- Low latency in segmentation and reassembly directions.

## 2.7 Clock Management

- Individual, per-port, integrated clock-recovery PLL allows for flexible, independent timing on each TDM port.

- Per-port Stratum 4 digital PLL supports several clock recovery modes:

- Synchronous clocking generates DS1 or E1 clock from network reference (19.44 MHz or 8 kHz)

- Adaptive clocking recovers clock from received-data buffer fill-level

- SRTS recovers clock from received RTS (residual time stamp) nibbles

- Line-rate clocking PLL locks to incoming DS1 or E1 clock and reduces jitter

- Free-running clocks PLL provides free-running high-accuracy clock for start-up or no-signal conditions (accuracy limited by MCLK accuracy)

- Direct control of PLL output frequency offset from centre frequency can be configured via CPU.

- Support for optional external PLL such as MT9042 or MT9044: primary & secondary network references and primary & secondary LOS references output to external PLL; TDM\_CLOCK input from external PLL.

- Bus clock I/O for operation in backplane mode: C4M/C2M and F0.

## 2.8 Testing Modes

- Per-port TDM\_in to TDM\_out low-latency loopback (DSTi input stream to DSTo output stream).

- Per-port TDM\_in to TDM\_out loopback through the Segmentation and Reassembly Circular Buffers in external memory (SDT mode only).

- Flexible, multi-stream, per-channel TDM circular-buffer loopback possible in SDT Backplane mode.

- Loopback provided from incoming UTOPIA FIFO to outgoing UTOPIA FIFO (with or without filtering by Match and Match Enable registers).

#### 2.9 Miscellaneous

- Master clock (MCLK) rate of 66.0 MHz.

- 2.5 Volt core supply and 3.3 Volt I/O supply (5V tolerant I/Os).

- Power consumption: 1.9 W.

- IEEE 1149 (JTAG) Boundary-Scan Test Access Port.

- 456-pin Plastic BGA.

- -40 to +85C (industrial temperature range).

## 2.10 Interrupts

- Wide variety of interrupt source bits, allowing for easy monitoring of MT90528 operation.

- Associated enable bits which enable or disable assertion of the service request and, ultimately, the IRQ interrupt pin.

### 2.10.1 Module Level Service Requests

#### 2.10.1.1 External Memory Interface Module

• External Memory Read Parity Error Alarm.

#### 2.10.1.2 TDM Module

- Per-port Loss of Signal Alarm (UDT mode only).

- Per-port UDT TDM Output Buffer Error Alarm (UDT mode only).

- Per-port SDT TDM Output Buffer Error Alarm (SDT mode only).

- Per-port Simple Underrun Error Alarm (SDT mode only).

- Per-port Permanent Underrun Error Alarm (SDT mode only).

#### 2.10.1.3 UTOPIA Module

- UTOPIA Incoming Cell Counter Rollover.

- Incoming Parity Mismatches Counter Rollover.

#### 2.10.1.4 TX\_SAR Module

• Data TX\_SAR - Transmit Non-CBR Data Cell Buffer Empty Alarm.

#### 2.10.1.5 UDT RX SAR Module

- Reassembled Cell Counter Rollover.

- AAL1-byte Header Error (i.e., CRC and/or Parity Error) Counter Rollover.

- AAL1-byte Sequence Error Counter Rollover.

- Lost Cell Counter Rollover.

- Misinserted Cell Counter Rollover.

- Write Underrun Counter Rollover.

- Write Overrun Counter Rollover.

- Late Cell Arrival Counter Rollover.

- Overall UDT Cell Counter Rollover.

#### 2.10.1.6 SDT RX\_SAR Module

- Reassembled Cell Counter Rollover.

- AAL1-byte Header Error (i.e., CRC and/or Parity Error) Counter Rollover.

- AAL1-byte Sequence Error Counter Rollover.

- Lost Cell Counter Rollover.

- Misinserted Cell Counter Rollover.

- Pointer Reframe Counter Rollover.

- Pointer Parity Error Counter Rollover.

- Write Underrun Counter Rollover.

- Write Overrun Counter Rollover.

- Pointer Out-of-Range Indicator.

- CAS Changed Status Indicator (only in CAS mode).

- Overall SDT Cell Counter Rollover.

#### 2.10.1.7 Data RX SAR Module

- Data RX\_SAR Cell Arrival Indicator.

- Data RX SAR Non-CBR Data Cell Buffer Overrun Alarm.

- Data RX SAR Buffer Half Full Indicator.

- Data Cell Counter Rollover.

#### 2.10.1.8 UDT Reassembly-Side Timeout Module

- Per-port Cut VC Alarm.

- Per-port Late Cell Arrival Alarm.

### 2.11 Statistics

The MT90528 provides a number of statistics to allow monitoring of the MT90528. These statistics generally parallel the operation of some of the service request source bits.

#### 2.11.1 TDM Module

- Per-port Simple Underrun Channel Indicator status field indicates which channel of the TDM port last experienced a simple underrun (SDT mode only).

- Per-port Permanent Underrun Channel Indicator status field indicates whether or not a particular channel of the TDM port has experienced a permanent underrun (SDT mode only).

#### 2.11.2 UTOPIA Module

- UTOPIA Incoming Cell Counter.

- Incoming Parity Mismatch Counter.

#### 2.11.3 TX SAR Module

Per-VC Transmitted Cell Counter.

#### 2.11.4 UDT RX SAR Module

- Within each VC's UDT Reassembly Control Structure, there is a bit (V = VC Arrival) which is set each time that a cell arrives on the VC. CPU monitoring of this bit can be used to provide per-VC timeout monitoring.

- As well, there is a late VC status bit and a cut VC status bit for each port (and therefore VC). These

bits are set when user-programmable timeout periods are passed without cells arriving on the VCs in

question.

- In addition to the counters themselves, if one of the following per-VC counters rolls over and the corresponding service enable bit for the counter is set, a status field indicates the number of the TDM port associated with the last UDT Reassembly Control Structure to generate a serviceable event.

- Per-VC Reassembled Cell Counter.

- Per-VC AAL1-byte Header Error Counter.

- Per-VC AAL1-byte Sequence Error Counter.

- Per-VC Lost Cell Counter.

- Per-VC Misinserted Cell Counter.

- Per-VC Write Underrun Counter.

- Per-VC Write Overrun Counter.

- Per-VC Late Cell Arrival Counter.

- Overall UDT Cell Counter.

#### 2.11.5 SDT RX\_SAR Module

- Within each VC's SDT Reassembly Control Structure, there is a bit (V = VC Arrival) which is set each time that a cell arrives on the VC. CPU monitoring of this bit can be used to provide per-VC timeout monitoring.

- In addition to the counters themselves, if one of the following per-VC counters rolls over and the corresponding service enable bit for the counter is set, a status field indicates the address in internal memory of the last SDT Reassembly Control Structure to generate a serviceable event.

- Per-VC Reassembled Cell Counter.

- Per-VC AAL1-byte Header Error Counter.

- Per-VC AAL1-byte Sequence Error Counter.

- Per-VC Lost Cell Counter.

- Per-VC Misinserted Cell Counter.

- Per-VC Pointer Reframe Counter.

- Per-VC Pointer Parity Error Counter.

- Per-VC Write Underrun Counter.

- Per-VC Write Overrun Counter.

- Overall SDT Cell Counter.

# 3. Pin Descriptions

## 3.1 Functional Pin Descriptions

Ball pin numbers are given in the following tables as defined in Figure 2 on page 32. Pins for buses are listed with the MSB appearing first.

I/O definitions are: Output (O), Input (I), Bidirectional (I/O), Power (PWR), or Ground (GND).

Input pad types are: CMOS or Schmitt, 3.3V. The notations "PU" and "PD" are used, respectively, to indicate that a pad has a weak internal pullup or pulldown resistor. All 3.3V inputs are 5V tolerant. The 3.3V CMOS inputs have a switching threshold of 1.6V, and tolerate input levels of up to 5V; therefore they are 5V TTL compatible.

Output pad types are described by voltage rail and current capability. 3.3V CMOS outputs will satisfy 5V TTL input thresholds at the rated current of the output.

**Table 1 - Microprocessor Interface Pins**

| Ball Pin #                                                                                                           | Pin Name       | I/O | Туре                   | Description                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------|----------------|-----|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E9                                                                                                                   | Intel/Moto     | I   | 3.3V CMOS<br>PD        | This input selects the microprocessor interface mode as Intel (pulled HIGH) or Motorola (pulled LOW). This pin must be configured before power-up.                                                                          |

| A7                                                                                                                   | CS             | I   | 3.3V CMOS<br>PU        | Active LOW chip select signal.                                                                                                                                                                                              |

| D8                                                                                                                   | WR/R_W         | I   | 3.3V CMOS<br>PU        | Active LOW Write Strobe (Intel) / Read_Write (Motorola).                                                                                                                                                                    |

| C7                                                                                                                   | RD/DS          | I   | 3.3V CMOS<br>PU        | Active LOW Read Strobe (Intel) / Active LOW Data Strobe (Motorola).                                                                                                                                                         |

| В7                                                                                                                   | AEM            | I   | 3.3V CMOS<br>PD        | Access External Memory - CPU accesses external memory when HIGH (internal memory and registers when LOW). This pin is usually connected to a high-order CPU address line.                                                   |

| C15, A16, E15,<br>D15, B16, C16,<br>A17, B17, D16,<br>C17, A18, B18,<br>C18, D17, A19,<br>B19, C19, D18,<br>A20, E17 | CPU_ADD[20:1]  | I   | 3.3V CMOS<br>PD        | CPU Address lines A20-A1.  All microprocessor accesses to the device are word-wide, but addresses in this document are given as byte addresses. The virtual A[0] bit would select between high and low bytes within a word. |

| D9, C8, B8, A8,<br>D10, C9, B9, A9,<br>D11, E11, C10,<br>B10, A10, C11,<br>B11, D12                                  | CPU_DATA[15:0] | I/O | 3.3V CMOS<br>PD / 12mA | CPU data bus. All CPU accesses are word accesses.                                                                                                                                                                           |

| C12                                                                                                                  | RDY/DTACK      | 0   | 3.3V, 24mA             | Ready (Intel) / Data Transfer Acknowledge (Motorola). Acts as normal output in Intel mode, tristated when CS is HIGH; acts as active LOW pseudo-open-drain output in Motorola mode.                                         |

| A11                                                                                                                  | ĪRQ            | 0   | 3.3V, 24mA             | Active LOW interrupt line (operates as open-drain: high-impedance when inactive).                                                                                                                                           |

**Table 2 - External Memory Interface Pins**

| Ball Pin #                                                                                              | Pin Name       | I/O | Туре                  | Description                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------|----------------|-----|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| H26                                                                                                     | MEM_CS_1       | 0   | 3.3V, 8mA             | Active LOW memory chip select signal for bank 1. This signal is used in all memory configurations to select bank 1 of external memory.                                                        |

| H25                                                                                                     | MEM_CS_2       | 0   | 3.3V, 8mA             | Active LOW memory chip select signal for bank 2. This signal is used to enable memory bank 2 when 2 or more banks of external RAM are connected to the MT90528.                               |

| H24                                                                                                     | MEM_CS_3       | 0   | 3.3V, 8mA             | Active LOW memory chip select signal for bank 3. This signal is used to enable memory bank 3 when 4 banks of external RAM are connected to the MT90528.                                       |

| J23                                                                                                     | MEM_CS_4       | 0   | 3.3V, 8mA             | Active LOW memory chip select signal for bank 4. This signal is used to enable memory bank 4 when 4 banks of external RAM are connected to the MT90528.                                       |

| G26                                                                                                     | MEM_WR         | 0   | 3.3V, 8mA             | Active LOW write enable.                                                                                                                                                                      |

| B21, D20, C21,<br>A22, B22, D21,                                                                        | MEM_ADD[19:0]  | 0   | 3.3V, 8mA             | Memory address lines. Connect these lines to external memory as follows:                                                                                                                      |

| A23, C22, D22,<br>B23, A24, C23,                                                                        |                |     |                       | Bank Size of 1M: MEM_ADD[19:0] are connected to memory.                                                                                                                                       |

| D23, B24, A25,                                                                                          |                |     |                       | Bank Size of 512K: MEM_ADD[18:0] are connected to memory.                                                                                                                                     |

| A26, B26, C24,                                                                                          |                |     |                       | Bank Size of 256K: MEM_ADD[17:0] are connected to memory.                                                                                                                                     |

| B25, C25                                                                                                |                |     |                       | Bank Size of 128K: MEM_ADD[16:0] are connected to memory.                                                                                                                                     |

| D24, C26, D25,<br>E23, E24, D26,<br>G22, F23, E25,<br>E26, J22, F24,<br>G23, F25, F26,<br>G24, H23, G25 | MEM_DATA[17:0] | I/O | 3.3V CMOS<br>PD / 8mA | Memory data lines. MEM_DATA[15:8] represent the upper byte; MEM_DATA[7:0] represent the lower byte. Optional lines [17] and [16] represent the high and low byte parity values, respectively. |

**Table 3 - TDM Port Pins**

|                                                                                                                                                                                 |                 |     |                 | IDM Port Pins                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ball Pin #                                                                                                                                                                      | Pin Name        | I/O | Type            | Description                                                                                                                                                                                                                                                                                                                           |

| P24, M25, K25,<br>K23, AB25, Y24,<br>V24, T24, AD20,<br>AC21, AE24,<br>AD26, AE17,<br>AE15, AE13,<br>AE11, AC10,<br>AC8, AD6, AD4,<br>AC3, AB2, W4,<br>V3, U1, P3, N2,<br>K2    | STiCLK[27:0]    | I   | 3.3V CMOS<br>PD | PCM Input Clocks.  These inputs are used to sample the incoming PCM data/ CAS from the E1 or DS1 lines.  In Structured CES mode, ST-BUS format STiCLK is 4.096 MHz; Generic format STiCLK is 1.544 MHz or 2.048 MHz for DS1; or 2.048 MHz for E1.  In Unstructured CES mode, these pins accept 1.544 MHz for DS1 or 2.048 MHz for E1. |

| R25, N25, N22,<br>L22, AC26, W22,<br>W26, U25, AF20,<br>AD21, AE23,<br>AF26, AF18,<br>AB14, AF14,<br>AC12, AC11,<br>AE8, AE6, AE4,<br>AD3, AC1, AA1,<br>W2, R4, R3, N4,<br>L2   | STiMF[27:0]     | ı   | 3.3V CMOS<br>PD | Input Frame Pulses. In Structured CES mode, these pins are input frame pulses which set the frame boundaries for the incoming data and CAS. These signals can be either multiframe or frame inputs. Not used in Unstructured CES mode.                                                                                                |

| P25, M26, M23,<br>J24, AA23, Y23,<br>V25, T23, AC19,<br>AE22, AD23,<br>AE26, AD17,<br>AD15, AD13,<br>AB12, AE9, AD8,<br>AF5, AF3, AD2,<br>AA4, V5, U4, U2,<br>R1, N1, K1        | DSTi[27:0]      | I   | 3.3V CMOS<br>PD | Serial PCM Data Inputs. In Unstructured CES mode, each pin carries a 1.544 Mbps or 2.048 Mbps serial stream. In Structured CES mode, each pin carries a 1.544 Mbps or 2.048 Mbps serial stream which contains a 24-channel data stream in DS1 operation or a 32-channel data stream in E1 operation.                                  |

| R24, N24, K26,<br>J25, AB24, Y25,<br>V23, U26, AE20,<br>AF22, AF24,<br>AD25, AC16,<br>AF16, AF13,<br>AF11, AF9, AF7,<br>AC7, AC5, AC4,<br>Y5, Y3, W1, U3,<br>R2, N3, L3         | CSTi/LOSi[27:0] | ı   | 3.3V CMOS<br>PD | Serial PCM Signalling Inputs or Input Loss of Signal (LOS) Indicators.  In Structured CES mode, these pins carry CAS signalling inputs.  In Unstructured CES mode, these pins input LOS signals from external LIUs.                                                                                                                   |

| R26, R23, L24,<br>N23, AC25,<br>AA26, W24, U24,<br>AC18, AC20,<br>AC22, AE25,<br>AE18, AC15,<br>AE14, AD12,<br>AD10, AB10,<br>AD7, AD5, AE1,<br>AB3, AA2, W3,<br>T4, T1, M5, L1 | SToCLK[27:0]    | 0   | 3.3V, 4mA       | PCM Output Clocks. These outputs are used to drive the PCM data/CAS out to the E1 or DS1 lines. In Structured CES mode, ST-BUS format SToCLK is 4.096 MHz; Generic format SToCLK is 1.544 MHz or 2.048 MHz for DS1; or 2.048 MHz for E1. In Unstructured CES mode, these pins provide 1.544 MHz for DS1 or 2.048 MHz for E1.          |

**Table 3 - TDM Port Pins**

| Ball Pin #                                                                                                                                                                     | Pin Name            | I/O | Туре      | Description                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T25, P23, M24,<br>K24, AC24,<br>AB26, Y26, U22,<br>AF19, AB18,<br>AB20, AF25,<br>AC17, AF17,<br>AF15, AC13,<br>AD11, AF8, AB8,<br>AE5, AF2, AD1,<br>AB1, Y2, T5, T3,<br>P4, M1 | SToMF[27:0]         | 0   | 3.3V, 4mA | Output Frame Pulses.  In Structured CES mode, these pins are output frame pulses which set the frame boundaries for the outgoing data and CAS. These signals are programmable as either multiframe pulses or frame pulses.  Not used in Unstructured CES mode.                                                     |

| T26, N26, L25,<br>J26, AB23,<br>AA24, W25, U23,<br>AD19, AE21,<br>AD22, AC23,<br>AD18, AE16,<br>AC14, AE12,<br>AE10, AC9, AF6,<br>AC6, AE2, AB4,<br>Y4, V4, V1, T2,<br>P1, M3  | DSTo[27:0]          | 0   | 3.3V, 4mA | Serial PCM Data Outputs.  In Unstructured CES mode, each pin carries a 1.544 Mbps or 2.048 Mbps serial stream.  In Structured CES mode, each pin carries a 1.544 Mbps or 2.048 Mbps serial stream which contains a 24-channel data stream in DS1 operation or a 32-channel data stream in E1 operation.            |

| R22, P26, L26,<br>L23, AA22,<br>AA25, W23, V26,<br>AE19, AF21,<br>AF23, AD24,<br>AB16, AD16,<br>AD14, AF12,<br>AF10, AD9, AE7,<br>AF4, AF1, AC2,<br>AA3, Y1, V2, P5,<br>P2, M2 | CSTo/<br>LOSo[27:0] | 0   | 3.3V, 4mA | Serial PCM Signalling Outputs or Output Loss of Signal (LOS) Indicators.  In Structured CES mode, these pins output CAS signalling. In Unstructured CES mode, each of these pins outputs an LOS or general purpose signal based on a user-programmable value in TDM Control Register 3 for the corresponding port. |

Table 4 - UTOPIA Bus Pins

| Ball Pin #                                                              | Pin Name          | I/O | Туре                   | Description                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------|-------------------|-----|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| H2                                                                      | UTO_IN_CLK        | I/O | 3.3V CMOS PD<br>/ 24mA | Synchronization clock for data transfer on UTO_IN_DATA. This clock can be output from an internal divider (equal to MCLK/2) or input from an external source. (RxClk when the MT90528 is in ATM mode; TxClk when the MT90528 is in PHY mode.)                                                                                                |

| L4, J1, J2, J3,<br>K4                                                   | UTO_IN_ADD[4:0]   | I   | 3.3V CMOS PD           | Multi-PHY address signals. These address inputs are used to poll the MT90528 and to select the next MPHY device to receive data on UTO_IN_DATA. These signals are driven from the ATM-end to the PHY-end, and only used when the MT90528 is in PHY mode. (Inactive when the MT90528 is in ATM mode; TxAddr when the MT90528 is in PHY mode.) |

| H3, J4, G1, G2,<br>H4, G3, F1, F2,<br>H5, G4, F3, E1,<br>E2, F4, D1, E3 | UTO_IN_DATA[15:0] | I   | 3.3V CMOS PD           | 16-bit UTOPIA input bus for cell-based data. When in 8-bit mode, only bits[7:0] are active. (RxData[15:0] when the MT90528 is in ATM mode; TxData[15:0] when in PHY mode.)                                                                                                                                                                   |

| K5                                                                      | UTO_IN_PAR        | I   | 3.3V CMOS PD           | Odd parity bit over UTO_IN_DATA[15:0]. When in 8-bit mode, odd parity bit over UTO_IN_DATA[7:0]. (RxPrty when the MT90528 is in ATM mode; TxPrty when in PHY mode.)                                                                                                                                                                          |

| К3                                                                      | UTO_IN_SOC        | I   | 3.3V CMOS PD           | Start of Cell for UTO_IN_DATA. Active HIGH input signal indicating the first word/byte of the cell being received. (RxSOC when the MT90528 is in ATM mode; TxSOC when in PHY mode.)                                                                                                                                                          |

| M4                                                                      | UTO_IN_CLAVATM_   | I   | 3.3V CMOS PD           | Handshake input for UTO_IN_DATA.                                                                                                                                                                                                                                                                                                             |

|                                                                         | ENBPHY            |     |                        | When the MT90528 is in ATM mode, this input is RxClav, indicating that the PHY-end has a complete cell to transfer on UTO_IN_DATA.                                                                                                                                                                                                           |

|                                                                         |                   |     |                        | When the MT90528 is in PHY mode, this input is TxEnb*, indicating that the ATM-end is transferring valid data on UTO_IN_DATA.                                                                                                                                                                                                                |

| H1                                                                      | UTO_IN_ENBATM_    | 0   | 3.3V, 16mA             | Handshake output for UTO_IN_DATA.                                                                                                                                                                                                                                                                                                            |

|                                                                         | CLAVPHY           |     |                        | When the MT90528 is in ATM mode, this output is RxEnb*, indicating that the MT90528 will begin to sample UTO_IN_DATA and UTO_IN_SOC at the end of the next clock cycle.                                                                                                                                                                      |

|                                                                         |                   |     |                        | When the MT90528 is in PHY mode, this output is TxClav, indicating that the MT90528 can accept a complete cell on UTO_IN_DATA.                                                                                                                                                                                                               |

Table 4 - UTOPIA Bus Pins

| Ball Pin #                                                              | Pin Name          | I/O | Туре                                                                                                                                                                                                                                                                                                                    | Description                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------|-------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D5                                                                      | UTO_OUT_CLK       | I/O | 3.3V CMOS PD<br>/ 24mA                                                                                                                                                                                                                                                                                                  | Synchronization clock for data transfer on UTO_OUT_DATA. This clock can be output from an internal divider (equal to MCLK/2) or input from an external source. (TxClk when the MT90528 is in ATM mode; RxClk when the MT90528 is in PHY mode.)                      |

| E4, D2, C1, D3,<br>D4                                                   | UTO_OUT_ADD[4:0]  | 1   | 3.3V CMOS PD Multi-PHY Address signals. These address inputs are use the MT90528, and to select the next MPHY device to dri on UTO_OUT_DATA. These signals are driven from the end to the PHY-end, and only used when the MT90528 is mode. (Inactive when the MT90528 is in ATM mode; when the MT90528 is in PHY mode.) |                                                                                                                                                                                                                                                                     |

| A2, B3, C3, C4,<br>A3, B4, C5, A4,<br>D6, E7, B5, A5,<br>C6, D7, B6, A6 | UTO_OUT_DATA[15:0 | 0   | 3.3V, 12mA                                                                                                                                                                                                                                                                                                              | 16-bit UTOPIA output data bus for cell-based data. When in 8-bit mode, only bits[7:0] are active. In Level 2 operation, this bus is tristated between cell transmissions. (TxData when the MT90528 is in ATM mode; RxData when in PHY mode.)                        |