## Freescale Semiconductor

**Data Sheet**

MCF5475EC Rev. 2, 10/2004

# MCF547x Integrated Microprocessor Electrical Characteristics

Applies to the MCF5470, MCF5471, MCF5472, MCF5473, MCF5474, and MCF5475

This chapter contains electrical specification tables and reference timing diagrams for the MCF547*x* microprocessor. This section contains detailed information on power considerations, DC/AC electrical characteristics, and AC timing specifications of the MCF547*x*.

#### NOTE

The parameters specified in this MPU document supersede any values found in the module specifications.

## 1 Maximum Ratings

Table 1 lists maximum and minimum ratings for supply and operating voltages and storage temperature. Operating outside of these ranges may cause erratic behavior or damage to the processor.

#### **Table of Contents**

| 1  | Maximum Ratings                                     | 1  |

|----|-----------------------------------------------------|----|

| 2  | Thermal Characteristics                             |    |

| 3  | DC Electrical Specifications                        |    |

| 4  | Supply Voltage Sequencing and Separation            |    |

|    | Cautions                                            | 5  |

| 5  | Output Driver Capability and Loading                |    |

| 6  | PLL Timing Specifications                           | 7  |

| 7  | Reset Timing Specifications                         | 8  |

| 8  | FlexBus                                             | 8  |

| 9  | SDRAM Bus                                           | 11 |

| 10 | PCI Bus                                             | 17 |

| 11 | Fast Ethernet AC Timing Specifications              | 18 |

| 12 | General Timing Specifications                       | 21 |

| 13 | I <sup>2</sup> C Input/Output Timing Specifications | 21 |

| 14 | JTAG and Boundary Scan Timing                       | 23 |

| 15 | DSPI Electrical Specifications                      | 26 |

| 16 | Timer Module AC Timing Specifications               | 26 |

**Table 1. Absolute Maximum Ratings**

| Rating                                                | Symbol              | Value                                              | Units |

|-------------------------------------------------------|---------------------|----------------------------------------------------|-------|

| External (I/O pads) supply voltage (3.3-V power pins) | EV <sub>DD</sub>    | -0.3 to +4.0                                       | V     |

| Internal logic supply voltage                         | IV <sub>DD</sub>    | -0.5 to +2.0                                       | V     |

| Memory (I/O pads) supply voltage (2.5-V power pins)   | SD V <sub>DD</sub>  | -0.3 to +4.0 SDR Memory<br>-0.3 to +2.8 DDR Memory | V     |

| PLL supply voltage                                    | PLL V <sub>DD</sub> | -0.5 to +2.0                                       | V     |

| Internal logic supply voltage, input voltage level    | V <sub>in</sub>     | -0.5 to +3.6                                       | V     |

| Storage temperature range                             | T <sub>stg</sub>    | -55 to +150                                        | °C    |

## 2 Thermal Characteristics

## 2.1 Operating Temperatures

Table 2 lists junction and ambient operating temperatures.

**Table 2. Operating Temperatures**

| Characteristic                         | Symbol            | Value            | Units |

|----------------------------------------|-------------------|------------------|-------|

| Maximum operating junction temperature | Tj                | 105              | °C    |

| Maximum operating ambient temperature  | T <sub>Amax</sub> | <70 <sup>1</sup> | °C    |

| Minimum operating ambient temperature  | T <sub>Amin</sub> | -0               | °C    |

NOTES:

## 2.2 Thermal Resistance

Table 3 lists thermal resistance values.

**Table 3. Thermal Resistance**

| Characteristic                                           |                         | Symbol            | Value                | Unit |

|----------------------------------------------------------|-------------------------|-------------------|----------------------|------|

| 324 pin TEPBGA — Junction to ambient, natural convection | Four layer board (2s2p) | $\theta_{JMA}$    | 22–24 <sup>1,2</sup> | °CW  |

| 388 pin TEPBGA — Junction to ambient, natural convection | Four layer board (2s2p) | $\theta_{JMA}$    | 20–22 <sup>1,2</sup> | °CW  |

|                                                          |                         |                   |                      |      |

| Junction to ambient (@200 ft/min)                        | Four layer board (2s2p) | $\theta_{JMA}$    | 23 <sup>1,2</sup>    | °CW  |

| Junction to board                                        |                         | $\theta_{JB}$     | 15 <sup>3</sup>      | °CW  |

| Junction to case                                         |                         | $\theta_{\sf JC}$ | 10 <sup>4</sup>      | °CW  |

| Junction to top of package                               | Natural convection      | Ψ <sub>jt</sub>   | 2 <sup>1,5</sup>     | °CW  |

This published maximum operating ambient temperature should be used only as a system design guideline. All device operating parameters are guaranteed only when the junction temperature lies within the specified range.

#### NOTES:

- $\theta_{JA}$  and  $\Psi_{jt}$  parameters are simulated in accordance with EIA/JESD Standard 51-2 for natural convection. Freescale recommends the use of  $\theta_{JA}$  and power dissipation specifications in the system design to prevent device junction temperatures from exceeding the rated specification. System designers should be aware that device junction temperatures can be significantly influenced by board layout and surrounding devices. Conformance to the device junction temperature specification can be verified by physical measurement in the customer's system using the  $\Psi_{it}$  parameter, the device power dissipation, and the method described in EIA/JESD Standard 51-2.

- <sup>2</sup> Per JÉDEC JESD51-6 with the board horizontal.

- Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

# 3 DC Electrical Specifications

Table 4 lists DC electrical operating temperatures. This table is based on an operating voltage of  $EV_{DD} = 3.3 V_{DC} \pm 0.3 V_{DC}$  and  $IV_{DD}$  of  $1.5 \pm 0.07 V_{DC}$ .

| Characteristic                                                      | Symbol                  | Min  | Max  | Units |

|---------------------------------------------------------------------|-------------------------|------|------|-------|

| External (I/O pads) operation voltage range                         | EV <sub>DD</sub>        | 3.0  | 3.6  | V     |

| Memory (I/O pads) operation voltage range (DDR Memory)              | SD V <sub>DD</sub>      | 2.30 | 2.70 | V     |

| Internal logic operation voltage range <sup>1</sup>                 | IV <sub>DD</sub>        | 1.43 | 1.58 | V     |

| PLL Analog operation voltage range <sup>1</sup>                     | PLL V <sub>DD</sub>     | 1.43 | 1.58 | V     |

| USB oscillator operation voltage range                              | USB_OSV <sub>DD</sub>   | 3.0  | 3.6  | V     |

| USB digital logic operation voltage range                           | USBV <sub>DD</sub>      | 3.0  | 3.6  | V     |

| USB PHY operation voltage range                                     | USB_PHYV <sub>DD</sub>  | 3.0  | 3.6  | V     |

| USB oscillator analog operation voltage range                       | USB_OSCAV <sub>DD</sub> | 1.43 | 1.58 | V     |

| USB PLL operation voltage range                                     | USB_PLLV <sub>DD</sub>  | 1.43 | 1.58 | V     |

| Input high voltage SSTL 3.3V (SDR DRAM)                             | V <sub>IH</sub>         | 2.0  | 3.6  | V     |

| Input low voltage SSTL 3.3V (SDR DRAM)                              | V <sub>IL</sub>         | -0.5 | 0.8  | V     |

| Input high voltage SSTL 2.5V (DDR DRAM)                             | V <sub>IH</sub>         | 2.0  | 2.8  | V     |

| Input low voltage SSTL 2.5V (DDR DRAM)                              | V <sub>IL</sub>         | -0.5 | 0.8  | V     |

| Output high voltage I <sub>OH</sub> = 8 mA, 16 mA,24 mA             | V <sub>OH</sub>         | 2.4  | _    | V     |

| Output low voltage I <sub>OL</sub> = 8 mA, 16 mA,24 mA <sup>5</sup> | V <sub>OL</sub>         | _    | 0.5  | V     |

| Capacitance <sup>2</sup> , V <sub>in</sub> = 0 V, f = 1 MHz         | C <sub>IN</sub>         | _    | TBD  | pF    |

**Table 4. DC Electrical Specifications**

#### NOTES:

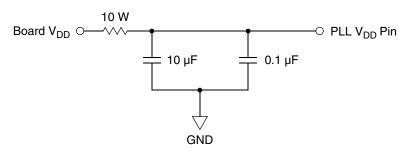

<sup>&</sup>lt;sup>1</sup> IV<sub>DD</sub> and PLL V<sub>DD</sub> should be at the same voltage. PLL V<sub>DD</sub> should have a filtered input. Please see Figure 1 for an example circuit. Note: There are three PLL V<sub>DD</sub> inputs. A filter circuit should used on each PLL V<sub>DD</sub> input.

<sup>&</sup>lt;sup>2</sup> Capacitance C<sub>IN</sub> is periodically sampled rather than 100% tested.

## 3.1 PLL Power Filtering

To further enhance noise isolation, an external filter is strongly recommended for PLL analog  $V_{DD}$  pins. The filter shown in Figure 1 should be connected between the board  $V_{DD}$  and the PLL  $V_{DD}$  pins. The resistor and capacitors should be placed as close to the dedicated PLL  $V_{DD}$  pin as possible.

Figure 1. System PLL V<sub>DD</sub> Power Filter

## 3.2 USB Power Filtering

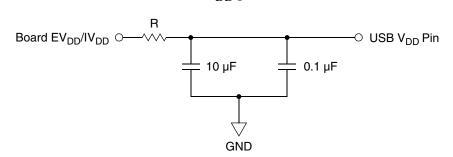

To minimize noise, a external filters are required for each of the USB power pins. The filter shown in Figure 2 should be connected between the board  $EV_{DD}$  or  $IV_{DD}$  and each of the USB  $V_{DD}$  pins. The resistor and capacitors should be placed as close to the dedicated USB  $V_{DD}$  pin as possible. A separate filter circuit should be included for each USB  $V_{DD}$  pin, a total of five circuits.

Figure 2. USB V<sub>DD</sub> Power Filter

#### **NOTE**

In addition to the above filter circuitry, a 0.01 F capacitor is also recommended in parallel with those shown.

Table 5 lists the resistor values and supply voltages to be used in the circuit for each of the USB  $V_{DD}$  pins.

| USB V <sub>DD</sub> Pin | Nominal Voltage | Resistor Value (R) |

|-------------------------|-----------------|--------------------|

| USB_OSCVDD              | 3.3V            | 0Ω                 |

| USBVDD                  | 3.3V            | 0Ω                 |

| USB_PHYVDD              | 3.3V            | 0Ω                 |

| USB_OSCAVDD             | 1.5V            | 0Ω                 |

| USB_PLLVDD              | 1.5V            | 10Ω                |

**Table 5. USB Filter Circuit Values**

MCF547x Integrated Microprocessor Electrical Characteristics, Rev. 2

#### Supply Voltage Sequencing and Separation 4 **Cautions**

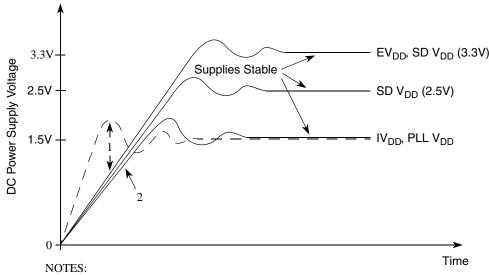

Figure 3 shows situations in sequencing the I/O  $V_{DD}$  (EV $_{DD}$ ), SDRAM  $V_{DD}$  (SD  $V_{DD}$ ), PLL  $V_{DD}$  (PLL  $V_{DD}$ ), and Core  $V_{DD}$  (IV<sub>DD</sub>).

- 1.  $\rm IV_{DD}$  should not exceed  $\rm EV_{DD}, SD~V_{DD}$  or PLL  $\rm V_{DD}$  by more than 0.4V at any time, including power-up.

- 2. Recommended that IV<sub>DD</sub>/PLL V<sub>DD</sub> should track EV<sub>DD</sub>/SD V<sub>DD</sub> up to 0.9V, then separate for completion of ramps.

- 3. Input voltage must not be greater than the supply voltage (EV<sub>DD</sub>, SD V<sub>DD</sub>, IV<sub>DD</sub>, or PLL V<sub>DD</sub>) by more than 0.5V at any time, including during power-up.

- 4. Use 1 microsecond or slower rise time for all supplies.

Figure 3. Supply Voltage Sequencing and Separation Cautions

The relationship between SD V<sub>DD</sub> and EV<sub>DD</sub> is non-critical during power-up and power-down sequences. Both SD  $V_{DD}$  (2.5V or 3.3V) and  $EV_{DD}$  are specified relative to  $IV_{DD}$ .

#### 4.1 Power Up Sequence

If EV<sub>DD</sub>/SD V<sub>DD</sub> are powered up with the IV<sub>DD</sub> at 0V, then the sense circuits in the I/O pads will cause all pad output drivers connected to the EV<sub>DD</sub>/SD V<sub>DD</sub> to be in a high impedance state. There is no limit on how long after EV<sub>DD</sub>/SD V<sub>DD</sub> powers up before IV<sub>DD</sub> must power up. IV<sub>DD</sub> should not lead the EV<sub>DD</sub>, SD V<sub>DD</sub> or PLL V<sub>DD</sub> by more than 0.4V during power ramp up, or there will be high current in the internal ESD protection diodes. The rise times on the power supplies should be slower than 1 microsecond to avoid turning on the internal ESD protection clamp diodes.

#### **Output Driver Capability and Loading**

The recommended power up sequence is as follows:

- 1. Use 1 microsecond or slower rise time for all supplies.

- IV<sub>DD</sub>/PLL V<sub>DD</sub> and EV<sub>DD</sub>/SD V<sub>DD</sub> should track up to 0.9V, then separate for the completion of ramps with EV<sub>DD</sub>/SD V<sub>DD</sub> going to the higher external voltages. One way to accomplish this is to use a low drop-out voltage regulator.

## 4.2 Power Down Sequence

If  $IV_{DD}PLL\ V_{DD}$  are powered down first, then sense circuits in the I/O pads will cause all output drivers to be in a high impedance state. There is no limit on how long after  $IV_{DD}$  and  $PLL\ V_{DD}$  power down before  $EV_{DD}$  or  $SD\ V_{DD}$  must power down.  $IV_{DD}$  should not lag  $EV_{DD}$ ,  $SD\ V_{DD}$ , or  $PLL\ V_{DD}$  going low by more than 0.4V during power down or there will be undesired high current in the ESD protection diodes. There are no requirements for the fall times of the power supplies.

The recommended power down sequence is as follows:

- 1. Drop IV<sub>DD</sub>/PLL V<sub>DD</sub> to 0V

- 2. Drop EV<sub>DD</sub>/SD V<sub>DD</sub> supplies

# 5 Output Driver Capability and Loading

Table 6 lists values for drive capability and output loading.

Table 6. I/O Driver Capability

| Signal                                                                                                                                         | Drive<br>Capability | Output<br>Load (C <sub>L</sub> ) |

|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------|

| SDRAMC (SDADDR[12:0], SDDATA[31:0], RAS, CAS, SDDM[3:0], SDWE, SDBA[1:0]                                                                       | 24 mA               | 15 pF                            |

| SDRAMC DQS and clocks (SDDQS[3:0], SDRDQS, SDCLK[1:0], SDCLK[1:0], SDCKE)                                                                      | 24 mA               | 15 pF                            |

| SDRAMC chip selects (SDCS[3:0])                                                                                                                | 24 mA               | 15 pF                            |

| FlexBus (AD[31:0], FBCS[5:0], ALE, R/W, BE/BWE[3:0], OE)                                                                                       | 16 mA               | 20 pF                            |

| FEC (EnMDIO, EnMDC, EnTXEN, EnTXD[3:0], EnTXER                                                                                                 | 8 mA                | 15 pF                            |

| Timer (TOUT[3:0])                                                                                                                              | 8 mA                | 50 pF                            |

| DACK[1:0]                                                                                                                                      | 8 mA                | 30 pF                            |

| PSC (PSCnTXD[3:0], PSCnRTS/PSCnFSYNC,                                                                                                          | 8 mA                | 30 pF                            |

| DSPI (DSPISOUT, DSPICS0/SS, DSPICS[2:3], DSPICS5/PCSS)                                                                                         | 24 mA               | 50 pF                            |

| PCI (PCIAD[31:0], PCIBG[4:1], PCIBG0/PCIREQOUT, PCIDEVSEL, PCICXBE[3:0], PCIFRM, PCIPERR, PCIRESET, PCISERR, PCISTOP, PCIPAR, PCITRDY, PCIIRDY | 16 mA               | 50 pF                            |

| I2C (SCL, SDA)                                                                                                                                 | 8 mA                | 50 pF                            |

| BDM (PSTCLK, PSTDDATA[7:0], DSO/TDO,                                                                                                           | 8 mA                | 25 pF                            |

| RSTO                                                                                                                                           | 8 mA                | 50 pF                            |

MCF547x Integrated Microprocessor Electrical Characteristics, Rev. 2

# 6 PLL Timing Specifications

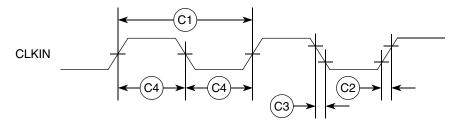

The specifications in Table 7 are for the CLKIN pin.

**Table 7. Clock Timing Specification**

| Num | Characteristic                       | Min   | Max  | Units |

|-----|--------------------------------------|-------|------|-------|

| C1  | Cycle time                           | 15.15 | 33.3 | ns    |

| C2  | Rise time (20% of Vdd to 80% of vdd) | _     | 2    | ns    |

| СЗ  | Fall time (80% of Vdd to 20% of Vdd) | _     | 2    | ns    |

| C4  | Duty cycle (at 50% of Vdd)           | 40    | 60   | %     |

### **Input Clock Timing Diagram**

Table 8 shows the supported PLL encodings.

Table 8. MCF547X Divide Ratio Encodings

| AD[12:8] <sup>1</sup> | Clock Ratio | CLKIN—PCI and FlexBus<br>Frequency Range<br>(MHz) | Internal XLB, SDRAM<br>Bus, and PSTCLK<br>Frequency Range<br>(MHz) | Core Frequency Range<br>(MHz) |

|-----------------------|-------------|---------------------------------------------------|--------------------------------------------------------------------|-------------------------------|

| 00011                 | 1:2         | 41.6–66.66                                        | 83.33–133.33                                                       | 166.66–266.66                 |

| 00101                 | 1:2         | 25.0–44.4                                         | 50.0-88.8                                                          | 100.0–177.66                  |

| 01111                 | 1:4         | 25.0–33.3                                         | 100–133.33                                                         | 200–266.66                    |

NOTES:

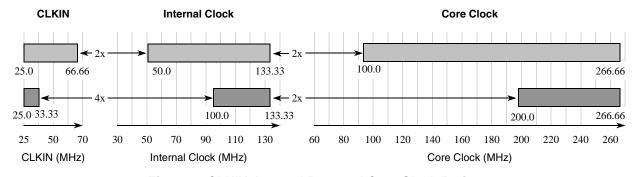

Figure 4 correlates CLKIN, internal bus, and core clock frequencies for the 1x–4x multipliers.

Figure 4. CLKIN, Internal Bus, and Core Clock Ratios

MCF547x Integrated Microprocessor Electrical Characteristics, Rev. 2

All other values of AD[12:8] are reserved.

# 7 Reset Timing Specifications

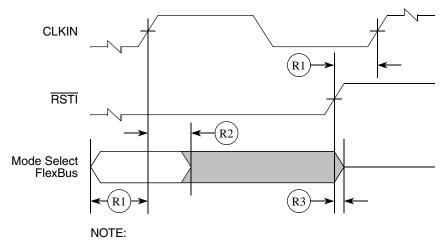

Table 9 lists specifications for the reset timing parameters shown in Figure 5

**Table 9. Reset Timing Specification**

| Num             | Characteristic          | 66 MHz | CLKIN | Units  |

|-----------------|-------------------------|--------|-------|--------|

| Nulli           | Cital acteristic        | Min    | Max   | Offics |

| R1 <sup>1</sup> | Valid to CLKIN (setup)  | 8      | _     | nS     |

| R2              | CLKIN to invalid (hold) | 1.0    | _     | nS     |

| R3              | RSTI to invalid (hold)  | 1.0    | _     | nS     |

NOTES:

Figure 5 shows reset timing for the values in Table 9.

Mode selects are registered on the rising clock edge before the cycle in which RSTI is recognized as being negated.

Figure 5. Reset Timing

## 8 FlexBus

A multi-function external bus interface called FlexBus is provided on the MCF5472 with basic functionality to interface to slave-only devices up to a maximum bus frequency of 66 MHz. It can be directly connected to asynchronous or synchronous devices such as external boot ROMs, flash memories, gate-array logic, or other simple target (slave) devices with little or no additional circuitry. For asynchronous devices, a simple chip-select based interface can be used. The FlexBus interface has six general purpose chip-selects ( $\overline{FBCS}[5:0]$ ). Chip-select  $\overline{FBCS0}$  can be dedicated to boot ROM access and can be programmed to be byte (8 bits), word (16 bits), or longword (32 bits) wide. Control signal timing is compatible with common ROM / flash memories.

RSTI and FlexBus data lines are synchronized internally. Setup and hold times must be met only if recognition on a particular clock is required.

## 8.1 FlexBus AC Timing Characteristics

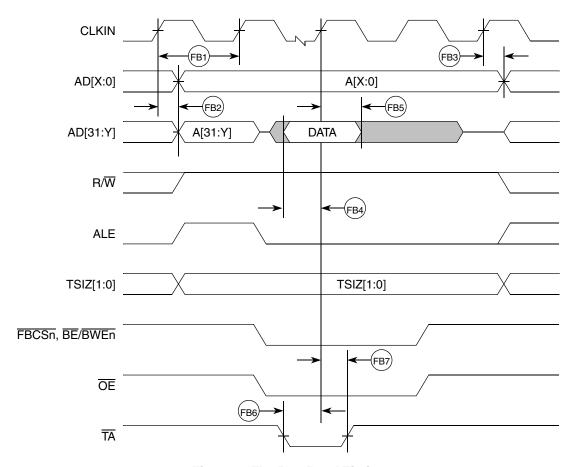

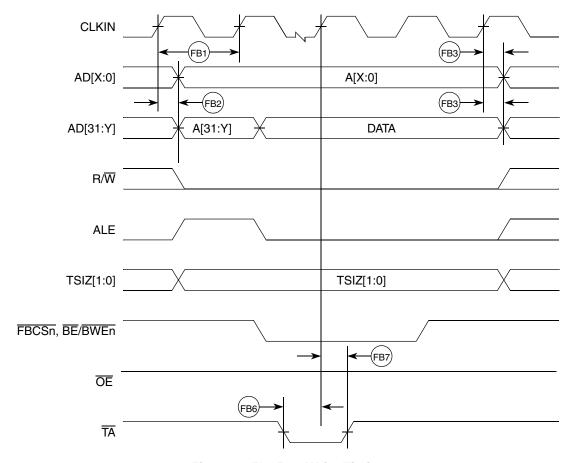

The following timing numbers indicate when data will be latched or driven onto the external bus, relative to the system clock.

**Table 10. FlexBus AC Timing Specifications**

| Num | Characteristic                                                                                                | Min   | Max   | Unit | Notes |

|-----|---------------------------------------------------------------------------------------------------------------|-------|-------|------|-------|

|     | Frequency of Operation                                                                                        | 30    | 66    | Mhz  | 1     |

| FB1 | Clock Period (CLKIN)                                                                                          | 15.15 | 33.33 | ns   | 2     |

| FB2 | Address, Data, and Control Output Valid (AD[31:0], FBCS[5:0], R/W, ALE, TSIZ[1:0], BE/BWE[3:0], OE, and TBST) | _     | 7.0   | ns   | 3     |

| FB3 | Address, Data, and Control Output Hold ((AD[31:0], FBCS[5:0], R/W, ALE, TSIZ[1:0], BE/BWE[3:0], OE, and TBST) | 1     | _     | ns   | 3, 4  |

| FB4 | Data Input Setup                                                                                              | 3.5   | _     | ns   |       |

| FB5 | Data Input Hold                                                                                               | 0     | _     | ns   |       |

| FB6 | Transfer Acknowledge (TA) Input Setup                                                                         | 4     | _     | ns   |       |

| FB7 | Transfer Acknowledge (TA) Input Hold                                                                          | 0     | _     | ns   |       |

| FB8 | Address Output Valid (PCIAD[31:0])                                                                            | _     | 7.0   | ns   | 5     |

| FB9 | Address Output Hold (PCIAD[31:0])                                                                             | 0     | _     | ns   | 5     |

#### NOTES:

The frequency of operation is the same as the PCI frequency of operation. The MCF547X supports a single external reference clock (CLKIN). This signal defines the frequency of operation for both FlexBus and PCI.

<sup>&</sup>lt;sup>2</sup> Max cycle rate is determined by CLKIN and how the user has the system PLL configured.

Timing for chip selects only applies to the FBCS[5:0] signals. Please see Section 9.2, "DDR SDRAM AC Timing Characteristics" for SDCS[3:0] timing.

<sup>&</sup>lt;sup>4</sup> The FlexBus supports programming an extension of the address hold. Please consult the MCF547X specification manual for more information.

These specs are used when the PCIAD[31:0] signals are configured as 32-bit, non-muxed FlexBus address signals.

#### **FlexBus**

Figure 6. FlexBus Read Timing

Figure 7. FlexBus Write Timing

## 9 SDRAM Bus

The SDRAM controller supports accesses to main SDRAM memory from any internal master. It supports either standard SDRAM or double data rate (DDR) SDRAM, but it does not support both at the same time. The SDRAM controller uses SSTL2 and SSTL3 I/O drivers. Both SSTL drive modes are programmable for either Class I or Class II drive strength.

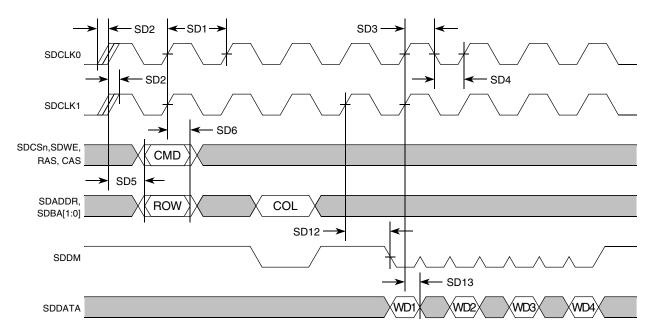

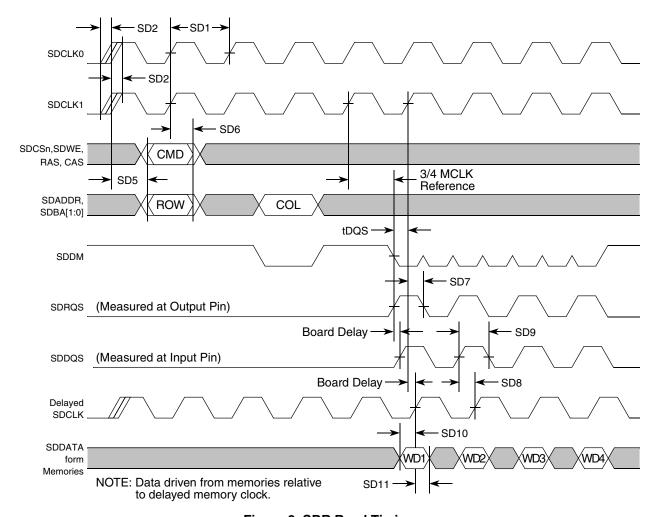

## 9.1 SDR SDRAM AC Timing Characteristics

The following timing numbers indicate when data will be latched or driven onto the external bus, relative to the memory bus clock, when operating in SDR mode on write cycles and relative to SDR\_DQS on read cycles. The MCF547x SDRAM controller is a DDR controller that has an SDR mode. Because it is designed to support DDR, a DQS pulse must still be supplied to the MCF547x for each data beat of an SDR read. The MCF547x accomplishes this by asserting a signal called SDR\_DQS during read cycles. Care must be taken during board design to adhere to the following guidelines and specs with regard to the SDR\_DQS signal and its usage.

#### **SDRAM Bus**

**Table 11. SDR Timing Specifications**

| Symbol | Characteristic                                                          | Min            | Max                      | Unit     | Notes |

|--------|-------------------------------------------------------------------------|----------------|--------------------------|----------|-------|

|        | Frequency of Operation                                                  | 83             | 133                      | Mhz      | 1     |

| SD1    | Clock Period (t <sub>CK</sub> )                                         | 7.52           | 12                       | ns       | 2     |

| SD2    | Clock Skew (t <sub>SK</sub> )                                           |                | TBD                      |          |       |

| SD3    | Pulse Width High (t <sub>CKH</sub> )                                    | 0.45           | 0.55                     | SDCLK    | 3     |

| SD4    | Pulse Width Low (t <sub>CKL</sub> )                                     | 0.45           | 0.55                     | SDCLK    | 4     |

| SD5    | Address, CKE, CAS, RAS, WE, BA, CS - Output Valid (t <sub>CMV</sub> )   |                | 0.5 × SDCLK +<br>1.0ns   | ns       |       |

| SD6    | Address, CKE, CAS, RAS, WE, BA, CS - Output Hold (t <sub>CMH</sub> )    | 2.0            |                          | ns       |       |

| SD7    | SDRDQS Output Valid (t <sub>DQSOV</sub> )                               |                | Self timed               | ns       | 5     |

| SD8    | SDDQS[3:0] input setup relative to SDCLK (t <sub>DQSIS</sub> )          | 0.25 × SDCLK   | 0.40 × SDCLK             | ns       | 6     |

| SD9    | SDDQS[3:0] input hold relative to SDCLK (t <sub>DQSIH</sub> )           | Does not apply | . 0.5 SDCLK fixe         | d width. | 7     |

| SD10   | Data Input Setup relative to SDCLK (reference only) (t <sub>DIS</sub> ) | 0.25 × SDCLK   |                          | ns       | 8     |

| SD11   | Data Input Hold relative to SDCLK (reference only) (t <sub>DIH</sub> )  | 1.0            |                          | ns       |       |

| SD12   | Data and Data Mask Output Valid (t <sub>DV</sub> )                      |                | 0.75 × SDCLK<br>+0.500ns | ns       |       |

| SD13   | Data and Data Mask Output Hold (t <sub>DH</sub> )                       | 1.5            |                          | ns       |       |

#### NOTES:

- The frequency of operation is either 2x or 4x the CLKIN frequency of operation. The MCF547X supports a single external reference clock (CLKIN). This signal defines the frequency of operation for both FlexBus and PCI, but SDRAM clock operates at the same frequency as the internal bus clock. Please see the PLL chapter of the MCF547X Specification for more information on setting the SDRAM clock rate.

- <sup>2</sup> SDCLK is one SDRAM clock in (ns).

- <sup>3</sup> Pulse width high plus pulse width low cannot exceed min and max clock period.

- <sup>4</sup> Pulse width high plus pulse width low cannot exceed min and max clock period.

- <sup>5</sup> SDR\_DQS is designed to pulse 0.25 clock before the rising edge of the memory clock. This is a guideline only. Subtle variation from this guideline is expected. SDR\_DQS will only pulse during a read cycle and one pulse will occur for each data beat.

- <sup>6</sup> SDR\_DQS is designed to pulse 0.25 clock before the rising edge of the memory clock. This spec is a guideline only. Subtle variation from this guideline is expected. SDR\_DQS will only pulse during a read cycle and one pulse will occur for each data heat.

- The SDR\_DQS pulse is designed to be 0.5 clock in width. The timing of the rising edge is most important. The falling edge does not affect the memory controller.

- Since a read cycle in SDR mode still uses the DQS circuit within the MCF547X, it is most critical that the data valid window be centered 1/4 clk after the rising edge of DQS. Ensuring that this happens will result in successful SDR reads. The input setup spec is just provided as guidance.

Figure 8. SDR Write Timing

Figure 9. SDR Read Timing

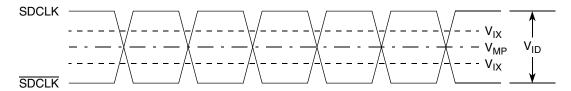

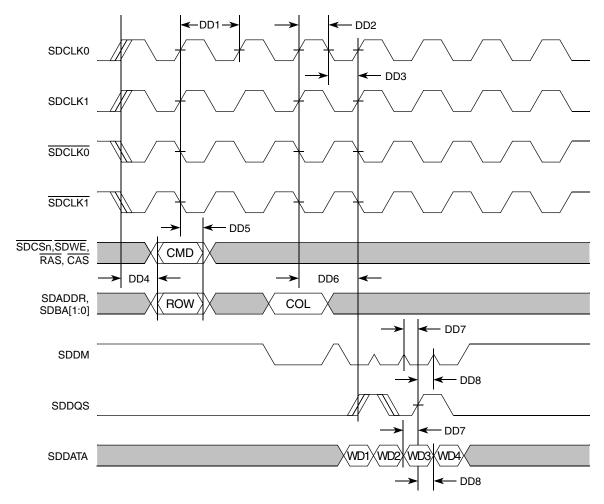

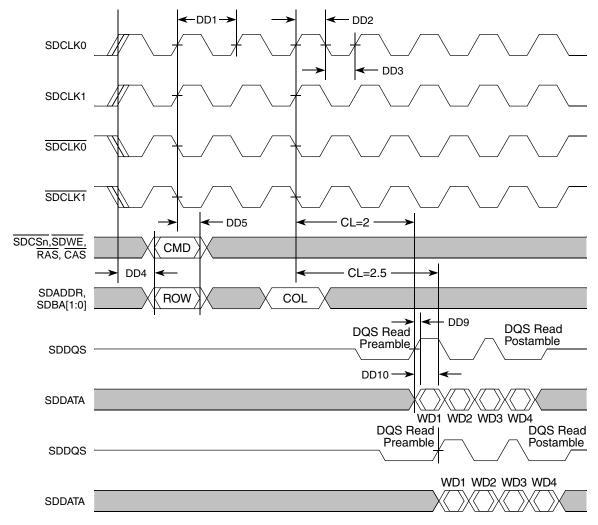

# 9.2 DDR SDRAM AC Timing Characteristics

When using the DDR SDRAM controller, the following timing numbers must be followed to properly latch or drive data onto the memory bus. All timing numbers are relative to the four DQS byte lanes.

Table 12shows the DDR clock crossover specifications.

**Table 12. DDR Clock Crossover Specifications**

| Symbol           | Characteristic                                         | Min  | Max          | Unit |

|------------------|--------------------------------------------------------|------|--------------|------|

| V <sub>MP</sub>  | Clock output mid-point voltage                         | 1.05 | 1.45         | V    |

| V <sub>OUT</sub> | Clock output voltage level                             | -0.3 | SD_VDD + 0.3 | V    |

| $V_{ID}$         | Clock output differential voltage (peak to peak swing) | 0.7  | SD_VDD + 0.6 | V    |

| V <sub>IX</sub>  | Clock crossing point voltage <sup>1</sup>              | 1.05 | 1.45         | V    |

NOTES:

MCF547x Integrated Microprocessor Electrical Characteristics, Rev. 2

The clock crossover voltage is only guaranteed when using the highest drive strength option for the SDCLK[1:0] and SDCLK[1:0] signals.

Figure 10. DDR Clock Timing Diagram

**Table 13. DDR Timing Specifications**

| Symbol | Characteristic                                                                                | Min                     | Max                     | Unit  | Notes  |

|--------|-----------------------------------------------------------------------------------------------|-------------------------|-------------------------|-------|--------|

|        | Frequency of Operation                                                                        | 83                      | 133                     | MHz   | 1      |

| DD1    | Clock Period (t <sub>CK</sub> )                                                               | 7.52                    | 12                      | ns    | 2      |

| DD2    | Pulse Width High (t <sub>CKH</sub> )                                                          | 0.45                    | 0.55                    | SDCLK | 3      |

| DD3    | Pulse Width Low (t <sub>CKL</sub> )                                                           | 0.45                    | 0.55                    | SDCLK | 4      |

| DD4    | Address, SDCKE, CAS, RAS, WE, SDBA, SDCS—Output Valid (t <sub>CMV</sub> )                     | _                       | 0.5 × SDCLK<br>+ 1.0 ns | ns    | 5      |

| DD5    |                                                                                               | 2.0                     | _                       | ns    |        |

| DD6    | Write Command to first DQS Latching Transition (t <sub>DQSS</sub> )                           | _                       | 1.25                    | SDCLK |        |

| DD7    | Data and Data Mask Output Setup (DQ->DQS) Relative to DQS (DDR Write Mode) (t <sub>QS</sub> ) | 1.0                     | _                       | ns    | 6<br>7 |

| DD8    | Data and Data Mask Output Hold (DQS->DQ) Relative to DQS (DDR Write Mode) (t <sub>QH</sub> )  | 1.0                     | _                       | ns    | 8      |

| DD9    | Input Data Skew Relative to DQS (Input Setup) (t <sub>IS</sub> )                              |                         | 1                       | ns    | 9      |

| DD10   | Input Data Hold Relative to DQS (t <sub>IH</sub> )                                            | 0.25 × SDCLK<br>+ 0.5ns | _                       | ns    | 10     |

| DD11   | DQS falling edge to SDCLK rising (output setup time) (t <sub>DSS</sub> )                      | 0.5                     | _                       | ns    |        |

| DD12   | DQS falling edge from SDCLK rising (output hold time) (t <sub>DSH</sub> )                     | 0.5                     | _                       | ns    |        |

| DD13   | DQS input read preamble width (t <sub>RPRE</sub> )                                            | 0.9                     | 1.1                     | SDCLK |        |

| DD14   | DQS input read postamble width (t <sub>RPST</sub> )                                           | 0.4                     | 0.6                     | SDCLK |        |

| DD15   | DQS output write preamble width (t <sub>WPRE</sub> )                                          | 0.25                    | _                       | SDCLK |        |

| DD16   | DQS output write postamble width (t <sub>WPST</sub> )                                         | 0.4                     | 0.6                     | SDCLK |        |

#### NOTES:

- The frequency of operation is either 2x or 4x the CLKIN frequency of operation. The MCF547X supports a single external reference clock (CLKIN). This signal defines the frequency of operation for both FlexBus and PCI, but SDRAM clock operates at the same frequency as the internal bus clock. Please see Section 2.2.6, "Reset Configuration Pins."

- <sup>2</sup> SDCLK is one memory clock in (ns).

- <sup>3</sup> Pulse width high plus pulse width low cannot exceed max clock period.

- <sup>4</sup> Pulse width high plus pulse width low cannot exceed max clock period.

- Command output valid should be 1/2 the memory bus clock (SDCLK) plus some minor adjustments for process, temperature, and voltage variations.

- This specification relates to the required input setup time of today's DDR memories. SDDATA[31:24] is relative to SDDQS3, SDDATA[23:16] is relative to SDDQS2, SDDATA[15:8] is relative to SDDQS1, and SDDATA[7:0] is relative SDDQS0.

- The first data beat will be valid before the first rising edge of SDDQS and after the SDDQS write preamble. The remaining data beats will be valid for each subsequent SDDQS edge.

MCF547x Integrated Microprocessor Electrical Characteristics, Rev. 2

#### **SDRAM Bus**

- This specification relates to the required hold time of today's DDR memories. SDDATA[31:24] is relative to SDDQS3, SDDATA[23:16] is relative to SDDQS2, SDDATA[15:8] is relative to SDDQS1, and SDDATA[7:0] is relative SDDQS0.

- Data input skew is derived from each SDDQS clock edge. It begins with a SDDQS transition and ends when the last data line becomes valid. This input skew must include DDR memory output skew and system level board skew (due to routing or other factors).

- 10 Data input hold is derived from each SDDQS clock edge. It begins with a SDDQS transition and ends when the first data line becomes invalid.

Figure 11. DDR Write Timing

Figure 12. DDR Read Timing

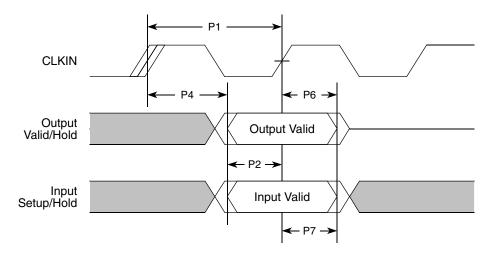

## 10 PCI Bus

The PCI bus on the MCF547x is PCI 2.2 compliant. The following timing numbers are mostly from the PCI 2.2 spec. Please refer to the PCI 2.2 spec for a more detailed timing analysis.

| Num | Characteristic                                                               | Min   | Max   | Unit | Notes |

|-----|------------------------------------------------------------------------------|-------|-------|------|-------|

|     | Frequency of Operation                                                       | 30    | 66    | MHz  | 1     |

| P1  | Clock Period (t <sub>CK</sub> )                                              | 15.15 | 33.33 | ns   | 2     |

| P2  | Address, Data, and Command (33< PCI ≤ 66 Mhz)—Input Setup (t <sub>IS</sub> ) | 3.0   | _     | ns   |       |

| P3  | Address, Data, and Command (0 < PCI $\leq$ 33 Mhz)—Input Setup ( $t_{IS}$ )  | 7.0   | _     | ns   |       |

| P4  | Address, Data, and Command (33-66 Mhz) - Output Valid (t <sub>DV</sub> )     | _     | 6.0   | ns   | 3     |

| P5  | Address, Data, and Command (0 -33 Mhz) - Output Valid (t <sub>DV</sub> )     |       | 11.0  | ns   |       |

**Table 14. PCI Timing Specifications**

MCF547x Integrated Microprocessor Electrical Characteristics, Rev. 2

| rabio i ii i di riiiiiig opodinoationo (dontinada) | Table 14. | . PCI Timing | <b>Specifications</b> | (continued) |

|----------------------------------------------------|-----------|--------------|-----------------------|-------------|

|----------------------------------------------------|-----------|--------------|-----------------------|-------------|

| Num | Characteristic                                                   | Min | Max | Unit | Notes |

|-----|------------------------------------------------------------------|-----|-----|------|-------|

| P6  | PCI signals (0 - 66 Mhz) - Output Hold (t <sub>DH</sub> )        | 0   | _   | ns   | 4     |

| P7  | PCI signals (0 - 66 Mhz) - Input Hold (t <sub>IH</sub> )         | 0   | _   | ns   | 5     |

| P8  | PCI REQ/GNT (33 < PCI ≤ 66Mhz) - Output valid (t <sub>DV</sub> ) | _   | 6   | ns   | 6     |

| P9  | PCI REQ/GNT (0 < PCI ≤ 33Mhz) - Output valid (t <sub>DV</sub> )  | _   | 12  | ns   |       |

| P10 | PCI REQ/GNT (33 < PCI $\leq$ 66Mhz) - Input Setup ( $t_{IS}$ )   | _   | 5   | ns   |       |

| P11 | PCI REQ (0 < PCI $\leq$ 33Mhz) - Input Setup ( $t_{IS}$ )        | 12  | _   | ns   |       |

| P12 | PCI GNT (0 < PCI $\leq$ 33Mhz) - Input Setup ( $t_{IS}$ )        | 10  | 1   | ns   |       |

#### NOTES:

- Please see Section 2.2.6, "Reset Configuration Pins," for more information on setting the PCI clock rate. Also specific guidelines may need to be followed when operating the system PLL below certain frequencies.

- <sup>2</sup> Max cycle rate is determined by CLKIN and how the user has the system PLL configured.

- <sup>3</sup> All signals defined as PCI bused signals. Does not include PTP (point-to-point) signals.

- <sup>4</sup> PCI 2.2 spec does not require an output hold time. Although the MCF547X may provide a slight amount of hold, it is not required or guaranteed.

- <sup>5</sup> PCI 2.2 spec requires zero input hold.

- <sup>6</sup> These signals are defined at PTP (Point-to-point) in the PCI 2.2 spec.

Figure 13. PCI Timing

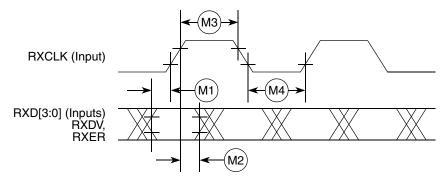

# 11 Fast Ethernet AC Timing Specifications

## 11.1 MII/7-WIRE Interface Timing Specs

The following timing specs are defined at the chip I/O pin and must be translated appropriately to arrive at timing specs/constraints for the EMAC\_10\_100 I/O signals.

The following timing specs meet the requirements for both MII and 7-Wire style interfaces for a range of transceiver devices. If this interface is to be used with a specific transceiver device the timing specs may be altered to match that specific transceiver.

| Num | Characteristic                      | Min | Max | Unit         |

|-----|-------------------------------------|-----|-----|--------------|

| M1  | RXD[3:0], RXDV, RXER to RXCLK setup | 5   | _   | ns           |

| M2  | RXCLK to RXD[3:0], RXDV, RXER hold  | 5   | _   | ns           |

| МЗ  | RXCLK pulse width high              | 35% | 65% | RXCLK period |

| M4  | RXCLK pulse width low               | 35% | 65% | RXCLK period |

Figure 14. MII Receive Signal Timing Diagram

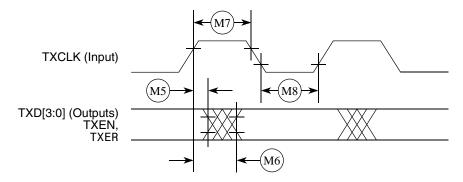

# 11.2 MII Transmit Signal Timing

**Table 16. MII Transmit Signal Timing**

| Num | Characteristic                        | Min | Max | Unit         |

|-----|---------------------------------------|-----|-----|--------------|

| M5  | TXCLK to TXD[3:0], TXEN, TXER invalid | 0   | _   | ns           |

| M6  | TXCLK to TXD[3:0], TXEN, TXER valid   | _   | 25  | ns           |

| M7  | TXCLK pulse width high                | 35% | 65% | TXCLK period |

| M8  | TXCLK pulse width low                 | 35% | 65% | TXCLK period |

Figure 15. MII Transmit Signal Timing Diagram

MCF547x Integrated Microprocessor Electrical Characteristics, Rev. 2

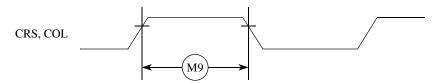

# 11.3 MII Async Inputs Signal Timing (CRS, COL)

**Table 17. MII Transmit Signal Timing**

| Num | Characteristic               | Min | Max | Unit          |

|-----|------------------------------|-----|-----|---------------|

| M9  | CRS, COL minimum pulse width | 1.5 |     | TX_CLK period |

Figure 16. MII Async Inputs Timing Diagram

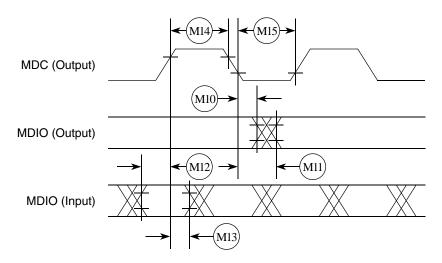

# 11.4 MII Serial Management Channel Timing (MDIO, MDC)

**Table 18. MII Serial Management Channel Signal Timing**

| Num | Characteristic                                           | Min | Max | Unit       |

|-----|----------------------------------------------------------|-----|-----|------------|

| M10 | MDC falling edge to MDIO output invalid (min prop delay) | 0   | _   | ns         |

| M11 | MDC falling edge to MDIO output valid (max prop delay)   | _   | 25  | ns         |

| M12 | MDIO (input) to MDC rising edge setup                    | 10  | _   | ns         |

| M13 | MDIO (input) to MDC rising edge hold                     | 0   | _   | ns         |

| M14 | MDC pulse width high                                     | 40% | 60% | MDC period |

| M15 | MDC pulse width low                                      | 40% | 60% | MDC period |

Figure 17. MII Serial Management Channel TIming Diagram

MCF547x Integrated Microprocessor Electrical Characteristics, Rev. 2

# 12 General Timing Specifications

Table 19 lists timing specifications for the GPIO, PSC, DREQ, DACK, and external interrupts.

**Table 19. General AC Timing Specifications**

| Name | Characteristic                             | Min | Max | Unit   |

|------|--------------------------------------------|-----|-----|--------|

| G1   | CLKIN high to signal output valid          | _   | 2   | PSTCLK |

| G2   | CLKIN high to signal invalid (output hold) | 0   | _   | ns     |

| G3   | Signal input pulse width                   | 2   | _   | PSTCLK |

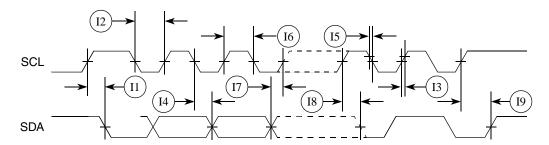

# 13 I<sup>2</sup>C Input/Output Timing Specifications

Table 20 lists specifications for the I<sup>2</sup>C input timing parameters shown in Figure 18.

Table 20. I<sup>2</sup>C Input Timing Specifications between SCL and SDA

| Num | Characteristic                                                         | Min | Max | Units      |

|-----|------------------------------------------------------------------------|-----|-----|------------|

| l1  | Start condition hold time                                              | 2   | _   | Bus clocks |

| 12  | Clock low period                                                       | 8   | _   | Bus clocks |

| 13  | SCL/SDA rise time (V <sub>IL</sub> = 0.5 V to V <sub>IH</sub> = 2.4 V) | _   | 1   | mS         |

| 14  | Data hold time                                                         | 0   | _   | ns         |

| 15  | SCL/SDA fall time (V <sub>IH</sub> = 2.4 V to V <sub>IL</sub> = 0.5 V) | _   | 1   | mS         |

| 16  | Clock high time                                                        | 4   | _   | Bus clocks |

| 17  | Data setup time                                                        | 0   | _   | ns         |

| 18  | Start condition setup time (for repeated start condition only)         | 2   | _   | Bus clocks |

| 19  | Stop condition setup time                                              | 2   | _   | Bus clocks |

Table 21 lists specifications for the I<sup>2</sup>C output timing parameters shown in Figure 18.

| Table 21. | I <sup>2</sup> C Output | Timing: | <b>Specifications</b> | between S | CL and SDA |

|-----------|-------------------------|---------|-----------------------|-----------|------------|

|-----------|-------------------------|---------|-----------------------|-----------|------------|

| Num             | Characteristic                                                            | Min | Max | Units      |

|-----------------|---------------------------------------------------------------------------|-----|-----|------------|

| 11 <sup>1</sup> | Start condition hold time                                                 | 6   | _   | Bus clocks |

| I2 <sup>1</sup> | Clock low period                                                          | 10  | _   | Bus clocks |

| I3 <sup>2</sup> | SCL/SDA rise time (V <sub>IL</sub> = 0.5 V to V <sub>IH</sub> = 2.4 V)    | _   | _   | μS         |

| I4 <sup>1</sup> | Data hold time                                                            | 7   | _   | Bus clocks |

| I5 <sup>3</sup> | SCL/SDA fall time ( $V_{IH} = 2.4 \text{ V to } V_{IL} = 0.5 \text{ V}$ ) | _   | 3   | ns         |

| I6 <sup>1</sup> | Clock high time                                                           | 10  | _   | Bus clocks |

| I7 <sup>1</sup> | Data setup time                                                           | 2   | _   | Bus clocks |

| I8 <sup>1</sup> | Start condition setup time (for repeated start condition only)            | 20  | _   | Bus clocks |

| I9 <sup>1</sup> | Stop condition setup time                                                 | 10  | _   | Bus clocks |

#### NOTES:

Because SCL and SDA are open-collector-type outputs, which the processor can only actively drive low, the time SCL or SDA take to reach a high level depends on external signal capacitance and pull-up resistor values.

Specified at a nominal 50-pF load.

Figure 18 shows timing for the values in Table 20 and Table 21.

Figure 18. I<sup>2</sup>C Input/Output Timings

Note: Output numbers depend on the value programmed into the IFDR; an IFDR programmed with the maximum frequency (IFDR = 0x20) results in minimum output timings as shown in Table 21. The I<sup>2</sup>C interface is designed to scale the actual data transition time to move it to the middle of the SCL low period. The actual position is affected by the prescale and division values programmed into the IFDR; however, the numbers given in Table 21 are minimum values.

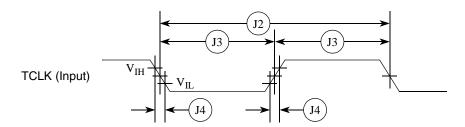

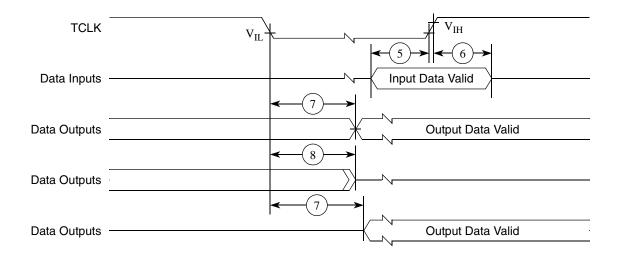

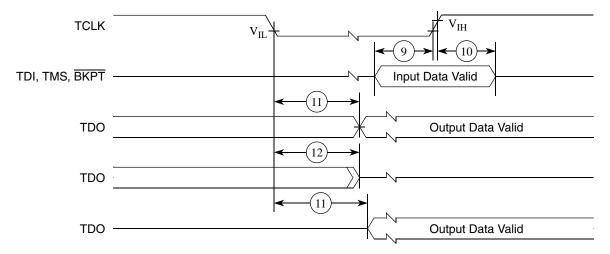

#### JTAG and Boundary Scan Timing 14

Table 22. JTAG and Boundary Scan Timing

| Num | Characteristics <sup>1</sup>                       | Symbol              | Min   | Max  | Unit            |

|-----|----------------------------------------------------|---------------------|-------|------|-----------------|

| J1  | TCLK Frequency of Operation                        | f <sub>JCYC</sub>   | DC    | 10   | MHz             |

| J2  | TCLK Cycle Period                                  | t <sub>JCYC</sub>   | 2     | _    | t <sub>CK</sub> |

| J3  | TCLK Clock Pulse Width                             | t <sub>JCW</sub>    | 15.15 | _    | ns              |

| J4  | TCLK Rise and Fall Times                           | t <sub>JCRF</sub>   | 0.0   | 3.0  | ns              |

| J5  | Boundary Scan Input Data Setup Time to TCLK Rise   | t <sub>BSDST</sub>  | 5.0   | _    | ns              |

| J6  | Boundary Scan Input Data Hold Time after TCLK Rise | t <sub>BSDHT</sub>  | 24.0  | _    | ns              |

| J7  | TCLK Low to Boundary Scan Output Data Valid        | t <sub>BSDV</sub>   | 0.0   | 15.0 | ns              |

| J8  | TCLK Low to Boundary Scan Output High Z            | t <sub>BSDZ</sub>   | 0.0   | 15.0 | ns              |

| J9  | TMS, TDI Input Data Setup Time to TCLK Rise        | t <sub>TAPBST</sub> | 5.0   | _    | ns              |

| J10 | TMS, TDI Input Data Hold Time after TCLK Rise      | t <sub>TAPBHT</sub> | 10.0  | _    | ns              |

| J11 | TCLK Low to TDO Data Valid                         | t <sub>TDODV</sub>  | 0.0   | 15.0 | ns              |

| J12 | TCLK Low to TDO High Z                             | t <sub>TDODZ</sub>  | 0.0   | 15.0 | ns              |

| J13 | TRST Assert Time                                   | t <sub>TRSTAT</sub> | 100.0 | _    | ns              |

| J14 | TRST Setup Time (Negation) to TCLK High            | t <sub>TRSTST</sub> | 10.0  | _    | ns              |

NOTES:

1 MTMOD is expected to be a static signal. Hence, it is not associated with any timing

**Figure 19. Test Clock Input Timing**

Figure 20. Boundary Scan (JTAG) Timing

**Figure 21. Test Access Port Timing**

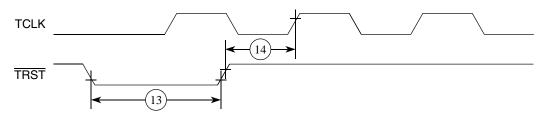

Figure 22. TRST Timing Debug AC Timing Specifications

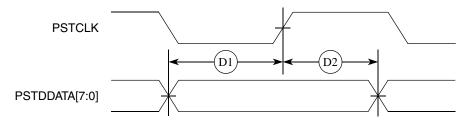

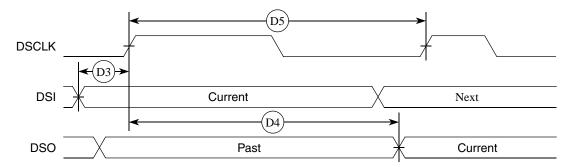

Table 23 lists specifications for the debug AC timing parameters shown in Figure 24.

| Num             | Characteristic           | 66  | MHz | Units   |  |

|-----------------|--------------------------|-----|-----|---------|--|

| Num             | Characteristic           | Min | Max |         |  |

| D1              | PSTDDATA to PSTCLK setup | 4.5 |     | ns      |  |

| D2              | PSTCLK to PSTDDATA hold  | 4.5 |     | ns      |  |

| D3              | DSI-to-DSCLK setup       | 1   |     | PSTCLKs |  |

| D4 <sup>1</sup> | DSCLK-to-DSO hold        | 4   |     | PSTCLKs |  |

| D5              | DSCLK cycle time         | 5   |     | PSTCLKs |  |

Figure 23 shows real-time trace timing for the values in Table 23.

Figure 23. Real-Time Trace AC Timing

Figure 24 shows BDM serial port AC timing for the values in Table 23.

Figure 24. BDM Serial Port AC Timing

NOTES:

1 DSCLK and DSI are synchronized internally. D4 is measured from the synchronized DSCLK input relative to the rising edge of CLKOUT.

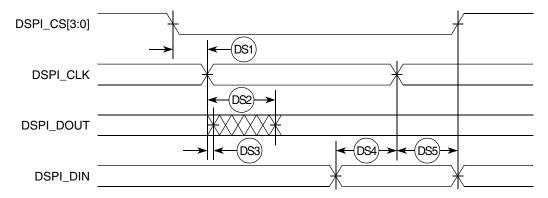

# 15 DSPI Electrical Specifications

Table 24 lists DSPI timings.

**Table 24. DSPI Modules AC Timing Specifications**

| Name | Characteristic                                    | Min     | Max       | Unit |

|------|---------------------------------------------------|---------|-----------|------|

| DS1  | DSPI_CS[3:0] to DSPI_CLK                          | 1 × tck | 510 × tck | ns   |

| DS2  | DSPI_CLK high to DSPI_DOUT valid.                 | _       | 12        | ns   |

| DS3  | DSPI_CLK high to DSPI_DOUT invalid. (Output hold) | 2       | _         | ns   |

| DS4  | DSPI_DIN to DSPI_CLK (Input setup)                | 10      | _         | ns   |

| DS5  | DSPI_DIN to DSPI_CLK (Input hold)                 | 10      | _         | ns   |

The values in Table 24 correspond to Figure 25.

Figure 25. DSPI Timing

# 16 Timer Module AC Timing Specifications

Table 25 lists timer module AC timings.

**Table 25. Timer Module AC Timing Specifications**

| Name | Characteristic                        | 0–66 | Unit |        |

|------|---------------------------------------|------|------|--------|

|      |                                       | Min  | Max  | Oille  |

| T1   | TIN0 / TIN1 / TIN2 / TIN3 cycle time  | 3    | _    | PSTCLK |

| T2   | TIN0 / TIN1 / TIN2 / TIN3 pulse width | 1    | _    | PSTCLK |

#### THIS PAGE INTENTIONALLY LEFT BLANK

MCF547x Integrated Microprocessor Electrical Characteristics, Rev. 2

#### How to Reach Us:

#### **Home Page:**

www.freescale.com

#### E-mail:

support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Technical Information Center 3-20-1, Minami-Azabu, Minato-ku Tokyo 106-0047, Japan 0120 191014 or +81 3 3440 3569 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.© Freescale Semiconductor, Inc. 2004. All rights reserved.

MCF5475EC Rev. 2 10/2004